о

р te

CN со 00

Изобретение относится к вычислительой технике и может быть использовано в нформационно-измерительных системах, апример, в переносных и автономных сисемах сбора и обработки аналоговых, в том исле и хроматографических сигналов.

Целью изобретения является повышеие точности, помехоустойчивости и расшиение функциональных возможностей за чет обеспечения опроса каналов в произвольной последовательности.

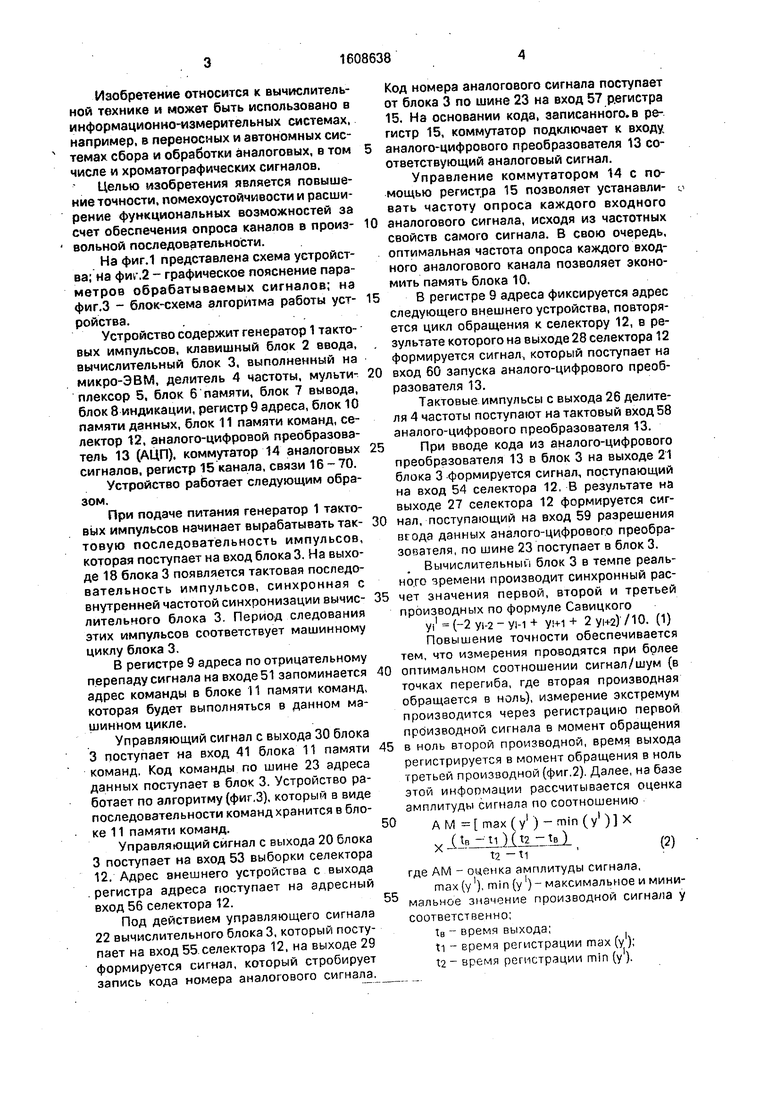

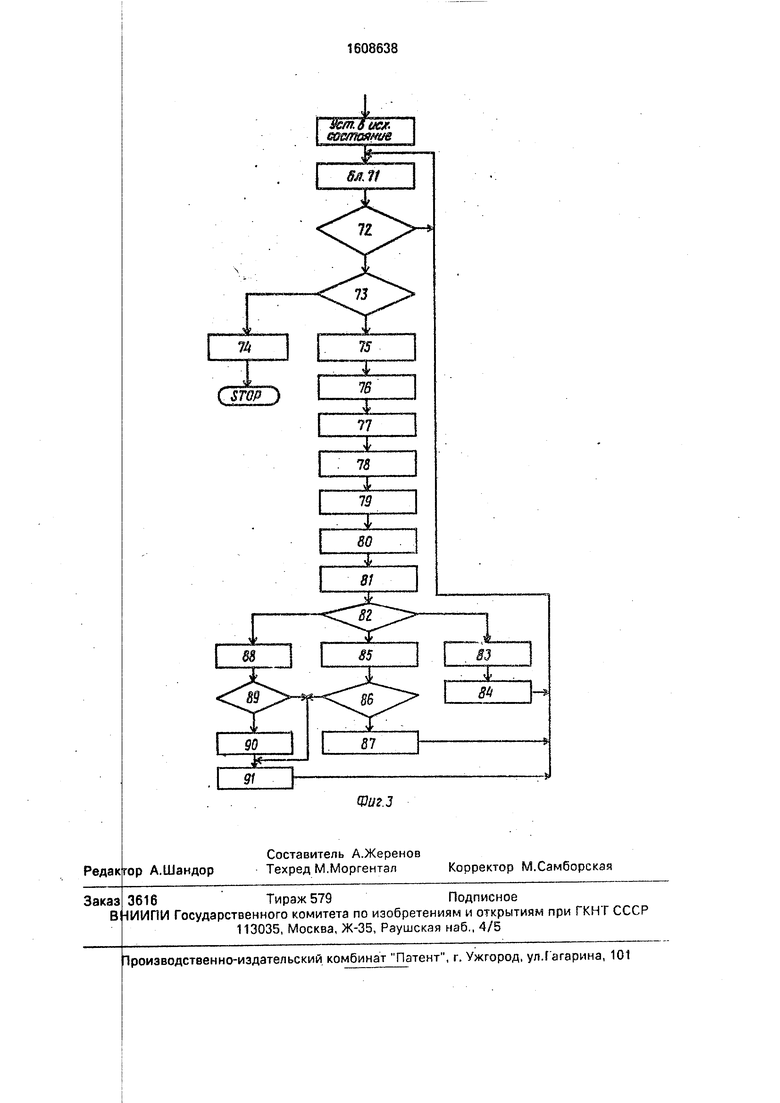

На фиг.1 представлена схема устройства; на фи1,-.2 - графическое пояснение параметров обрабатываемых сигналов; на фиг.З - блок-схема алгоритма работы устройства..

Устройство содержит генератор 1 тактовых импульсов, клавишный блок 2 ввода, вычислительный блок 3, выполненный на микро-ЭВМ, делитель 4 частоты, мультиплексор 5. блок 6 памяти, блок 7 вывода, блок 8 индикации, регистр 9 адреса, блок iu памяти данных, блок 11 памяти команд, селектор 12. аналого-цифровой преобразователь 13 (АЦП), коммутатор 14 аналоговых сигналов, регистр 15 канала, связи 16 - 70. Устройство работает следующим обраПри подаче питания генератор 1 тактовых импульсов начинает вырабатывать тактовую последовательность импульсов, которая поступает на вход блока 3. На выходе 18 блока 3 появляется тактовая последовательность импульсов, синхронная с внутренней частотой синхронизации вычислительного блока 3. Период следования этих импульсов соответствует машинному

циклу блока 3.

В регистре 9 адреса по отрицательному перепаду сигнала на входе 51 запоминается адрес команды в блоке 11 памяти команд, которая будет выполняться в данном ма- цJиннoм цикле.

Управляющий сигнал с выхода 30 Ьлока 3 поступает на вход 41 блока 11 памяти команд, Код команды по шине 23 адреса данных поступает в блок 3. Устройство работает по алгоритму (фиг.З). который в виде последовательности команд хранится в бло. ке 11 памяти команд.ппРпо„а

Управляющий сигнал с выхода 20 Ьлока

3 поступает на вход 53 выборки селектора

12 Адрес внешнего устройства с выхода

.регистра адреса поступает на адресный

вход 56 селектора 12.

Под действием управляющего сигнала 22 вычислительного блока 3. который поступает на вход 55.селектора 12. на выходе 29 формируется сигнал, который стробирует запись кода номера аналогового сигналу.

5

10

15

Код номера аналогового сигнала поступает от блока 3 по шине 23 на вход 57 регистра 15. На основании кода, записанного, в регистр 15. коммутатор подключает к входу аналого-цифрового преобразователя 13 соответствующий аналоговый сигнал.

Управление коммутатором 14 с помощью регистра 15 позволяет устанавли- L вать частоту опроса каждого входного аналогового сигнала, исходя из частотных свойств самого сигнала. В свою очередь, оптимальная частота опроса каждого входного аналогового канала позволяет экономить память блока 10.

В регистре 9 адреса фиксируется адрес следующего внешнего устройства, повторяется цикл обращения к селектору 12. в результате которого на выходе 28 селектора 12 формируется сигнал, который поступает на вход 60 запуска аналого-цифрового преобразователя 13.

Тактовые импульсы с выхода 26 делителя 4 частоты поступают на тактовый вход 58 аналого-цифрового преобразователя 13. При вводе кода из аналого-цифрового преобразователя 13 в блок 3 на выходе 21 блока 3 формируется сигнал, поступающий на вход 54 селектора 12, В результате на выходе 27 селектора 12 формируется сиг- нал. поступающий на вход 59 разрешения Bf ода данных аналого-цифрового преобразователя, по шине 23 поступает в блок 3.

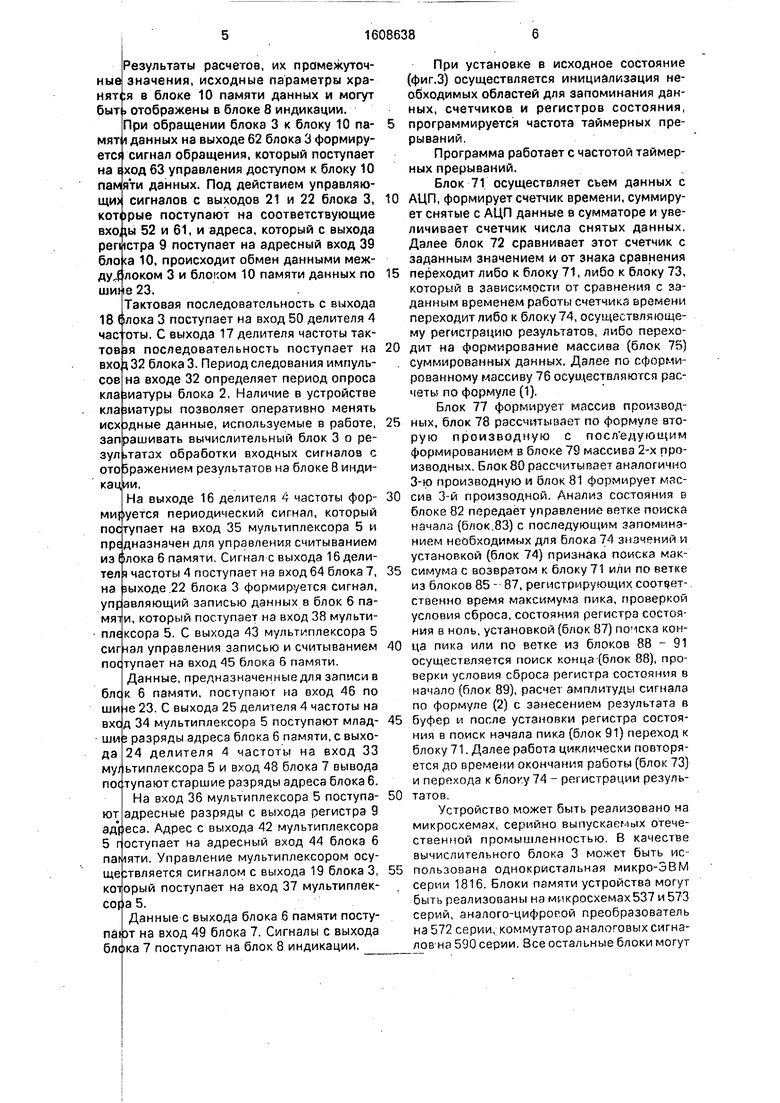

Вычислительный блок 3 в темпе реального времени производит синхронный рас- 5 чет значения первой, второй и третьей производных по формуле Савицкого

(-2 у1-2 - + + 2 У1+2)710. (1) Повышение точности обеспечивается тем что измерения проводятся при более 0 оптимальном соотношении сигнал/шум (в точках перегиба, где вторая производная обращается в ноль), измерение экстремум производится через регистрацию первой производной сигнала в момент обращения 5 в ноль второй производной, время, выхода регистрируется в момент обращения в ноль третьей производной {фиг,2). Далее, на базе этой информации рассчитывается оценка амплитуды сигнала по соотношению 50 А W max(y )-niin(y )X

у )il2- (2)

Т2 - t1

где AM - оценка амплитуды сигнала.

max (у ), min {у ) - максимальное и мини- 55 мальное значение производной сигнала у соответственно;

ta время выхода;

ti - время регистрации max (у); t2 - время регистрации min (у ).

Результаты расчетов, их промежуточные значения, исходные параметры хранят; ;я в блоке 10 памяти данных и могут быт отображены в блоке 8 индикации.

При обращении блока 3 к блоку 10 памяти данных на выходе 62 блока 3 формиру- етс5 сигнал обращения, который поступает на ход 63 управления доступом к блоку 10 памяти данных. Под действием управляю- щи сигналов с выходов 21 и 22 блока 3, которые поступают на соответствующие входы 52 и 61, и адреса, который с выхода регистра 9 поступает на адресный вход 39 бло са 10, происходит обмен данными между J локом 3 и 10 памяти данных по ште 23.

Тактовая последовательность с выхода 18 Йлока 3 поступает на вход 50 делителя А . С выхода 17 делителя частоты тактов зя последовательность поступает на вхо 32 блока 3. Период следования импульсов на входе 32 определяет период опроса кла5иатуры блока 2, Наличие в устройстве кла 5иатуры позволяет оперативно менять исхэдные данные, используемые в работе, запрашивать вычислительный блок 3 о результатах обработки входных сигналов с ото Зражением результатов на блоке 8 индикации.

На выходе 16 делителя 4 частоты фор- 1уется периодический сигнал, который гупает на вход 35 мультиплексора 5 и предназначен для управления считыванием флока 6 памяти. Сигнал с выхода 16дели- частоты 4 поступает на вход 64 блока 7, зыходе.22 блока 3 формируется сигнал, вляющий записью данных в блок 6 па- , который поступает на вход 38 мульти- сора 5. С выхода 43 мультиплексора 5 сигнал управления записью и считыванием

на вход 45 блока 6 памяти. Данные, предназначенные для записи в 6 памяти, поступают на вход 46 по не 23. С выхода 25 делителя 4 частоты на вхсд 34 мультиплексора 5 поступают млад- э разряды адреса блока 6 памяти, с выхо- 24 делителя 4 частоты на вход 33 ьтиплексора 5 и вход 48 блока 7 вывода по( тупаютстаршие разряды адреса блока 6. На вход 36 мультиплексора 5 поступа- адресные разряды с выхода регистра 9 leca. Адрес с выхода 42 мультиплексора гоступает на адресный вход 44 блока 6 памяти. Управление мультиплексором осуществляется сигналом с выхода 19 блока 3, который поступает на вход 37 мультиплексора 5.

Данные с выхода блока .6 памяти посту- naijOT на вход 49 блока 7. Сигналы с выхода блока 7 поступают на блок 8 индикации.

поступает

блрк ши

шм да му;

ащ

5

При установке в исходное состояние (фиг.З) осуществляется инициализация необходимых областей для запоминания данных, счетчиков и регистров состояния,

программируется частота таймерных прерываний.

Программа работает с частотой таймерных прерываний.

Блок 71 осуществляет съем данных с

0 АЦП, формирует счетчик времени, суммирует снятые с АЦП данные в сумматоре и увеличивает счетчик числа снятых данных. Далее блок 72 сравнивает этот счетчик с заданным значением и от знака сравнения

5 переходит либо к блоку 71, либо к блоку 73, который в зависимости от сравнения с заданным временем работы счетчика времени переходит либо к блоку 74, осуществляющему регистрацию результатов, либо перехо0 дит на формирование массива (блок 75) суммированных данных. Далее по сформированному массиву 76 осуществляются расчеты по формуле (1).

Блок 77 формирует массив проязвод5 ных, блок 78 рассчйтываат по вторую производную с посл едующим формированием в блоке 79 массива 2-х производных. Блок ВО рассчитывает аналогично 3-ю производную и блок 81 формирует мас0 сив 3-й производной. Анализ состояния в блоке 82 передаёт управление ветке поиска начала (блок.83) с последующим запоминанием необходимых для блока 74 значений и установкой (блок 74) признака поиска мак5 симума с возвратом к блоку 71 или по ветке из блоков 85 - 87, регистрирующих, ственно время максимума пика, проверкой условия сброса, состояния регистра состояния в ноль, установкой (блок 87) по 1Ска кон0 ца пика или по ветке из блоков 88-91 осуществляется поиск конца {блок 88), проверки условия сброса регистра состояния в начало (блок 89), расчет амплитуды сигнала по формуле (2) с занесением результата в

5 буфер и после установки регистра состояния в поиск начала пика (блок 91) переход к блоку 71. Далее работа циклически повторяется до времени окончания работы (блок 73) и перехода к блоку 74 - регистрации резуль0 татов.

Устройство может быть реализовано на микросхемах, серийно выпускаемых отечественной промышленностью. В качестве вычислительного блока 3 может быть ис5 пользована однокристальная микро-ЭВМ серии 1816. Блоки памяти устройства могут быть реализованы на микросхемах537 и 573 серий, аналого-цифрог.ой преобразователь на 572 серии, коммутатор аналоговых сигна- лов-на 590 серии. Все остальные блоки могут

быть реализованы на микросхемах 561 серии.

Формула изобретения Многоканальное устройство для обработки хроматографйческих сигналов, содержащее коммутатор аналоговых сигналов, генератор тактовых импульсов, селектор, блок памяти данных, аналого-цифровой преобразователь, информационный вход которого соединен с выходом коммутатора аналоговых сигналов, информационный вход которого является входом устройства, отличающееся тем, что, с целью повышения точности, помехоустойчивости и расширения функциональных возможностей за счет обеспечения опроса каналов в произвольной последовательности, в него введены клавишный блок ввода, вычислительный блок, делитель частоты, мультиплексор, блок памяти, блок вывода, регистр адреса, регистр канала и блок памяти команд, причем выход генератора тактовых импульсов соединен с синхронизирующим входом вычислительного блока, который соединен двусторонними связями с клавишным блоком ввода, тактовый выход вычислительного блока соединен с синхронизирующим входом регистра адреса и с входом делителя частоты, первый выход которого подключен к входу опроса клавиатуры вычислительного блока, второй выход делителя частоты подключен к первому информационному входу мультиплексора и к первому информационному входу блока вывода, третий выход подключен к второму информационному входу мультиплексора, четвертый выход подключен к третьему информационному входу мультиплексора и к входу разрешения выдачи блока вывода, пятый выход делителя частоты соединен с тактовым входом аналого-цифрового преоба

разователя, первый выход мультиплексора соединен с адресным входом блока памяти, вход записи-считывания которого соединен с вторым выходом мультиплексора, выход блока памяти соединен с вторым информационным входом блока вывода, выход которого является выходом устройства, выход регистра адреса соединен с адресными входами мультиплексора, блока памяти дан- ных, блока памяти команд и селектора, информационный выход вычислительного блока соединен шиной с информационными входами регистра адреса, регистра канала, блока памяти и блока памяти данных, ин- 5 формационный вход вычислительного блока соединен шиной с информационными выходами блока памяти данных, блока памяти команд м аналого-цифрового преобразователя, соответственно выходы селектора со- 0 единены с входом разрешения ввода, с входом запуска аналого-цифрового преобразователя и с входом записи регистра канала, первый управляющий выход вычислительного блока соединен с первым 5 управляющим входом мультиплексора, второй управ ляющий вход мультиплексора, вход записи блока памяти данных и вход разрешения ввода селектора соединены С вторым управляющим выходом вычисли- 0 тельного блока, третий управляющий выход которого соединен с входом выборки селектора, четвертый управляющий выход подключен к входу считывания блока памяти данных и к входу разрешения ввода селек- 35 тора, пятый управляющий выход вычисли- тельного блока соединен с входом разрешения доступа блока памяти данных, шестой управляющий выход соединен с входом записи блока памяти команд, выход ре- 40 гист ра канала соединен с адресным входом коммутатора аналоговых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки хроматографических колонок | 1990 |

|

SU1718227A2 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1987 |

|

SU1413655A1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| Устройство для ввода информации | 1988 |

|

SU1716501A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1991 |

|

RU2029370C1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| УСТРОЙСТВО ОБРАБОТКИ АНАЛОГОВЫХ СИГНАЛОВ С ПРИМЕНЕНИЕМ ЦИФРОВОЙ ФИЛЬТРАЦИИ | 2021 |

|

RU2777306C1 |

Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах. Целью изобретения является повышение точности, помехоустойчивости и расширение функциональных возможностей за счет обеспечения опроса каналов в произвольной последовательности. Устройство содержит генератор 1 тактовых импульсов, клавишный блок 2 ввода, вычислительный блок 3, выполненный на микроЭВМ, делитель 4 частоты, мультиплексор 5, блок 6 памяти, блок 7 вывода, блок 8 индикации регистр 9 адреса, блок 10 памяти данных, блок 11 памяти команд, селектор 12, аналого-цифровой преобразователь 13, коммутатор 14 аналоговых сигналов, регистр 15 канала и связи 16 - 70. 3 ил.

| кл, С 581.323(088.8) 1атент США № 3488480, 06F15/20, G 06 G 7/48 | |||

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| илис Я.Я | |||

| и др | |||

| Первичная обработка хрог атограмм и спектров на ЭВМ | |||

| - Рига, | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Многоканальная система для анализаэКСТРЕМуМОВ | 1977 |

|

SU842826A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1990-11-23—Публикация

1988-10-17—Подача