L- (L-.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для обработки хроматографических сигналов | 1988 |

|

SU1608638A1 |

| Устройство для регистрации одиночных ударов | 1987 |

|

SU1479878A1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1991 |

|

RU2029370C1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| ЦИФРОАНАЛОГОВАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ И ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2022364C1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ МАКСИМАЛЬНОГО ЗНАЧЕНИЯ ИМПУЛЬСНОГО АНАЛОГОВОГО СИГНАЛА | 1993 |

|

RU2063048C1 |

Изобретение относится к вычислительной технике и может быть использовано в 2 кроматографическом приборостроении для автоматического контроля качества (идентичности) колонок. Целью изобретения является расширение функциональных возможностей за счет определения отклонения параметров колонки от идеальных значений. В известное устройство введены цифроаналоговый преобразователь и регистр, информационный вход которого подключен к шине, управляющий вход регистра соединен с соответствующим входом селектора, выход регистра соединен с входом цифроаналогового преобразователя, выход которого является информационным выходом устройства. 3 ил., 1 табл.

Изобретение относится к вычислительной технике, может быть использовано в хроматографическом приборостроении для автоматического контроля качества (идентичности) .колонок и является усовершенствованием изобретения по авт.св. № 1608638.

Целью изобретения является расширение функциональных возможностей путем определения отклонения параметров колонки от идеальных значений.

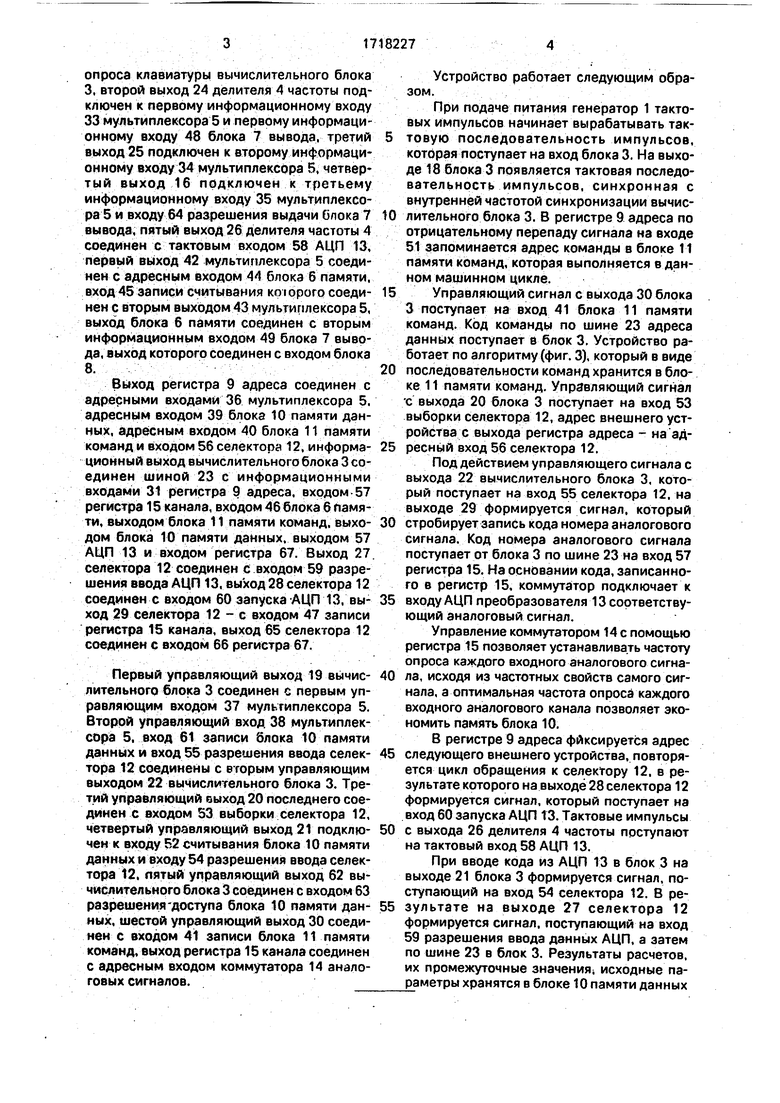

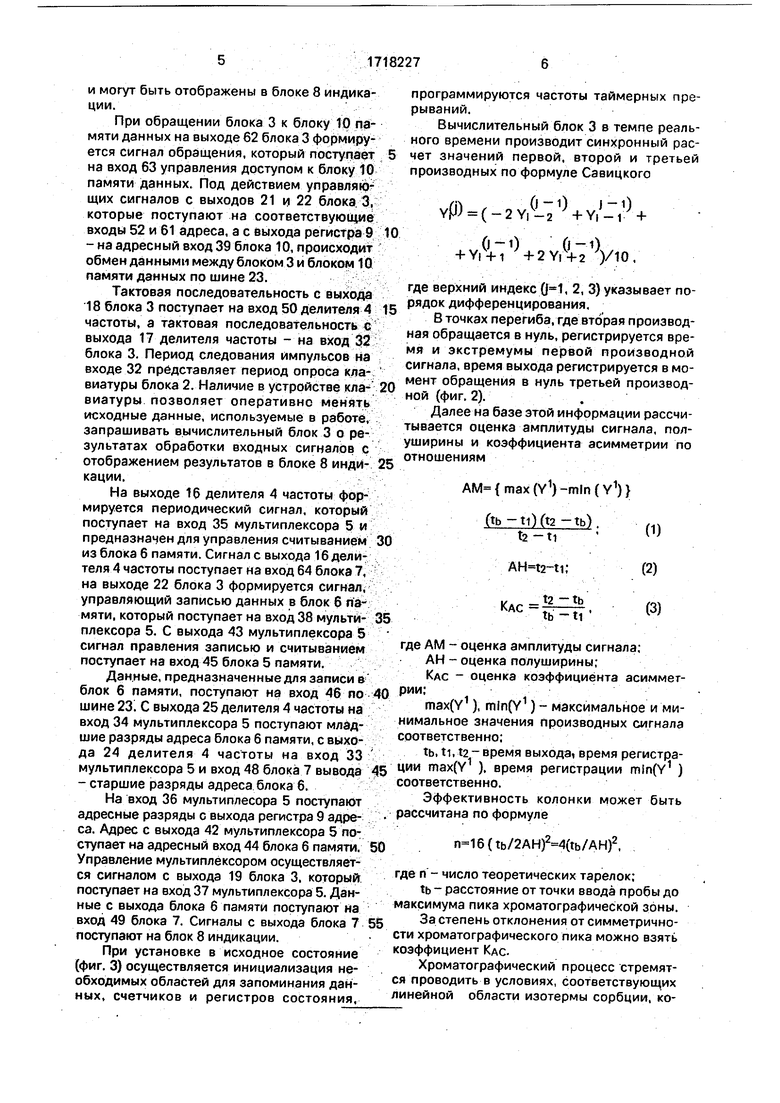

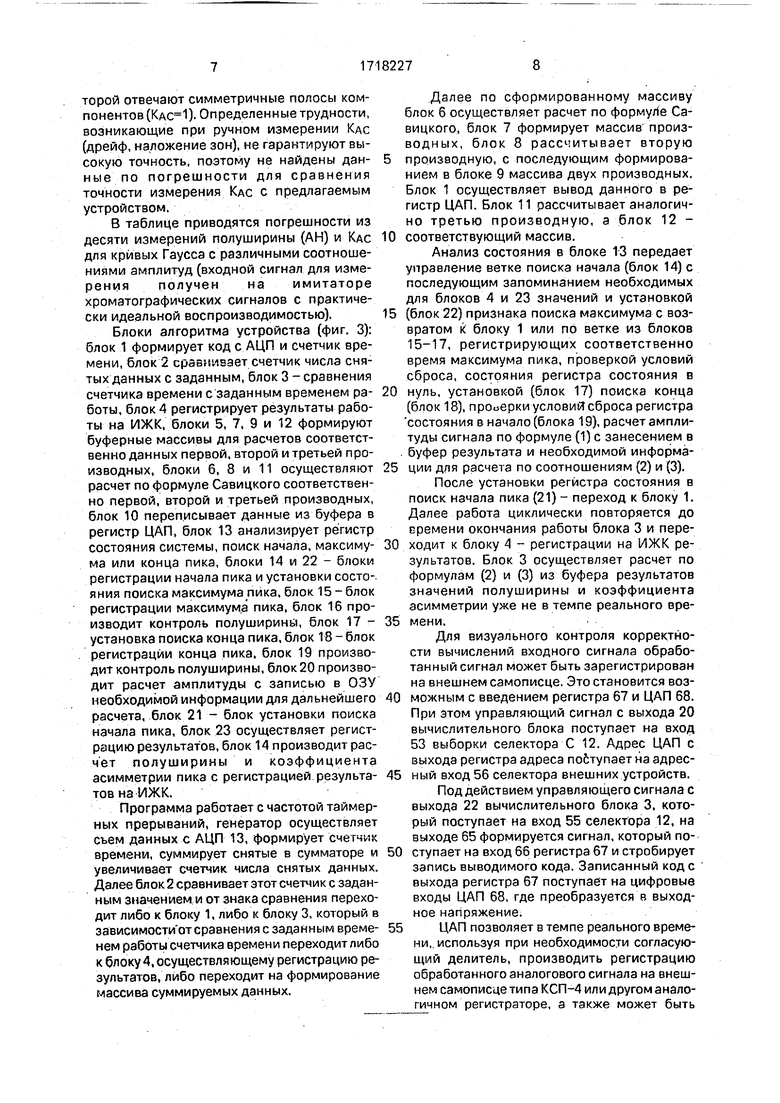

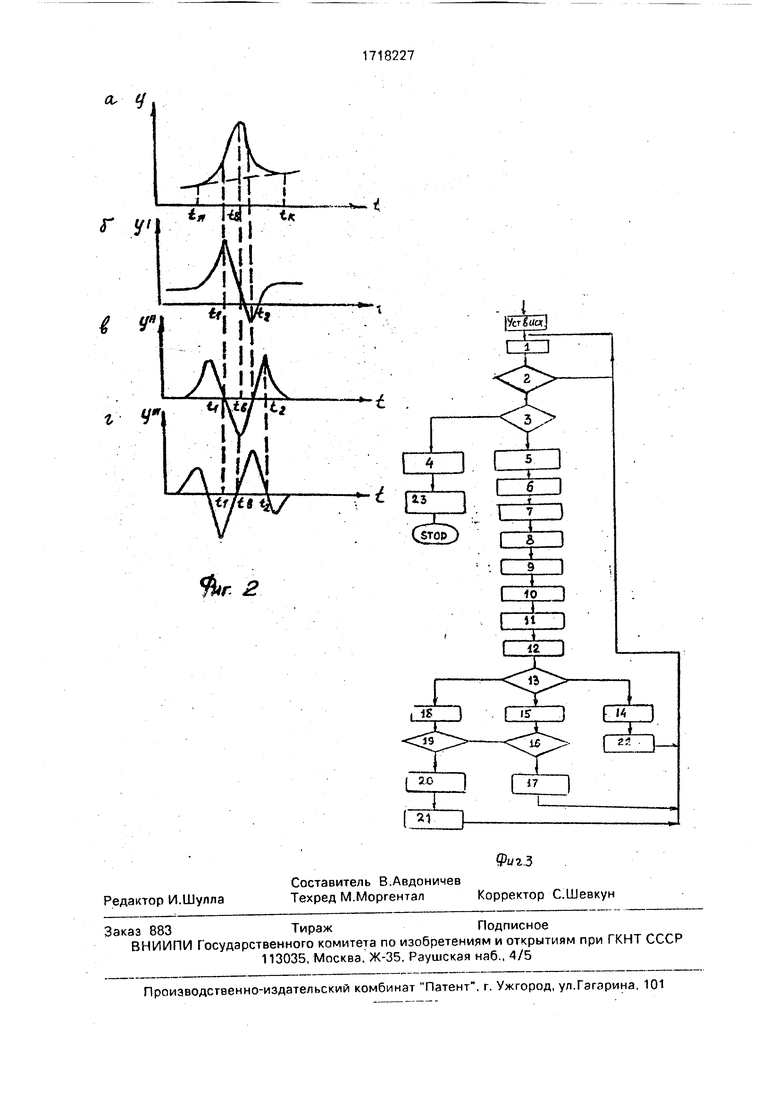

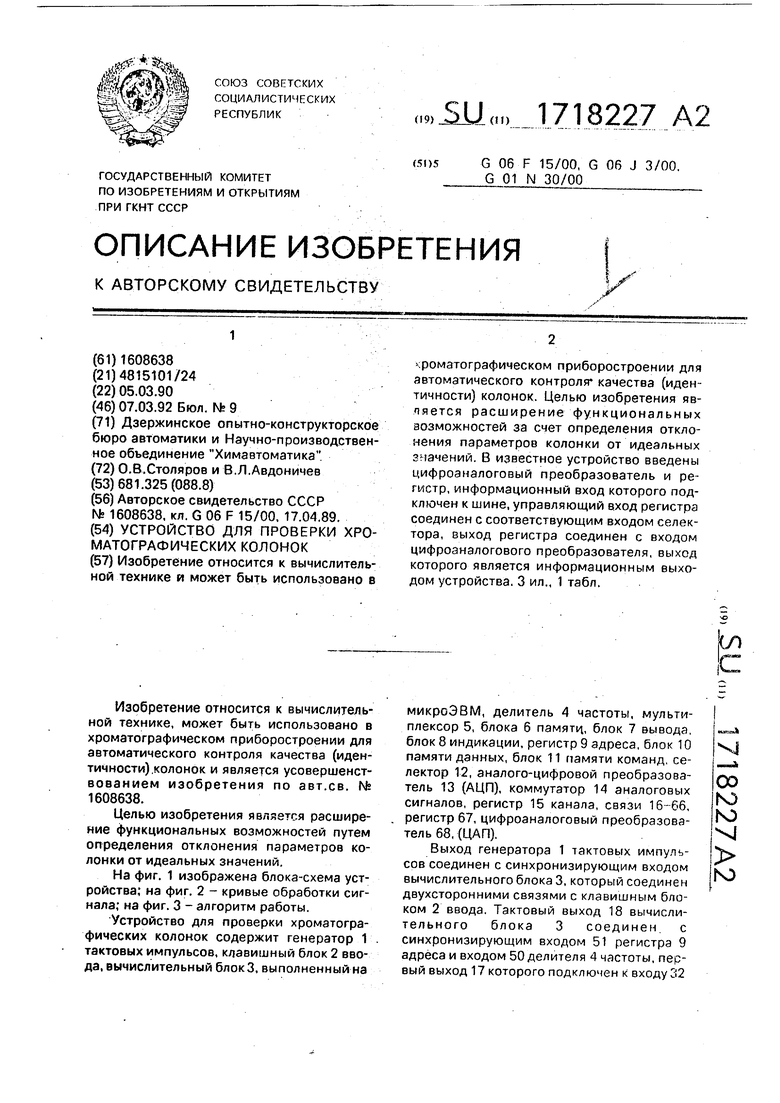

На фиг. 1 изображена блока-схема устройства; на фиг. 2 - кривые обработки сигнала; на фиг. 3 - алгоритм работы.

Устройство для проверки хроматогра- фических колонок содержит генератор 1 тактовых импульсов, клавишный блок 2 ввода, вычислительный блок 3, выполненный на

микроЭВМ, делитель 4 частоты, мультиплексор 5, блока б памяти., блок 7 вывода, блок 8 индикации, регистр 9 адреса, блок 10 памяти данных, блок 11 памяти команд, селектор 12, аналого-цифровой преобразователь 13 (АЦП), коммутатор 14 аналоговых сигналов, регистр 15 канала, связи 16-66, регистр 67, цифроаналоговый преобразователь 68, (ЦАП).

Выход генератора 1 тактовых импульсов соединен с синхронизирующим входом вычислительного блока 3, который соединен двухсторонними связями с клавишным блоком 2 ввода. Тактовый выход 18 вычислительного блока 3 соединен, с синхронизирующим входом 51 регистра 9 адреса и входом 50 делителя 4 частоты, первый выход 17 которого подключен к входу 32

VJ 00

ю к xj

ю

опроса клавиатуры вычислительного блока 3, второй выход 24 делителя 4 частоты подключен к первому информационному входу 33 мультиплексора 5 и первому информационному входу 48 блока 7 вывода, третий выход 25 подключен к второму информационному входу 34 мультиплексора 5, четвертый выход 16 подключен к третьему информационному входу 35 мультиплексора 5 и входу 64 разрешения выдачи блока 7 вывода, пятый выход 26 делителя частоты 4 соединен с тактовым входом 58 АЦП 13, первый выход 42 мультиплексора 5 соединен с адресным входом 44 блока 6 памяти, вход 45 записи считывания крюрого соединен с вторым выходом.4.3. мультиплексора 5, выход блока 6 памяти соединен с вторым информационным входом 49 блока 7 вывода, выход которого соединен с входом блока

Выход регистра 9 адреса соединен с адресными входами 36 мультиплексора 5. адресным входом 39 блока 10 памяти данных, адресным входом 40 блока 11 памяти команд и входом 56 селектора 12, информационный выход вычислительного блока 3 соединен шиной 23 с информационными входами 31 регистра 9 адреса, входом 57 регистра 15 канала, входом 46 блока 6 памяти, выходом блока 11 памяти команд, выходом блока 10 памяти данных, выходом 57 АЦП 13 и входом регистра 67. Выход 27. селектора 12 соединен с входом 59 разрешения ввода АЦП 13, выход 28 селектора 12 соединен с входом 60 запуска АЦП 13, выход 29 селектора 12 - с входом 47 записи регистра 15 канала, выход 65 селектора 12 соединен с входом 66 регистра 67.

Первый управляющий выход 19 вычислительного блока 3 соединен с первым управляющим входом 37 мультиплексора 5. Второй управляющий вход 38 мультиплексора 5. вход 61 записи блока 10 памяти данных и вход 55 разрешения ввода селектора 12 соединены с вторым управляющим выходом 22 вычислительного блока 3. Третий управляющий выход 20 последнего соединен с входом 53 выборки селектора 12, четвертый управляющий выход 21 подключен к входу Б2 считывания блока 10 памяти данных и входу 54 разрешения ввода селектора 12, пятый управляющий выход 62 вычислительного блока 3 соединен с входом 63 разрешения доступа блока 10 памяти данных, шестой управляющий выход 30 соединен с входом 41 записи блока 11 памяти команд, выход регистра 15 канала соединен с адресным входом коммутатора 14 аналоговых сигналов.

Устройство работает следующим образом.

При подаче питания генератор 1 тактовых импульсов начинает вырабатывать тактовую последовательность импульсов, которая поступает на вход блока 3. На выходе 18 блока 3 появляется тактовая последовательность импульсов, синхронная с внутренней частотой синхронизации вычис0 лительного блока 3. В регистре 9 адреса по отрицательному перепаду сигнала на входе 5.1 запоминается адрес команды в блоке 11 памяти команд, которая выполняется в данном машинном цикле.

5 Управляющий сигнал с выхода 30 блока 3 поступает на вход 41 блока 11 памяти команд. Код команды по шине 23 адреса данных поступает в блок 3. Устройство работает по а л го ритму (фиг. 3), который в виде

0 последовательности команд хранится в блоке 11 памяти команд. Управляющий сигнал ;с выхода 20 блока 3 поступает на вход 53 выборки селектора 12, адрес внешнего устройства с выхода регистра адреса - на ад5 ресный вход 56 селектора 12.

Под действием управляющего сигнала с выхода 22 вычислительного блока 3, который поступает на вход 55 селектора 12. на выходе 29 формируется сигнал, который

0 стробирует запись кода номера аналогового сигнала. Код номера аналогового сигнала поступает от блока 3 по шине 23 на вход 57 регистра 15. На основании кода, записанного в регистр 15, коммутатор подключает к

5 входу АЦП преобразователя 13 соответствующий аналоговый сигнал.

Управление коммутатором 14 с помощью регистра 15 позволяет устанавливать частоту опроса каждого входного аналогового сигна0 ла, исходя из частотных свойств самого сигнала, а оптимальная частота опроса каждого входного аналогового канала позволяет экономить память блока 10.

В регистре 9 адреса фиксируется адрес

5 следующего внешнего устройства, повторяется цикл обращения к селектору 12. в результате которого на выходе 28 селектора 12 формируется сигнал, который поступает на вход 60 запуска АЦП 13. Тактовые импульсы

0 с выхода 26 делителя 4 частоты поступают на тактовый вход 58 АЦП 13.

При вводе кода из АЦП 13 в блок 3 на выходе 21 блока 3 формируется сигнал, поступающий на вход 54 селектора 12. В ре5 зультате на выходе 27 селектора 12 формируется сигнал, поступающий на вход 59 разрешения ввода данных АЦП. а затем по шине 23 в блок 3. Результаты расчетов, их промежуточные значения; исходные па- раметры хранятся в блоке 10 памяти данных

и могут быть отображены в блоке 8 индикации.

При обращении блока 3 к блоку 10 памяти данных на выходе 62 блока 3 формируется сигнал обращения, который поступает на вход 63 управления доступом к блоку 10 памяти данных. Под действием управляющих сигналов с выходов 21 и 22 блока. 3, которые поступают на соответствующие входы 52 и 61 адреса, а с выхода регистра 9

-на адресный вход 39 блока 10, происходит обмен данными между блоком 3 и блоком 10 памяти данных по шине 23.

Тактовая последовательность с выхода 18 блока 3 поступает на вход 50 делителя 4 частоты, а тактовая последовательность с выхода 17 делителя частоты - на вход 32 блока 3. Период следования импульсов на входе 32 представляет период опроса клавиатуры блока 2. Наличие в устройстве кла- виатуры позволяет оперативно менять исходные данные, используемые в работе, запрашивать вычислительный блок 3 о результатах обработки входных сигналов с отображением результатов в блоке 8 индикации.

На выходе 16 делителя А частоты формируется периодический сигнал, который поступает на вход 35 мультиплексора 5 и предназначен для управления считыванием из блока б памяти. Сигнал с выхода 16 делителя 4 частоты поступает на вход 64 блока 7, на выходе 22 блока 3 формируется сигнал; управляющий записью данных в блок 6 памяти, который поступает на вход 38 мультиплексора 5. С выхода 43 мультиплексора 5 сигнал правления записью и считыванием поступает на вход 45 блока 5 памяти.

Данные, предназначенные для записи в блок 6 памяти, поступают на вход 46 по шине 23 С выхода 25 делителя 4 частоты на вход 34 мультиплексора 5 поступают младшие разряды адреса блока 6 памяти, с выхода 24 делителя 4 частоты на вход 33 мультиплексора 5 и вход 48 блока 7 вывода

-старшие разряды адреса блока 6.

На вход 36 мультиплесора 5 поступают адресные разряды с выхода регистра 9 адреса. Адрес с выхода 42 мультиплексора 5 поступает на адресный вход 44 блока 6 памяти. Управление мультиплексором осуществляется сигналом с выхода 19 блока 3. который поступает на вход 37 мультиплексора 5. Данные с выхода блока 6 памяти поступают на вход 49 блока 7. Сигналы с выхода блока 7 поступают на блок 8 индикации.

При установке в исходное состояние (фиг. 3} осуществляется инициализация необходимых областей для запоминания данных, счетчиков и регистров состояния,

программируются частоты таймерных прерываний.

Вычислительный блок 3 в темпе реального времени производит синхронный рас- чет значений первой, второй и третьей производных по формуле Савицкого

10

YP).(-2Y,0-V)tY1J--| + + Y|(VV) + 2Y,(+21))/10.

где верхний индекс , 2, 3) указывает порядок дифференцирования.

В точках перегиба, где вторая производная обращается в нуль, регистрируется время и экстремумы первой производной сигнала, время выхода регистрируется в момент обращения в нуль третьей производной (фиг, 2)..

Далее на базе этой информации рассчитывается оценка амплитуды сигнала, полуширины и коэффициента асимметрии по отношениям

(Y1)-mln(Y1)} (tb -ti)(t2 -tb).

t2-tl

AH t2-ti;

(1)

(2)

35

K.r - t2 tb

KAC tb-ti

(3)

где AM-оценка амплитуды сигнала; АН - оценка полуширины; Кдс - оценка коэффициента асиммет- РИИ;.

max(Y ), min(Y ) - максимальное и минимальное значения производных сигнала соответственно;

tb, ti, t2 - время выхода, время регистрации max(Y1 ), время регистрации mlnfY1 ) соответственно.

Эффективность колонки может быть рассчитана по формуле

50

(tb/2AH)(tb/AH)2,

где п - число теоретических тарелок;

tb - расстояние от точки ввода пробы до максимума пика хроматографической зоны. За степень отклонения от симметричности хроматографического пика можно взять коэффициент КАС.

Хроматографический процесс стремятся проводить в условиях, соответствующих линейной области изотермы сорбции, которой отвечают симметричные полосы компонентов (). Определенные трудности, возникающие при ручном измерении Кдс (дрейф, наложение зон), не гарантируют высокую точность, поэтому не найдены дан- ные по погрешности для сравнения точности измерения КАС с предлагаемым устройством.

В таблице приводятся погрешности из десяти измерений полуширины (АН) и КАС для кривых Гаусса с различными соотношениями амплитуд (входной сигнал для измерения получен на имитаторе хроматографических сигналов с практически идеальной воспроизводимостью).

Блоки алгоритма устройства (фиг. 3): блок 1 формирует код с АЦП и счетчик времени, блок 2 сравнивает счетчик числа снятых данных с заданным, блок 3 - сравнения счетчика времени с заданным временем ра- боты, блок 4 регистрирует результаты работы на ИЖК, блоки 5, 7, 9 и 12 формируют буферные массивы для расчетов соответственно данных первой, второй и третьей производных, блоки 6, 8 и 11 осуществляют расчет по формуле Савицкого соответственно первой, второй и третьей производных, блок 10 переписывает данные из буфера в регистр ЦАП, блок 13 анализирует регистр состояния системы, поиск начала, максиму- ма или конца пика, блоки 14 и 22 - блоки регистрации начала пика и установки состояния поиска максимума пика, блок 15-блок регистрации максимума пика, блок 16 производит контроль полуширины, блок 17 - установка поиска конца пика, блок 18 - блок регистрации конца пика, блок 19 производит контроль полуширины, блок 20 производит расчет амплитуды с записью в ОЗУ необходимой информации для дальнейшего расчета, блок 21 - блок установки поиска начала пика, блок 23 осуществляет регистрацию результатов, блок 14 производит расчет полуширины и коэффициента асимметрии пика с регистрацией результа- тов на ИЖК.

Программа работает с частотой таймер- ных прерываний, генератор осуществляет съем данных с АЦП 13, формирует счетчик времени, суммирует снятые в сумматоре и увеличивает счетчик числа снятых данных. Далее блок 2 сравнивает этот счетчик с задан- ным значением и от знака сравнения переходит либо к блоку 1, либо к блоку 3, который в зависимости от сравнения с заданным време- нем работы счетчика времени переходит либо к блоку 4, осуществляющему регистрацию результатов, либо переходит на формирование массива суммируемых данных.

Далее по сформированному массиву блок 6 осуществляет расчет по формуле Савицкого, блок 7 формирует массив произ- водных, блок 8 рассчитывает вторую производную, с последующим формированием в блоке 9 массива двух производных. Блок 1 осуществляет вывод данного в регистр ЦАП. Блок 11 рассчитывает аналогично третью производную, а блок 12 - соответствующий массив.

Анализ состояния в блоке 13 передает управление ветке поиска начала (блок 14) с последующим запоминанием необходимых для блоков 4 и 23 значений и установкой (блок 22) признака поиска максимума с возвратом к блоку 1 или по ветке из блоков 15-17, регистрирующих соответственно время максимума пика, проверкой условий сброса, состояния регистра состояния в нуль, установкой (блок 17) поиска конца (блок 18), проверки условий сброса регистра состояния в начало (блока 19), расчет амплитуды сигнала по формуле (1) с занесением в буфер результата и необходимой информации для расчета по соотношениям (2) и (3).

После установки регистра состояния в поиск начала пика (21) - переход к блоку 1. Далее работа циклически повторяется до времени окончания работы блока 3 и переходит к блоку 4 - регистрации на ИЖК результатов. Блок 3 осуществляет расчет по формулам (2) и (3) из буфера результатов значений полуширины и коэффициента асимметрии уже не в темпе реального времени.

Для визуального контроля корректности вычислений входного сигнала обработанный сигнал может быть зарегистрирован на внешнем самописце, Это становится возможным с введением регистра 67 и ЦАП 68. При этом управляющий сигнал с выхода 20 вычислительного блока поступает на вход 53 выборки селектора С 12. Адрес ЦАП с выхода регистра адреса побтупает на адресный вход 56 селектора внешних устройств.

Под действием управляющего сигнала с выхода 22 вычислительного блока 3, который поступает на вход 55 селектора 12, на выходе 65 формируется сигнал, который поступает на вход 66 регистра 67 и стробирует запись выводимого кода. Записанный код с выхода регистра 67 поступает на цифровые входы ЦАП 68, где преобразуется в выходное напряжение.

ЦАП позволяет в темпе реального времени,, используя при необходимости согласующий делитель, производить регистрацию обработанного аналогового сигнала на внешнем самописце типа КСП-4 или другом аналогичном регистраторе, а также может быть

использован для управления в темпе реального времени внешним объектом.

Формула изобретения

Устройство для проверки хроматогра- фических колонок по авт.св, № 1608638, отличающееся тем, что, с целью расщи рения функциональных возможностей путем определения отклонения параметров

колонки от идеальных значений, в него дополнительно введены цифроаналоговый преобразователь и регистр, информационный вход которого подключен через шину, к информационному выходу вычислительного блока, управляющий вход регистра соединен с соответствующим входом селектора, выход регистра - с входом цифроаналогово- го преобразователя, выход которого являет- ся информационным выходом устройства.

t

в

$

68

0,- ff

| Многоканальное устройство для обработки хроматографических сигналов | 1988 |

|

SU1608638A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1992-03-07—Публикация

1990-03-05—Подача