Изобретение относится к вычислительной технике и может быть использо- вгно автономно или в составе много- щоцессорных вычислительных систем для У1еличения производительности вычислений.

Цель изо&ретения - расширение классе решаемых задач за счет дополнительного извлечения квадратного корня и; чисел, представленных в дополнительном коде.

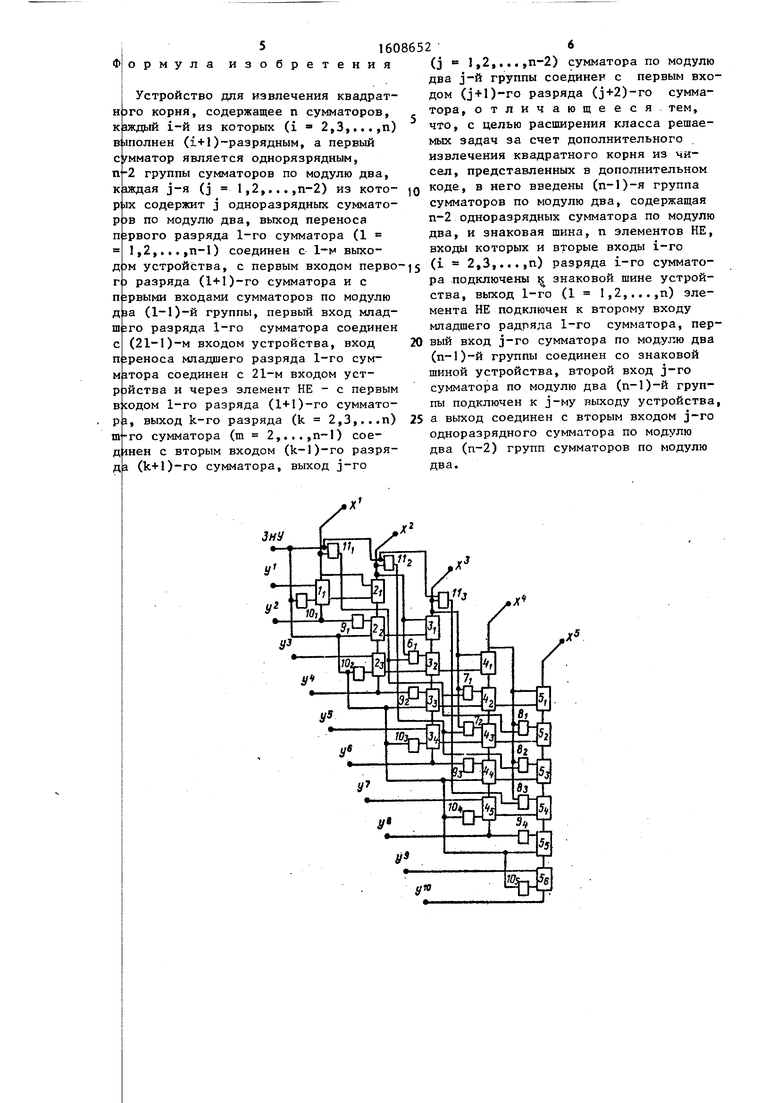

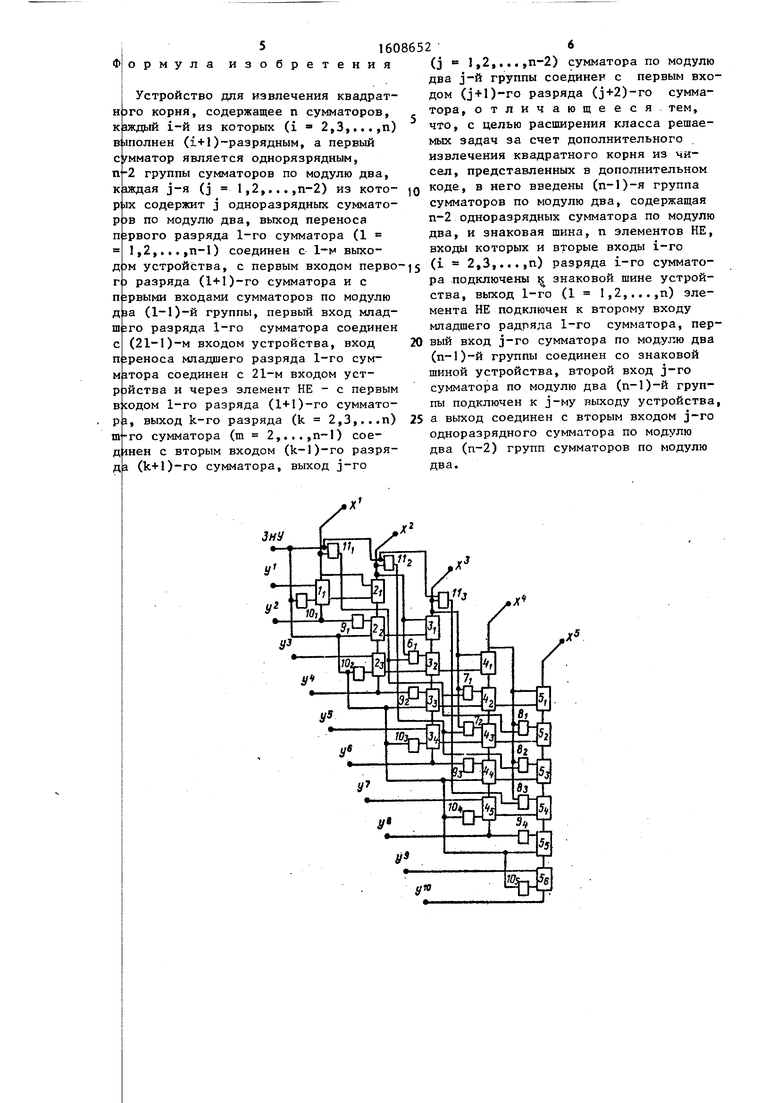

На чертеже представлено схема уст- рс|йства для случая, когда п 5, т.е. в выражении X Зн Y 4 результат X представлен п 5, а аргумент Y р Эрядами.

Устройство для извлечения квадрат- нс(го корня содержит знаковую шину

,ЗнУ, входные шины разрядов Y, Y,...,Y , выходные шины разрядов Х Х, ...,Х , сумматоры 1-5 (нижние индексы обозначают номера разрядов суматоров, например второй разряд третьего сумматора), три группы сумматоров тю модулю два 6-8 (нижние индексы обозначают номер одно- . разрядного сумматора по модулю два, входящего в состав данной группы), элементы НЕ 9, дополнительно введенные элементы НЕ 104-105 , до полнительно введенные сумматоры по модулю два 11,-llg.

Устройство работает следующим образом..-, Вычисление функции X , где, подкоренное значение и искомая

О5

о

СХ)

а ел

tc

величина квадратного корня X представлены в дополнительном коде, выполняется следующим образом.

На первом сумматоре 1 вычисляется невязка Е|. в соответствии с выражением

Е

Y + ЗнУ

(-2),

где SHY - значение знакового разря-

да (О или 1).

Значение первого (старшего) разряда X вычисляется как

X

где р ,

значение тора 1(.

переноса из .сумма

На i-M параллельном сумматоре (i 1,3,...,п) вычисляется невязка

f

,-( в;

соответствии

12Е;.

с выражением ; -Х,- ЗнУ 2

1

Vp - x;.,f зГу.

Значение 1-го разряда X квадратного корня вычисляется как

Х р (i 2,3,....,п), .Пример 1. Извлечь квадратный корень из числа У 0.0101101001.

Ниже приведены значения двоичных кодов на входах соответствующих разрядов сумматоров О - 1-й вход разряда Ц; 1) +1 - 2-й вход разряда - вход переноса разряда 1,; 10 - выход суммы переноса разряда 1;

X

1

старшего

9

5 Л9 - :

р 1 - значение разряда результата;

2)Ю О - 1-е входы разрядов 2.,,., 011 - 2-е входы разрядов 2,2,21 - вход переноса разряда 0110- выходы разрядов 2,22,2 и переноса 2 разряда. 2 , Х р 0;

3)0101 - 1-е входыразр}:дов 3,,3,3, З 1001 -2-е входы разрядов 3,, 32 3.,3

О - вход переноса разряда 3.; 01110 - выходы разрядов ,3,3

и переноса разряда 3 , Х 5

р 0; 4) 01011- 1-е входы разрядов 4

4з,Ч,.5;

11001 - 2-авходы разрядов 4,4,

4o,,.,45;

О - вход переноса разряда 100100 - выходы разрядов

5) 101110 4j, 4., 4,

t,t Л к переноса разряY . 1.

д-р - I,

да

1-е входы разрядов

5 3 : 4 ,5 5, 5б ;

Зо5

2

1

п

15

20

010001 - .2-е входы разрядов 54,5

1 §5 5-, 5

г

вход переноса разряда 5,;

. 6

1000000 - выходы разрядов 5,55, 5,54,5,5 и переноса

Результат 0.10011. Проверка:

разрядов 5, X s р- равен X ЗнУ

(0.10011) 0.0101101001. П р и м е р 2. Извлечь квадратный корень из того же числа У, что и в примере 1, но отрицательного, которое в дополнительном коде имеет вид У - 1.1010010111.

Ниже приведены значения двоичных кодов на входах соответствующих, разрядов сумматоров. 1) 1 - 1-й вход разряда К;

0- 2-й вход разряда

OL - вход переноса разряда Ьх ;

01- выход суммы и переноса разря

0

X

(

да Р

1; о 2) 011 110. - О

1-е входы 2-е

значение старшего разряда результата; разрядов 2,,,2,;

2,,2я,2;

входы разрядов /, ,2., вход переноса разряда .2з;

2,,2,2

1001- выходы разрядов

и переноса 2 разряда

3 2i

3) 1010- 1-е входы разрядов 3,,32,3j,3 О ПО - 2-е входы, разрядов 3,,3, 3,, 3

-вход переноса разряда 10001 - выходы разрядов 3,32,

3,34 и переноса 3 разряда 3, Х р 1 4) 10100 - 1-е входы 43,4,45; 00110 - 2-е входы разрядов ,4,

разрядов 4,4,

1

5

вход переноса разряда 011011 -выходы разрядов 4

Ч. да 4

1

и переноса Х- р 0;

fP

4 разря5) 010001 - 1-е входы разрядов

5 ,5,5 j,5g; 101110 - 2-е входы разрядов

5 ,, 5 2, 5( 5,,

55

50

5о ,5 5

6

вход переноса разряда 1000000 - выходы разрядов 5,5,

5,,34,55-,5 и переноса 5 разряда 5(, 1. Результат равен X ЗнУ ЧУ 1.01101.

Проверка: (0.01101) дополнительный код (1.10011) прямой код (1.10011) 0.0101101001.

160

Формула изобретения

Устройство для извлечения квадрат- нЬго корня, содержащее п сумматоров, каждый i-й из которых (i 2,3,...,п) в.1полнен (1+1)разрядным, а первый С| мматор является однорязрядным, п-2 группы сумматоров по модулю два,

1ждая j-я (J 1,2,...,п-2) из кото- )о содержит j одноразрядных суммато- JB по модулю два, выход переноса jpBoro разряда 1-го сумматора (1 1,2,...,п-1) соединен с 1-м выход)м устройства, с первым входом перво- з 2,3,...,п) разряда 1-го суммато) разряда (1+1)-го сумматора и с

грвыми входами сумматоров по модулю дза (1-1)-и группы, первый вход млад- Ш2ГО разряда 1-го сумматора соединен

(j 1,2,...,п-2) сумматора по модулю два j-й группы соединен с первым входом (j+l)-ro разряда (j+2)-ro сумматора, отличающееся тем, что, с целью расширения класса решаемых задач за счет дополнительного . извлечения квадратного корня из чисел, представленных в дополнительном коде, в него введены (п-1)-я группа сумматоров по модулю два, содержащая п-2 одноразрядных сумматора по модулю два, и знаковая шина, п элементов НЕ, входы которых и вторые входы i-ro

pa .подключены знаковой шине устройства, выход 1-го (1 1,2,...,п) зле- мента НЕ подключен к второму входу младшего радряда 1-го сумматора, пер20 вый вход j-ro сумматора по модулю два (п-1)-й группы соединен со знаковой шиной устройства, второй вход j-ro сумматора по модулю два (п-1)-й группы подключен к j-му выходу устройства,

(21-1)-м входом устройства, вход греноса младшего разряда 1-го сумматора соединен с 21-м входом уст- зйства и через элемент НЕ - с первым содом 1-го разряда (1+1)-го суммато- выход k-ro разряда (k 2,3,...п) т-го сумматора (т 2,.,.,п-1) сое- с вторым входом (k-l)-ro разряда (k+l)ro сумматора, выход j-ro

)о (j 1,2,...,п-2) сумматора по модулю два j-й группы соединен с первым входом (j+l)-ro разряда (j+2)-ro сумматора, отличающееся тем, что, с целью расширения класса решаемых задач за счет дополнительного . извлечения квадратного корня из чисел, представленных в дополнительном коде, в него введены (п-1)-я группа сумматоров по модулю два, содержащая п-2 одноразрядных сумматора по модулю два, и знаковая шина, п элементов НЕ, входы которых и вторые входы i-ro

з 2,3,...,п) разряда 1-го сумматоpa .подключены знаковой шине устройства, выход 1-го (1 1,2,...,п) зле- мента НЕ подключен к второму входу младшего радряда 1-го сумматора, пер20 вый вход j-ro сумматора по модулю два (п-1)-й группы соединен со знаковой шиной устройства, второй вход j-ro сумматора по модулю два (п-1)-й группы подключен к j-му выходу устройства

25 а выход соединен с вторым входом j-ro одноразрядного сумматора по модулю два (п-2) групп сумматоров по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления корней квадратного уравнения | 1980 |

|

SU999060A1 |

| Устройство для извлечения квадратного корня | 1978 |

|

SU773617A1 |

| Устройство для извлечения квадратного корня | 1979 |

|

SU857981A1 |

| Матричный вычислитель | 1983 |

|

SU1137464A1 |

| Матричное устройство для извлечения квадратного корня | 1985 |

|

SU1260951A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

Изобретение относится к вычислительной технике и может быть использовано автономно или в составе вычислительной системы для увеличения производительности вычислений. Целью изобретения является расширение класса решаемых задач за счет дополнительного извлечения квадратного корня из чисел, представленных в дополнительном коде, организаций структуры устройства, удобной для применения в качестве быстродействующего спецпроцессора в составе вычислительных систем и реализации в виде большой интегральной схемы, это достигается благодаря введению знаковой шины, N инверторов и (N-2) сумматоров по модулю два. 1 ил.

X

ЗнИ

7

T fe

7

Авторы

Даты

1990-11-23—Публикация

1988-10-17—Подача