ки (j,-1)-ro столбца, с вторым входом вычислительного элемента (i, + 1.)-H строки (1,+1)-го столбца, с входом суммы вычислительного элемента ((+1) -и строки j, -го столбца и с входом переноса вычислительного элемента (, + 1)-й строки (j,-1)-го .столбца мат рицы, отличающееся тем, что, с целью повышения производитель.кости, оно содержит полусумматор, два сдвигающих регистра и группу элементов И, в матрице вьмислительных элементов вычислительные элементы, расположенные в первой строке j -х столбцов (где j 3, . . . ,2n-t-1), а также в первой строке первого столбца, являются вычислительными элементами второго типа, вычислительный элемент, расположенный в первой строке второго столбца, является вычислительным элементом третьего типа, вычислительные элементы, расположенные в ц -х строках j,-x столбцов (где 1 ). 4,,..,2п + + 1), j 1, . .., п -V, з. -3, если 4 f-, j 2ni2-i если s ),а также во второй строке первог столбца являются вычислительными элементами четвертого типа, вычислительные элементы, расположенные во второй строке второго и третьего столбцов, являются вычислительными элементами пятого типа, вычислительные элементы, расположенные в (16+)7 строках. ( 2)- X столбцов (где i g 1,, . . , ,п-2) а такжев (if,-2)-X строках (1 15)-х столбцов, являются вычислительными элементами шестого типа, вычислительные элементы, расположенные во второй строке столбцов (где j 5,,..) ,),являются вычислительными элементами седьмого типа, вычислитель ные элементы, расположенные в(18+1)-А строках л- столбцов (где ig 2j.,., n) , а также в( +2)-А стро ках Va - 5 столбцов (где Jo, ;П) являются вычислительными элементами восьмого типа, причем знаковый разряд первой входной шины соединен с вторым входом вычислительного элемента второго типа первой строки первого столбца, первый значащий разряд первой входной шины соединен с первым входом вычислительного элемента третьего типа, i -и значащий разряд первой входной шины (i 2,...,п; соединен с первым входом вычислительного элемента второго типа первой строки 2i-го столбца, а также с вторым входом вычислительного элемента второго типа первой строки (2i+1)-ro столбца, знаковьй разряд второй входнон шины соединен с первым входом вычислительного элемеита второго типа первой строки первого столбца, с вторым входом вычислительного элемен-. та третьего типа, j -и значащий разряд (, ...,П-1) второй входной шины соединен с первым входом вычислительного элемента второго типа первой строки (2j+1)-ro столбца, а также с вторым входом вычислительного элемента второго тд1па первой строки ()-го столбца, п-и значащий разряд второй входной шины соединен с первым входом вычислительного элемента второго типа первой строки (2п+1)го столбца, первый и второй выходы, выход суммы и выход переноса вычислительного элеме.нта р-й строки V-го столбца (где р 1,,,.,2п+1,k 1,..., 2h+1) соединены соответственно с первым входом вычислительного элемента (р+1)-й строки (k-1)-ro столбца, с вторым входом вычислительного элемента (р+1)-й строки (К+1)-го столбца, с входом суммы вычислительного элемента (р+1)-й строкиk-го столбца и с входом переноса вьпгаслительного элемента (р+1)-й строки (k-l)-ro столбца, третий выход вычислительного элемента первой строки второго столбца соединен с входом переноса вычислительного элемента второй строки первого столбца, третьи выходы остальных вычислительных элементов р-х строк k -X столбцов соединены с третьими входами вычислительных элементов (р+1)-х строк .()х столбцов, .выходы первого и второго триггеров соединены соответственно с первым и вторым входами полусумматора, выход суммы полусумматора соединен с входом переноса вычислительного элемента . второ.й строки п-го столбца, выход переноса полусумматора соединен с входом переноса вычислительного элемента второй строки (п-1)-го столбца, выход суммы вычислительного элемента Г| -и строки (2t)+2-T)-ro столбца . (где Г 1,..,2п) соединен с информационным входом г-го триггера первой группы триггеров, выход суммы вычислительного элемента (211|+1)-й строки первого столбца соединен с информационным входом первого сдвигающего регистра,s-и выход первого сдвигающего регистра (е 1.,.. ., 1 +log N ) соединен с первым входом (9+2п)-го одноразрядного сумматора группы, выходы триггеров второй группы соединены с первыми входами соответствующих элементов И группы, выходы второго сдвигающего регистра соединены с вторыми входами соответствующих элементов И группы, выходы элементов И группы соединены с третьими входами соответствующих одноразрядных сумматоров . группы, тактовьй вход устройства соединен с тактовыми входами первого и второго сдвигающих регистров и с управляющими входами всех вычислительных элементов матрицы, вход установк устройства соединен с входами установки в О первого и второго триггеров, вход вьщачи результата устройства соединен с информационным входо второго сдвигающего регистра, выходы триггеров второй группы являются выходом результата устройства, кроме того, вычислительный элемент второго типа содержит первьш, второй триггеры и элемент И, причем тактовые входы первого и второго триггеров объединены и являются управляклцим входом вычислительного элемента второго типа, информационные входы первого и второго триггеров являются соответственно первым и вторым входами вычислительного элемента второго типа, выходы первого и второго триггеров соединены соответственно с первым и вторым входами элемента И и являются соответственно первым и вторым выходами вычислительного элемента . второго типа, выход элемента И является выходом суммы вычислительного элемента второго типа, кроме того, вычислительный элемент третьего типа содержит первьш и второйтриггеры, первый и второй элементы И, причем тактовые входы первого и второго триггеров .объединены и являются

управляющим входом вычислительного элемента третьего типа, информационные входы первого и второго триггеров являются, соответственно первым и вторым входами вычислительного элемента третьего типа, инверсный выход первого триггера соединен с первым входом первого элеме-нта И, прямой вь1ход первого триггера соединен с первым входом второго элемента И, прямой выход второго Tpi rrepa сое- динен с вторыми входами первого и

второго элементов И и я-вляется вторым выходом вычислительного элемента третьего типа, выход первого элемента И является третьим выходом вычислительного элемента третьего типа, выход второго элемента И является выходом суммы вычислительного элемента третьего типа, кроме того, вычислительный элемент четвертого..

типа содержит триггер суммы, триггер переноса и полусумматор, причем тактовые входы триггера суммы и триггера переноса объединены и являются управляющим входом вычисли.тельного элемента четвертого типа, информационный вход триггера суммы является входом суммы вычислительного элемента четвертого типа, информационный вход триггера переноса является входом переноса вычислительного элемента четвертого типа, выход триггера суммы соединен с первым входом полусумматора, выход триггера переноса соединен с вторым входом полусумматора, выход суммы полусумматора является вьп:одом суммы вычислительного элемента четвертого типа, выход переноса является вькодом переноса вычислительного элемента четвертого типа, кроме того, вычислительный элемент пятого типа содержит первый и второй триггеры, триггер суммы, первый и второй элементы И и полусумматор, причем тактовые входы первого и второго триггеров, а также триггера суммы

объединены и являются управляющим входом вычислительного элемента пятого типа, информационные входы первого и второго триггеров и триггера суммы являются соответственно первым и вторым входами и входом суммы вычислительного элемента пятого типа, инверсный выход первого триггера соединен с первым входом первого элемента И, прямой выход второго триггера

соединен с вторым входом первого элемента И, с первым входом второго элемента И и является вторым вьгходом вычислительного элемента пятого типа, выход первого элемента И является третьим выходом вычислительного элемента пятого типа, прямой выход первого триггера соединен с вторым входом второго элемента И, выход второго элемента И соединен с первым входом полусумматора, прямой выход триггера суммы соединен с вторым входом полусумматора, выход суммы полусумь1атора

является выходом суммы вычислительното элемента пятого типа, выход переноса полусумматора является выходом переноса вычислительного элемента пятого типа, кроме того, вычислительньй элемент шестого типа содержит первьй и второй триггеры, триггер суммы, триггер переноса, первый и второй элементы И и одноразрядный сумматор, причем тактовые входы первого и второго триггеров, триггера суммы и триггера переноса объединены и являются управляющим входом вычислительного элемента шестого типа, информа, дионные входы первого и второго триггеров, триггера суммы и триггера переноса соединены соответственно с первым и вторым входами, входом суммы и входом переноса вычислительного элемента шестого типа, инверсньй выход первого триггера соединен с первым входом-первого элемента И, прямой выход второго триггера соединен с вторым входом первого элемента И, с первым входом второго элемента И и является вторым выходом вычислитель-

ного элемента шестого типа, выход первого элемента И является третьим выходом вычислительного элемента шестого типа, прямой выход первого триггера соединен с вторым входом второго элемента И, выход второго элемента И соединен с первым входом одноразрядного румматора, выходы триггера суммы и триггера переноса соединены со ответственно с вторым и третьим входами одноразрядного сумматора и являвдтся соответственно выходами суммы и переноса вычислительного элемента шестого типа, кроме того, вычислительный элемент седьмого типа содержит первый и второй триггеры,триггер суммы, первый элемент И и полусумматор, причем тактовые входы

11

1

первого и второго триггеров, триггера суммы объединены и являются управляющим входом вычислительного элемента седьмого типа, информационные входы первого и второго триггеров и триггера суммы являются соответственно первым и вторым входами и входом суммы вычислительного элемента седьмого типа, выходы первого и второго триггеров соединены соответственно с первым и вторым входами первого элемента И и являются соответственно первым и вторым выходами вычислительного элемента седьмого типа, выход элемента И соединен с первым входом полусумматора, выход триггера суммы соединен с вторым входом полусумматора, выходы cyMNfci и переноса полусумматора являются

соответственно выходами суммы и переноса вычислительного элемента седьмого типа, кроме того, вычислительный элемент восьмого типа содержит триггер суммы, триггер переноса, первый триггер и одноразрядный сумма.тор, причем тактовые входы триггера суммы, триггера переноса и первого триггера объединены и являются управляюп м входом вьиислительного элемента восьмого типа, информационные входы триггера суммы, триггера переноса и первого триггера являются соответственно входами суммы, переноса и третьим входом вычислительного элемента восьмого типа, выходы триггера суммы, триггера переноса и первого триггера соединены соответственно с первым, вторым и третьим вхо-; дами одноразрядного сумматора, выходы суммы и переноса однораз рядного сумматора являются выходами соответственно суммы и переноса вычислительного элемента восьмого типа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для одновременного вычисления двух многочленов | 1987 |

|

SU1439580A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММ ПРОИЗВЕДЕЩШ, содержащее матрицу вычислительных элементов, два триггера, три группы триггеров, группу одноразрядных сумматоров, причем тактовьй вход устройства соединен с тактовыми входами триггеров первой, второй и третьей, групп, тактовыми входами первого и второго триггеров, выходы триггеров первой группы соединены с первыми входами соответствующих одноразрядных сумматоров группы, выходы суммы и переносы которых соединены соответственно с информационными входами соответствующих триггеров второй и третьей групп, выход X-го триггера третьей группы (,2,. . . ,2n+log N , гдеМ - коли;чество пар операндов) соединен с вторым входом (х+1)-го одноразрядного сумматора группы, информационные входы первого и второго триггеров соединены соответсгвенно с знаковыми разрядами первойи второй входных шин, в матрице вычислительных элеrt, . fe,: /9 ... -- « -:/.. ментов вычислительные элементы,расположенные в 1, X строках J, -X столбцов (где , 3,...,n,j, 5,..., 2 3 i,j,-2,. если J, п i J 1, 2п j, +2, если Г1 ,2n-O , а также во второй строке п-го и (h-1)-го столбцов ( Г1 - разрядность, операндов), содержат каждый первый и второй триггеры, триггер суммы и триггер переноса, элемент И и одноразрядньй сумматор, причем информационные входы первого и второго триггеров, триггера суммы и триггера переноса являются соответственно первым, вторым входами, входом суммы и входом переноса вычислительного элемента, тактовые входы триггесл ров суммы,, переноса первого и второго триггеров соединены с управляющим входом вычислительного элемента, выходы первого и второго триггеров являются соответственно первым и вторым выходами вычислительного элемента и соединены соответственно с первым и вторым входами элемента И, а выход которого и выходы триггеров суммы и переноса соединены соответо ственно с входами с первого по третий одноразрядного сумматора, выхода суммы и переноса которого являются соответственно выходами суммы и переноса вычислительного элемента, который является вычислительным элементом первого типа, причем первьш и BTOpofi выходы, выход суммы и выход переноса вычислительного элемента первого типа (, -и строки j; -го столбца матрицы вычислительных элементов соелпнены соответственно с перрым входом вычислительного элемента (i, +1)-й стро

Изобретение относится к цифровой .вычислительной технике и может быть использовано при построении специализированных вычислительных систем.

Известно устройство для вычисления сумм произведений, содержащее

матрицу модулей, два регистра, накапливакнций сумматор, блок анализа lJ .

Недостатком данного устройства является относительно невысокая производительность при вычислении мно.гих сумм произведений, которая является следствием наличия холостых тактов, необходимых, чтобы закончить вычисление суммы произведений перед подачей операндов, относящихся к сле дующей сумме произведений. Наиболее близким по технической сущностИ к изобретению является устройство для вычисления сумм произведений, содержащее матрицу вычислител ных элементов, которая содержит (п+ +1) строк, первые три строки имеют (2п+1) вычислительных элементов, каж дая последующая строка.матрицы имеет на один вычислительный элемент меньше, последняя строка содержит (п+3) вычислительных элементов, (п+1)-разрядные первый и второй регистры one- ранда, первую и вторую группу элементов И-НЕ, накапливакнций сумматор, первый, второй и третий триггеры,при чем первая входная шина соединена с. информационными входами первого регистра операнда, вторая входная шина соединена с информационными входами второго регистра операнда, выходы значащих разрядов первого регистра операнда и второго регистра операнда соответственно соединены с первыми входйми элементов И-НЕ первой и второй групп, вторые входы элементов Ипервой группы соединены с выходом знакового разряда второго регистра операнда, вторые входы элементов И-Н второй группы соединены с вьгходом знакового разряда первого регистра операнда, первые и вторые информаци онные входы накапливающего сумматора соответственно соединены с Сп+2) младшими входами и с (п+2) старшими выходами вычислительных элементов последней строки матрицы, первый управляклций вход накапливающего сумматора подключен к шине установки в выходы накапливающего сумматора соединены с выходной шиной уст- pofjcTBa, ишна тактовых импульсов соединена с вторым управляницим входо накапливающего сумматора, с управляющим входом каждого вычислительного элемента матрицы, с управляющими входами первого и второго регистров операнда, первый и второй выходы (i,j)-ro (,...,п; ,...,2n) сое динены соответственно с первым входо (i+1, j-1)-ro вычислительного элемен та и вторым входом (i+1, j+1)-ro вычисл.ительного элемента, а выходы поразрядной суммы и переноса соотв т ственно с входим поразрядной суммы (i+1, j)rro вычислительного элемента и входом переноса (i+1, j-1)-ro вычислительного элемента, первый выход (1,1)-го вычислительного элемента соединен с- вторьм входом (1+1,1)го вычислительного элемента, а -выход поразрядной суммы - с входом поразрядной суммы (i+1,2п+1)-го вычислительного элемента,, выход переноса (i, 2п-1)-го вычислительногоэлемента соединен с входом переноса (i+1, 2п+1)-го вычислительного элемента (,2) вход переноса (2п+1)-го вычислительного элемента второй и третий строк матрицы соединены соответственно с выходами первого и второго триггеров, информационный вход которого соединен с выходом третьего триггера, управляющие входы триггеров подключены к тактовой шине, первые и вторые входы вычислительных элементов нечетных столбцов первой строки матрицы поразрядно соединены с выходами второго и первого регистров операнда, первые и вторые входы вычислительных элементов четных столбцов первой строки матри1р 1 соединены соответственно с младшими выходами первого регистра операнда и старшими выходами второго регистра операнда, входы поразрядной суммы и переноса вычислительных элементов с первого по п-й первой строки матршфл соединены соответственно с выходами элементов И-НЕ второй группы и с выходами элементов И-НЕ первой группы, входы поразрядной суммы и переноса остальных вычислительных элементов первой строки матрицы соединены соответственно с выходами знаковых разрядов первого и второго регистров операндов, которые соответ-ственно соединены с входами первого и третьего триггеров. Вычислительный элемент содержит полусумматор, элемент п, два триггера, триггера переноса и поразряд- ной суммы, причем тактовые входы всех триггеров соединены с управляющим входом вычислительного элемента, информационные входы первого и второго триггеров триггера поразрядной суммы и триггера переноса являются соответственно первым и вторым входамиi входами поразрядной суммы и переноса вычислительного элемента, выход первого триггера соединен с 51 первым входом- элемента И и является /первым вьгходом вычисли ельного элемента, выход второго триггера соединен с вторым входом элемента И и является вторым выходом вычислительног элемента, выход элемента И,выходы триггеров поразрядной суммы и перено са .соединены соответственно с входами полусумматора, выходы которых являются соответственно выходами переноса и поразрядной суммы вычислитель ного элемента 12J . Недостатком известного устройства является низкая производительность, обусловлейная наличием холостых так.тов, в течение которых на.входы устройства должны поступать ну:;1евыё зна чения сомножителей. Цель изобретения - повьш1ение лронзводительности. Поставленная цель достигается тем, что в устройство для вычисления произведений, содержащее матрицу вычислительных элементов, два Триггера, три группы триггеров, груп пу одноразрядных сумматоров, причем тактовый вход устройства соединен с тактовыми входами триггеров первой, второй и третьей групп, тактовыми входами первого и второго триггеров, выходы триггеров первой группы соеди нены с первыми входами соответствующих одноразрядных сумматоров группы, выходы суммы и переноса которых соединены соответственно с информационными входами соответствующих триггеров второй и третьей групп, выход х-ого триггера третьей группы (, 2,.,.,2n+logjN; где N - количество .пар операндов) соединен с вторым входом (х+1)-го одноразрядного сумматора группы, информационные входы первого и второго триггеров соединены соответственно с знаковыми разрядами первой и второй входных шин, в матрице вычислительных элементов вычислительные элементы, расположенные в строках j -X столбцов (где i, 3.,...,п; ,..l,2n-1; 3ii,fcji -2, если j,6n + 2; i,2n-j +2, если п + ,2n О, а также во второй строке п-го и (п.-1) го столбцов (п - разрядность операндов) , содержат каждьй первый и второй триггеры, триггер суммы и триг.гер переноса, элемент И и одноразрядный сумматор, причем информационные входы первого и второго тригге16ров, триггера суммы и триггера переноса являются соответственно первым, вторым входами, входом суммы.и входом переноса вычислительного элемента, тактовые входы триггеров суммы, переноса первого и второго триггеров соединены с управляюпсим входом вычислительного элемента, выходы первого и второго триггеров являются соответственно первым и вторым выходами вычислительного элемента и соединены соответственно с первым и вторым входами элемента И, выход которого и выходы триггеров суммы и переноса соединены соответственно с входами с первого по третий одноразрядного сумматора, выходы суммы и переноса которого являются соответственно выходами суммы и переноса вычислительного элемента, которьй является вычислительным элементом первого типа, причем первьй и второй выходы,выход суммы и выход переноса вычислительного элемента первого типа ij-й строчки j. -столбца матрицы вычислительных элементов соединены соответственно с первым входом вычислительного элемента (1, 1)-й строки (jj-1)го столбца, с вторым входом вычислительного элемента (1-(+1)-й строки (j,+1)-ro столбца, с входом суммы вычислительного элемента ()-и .строки j,-ro столбца и с входом переноса вычислительного элемента (if+ +1)-й строки ()-ro столбца матрицы, содержит полусумматор, два сдвигающих регистра и группу элементов И, в матрице вычислительных элементов вычислительные элементы, расположенные в первой строке столбцов (где J2 - 2П+1), а также в первой строке первого столбца, являются вычислительными элементами второго типа, вычислительный элемент, расположенньш в первой строке второго столбца, является вычислительным элементом третьего типа, вычислительные элементы, распо.ложенные в строках j -х столбцов (где ,52п+1), j.,b2,.., ,..,п-1; j i-3, если и j 2n+2-i , если n+2 i ), a также во второй строке первого столб ца, являются вычислительными элементами четвертого типа, вычислительные элементы, расположенные во второй строке второго и третьего столбцов, являются вычислительными элементами

пятого типа, вычислительные элементы, расположенные в (ig+2)-x строках (i + 2)-л столЬцов (где 1 1,2,.. ....,п-2), а также в (i,+2)-x строках (i,+3)-x столбцов, являются вычис- 5 лительнымн элементаьш шестого типа, вычислительные элементы, расположенные во второй строке j-,x столбцов (где ,6, ,. . ,2п, j.,n-1,n), являются вычислительными элементами О седьмого типа, вычислительные элементы, расположенные в (ig + 1)-X

строках ie X столбцов (где i.,2,3,. ,.. ,п) , а также в (jg--2)-X строках jg-X столбцов (где jg 1,2,., . ,п) , 15 являются вычислительными элементами восьмого типа, причем знаковый разряд первой входной шины соединен с вторым входом вычислительного элемента второго типа первой строки и 20 первого столбца, первый значащий разряд первой входной шины соединен с ..

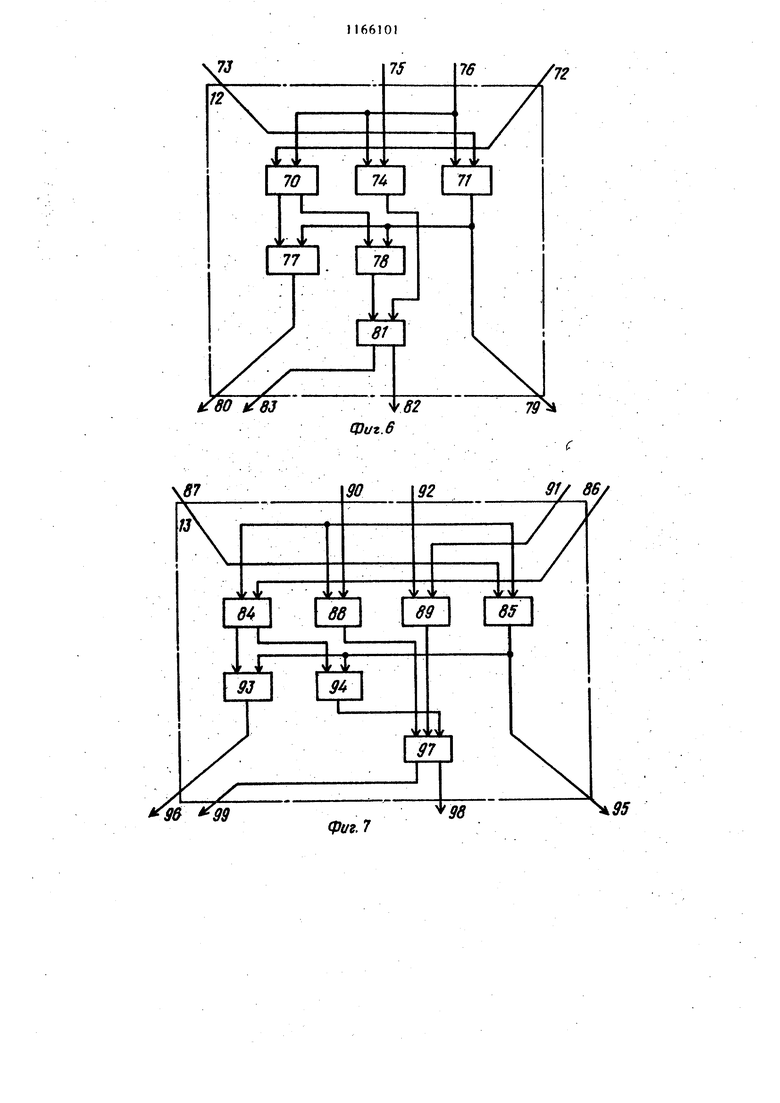

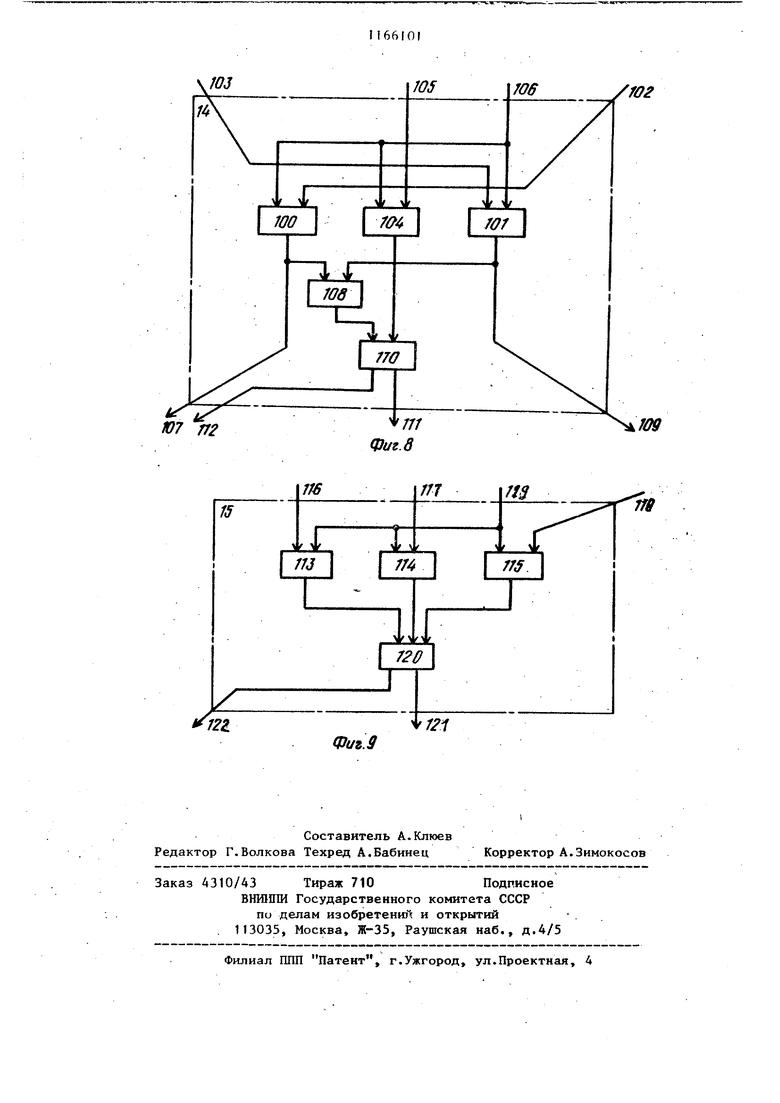

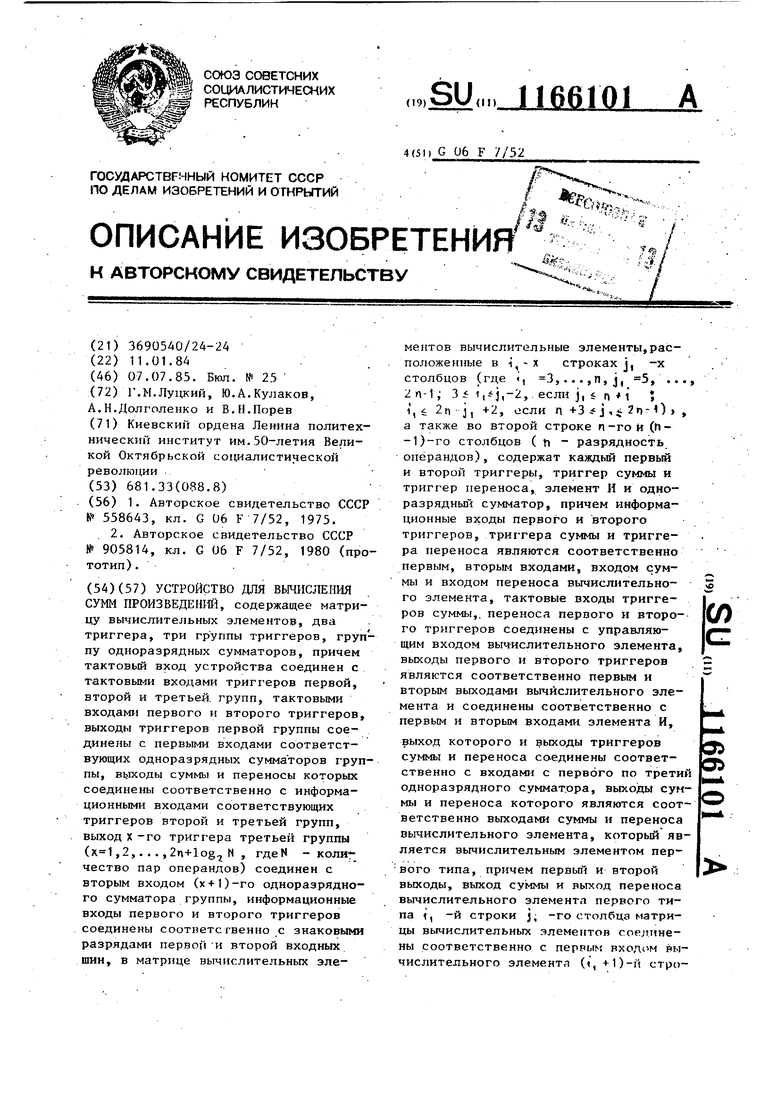

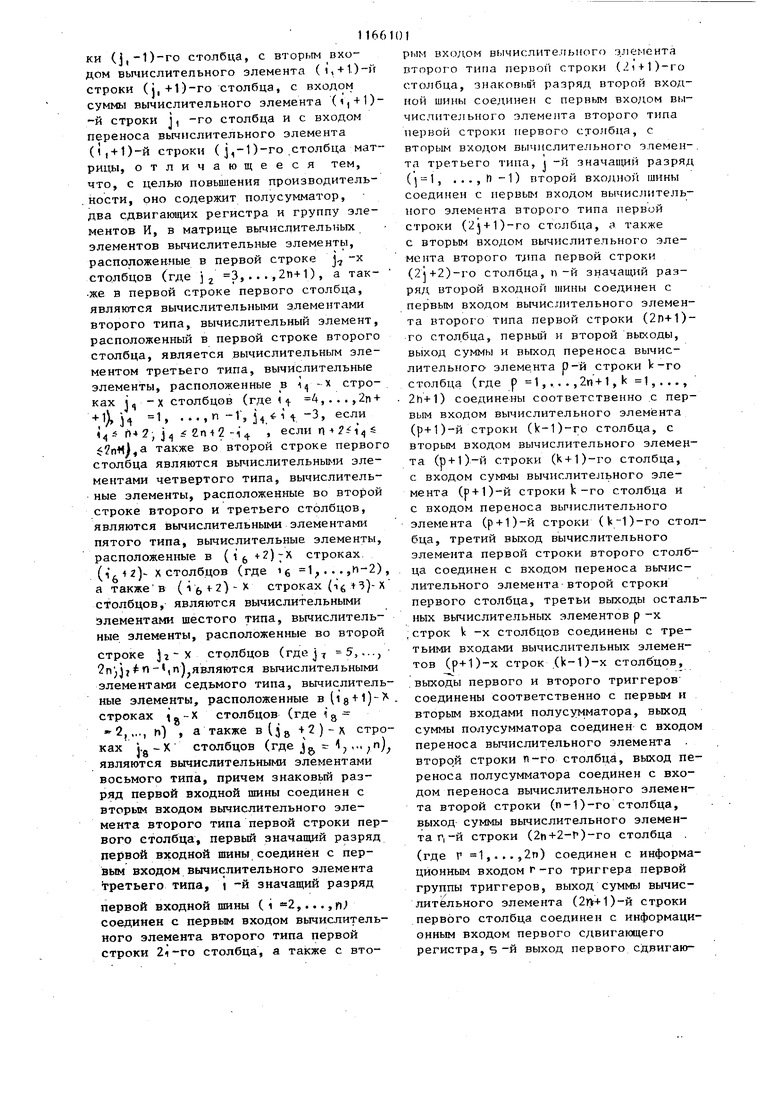

первым входом вычислительного элемента третьего типа, i-й значащий разряд первой входной шины (,3,..., 25 п) соединен с первым входом вычислитепьного элемента второго типа первой строки (2i)-ro столбца, а также с вторым входом вычислительного элемента второго типа первой строки 30 (21+1)-го столбца, знаковый разряд

второй, входной шины соединен с первым входом вычислительного элемента второго типа первой строки первого столбца, с вторым входом вычисли- jj тельного элемента третьего типа, j-й значащий, разряд (j 1,2,...,п-1) второй входной шины соединен с первым входом вычислительного элемента второго типа первой строки (2j+1)-ro Q столбца, а также с вторым входом вычислительного элемента второго типа первой строки (2j+2)-ro столбца, п-й значащий разряд второй входной шины соединен с первым входом вычисли- j тельного элемента второго типа первой строки (2п+1)-го столбца, первый

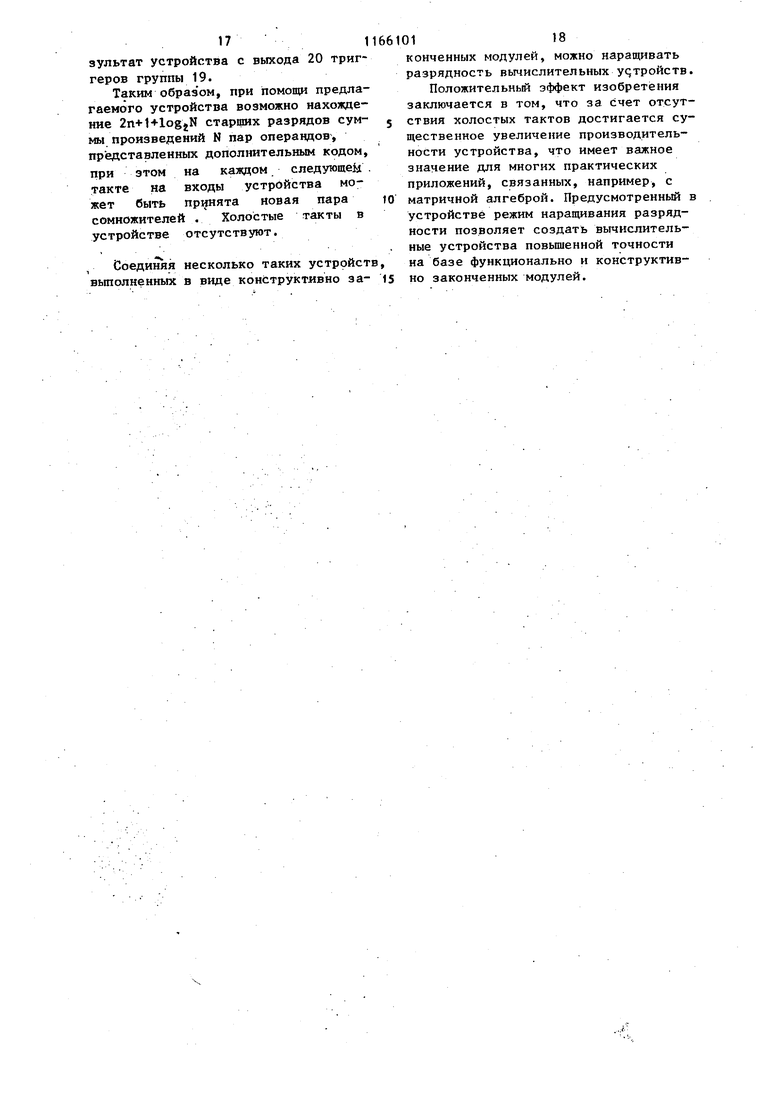

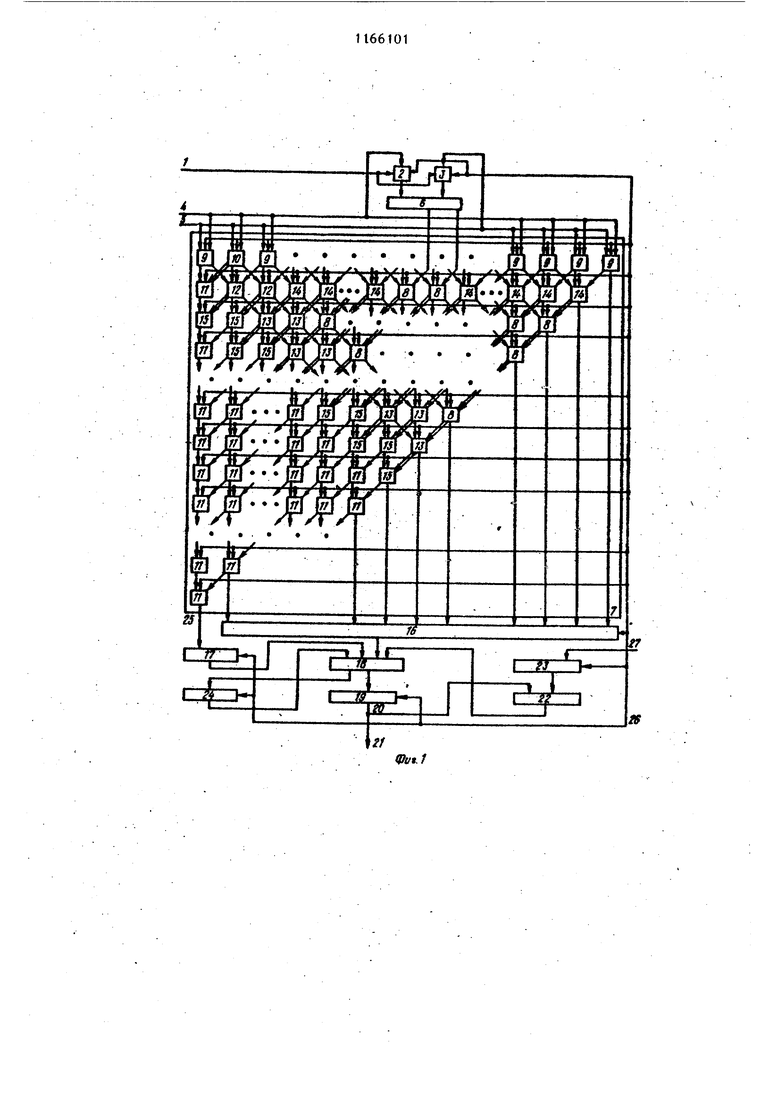

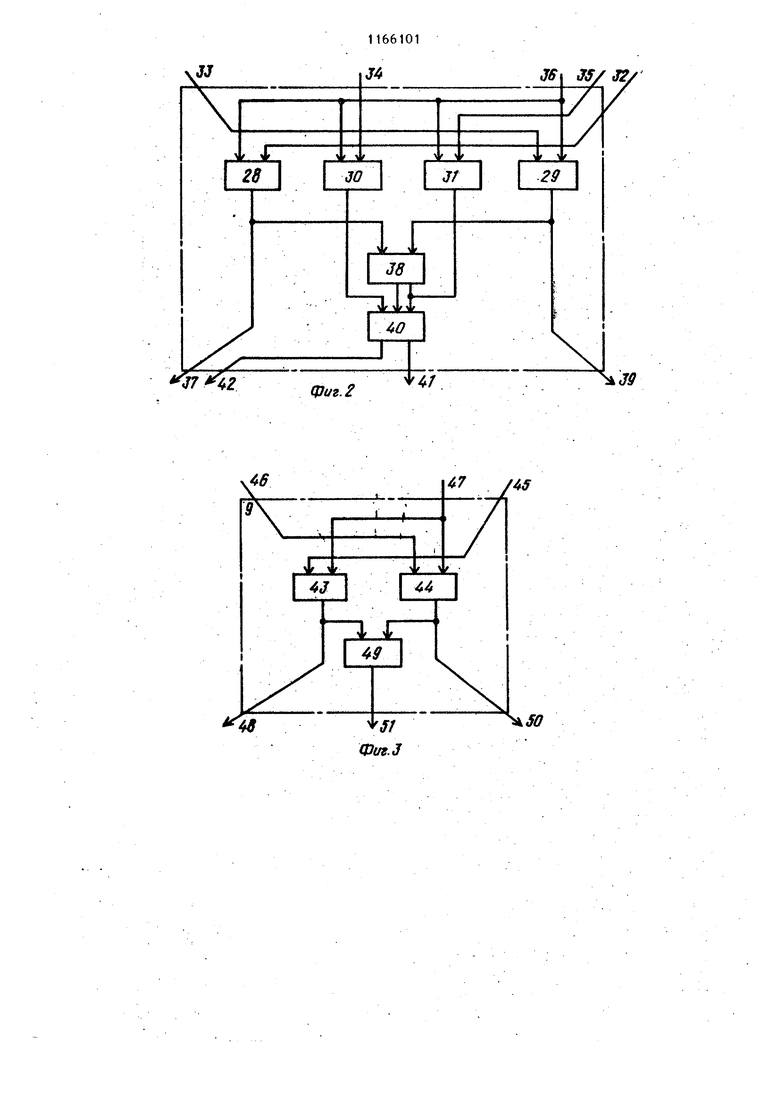

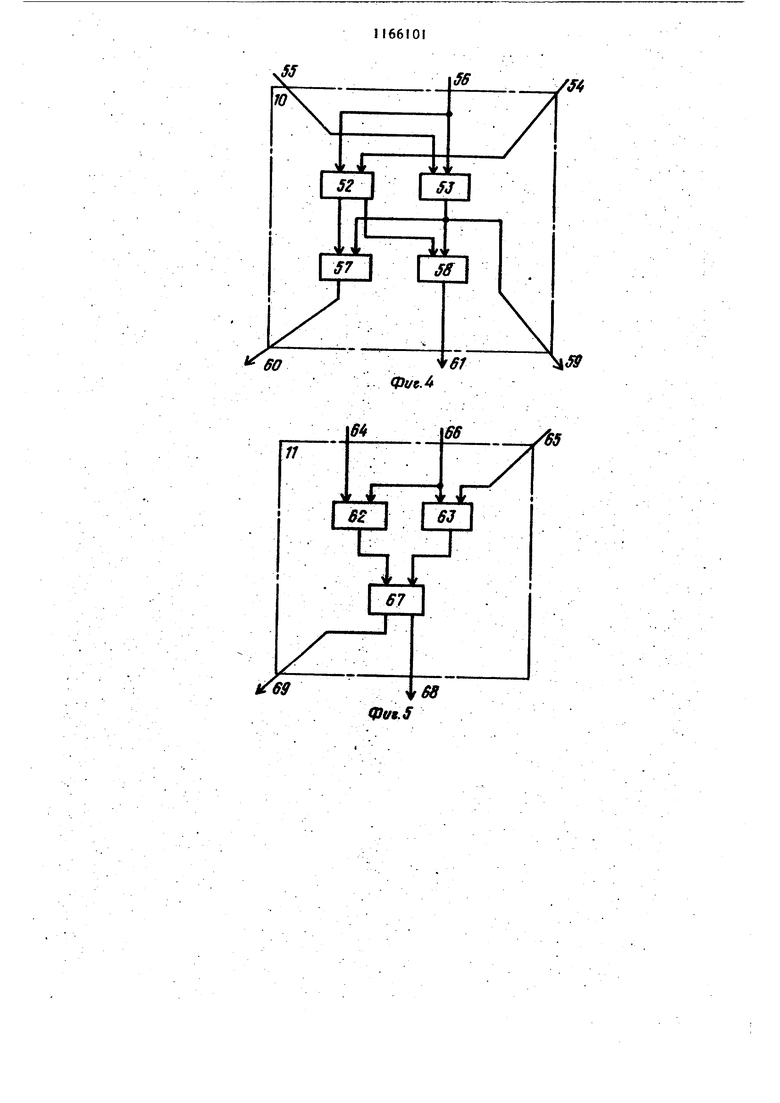

и второй выходы, выход суммы и выход переноса вычислительного элемента р-й строкиk-го столбца (где ,2,. .50 ...,2п+1; ,2,...,2п+1) соединены соответственно с первым входом вычислительного элемента (р+1)-й строки (k-1)-го столбца, с вторым входом вы числительного элемента (р+1)-й стро- 55 ки (k+1)-ro столбца с входом суммы вычислительного элемента (р+1)-й : строки k -го столбца и с входом переноса вычислительного элемента (р+1)-й строки (k-l)-ro столбца, третий выход вычислительного элемента первой стро- ки второго столбца соединен с входом переноса вычислительного элемента второй строки первого столбца, третьи выходы остальных вычислительных элементов р-х строк k -X столбцов соединены с третьими входами вычислительных элементов (р+1)-х строк (V-I)-X столбцов, выходы первого и второго триггеров соединены соответственно с первым и вторым входами полусумматора, выход суммы полусумматора соединен с входом переноса вычислительного элемента второй строки п-го столбца, выход переноса полусумматора соединен с входом переноса вычислительного элемента второй строки (n-l)-ro столбца, вьгход суммы вычислительного элемента г-й строки (2п+2-г)-го столбца (где ,2,,..,2п) соединен с информационным входом г-го триггера первой группы триггеров, выход суммы вычислительного элемента (2п+1)-й строки первого столбца соединен с информационным входом первого сдвигающего регистра, S -и вьгход первого сдвиганлцего регистра (,2,..., 1 + +logjN) соединен с первым входом (з+2п)-го одноразрядного сумматора группы, выходы триггеров второй группы соединены с первыми входами соответствукяцих эл.ементов И группы, выходы второго сдвигающего регистра соединены-с вторыми входами соответствующих элементов И группы, выходы элементов И группы соединены с третьими входами соответствующих одноразрядных сумматоров группы, тактовьА вход устройства соединен с тактовыми входами первого и второго сдвигающих регистров и с управляющими входами всех вычислительных элементов матлицы, вход установки устройства соединен с входами установки в О первого и второго триггеров, вход вьщачи результата устройства соединен с информационным входом второго сдвигающего регистра, выходы триггеров второй группы являются выходом результата устройства, кроме того, вычисли- . тельный элемент второго типа содержит первый, второй триггеры и элемент И, Причем тактовые входы первого и второго триггеров объединены и являются управляннцим входом вьпшслительного элемента второго типа, информационные входы первого и второго триггеров являются соответственно первым и вторым входами вьмислительного элемента второго типа, выходы первого и второго триггеров соединены соответственно с первым и вторым входами элемента И и являются соответственно первым и вторым выходами вьгчислитель элемента И является выходом суммы вычислительного элемента второго типа j кроме того, вычислительньш элемент третьего типа содер кит первый и второй триггеры, первый и второй элементы И, причем тактовые входы первого и второго триггеров объединены и являются управляющим входом вычислительного элемента третьего типа, информационные входы первого и второго триггеров являются соответственно первым и вторым входами вычислительного элемента третьего типа, инверсный выход первого триггера соединен с первым входом первого элемента И, прямой выход первого триггера соединен с первым входом второго элемента И, прямой выход второго триггера соединен с вторыми входами первого и второго элементов и является вторым выходом вычислительного элемента третьего типа, выход первого элемента И явлйется третьим выходом вычислительного элемента третьего типа, выход второго элемента И является выходом суммы вычислительного элемента третьего типа кроме того, вычислительный элемент четвертого типа содержит триггер сум мы, триггер переноса и полусумматор причем тактовые входы триггера суммы и триггера переноса объединены и являются управляющим входом вычислительного элемента четвертого типа, информационный .вход триггера суммы является входом суммы -вычислительно го элемента четвертого типа, информационный вход триггера переноса является входом переноса вычислительного элемента четвертого типа, ВБпсод триггера суммы соединен с пер вым входом полусумматора, выход три гера переноса соединен с вторым вхо дом полусумматора, выход суммы полу сумматора является выходом суммы вы числительногр элемента четвертого т па, выход переноса является выходом переноса вычислительного элемента четвертого типа, кроме того, вычисл 1 110 тельный элемент пятого типа содержит первый и второй триггеры, триггер суммы, первый и второй элементы И и полусумматор, причем тактовые входы первого и второго триггеров, а также триггера суммы объединены и являются управляющим входом вычислительного элемента пятого типа, информационг{ые входы первого и второго триг- геров и триггера суммы являются соответственно первым, и вторым входами и входом вычислительного элемента пятого ,типа, инверсный выход первого триггера соединен с первым входом первого элемента И, прямой выход второго триггера соединен с вторым входом первого элемента И, с первым входом второго элемента И и является вторым выходом вычислительного элемента пятого типа, выход первого элемента И является третьим выходом вычислительного элемента пятого типа, прямой выход .первого триггера соединен с вторым входом второго элемента И, выход второго элемента И соединен с первым входом полусумматора, прямой выход триггера суммы соединен с вторым входом полусумматора, выход суммы полусумматора,является выходом суммы вычислительного элемента пятого типа, выход переноса полусумматора является выходом переноса вычислительного элемента пятого типа, кроме того, вычислительньй элемент шестого типа содержит первый и второй триггеры, триггер суммы, триггер переноса, первый и второй элементы И и одноразрядный сумматор, причем тактовые входы первого и второго триггеров, триггера суммы и триггера переноса объединены и являются управляютщим входом вычислительного элемента шестого типа, информационные входы первого и второго триггеров, триггера суммы и триггера переноса соединены соответственно с первым и вторым . входами, входом суммы и входом переноса вычислительного элемента шестого типа, инверсный выход первого триггера соединен с первым.входом первого элемента И, прямой выход второго триггера соединен с вторым входом первого элемента И, с первым входом второго элемента И и является вторым выходом вычислительного элемента шестого типа, выход первого элемента И является третьим выходом вычислительного элемента шестого типа,. 11 прямой выход первого триггера соединен с вторым входом второго элемента И, выход второго элемента И сое(Динен с первым входом одноразрядног сумматора, выходы триггера суммы и триггера переноса соединены соответственно с вторым и третьим входами одноразрядного сумматора и являются соответственно выходами суммы и переноса вычислительного элемента шеетого типа, кроме того, вычислительный элемент седьмого типа содержит первьй и второй триггеры, триггер суммы, первый э лемент И и полусумматор, причем тактовые входы первого и второго триггеров, триггера суммы объединены и являются управляющим входом вычислительного элемента седьмого типа, информационные входы первого и второго триггеров и триггера- суммы являются соответствен но первым и вторьм входами и входом суммы вычислительного элемента седьмого типа, выходы первого и второго {триггеров соединены соответственно с первым и вторым входами первого элемента И и являются соответственно первым и вторым выходами вычислитель ного элемента седьмого типа, выход элемента И соединен с первым входом полусумматора, выход триггера ,суммы соединен с вторым входом полусуммато ра, выходы суммы и переноса полусумматора являются соответственно выходами суммы и переноса вычислительного элемента седьмого типа, кроме того, вычислительный элемент, восьмого типа содержит триггер суммы, триггер переноса, первьй триггер и одноразрядный сумматор, причем тактовые вхо ды триггера суммы, триггера переноса и первого триггера объединены и явля ются управляющим входом вычислительного элемента восьмого типа, информа ционные входы триггера суммы, триггера переноса и первого триггера являются соответственно входами суммы, переноса и третьим входом вычислительного элемента восьмого типа, выходы триггера суммы, триггера переноса и первого триггера соединены соответственно с первым, вторым и третьим входами одноразрядного сумматора, выходы суммы и переноса одноразрядного сумматора являются выходами соответственно суммы и переноса вычислительного элемента восьмого типа. 01,12 На фиг.1 представлена структурная схема устройства для вычисления сумм произведений} на фиг.2 - схема вычислительного элемента первого типа; на фиг.З - то же, второго типа на фиг.4 - то же, третьего типа;на фиг.З - то же, четвертого типа; на фиг.6 - то же, пятого типа-,- на фиг.7то же, шестого типа; на фиг.8 - то же, седьмого типа; на фиг.9 - то же, восьмого типа.. Устройство для вычисления сумм произведений содержит (фиг.1) вход 1 установки 3, который, соединен с входами установки в О триггеров 2 и 3, выходы знаковых разрядов первой и второй входных шин 4 и 5 соединены с информационными входами триггеров 2 и 3, выходы триггеров 2 и 3 соединены с входами полусумматора 6. Матриц цу 7 вычислительных элементов, содержащую 2п+1 строк, первая строка которой имеет 2п+1, вычислительных элементов, а каждая последующая - на один вычислительный элемент меньше; вычислительные элементы 8-15 матрицы, первую группу 16 триггеров, первый сдвигающий регистр 17, группу 18 одноразрядных сумматоров, вторую .группу 19 триггеров, выходы 20 второй группы триггеров, выход 21 результата устройства, группу 22 элементов И, второй сдвигающий регистр 23, третью группу 24 триггеров, выход знака 25 матрицы 7 вычислительных элементов, тактовьй вход 26 устройства, вход 27 выдачи результата устройства. В вычислительном элементе первого типа 8 (фиг.2) информационные входы первого, Еторого триггеров 28 и 29, триггеры суммы 30 и переноса 31 являются соответственно первым, вторым входами 32 и 33, входом суммы 34, и переноса 35 вычислительного элемента 8. Тактовые входы триггеров 28-31 объединены и являются управляющими входами 36 вычислительного элемента 8. Выхрд триггера 28 является первым выходом 37 вычислительного элемента и соединен с первым входом лемента И 38, выход триггера 29 вляется вторым выходом 39 вычислиельного элемента 8 и соединен с торым входом элемента -И 38, выход риггеров 30 и 31, а также элемена И 38 соединены соответственно с ервым, вторым и третьим входами одоразрядного сумматора 40. Выходы суммы и переноса одноразрядного сумматора 40 являются выходами суммы 41 и переноса 42, вьиислительного элемент. 8. В вычислительном элементе второго :типа 9 (фиг.З) информационные входы первого и второго триггеров 43 и 44 являются первым 45 и вторьм 46 входами вычислительного элемента 9. Так товые входы триггеров 43 и 44 объеди йены и являются управляющим входом 47 вычислительного элемента. Выход первого триггера 43 является первым выходом 48 вычислительного элемента 9 и соединен с первым входом элемента И 49, выход второго триггера 44 является вторым выходом 50 вьгчислительного элемента 9 и соединен с вто рым входом элемента И 49, выход элемента И 49 является выходом 51 суммы вычислительного элемента 9. В вычислительном элементе третьего типа 10 (фиг.4) информационные входы первого и второго триггеров 52 и 53 являются первым 54 и вторым 55 входами вычислительного элемента 10. Тактовые входы триггеров 52 и 53 объединены и являются управляю.щим входом 56 вычислительного элемента 10. Инверсный выход триггера 52 соединён с первым входом элемента И 57, прямой выход триггера 52 соединен с первым входом элемента И 58, прямой вьпсод триггера 53 соединен с вторыми входами элементов И 57 и 58 и является вторым выходом 59 вычислительного элемента 10, выход элемента И 57 является третьим выходом 60 вычислительного элемента 10, выход элемента-И 58 является выходом суммы 61 вычислительного элемента 10. В вычислительном элементе четвертого типа 11. (фиг.5) информационные входы -триггера суммы 62 и переноса 63 являются входами суммы 64 и пере носа 65 вычислительного элемента 11 Тактовые входы триггеров 62 и бЗ.объ - единены и являются угфавляющими вхо дом 66 вычислительного элемента 11. Выходы триггеров 62 и 63 соединены с пербьм и вторым входами полусумма тора 67, выход суммы полусумматора 67 является вькрдом суммы 68 вычислительного элемента 11, выход переноса 69 вычислительного элемента 11 В вычислительном элементе пятого типа 12 (фиг.6) информационные входы первого и второго триггеров 70 и 71 являются первым входом 72 и вторым входом 73 вычислительного элемента 12, информационный вход триггера 74 суммы является входом суммы 75 вычислительногоэлемента 12. Тактовые входы три1-геров 70, 71 я 74 объединены и являются управляющим входом 76 вычислительного элемента 12. Инверсный выход триггера 70 сое-динен с первым входом элемента И 77, прямой выход триггера 70 соединен с первым входом элемента И 78, прямой выход триггера 71 соединен с вторыми входами элементов И 77 и 78 и являются вторым выходом 79 вычислительного элемента 12, выход элемента И 77 . является третьим выходом 80 вычислительного элемента 12, выход триггера 74 и выход элемента И 78 соединены с первым и вторым входами полусумматора 81, выходы суммы и переноса полусумматорв 81 являются соответственно выходом суммы 82 и выходом переноса 83 вычислительного элемента 12.. В вычислительном элементе шестого типа 13 (фиг.7) информационные входы первого и второго триггеров 84 и 85 являются первым входом 86 и вторым входом 87 вычислительного элемента, информационные входы триггеров суммы и переноса 88 и 89 являются входом суммы 90 и переноса 91 вычрслительного элемента 13. Тактовые входы триггеров .84, 85, 88 и 89 объе-динены и являются управляющим входом 92 вычислительного элемента 13. Инверсный выход триггера 84 соединен с первьш входомэлемента И 93, п1рямой выход триггера 84 соединен с первым входом элемента И 94, а прямой выход триггера 85 соединен с вторыми входа-. ми элементов И, 93 и 94 и является вторым выходом 95 вычислительного элемента 13, выход элемента И 93 является третьим выходом 96 вычислительного элемента 13, выходы триггеров 88 и 89, а также элемента И 94 соединены с первым, вторым и третьим входами одноразрядного сумматора 97, выходы сушш и переноса одноразрядного сумматора 97 являются выходом 98 суммы и переноса 99| вычислительного, элемента 13. В вычислительном элементе седьмого типа 14 (фиг.8) информационные входы первого и второго триггеров 100 и 101 являются первым входом 102 и вторым входом 103 вычислительного элемента 14, вход триггера 104 суммы, является входом 105 суммы вычислитель ного элемента 14, тактовые входы триггеров 100, 101 и 104.объединены и являются управляющим входом 106 вычислительного элемента 14. Выход триг гера 100 является первым выходом 107 вычислительного элемента 14 и соединей с первым входомэлемента И 108, выход триггера 101 является вторьм выходом 109 вычислительного элемента 14 и соединен с вторым входом элемента И 108, выход триггера 104 и вьгход элемента И 108 соединены с первым и вторым входами полусумматора 110, выходы суммы и переноса полусумматора 110 являются, выходом суммы 111 и переноса 112 вычислительного элемента 14. Б вычислительном элементе восьмого типа 15 (фиг.9) информационные входы триггеров переноса 113, суммы 114 и первого триггера 115 являются входами переноса 116, 117 и третьим вхо дом 118 вычислительного элемента 15, тактовые входы триггеров 113-115 объединены и являются управляющим входом 119 вычислительного элемента 15 Вы- 30 ходы триггеров 113, 114 и 115 соединены с первым, вторым и третьим входами одноразрядного сумматора 120. Выходы суммы и переноса одноразрядно го сумматора 120 являются выходом суммы 121 и выходом переноса 122 вычислительного элемента 15. Устройство работает следующим образом. В первом такте на входы триггеров 2 и 3 вычислительных элементов 9 и 10 первой строки принимается первая пара сомножителей, представленная до полнительным кодом, .причем в триггеры 43 вычислительных элементов 9 и ,триггер 52 вычислительного элемента 10 записывается код , а в триггеры 44 элементов 9и триггер 53 элемента 10 записывается код , , ..., Ь,.,а, где во и bjj - знаковые разряды а, а,... а,Ь, , Ь, ..., Ь значащие разряды операндов, в триггеры 2 и 3 записывается соответственно а,, и Ьд. В матрице 7 вычислительных элемен тов умножение производится путем умножения дополнительных кодов и прибавления поправки 1 101 If А. ГАи, IB .2а, .2Ь„ -А . + (ао+Ьо ) , где .; и операнды в до- г- т. г т полнительных кодах,-AJ и L-BJ ок - - -jo|c поразрядная инверсия операндов в дополнительных кодах. Умножение производится путем сдви, влега величины b , а b, , во по цепям первых входов и первых выходов вычислительных элементов сдвига величины , Ь, ,... ,Ь| ,а вправо по цепям вторых входов и вторых выходов вычислительных элементов и одновременного суммирования поразрядных коньюнкций. Величины 2а. f-B, 2Ь„ -Л о L -JOK -O L JoK нормируются в элементах 10-13, расположенных по диагонали матрицы вычислительньгх элементов 7. Поразрядные к ньюнк- ции Ъ а, ,... ,Ьоа„, адЬ, ,... ,, .передаются-по цепям третьих входов и третьих выходов вычислительных элементов. Величина ( ) игд , формируется путем записи содержимого полусумматоа 6 в элементы второй строки, причем перенос записывается в (п-1)-й столбец, а сумма - в п-й столбец, () разрядное произведение форми- руется в матрице 7 вычислительных элементов следующим образом; на втором такте формируется 2п-й младший значащий разряд произведения, на третьем - (2п-1)-й на четвертом (2п-2)-й,-и так далее, на (2п+1)-м такте формируется старший значащий разряд, на (2п+2)-м такте формиру-; ется знаковый разряд, причем для каждого выхода на следуницем такте появляется результат, соответствующий новой паре сомножителей. Знаковый разряд дополнительного кода произведения подается на информационный вход сдвигающего регистра 17, а значащие разряды - на входы группы 16; триггеров. Элементы 16-19,23 и 24 образуют конвейерный накапливающий сумматор. По мере готовности результатов на вход сдвигающего регистра 23 по шине 27 подается в течение одного такта уровень логического нуля. Ноль сдвигается в регистре 23, обеспечивая последовательное отключение обратной связи сумматора для всех его одноразрядных сумматоров 18, начиная с младших разрядов. Сумма произведений подается на выход 21 ре171166

зультат устройства с выхода 20 триггеров группы 19.

Таким образом, при помощи предлагаемого устройства возможно нахождение 2n+HlogjN старших разрядов сум- j мы произведений N пар операндов, представленных дополнительным кодом, при этом на каждом следующей такте на входы устройства может быть npijHHTa новая пара ю сомножителей . Холостые такты в устройстве отсутствуют.

Соединяя несколько таких устройств, выполненных в виде конструктивно за- is

118

конченных модулей, можно наращивать разрядность вычислительных устройств.

Положительный эффект изобретения заключается в том, что за. счет отсутствия холостых тактов достигается существенное увеличение производительности устройства, что имеет важное значение для многих практических приложений, связанных, например, с матричной алгеброй. Предусмотренный в устройстве режим наращивания разрядности позволяет создать вычислительные устройства повышенной точности на базе функционально и конструктивно законченных модулей.

Ц)иг.2

.46

JS

4f

47 /4

W 1 r

I 4J

f f

ЧЛ7

Л ФигЗ

Л

фуе.4

S7

/Г

// ffff

ID

95

98

15

1/122.

Фиг.З

т

т

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения производных бензодиазепина | 1971 |

|

SU558643A3 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-07—Публикация

1984-01-11—Подача