модулю два /-ГО блока суммирования соединен с выходом элемента И (n-2-m)-го одноразрядного конмутатр-; ра (, ) 9 вторые входы сумматоров по модулю два j-ro блока суммирования соединены с выходом элемента И J-ro одноразрядного коммутатора, выходы элементов И t-x одноразрядных коммутаторов (l,n-l) являются соответственно выходами старших разрядов результата вычисления квадратного корня устройства, выход п-го разряда результата, вычисления квадратного корня которого является выходом переноса дополнительного сумматора (n-l)-ro блока суммирования, первый и второй входы элемента ИЛИ j-ro одноразрядного ком мутатора соединены соответственно с выходами переносов (j+3)-разрядного дополнительного сумматора (j-O-ro блока суммирования и (h+2)разрядного сумматора j-ro блока суммирования, входы элемента ИЛИ первог одноразрядного коммутатора соединены с выходом старшего разряда и с выходом переноса (п+2)-разрядного сумматора первого блока суммирования, выходы старших разрядов дополнительных сумматоров являются соответственно старШиьи разрядными выходами резуль14 тата вычисления произведения двух величин устройства, младшими разрядными выходами р езультата вычисления произведения двух величин которого являются соответственно выходы дополнительного сумматора (n-l)-ro блока суммирования, разрядные выходы с второго по |(п-Г:)-й разряд дополнительного сумматора и разрядные выходы с п по (п+2)-й разряд ( h+2)-разрядного сумматора первого блока сум мирования соединены с первыми входс1ми соответствующих разрядов (п+2)-разрядного сумматора второго блока суммирования, разрядные выходы дополнительного сумматора j-ro блока суммирования соединены соответственно с входами первого операнда (п+2)-разрядного сумматора (j+1)го блока суммирования, разрядные входы второго операнда ()-разрядных сумматоров J-X блоков суммирования соединены соответственно с выходами элементов И j-й группы, первые входы элементов И с первого по п-й всех групп соединены соответственно с разрядными входами первого операнда устройства, вторые входы элементов И каждой группы объединены и соединены соответственно с разрядными входами второго операнда устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Вычислительное устройство | 1981 |

|

SU1086426A1 |

| Устройство для суммирования нескольких Р-ичных чисел | 1983 |

|

SU1188730A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Универсальный операционный блок | 1990 |

|

SU1714585A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

MATPtHHbtfi ВЫЧИСЛИТЕЛЬ, содержащий (и-1) блоков суммирования и (п-2) элементов И (где п- разрядность операндов J, о т л и ч а ю щ и и с я тем, что, с целью расширения его функциональных возможностей путем обеспечения возможности вычисления произведения двух величин, помимо вычисления квадратного корня, в него введены h групп элементов И по Г| элементов в каждой и (rt-1) одноразрядных коммутаторов, причем первый блок суммирования содержит (h+2)разрядный сумматор и (п-1)-разрядный дополнительный сумматор, входы разрядов. .первого операнда которого соединены соответственно с выходами (h-l) старших разрядов (п+2)-разрядного сумматора, входы с второго по (п-1) разрядов второго операнда (п-1) разрядного дополнительного сумматора первого блока суммирования соединены с шиной логической единицы, входы разрядов с второго по (П-И)-й первого операнда (п+2)-разрядного сумматора первого блока суммирования соединены соответственно с выходами элементов И первой группы, входы разрядов с третьего по (и+2)-й второго операнда (п+2)-разрядного сумматора первого блока суммирования соединены соответственно с выходами элементов И второй группы, каждый одноразрядный коммутатор содержит элемент И и элемент ИЛИ, выход которого соединен с первым входом элемента И того же одноразрядного коммутатора, вход задания режима устройства соединен с вторыми входами элементов И всех одноразрядных коммутаторов и инверсными входами всех элементов И, j- и блок суммирования содержит ( ft+2)-разрядный сумматор , (j +3 )-разрядный дополнитель- . ный сумматор, (-1) сумматоров по модулю два (,n-l) и элемент ИЛИ, входы разрядов первого операнда (J+3)-разрядного дополнительного сумматора соединены с выходами соответственно (j+3)-x старших разрядов . (п+2)-разрядного сумматора, выходы сумматоров по модулю два соединены 4 с входами разрядов, начиная со вто- iifc рого, второго операнда (/+3)-разряд- О) ного дополнительного сумматора, пер- 4 вый и второй входы элемента ИЛИ j-ro блока суммирования соединены соответственно с выходами переноса (п+2)-раз рядного сумматора и (j+31-разрядного дрполнительного сумматора этого же блока суммирования, выход элемента ИЛИ -го блока суммирования соединен с входом (-П-го элемента И, выход которого соединен с входом старшего разряда (h+2)-разрядного сумматора (j-l)-ro блока суммирования, первый вход гп-го сумматора по

1

Изобретение относится к вычислительной Технике и может быть применено в качестве спецпроцессора в комплексе с цифровой вычислительной машиной для оперативного вычисления функций )(V и ot xv .

Известно устройство, содержащее (п-1) сумматоров, п сумматоров по модулю два, группы из п элементов ИЛИ, группы элементов НЕ и (п-2) дополнительные группы из (n-i-1) сумматоров по модулю два в каждой, причем выход j-ro одноразрядного сматора г-го сумматора соединен с первым входом J-ro одноразрядного сумматора (j-l)-ro сумматора ( j 1,2,..., ft-i+l) (i Ь|,2,...,л-2), а вторые входы j-x одно1 азрядных сумматоров (i-l)-ro сумматора подключены к выходу переноса первого

одноразрядного сумматора i-ro сумь атора i .

Недостатком известного устройства являются ограниченные функциональные возможности, так как в устройстве вычисляется только корень квадратный произвольного числа.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее (п-1) сумматоров, группы сумматоров по модулю два, элементы ИЛИ, элементы НЕ, группы из (fi-2) элементов И и шину логической единицы, причем выход каждого (i-fl)-ro разряда j-ro сумматора 0 1 ,2,. .. ,п+2, j 1 ,2,... ,п-2) соединен с первым входом i-ro разряда (j+l)-ro сумматора, а второй вход первого одноразрядного сумматора (t+1)- го сумматора соединен с

выходом переноса первого одноразрядного сумматора 1-го сумматора 2j.

Ограниченные функциональные возможности обусловлены тем, что в известном устройстве вычисляется ot ту, а не вычисляются зависимости оС Уху и .

Целью изобретения является расширение функциональных возможностей устройства за счет получения возможности вычисления произведения двух величин.

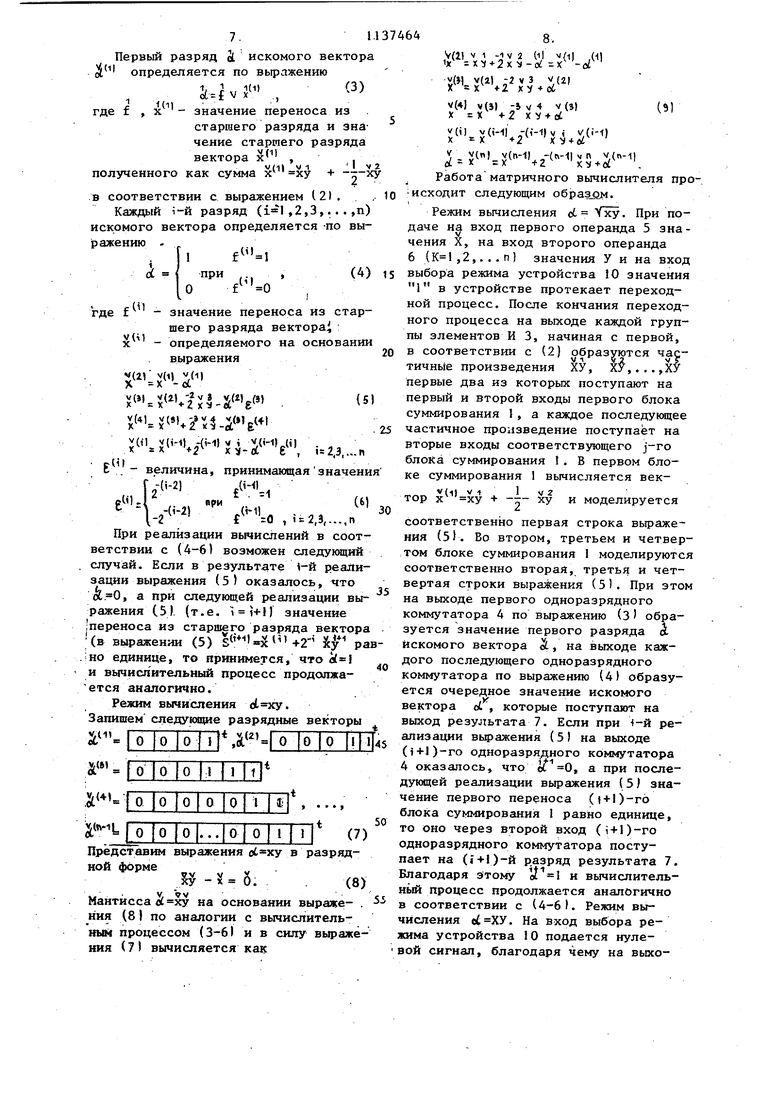

Поставленная цель достигается тем, что матричный вычислитель, содержащий (п-1) блоков суммирования и (г1-2} злементов И (где tiразрядность операндов ), дополнительно содержит fi групп элементов И по п элементов в каждой и (h-1) одноразрядных коммутаторов, причем первый блок суммирования содержит (п+2)-разрядный сумматор и (п-1)разрядный дополнительный сумматор, входы разрядов первого операнда которого соединены соответственно с выходами (п-1) старших разрядов (л+2) разрядного сумматора, входы с второго по (-Празрядов второго one- . ранда (п-1)-разрядного дополнительного сумматора первого блока суммирования соединены с шиной логической единицы, входы разрядов с второго по ,(11+1)-й первого операнда (h+2)разрядного сумматора первого блока суммирования соединены соответственно с выходами элементов И первой , входы разрядов с третьего по (п+2)-й второго операнда (п-ь2)-разрядного сумматора первого блока сум мирования соединены соответственно с выходами элементов И второй группы, каждый одноразрядный коммутатор содержит элемент И и элемент ИЛИ, выход которого соединен с первым вх дом элемента И этого же одноразрядного коммутатора,вход задания режима устройства соединен с вторыми вх дами элементов И всех одноразрядных коммутаторов и инверсными входами всех элементов И, j-й блок суммиров ния содержит (п+2)-разрядный сумматор, (1+3)-разрядный дополнительный сумматор, (J-1) сумматоров по модулю два {j 2, п-1 ) и элемент ИЛИ, входы разрядов первого операнда (j+3)-разрядного дополнительного сумматора соединены с выходами соответственно ()+3)-старших раз рядов (п+2)-разрядного сумматора,

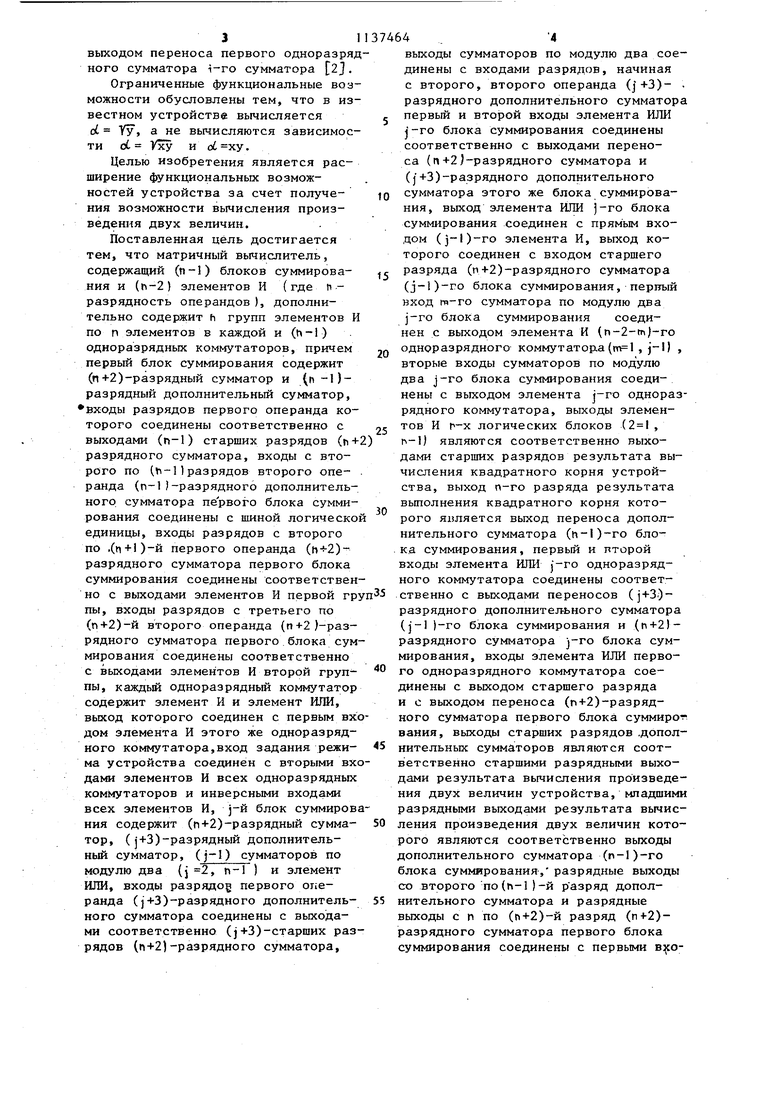

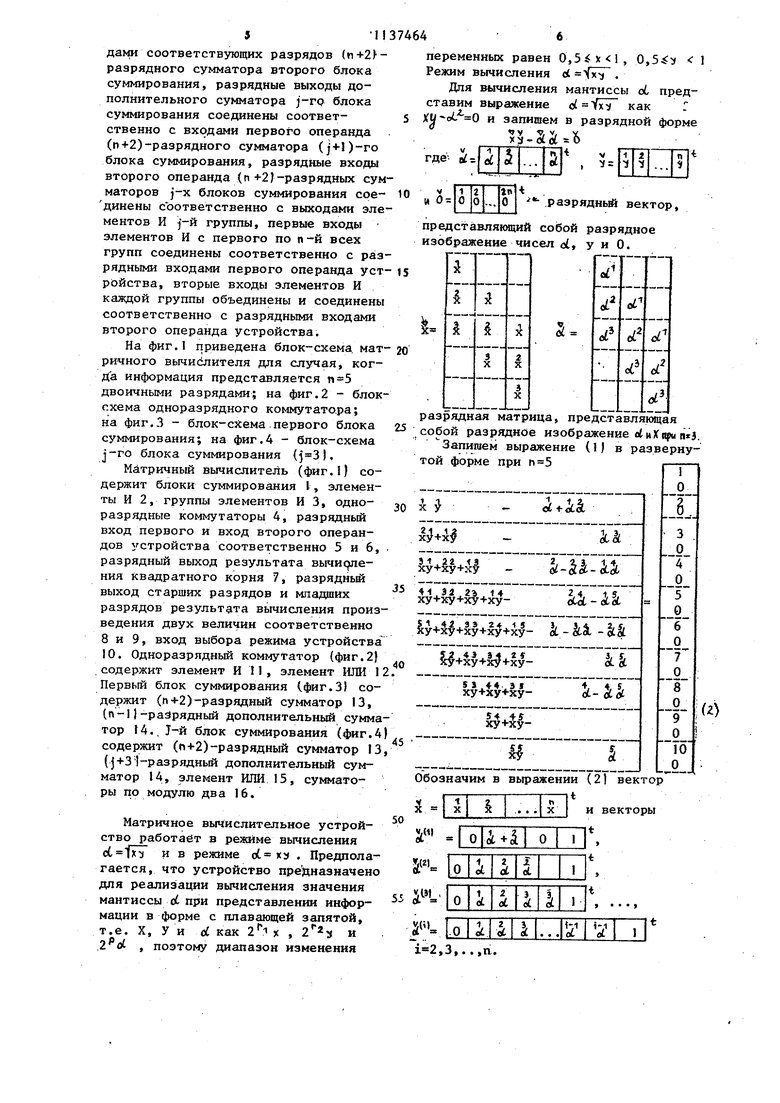

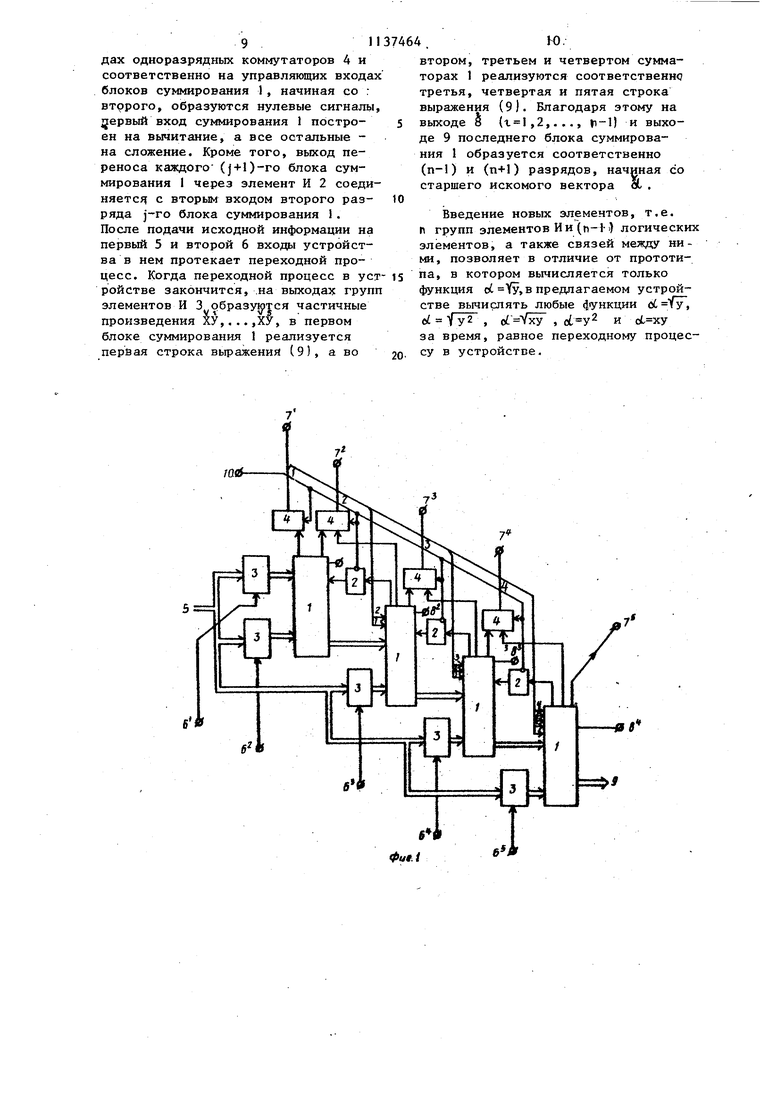

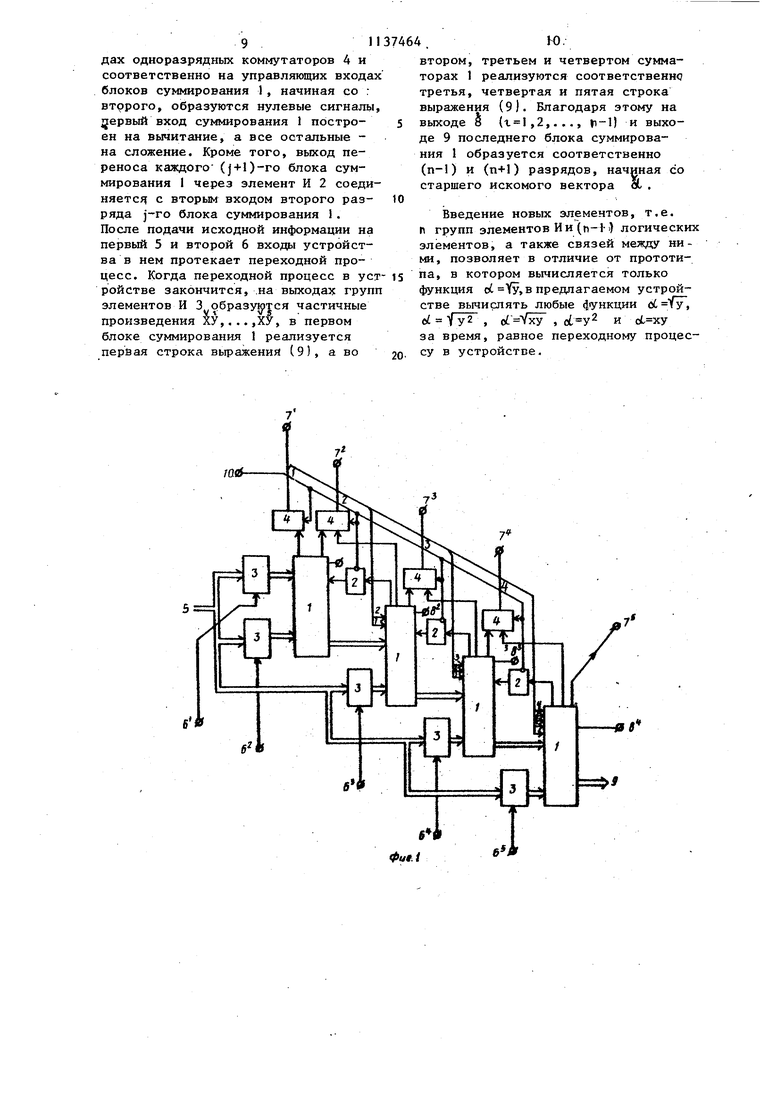

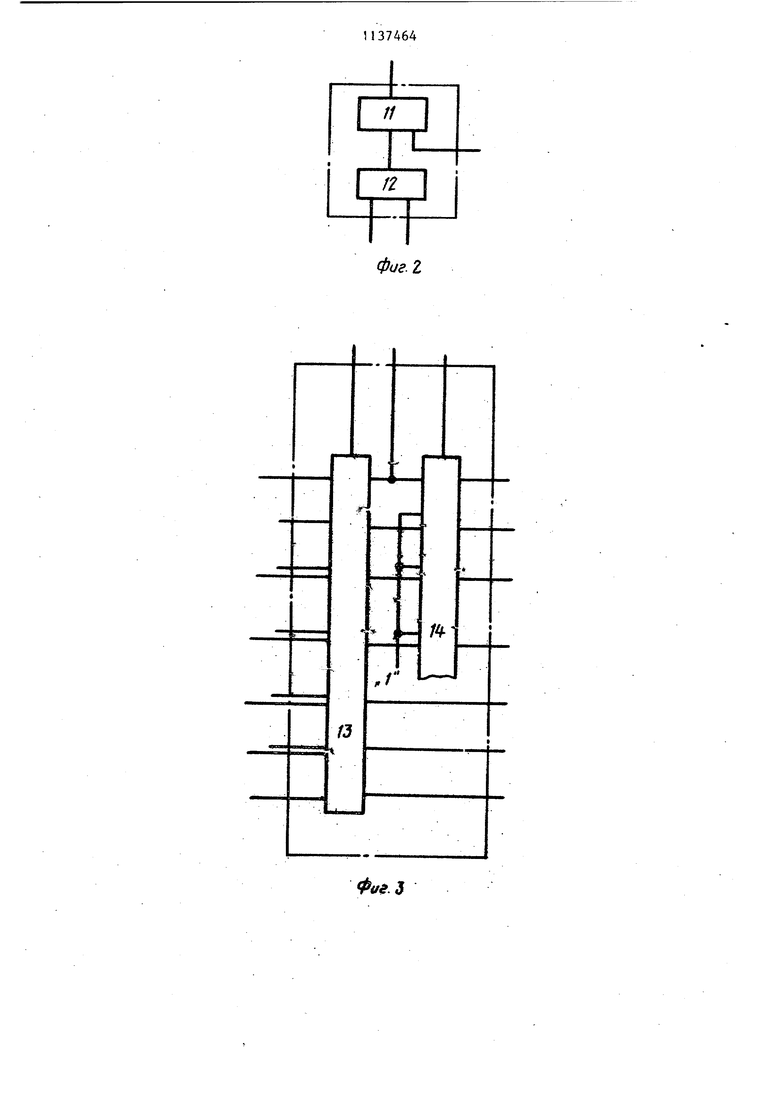

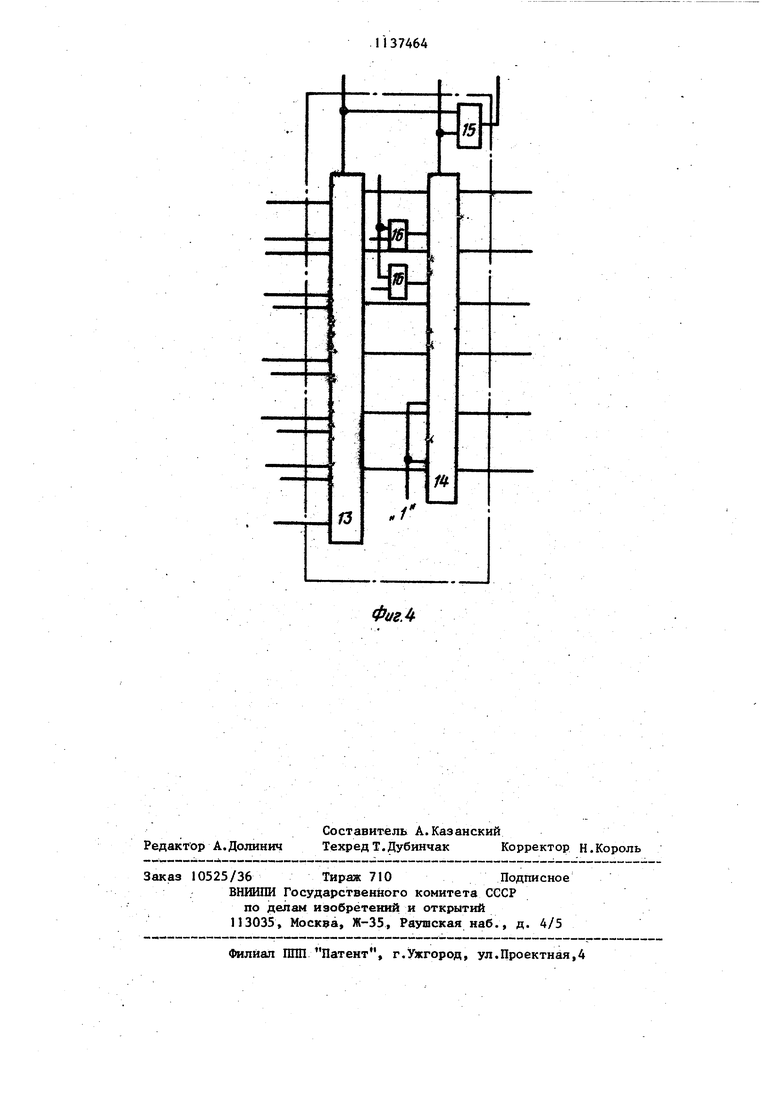

выходы сумматоров по модулю два соединены с входами разрядов, начиная с второго, второго операнда (j+3)- разрядного дополнительного сумматора первый и второй входы элемента ИЛИ j-ro блока суммирования соединены соответственно с выходами переноса (п+2)-разрядного сумматора и (J +3)-разрядного дополнительного сумматора этого же блока суммирования, выход элемента ИЛИ j-ro блока суммирования соединен с прямым входом (j-l)-ro элемента И, выход которого соединен с входом старшего разряда (п+2)-разрядного сумматора (j-l)-ro блока суммирования, перный вход т-го сумматора по модулю два j-ro блока суммирования соединен с выходом элемента И (n-2-tn)-ro одноразрядного коммутатор,а ( , j-I) , вторые входы сумматоров по модулю два j-ro блока суммирования соединены с выходом элемента j-ro одноразрядного коммутатора, выходы элементов И г-х логических блоков (, п-1) являются соответственно выходами старших разрядов результата вычисления квадратного корня устройства, выход п-го разряда результата выполнения квадратного корня которого является выход переноса дополнительного сумматора (h-l)-ro блока суммирования, первый и г торой ходы элемента ИЛИ j-ro одноразрядого коммутатора соединены соответственно с выходами переносов (j+3) - разрядного дополнительного сумматора (j-1 )-го блока суммирования и (п+2)разрядного сумматора j-ro блока суммирования, входы элемента ИЛИ первого одноразрядного коммутатора соединены с выходом старшего разряда и с выходом переноса (п+2)-разрядного сумматора первого блока суммирог вания, выходы старших разрядов .дополнительных сумматоров являются соответственно старшими разрядными выходами результата вычисления произведения двух величин устройства, мпадшими разрядными выходами результата вычисления произведения двух величин которого являются соответственно выходы дополнительного сумматора (n-l)-ro блока суммирования, разрядные выходы со второго nolh-l )-й разряд дополнительного сумматора и разрядные выходы с п по (п+2)-й разряд (п+2)разрядного сумматора первого блока суммирования соединены с первыми вхо5113дами соответствующих разрядов (п+2} разрядного сумматора второго блока суммирования, разрядные выходы дополнительного сумматора j-rg блока суммирования соединены соответственно с входами первого операнда (п+2)-разрядного сумматора (j+l)-ro блока суммирования, разрядные входы второго операнда (п +2J-разрядных сумматоров J-X блоков суммирования соединены сЪответственно с выходами элементов И j-й группы, первые входы элементов И с первого по п-и всех групп соединены соответственно с разрядными входами первого операнда устройства, вторые входы элементов И каждой группы объединены и соединены соответственно с разрядньп и входами второго операнда устройства. На фиг,1 приведена блок-схема, матричного вычислителя для случая, когда информация представляется двоичными разрядами; на фиг.2 - блоксхема одноразрядного коммутатора; на фиг.З - блок-схема.первого блока суммирования; на фиг.4 - блок-схема j-ro блока суммирования (). Матричный вычислитель (фиг.1) содержит блоки суммирования I, элементы И 2, группы элементов ИЗ, одноразрядные коммутаторы 4, разрядный вход первого и вход второго операндов з стройства соответственно 5 и 6, разрядный выход результата вычи ления квадратного корня 7, разрядный выход старших разрядов и младших разрядов результата вычисления произведения двух величин соответственно 8 и 9, вход выбора режима устройства 10. Одноразрядный коммутатор (фиг.2) содержит элемент И 11, элемент ИЛИ 12 Первый блок суммирования (фиг.31 содержит (п+2)-разрядный сумматор 13, (п-)-разрядный дополнительный сумматор 14., J-й блок суммирования (фиг.4) содержит (п+2)-разрядный сумматор 13, (J+3 )-разрядный дополнительный сумматор Ц, элемент ИЛИ 5, суммато2 dL

поэтому диапазон изменения

,3,..,п. , 0,5.: 1 . иссы об предx7 как Г ставляющая ение о( и)(яри шЗ. 1) в разверну2) вектор векторы Первый разряд ot искомого вектора . определяется по выражению 2t значение переноса из старшего разряда и значение старшего разряда вектора х , «Ml 1 1 полученного как сумма х ху .-2-х в соответствии с выражением (21. Каждый i-й разряд (,2,3,...,п) искомого вектора определяется -по вы ражению1 - значение переноса из старшего разряда вектора - определяемого на основании выражения иГ v( ((L;w4; | X ie( . (,,(M(4t v((H)(H,.v.(H,gU) 2Л..п величина, принимающая значен , U2,3,...,n При реализации вычислений в соот ветствии с (4-6) возможен следующий случай. Если в результате -й реали зации выражения (5 ) оказалось, что Л.0, а при следующей реализации вы ражения (51. (т.е. ) значение .переноса из старшего разряда вектор (в выражении (5) И)+2 :ky р .iHO единице, то принимется, что а( и вычислительный процесс продолжа/ется аналогично. Режим вычисления . Представга4 выражения в разрядной форме„ . .(8 ., V. Vv Мантисса л ху на основании выражения (8) по аналогии с вычислительным процессом (3-61 и в силу выраже ния (7) вычисляется как 1 (4 (5 648. vat 1 2 Ы v(i) (i| K X V -Ы )( -d v(l v(at -2 V 3 V(2| X X +2 ХУ + ot V{) V(3) -J V 4 V(3) X x -гху-к ;;(),v(Mi(M,(i-i) J (. Работа матричного вычислителя проИСХОДИТ следующим образом. Режим вычисления oL Уху. При подаче на вход первого операнда 5 значения X, на вход второго операнда 6 (,2,...п) значения У и на вход выбора режима устройства 10 значения 1 в устройстве протекает переходной процесс. После кончания переходного процесса на выходе каждой группы злементов И 3, начиная с первой, в соответствии с (2) образуются часvivf V тичнЫе произведения ХУ, ХУ,...,ХУ первые два из которых поступают на первый и второй входы первого блока суммирования I, а каждое последующее частичное произведение поступает на вторые входы соответствующего j-ro блока суммирования . В первом блоке суммирования 1 вычисляется векV(il V t 1 V 2 тор х + --- ху и моделируется соответственно первая строка вьфажения (51. Во втором, третьем и четвертом блоке суммирования 1 моделируются соответственно вторая, третья и четвертая строки выражения (5). При зтом на выходе первого одноразрядного коммутатора 4 по выражению (З образуется значение первого разряда d искомого вектора cL, на выходе каждого последующего одноразрядного коммутатора по выражению (4) образуется очередное значение искомого вектора ot , KOTopaiie поступают на выход результата 7. Если при 1-й реализации вьфажения (51 на выходе (t+l)-ro одноразрядного коммутатора 4 оказалось, что , а при последующей реализации выражения (5 значение первого переноса О + 1)-г6 блока суммирования равно единице, то оно через второй вход (i+l)-ro одноразрядного коммутатора поступает на («+1)-й разряд результата 7. Благодаря этому ot 1 и вычислительньй процесс продолжается аналогично в соответствии с (4-61. Режим вычисления . На вход выбора режима устройства 10 подается нулевой сигнал, благодаря чему на выхо91дах одноразрядных коммутаторов 4 и соответственно на управляющих входах блоков суммирования 1, начиная со : второго, образуются нулевые сигналы jjepBbifl вход суммирования 1 построен на вычитание, а все остальные на сложение. Кроме того, выход переноса каждого- (j + O-ro блока суммирования 1 через элемент И 2 соединяется с вторым входом второго разряда j-го блока суммирования 1. После подачи исходной информации на первый 5 и второй 6 входы устройства в нем протекает переходной процесс. Когда переходной процесс в уст ройстве закончится, на выходах групп элементов И 3 образуются частичные произведения ХУ,...,ХУ, в первом блоке суммирования 1 реализуется первая строка выражения (9), а во

/Q

5 - втором, третьем и четвертом сумматорах 1 реализуются соответственнс третья, четвертая и пятая строка выражения (9). Благодаря этому на выходе в (г 1,2,..., |п-1) и выходе 9 последнего блока суммирования 1 образуется соответственно (п-1) и (п+1) разрядов, начиная со старшего искомого вектора d, , Введение новых элементов, т.е. п групп элементов И и (n-i) логических элементов, а также связей между ними, позволяет в отличие от прототипа, в котором вычисляется только функция оС Yy, в предлагаемом устройстве вычислять любые функции оС Уу, d Уу2 , , ot-y и за время, равное переходному процессу в устройстве.

QD i

фиг. I

n

j Фи9.

.4

| I, Авторское свидетельство СССР № 773617, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для извлечения квадратного корня | 1979 |

|

SU857981A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-30—Публикация

1983-02-09—Подача