СК)

00 О)

а

10

31608660

Изобретение относится к вычислительной технике и может .быть применено в устройствах обработки информации, использующих представление чисел в . система остаточных {слассов.

Целью изобретения является расширение функциональных возможностей за счет обеспечения вычисления ядра и уточненного ранга.

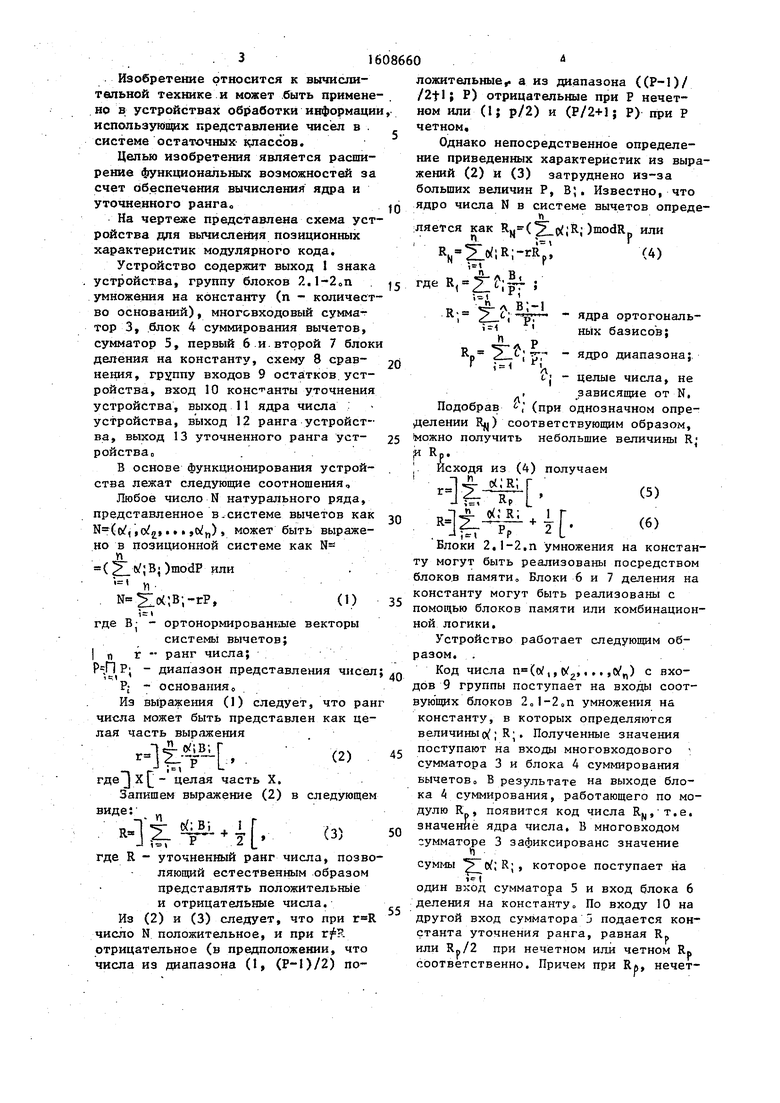

На чертеже представлена схема устройства для вычисления позиционных характеристик модулярного кода.

Устройство содержит выход 1 знака устройства, группу блоков 2.1-2оП . умножения на константу (п количество оснований), многовходовый сумма- тор 3, блок 4 суммирования вычетов, сумматор 5, первый 6 и.второй 7 блоки деления на константу, схему 8 срав- JQ нения, группу входов 9 остатков, устройства, вход 10 конс- анты уточнения устройства, выход 11 ядра числа устройства, выход 12 ранга устройстложительные,. а из диапазона ((Р-1)/ /2tl; Р) отрицательные при Р нечетном или (1; р/2) и (Р/2-И; Р) при Р четном.

Однако непосредственное определение приведенных характеристик из выра жений (2) и (3) затруднено из-за больших величин Р, В;, Известно, что

ядро числа N в системе вычетов опреде

;ляется как R(pi;R,)modR или

Rn ilo ;R;-rfpl (4)

5 д в;R с; V.- - ядра ортогональ- Hbix базисов;

,- - ядро диапазона;,

Ч

tj - целые числа, не

, зависящие от N. Подобрав , (при однозначном определении ) соответствующим образом, ва, выход 13 уточненного ранга уст- 25 можно получить небольшие величины Rройства

В основе функционирования устройства лежат следующие соотношения,

Любое число N натурального ряда, представленное в.системе вычетов как N(o(,,,.. ,,) , может быть выражено в позиционной системе как Nп ( в/;В; )raodP или

pi Rp.

Исходя из (4) получаем

(

м

(1)

N 2 0 :8;-гр.

где Bj - opTOHopMHpoBaHtaie векторы

сисТегФ вычетов; In г - ранг числа;

Р.ПР; - диапазон представления чисел; PJ - основания

Из выражения (1) следует, что ранг числа может быть представлен как целая часть выражения -1 п

г 1Г35

40

(2)

|У;В; Г

-I г гдeJXL- целая часть X.

Запишем выражение (2) в следующем виде:-

«

где R - уточненный ранг числа, позволяющий естественным образом представлять положительньге и отрицательные числа. Из (2) и (3) следует, что при

число N положительное, и при т:.

отрицательное (в предположении, что

числа из диапазона (1, (Р-1)/2) по30

Блоки 2,1-2,п умножения на константу могут быть реализованы посредством блоков памяти. Блоки 6 и 7 деления на константу могут быть реализованы с помощью блоков памяти или комбинационной логики.

Устройство работает следующим образом, .

Код числа п(о/,,(У,. ,t ,0( „) с входов 9 группы поступает на входы соот- вую щих блоков 2„1-2оП умножения на константу, в которых определяются величиныо ; RI , Полученные значения д поступают на входы многовходового сумматора 3 и блока 4 суммирования Бычетово В результате на выходе блока 4 суммирования, работающего по модулю R , появится код числа Rj,-T,e, значение ядра числа, В многовходом

сумматоре 3 зафиксировано значение 1

суммы R; , которое поступает на

1 ( один вход сумматора 5 и вход блока 6

деления на константу По входу 10 на другой вход сумматора 5 подается константа уточнения ранга, равная R,,

тч / л

или Rp/2 при нечетном или четном R соответственно. Причем при RA, нечет0

Q

ложительные,. а из диапазона ((Р-1)/ /2tl; Р) отрицательные при Р нечетном или (1; р/2) и (Р/2-И; Р) при Р четном.

Однако непосредственное определение приведенных характеристик из выражений (2) и (3) затруднено из-за больших величин Р, В;, Известно, что

ядро числа N в системе вычетов опреде;ляется как R(pi;R,)modR или

Rn ilo ;R;-rfpl (4)

5 д в;R с; V.- - ядра ортогональ- Hbix базисов;

,- - ядро диапазона;,

Ч

tj - целые числа, не

, зависящие от N. Подобрав , (при однозначном опреpi Rp.

Исходя из (4) получаем

5

0

Блоки 2,1-2,п умножения на константу могут быть реализованы посредством блоков памяти. Блоки 6 и 7 деления на константу могут быть реализованы с помощью блоков памяти или комбинационной логики.

Устройство работает следующим образом, .

Код числа п(о/,,(У,. ,t ,0( „) с входов 9 группы поступает на входы соот- вую щих блоков 2„1-2оП умножения на константу, в которых определяются величиныо ; RI , Полученные значения поступают на входы многовходового сумматора 3 и блока 4 суммирования Бычетово В результате на выходе блока 4 суммирования, работающего по модулю R , появится код числа Rj,-T,e, значение ядра числа, В многовходом

сумматоре 3 зафиксировано значение 1

суммы R; , которое поступает на

1 ( один вход сумматора 5 и вход блока 6

деления на константу По входу 10 на другой вход сумматора 5 подается константа уточнения ранга, равная R,,

тч / л

или Rp/2 при нечетном или четном R соответственно. Причем при RA, нечетнем по первому входу сумматора 5, в Н€ го записывается удвоенная сумма

щ оизведений остатков на ядра орто.п

ГС нальных базисов (что в

д1 оичной системе легко может быть

осуществлено путем добавления нуля Чправа),

Таким образом, с выхода суммато5 на вход блока 7 деления на конИ

10

содержащее группу блоков умножения на константу многовходовый сумматор, блок суммирова:ния вычетов, сумматор, первый блок деления на кодстан- ту и схему сравнения, причем группа входов остатков устройства соединена с входаг-ш соответствующих .блоков умножения на константу группы, выходы которых соединены с соответствующими входами группы блока суммирования вычетов, выход многовходово 2o(;R;+Rp при

-

I на

анту подается величина Zp(;R;+Hp/2 сумматора соединен с входом первого блока деления на константу, о т- J5 л и чающееся тем, что, с целью расширения функциональных возможнстанту преобразуют суммы R; ностей за счет обеспечения вычисления

р п /7 f n 4.R V - ДР уточненного ранга, оно содер К; Р-;+Кр/ - ° жР,т. второй бчок деления на константу,

ранга г и уточненного ранга R, ко- 20 причем выходы блоков умножения на конпоступапт на выходы 12 и 13 со- станту группы соединены с входами

соответствующих слагаемых многовходо- вого сумматора, выход которого соединен с входом первого слагаемого сум- 25 матора, вход второго слагаемого которого является входом константы уточП и RP четном или

R- нечетномо Блоки 6 и 7 деления на РП

к и

т )рые

о г

Н1Й

хэды

ветственнОо

Одновременно с поступлением значе- ранга и уточненного ранга на и 13 устройства их значения подаются на входы схемы 8 сравнения,

которой сравниваются их значения. ПЬи равенстве сигнал, соответ- гвующий значению число положительнения устройства, выход ядра числа которого соединен с выходом блока суммирования вычетов, выход сумматоное, подается на выход 1 устройства. Q pa соединен с входам второго блока

Йсли г не равно R, сигнал на выход I устройства не подается, что соответствует значению число отрицательное, Процесс определения позиционных харак- аристик модулярного кода закончен.

деления на константу, выход которого является выходом уточненного ранга устройства, выход ранга которого соединен с выходом первого блока деления на константу и с первым входом

1ИСТИК модулярного кода закончен, ,ния на KOHuidHiy и ис -поич Дополнительный положительный эффект схемы сравнения, второй вход и выход заключается в упрощении устройства, которой соединены с выходом второго ормула изобретения блока деления на константу и с выхо- Устройство дпя вычисления позицион- дом знака устройства соответственно, ых характеристик модулярного кода, 0

0

содержащее группу блоков умножения а константу многовходовый сумматор, блок суммирова:ния вычетов, сумматор, первый блок деления на кодстан- ту и схему сравнения, причем группа входов остатков устройства соединена с входаг-ш соответствующих .блоков умножения на константу группы, выходы которых соединены с соответствующими входами группы блока суммирования вычетов, выход многовходово сумматора соединен с входом первосоответствующих слагаемых многовходо- вого сумматора, выход которого соединен с входом первого слагаемого сум- матора, вход второго слагаемого которого является входом константы уточнения устройства, выход ядра числа которого соединен с выходом блока суммирования вычетов, выход сумматоpa соединен с входам второго блока

деления на константу, выход которого является выходом уточненного ранга устройства, выход ранга которого соединен с выходом первого блока деления на константу и с первым входом

,ния на KOHuidHiy и ис -поич схемы сравнения, второй вход и выход которой соединены с выходом второго блока деления на константу и с выхо- дом знака устройства соответственно,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Устройство для вычисления позиционных характеристик модулярного кода | 1984 |

|

SU1244797A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| Вычислительное устройство в модулярной системе счисления | 1984 |

|

SU1244665A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для нормализации чисел в модулярной системе счисления | 1986 |

|

SU1332317A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

Изобретение относится к вычислительной технике и предназначено для создания устройств обработки информации, использующих представления чисел в виде вычетов в системе остаточных классов. Цель изобретения - расширение функциональных возможностей за счет обеспечения вычисления ядра и уточненного ранга. Устройство содержит группу блоков 2 умножения на константу, многовходовый сумматор 3, блок 4 суммирования вычетов, сумматор 5, блоки 6 и 7 деления на константу и схему 8 сравнения. 1 ил.

| Устройство для вычисления позиционных характеристик модулярного кода | 1984 |

|

SU1244797A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-11-23—Публикация

1989-02-13—Подача