Изобретение относится к вычислительной технике и может быть применено в устройствах обработки информа- , использующих представление чисел в системе остаточных классов (модулярные коды).

Цель изобретения - расширение функциональных возможностей путем обеспечения преобразования числа из системы остаточных классов с произ- вольным числом п оснований в позиционную систему счисления,

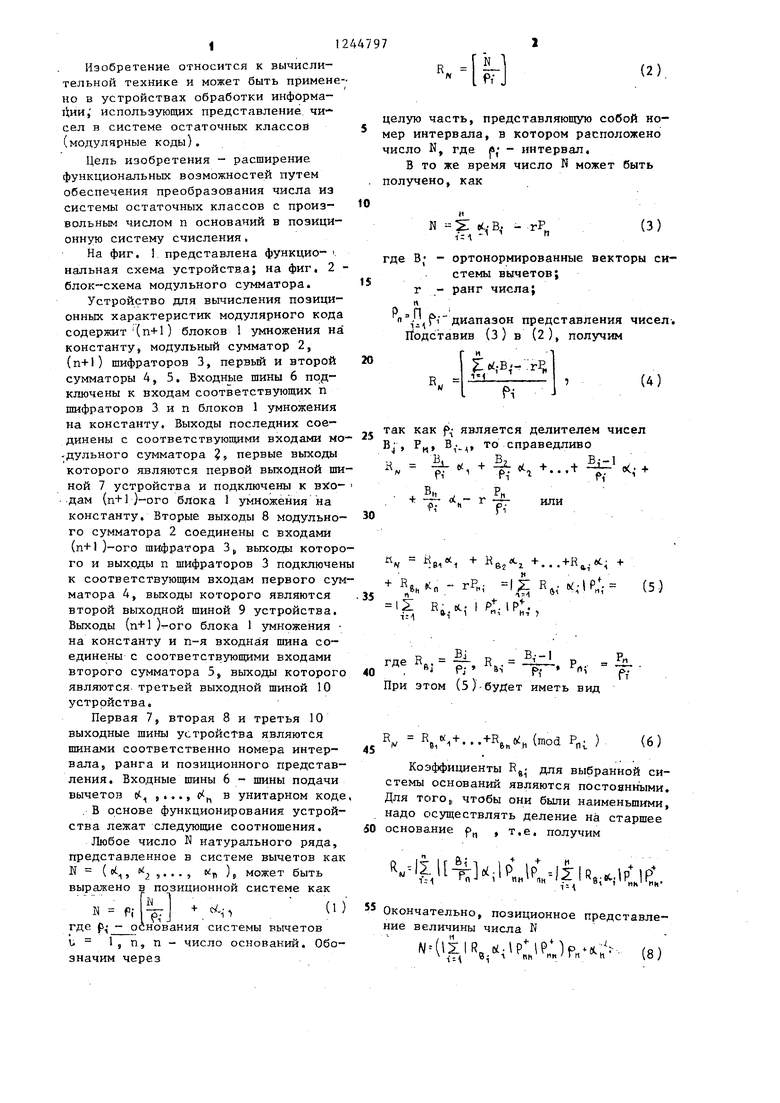

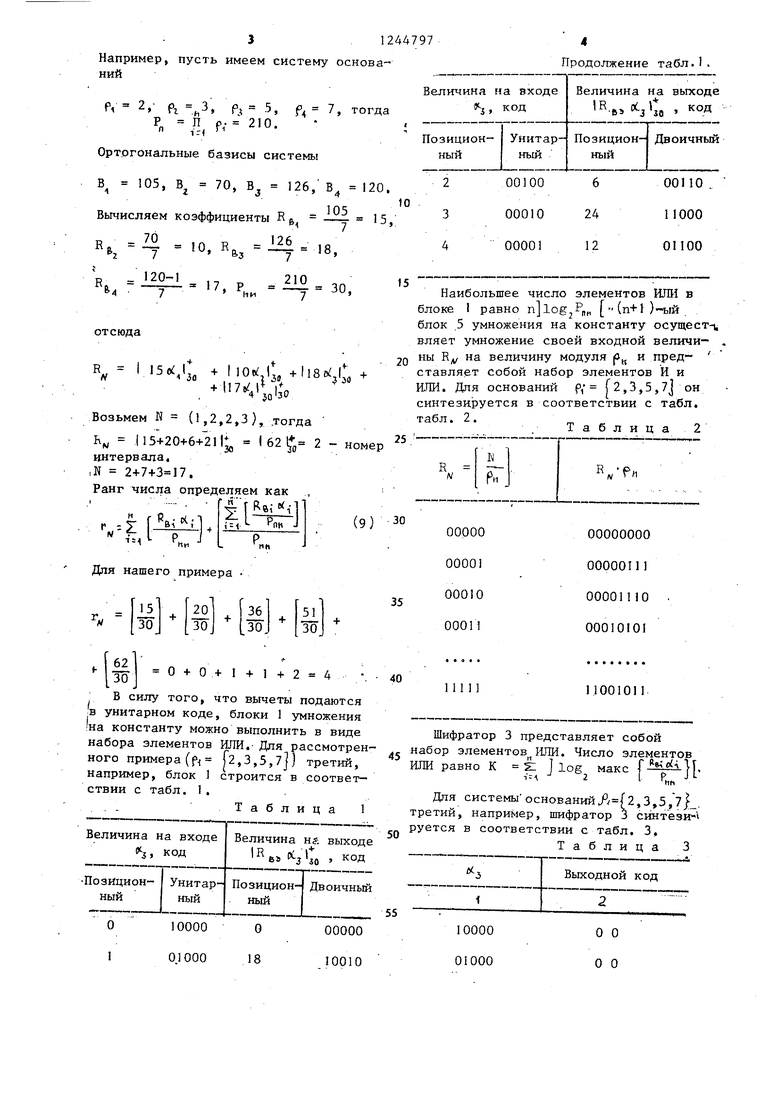

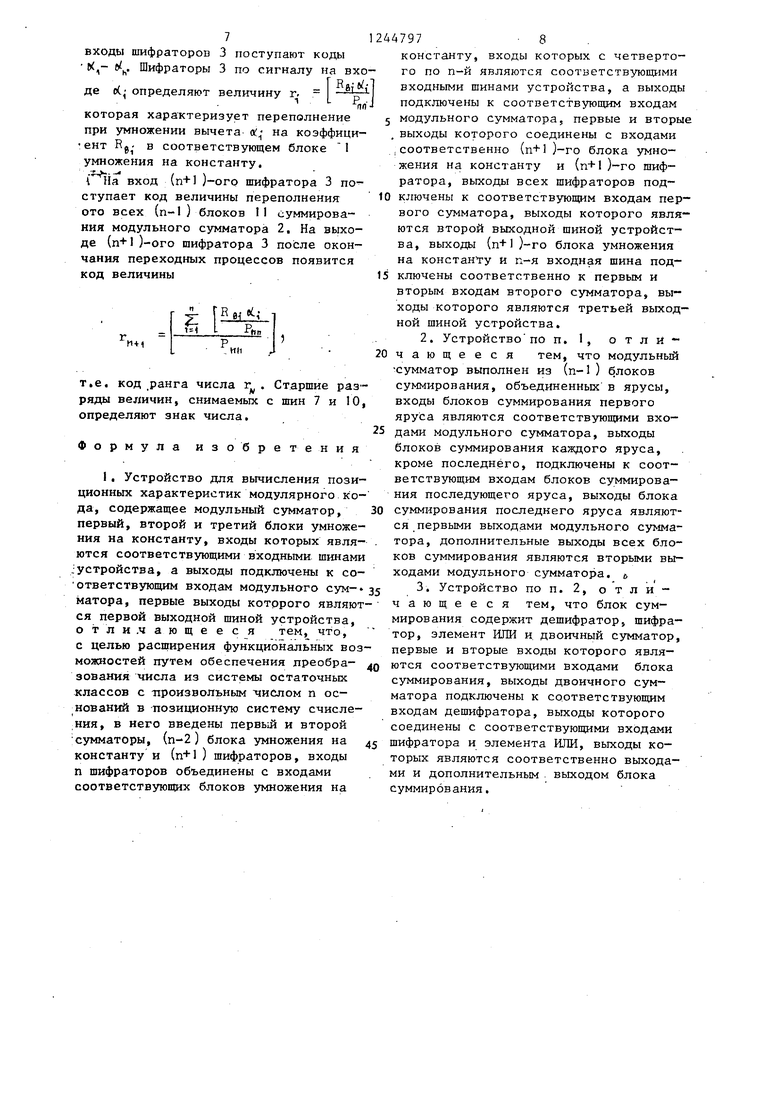

На фиг, 1 представлена функцио- . нальная схема устройства; на фиг, 2 - блок-схема модульного сумматора.

Устройство для вычисления позиционных характеристик модулярного кода содержит (п+1) блоков 1 умножения на константу, модульный сумматор 2, (п+1) шифраторов 3, первый и второй сумматоры 4, 5. Входные шины 6 подключены к входам соответствующих п шифраторов 3 и п блоков 1 умножения на константу. Выходы последних соединены с соответствующими входами мо -дульного сумматора , первые выходы которого являются первой вьгх.одной шиной 7 устройства и подключены к входам ( блока 1 умножения на константу. Вторые выходы 8 модульно- го сумматора 2 соединены с входами (п+1 )-ого шифратора 3 выходы которого и выходы п шифраторов 3 подключен к соответствующим входам первого сумматора 4, выходы которого являются второй выходной шиной 9 устройства. Выходы (п+1 )т-ого блока 1 умножения на константу и п-я входная шина соединены с соответствуюшлми входами второго сумматора 5j выходы которого являются третьей выходной шиной 10 устройства.

Первая 7, вторая 8 и третья 10 выходные шины устройства являются шинами соответственно номера интер- вала5 ранга и позиционного представления. Входные шины 6 - шины подачи вычетов ct, , ..., (i в унитарном коде . В основе функционирования устройства лежат следующие соотношения.

Любое число N натурального ряда, представленное в системе вычетов как К ( 2 5... 5 f может быть выражено в позиционной системе как

с.

i -

(1)

Гй 1

й г(Ь

где р - основания системы вычетов U - 1, п, п - число оснований. Обозначим через

ли pj

К„

(2)

целую часть, представляющую собой номер интервала, в котором расположено число N, где ft- - интервал,

В то же время число N может быть получено, как

f.fi-B,- -гР,

(3)

где В; - ортонормированные векторы системы вычетов;

г - ранг числа;

п

диапазон представления чисел. ТТодставив (3) в (2), получим

.-

r,o.B.--.ri;

Pi

(4)

так как f является делителем чисел

j °i M

i.

А. Pi

Ilh. f,« +

TO справедливо

ct

PI

IL PI

г i

или

v

B.

+ +.

H

.+«a,-« RftH -n -- rp.; H,E R,,.;IP:- f, R,s-tp:.ip:,-,

Rp

R VI

P; p,

этом (5).буяет иметь вид

SL

Рт

RN RB/.-.-.+R

6п.И

(mod РП- )

(6)

Коэффициенты для выбранной системы оснований являются постоянными. Для того,, чтобы они бьши наименьшими, надо осуществлять деление на старшее основание р , т.е, получим

,it,ipjp:4.i«.ip:jc

55 Окончательно, позиционное

ние величины числа N

представле «« HPnVCjP.C-- (8)

31244797

Например, пусть имеем систему оснований

PI 2,- Рг 3, ,, 5, f 7, тогда РП П, Р..

Ортргональные базисы системы

В 105, В, 70, В- 126, В. 120.

J4 д

Вычисляем коэффициенты е -т

1Я

7

R 70 126 «&, Т - ° Ьз fe.

120-1

,7, .ili.30,

Ни

отсюда

R

Наибольшее число элементов ИЛИ блоке I равно njlog Pn -(п+О-ый блок .5 умножения на константу осущ вляет умножение своей входной вели 20 ны R, на величину модуля р, и пред

, А ijv-o ri-ij- j. .-. p-f, X. t-v,

- ( за Oei lij +Il8oi I +ставляет собой набор элементов И и

, -l 7.,|it

ИЖ. Для оснований р, Г2,3,5,7j синтезируется в соответствии с табл

Возьмем N (1,2,2,3), .тогда

К„ 115+20+6+211 62 2 - интервала. iN 2+7+3 17. Ранг числа определяем как ,

f iLli

РПИ J

-Sj

Для нашего примера

г 21 Ч 20 36. 30 30 Г 30

1L

30

62

Jo

о + о + 1 + 1+2 4

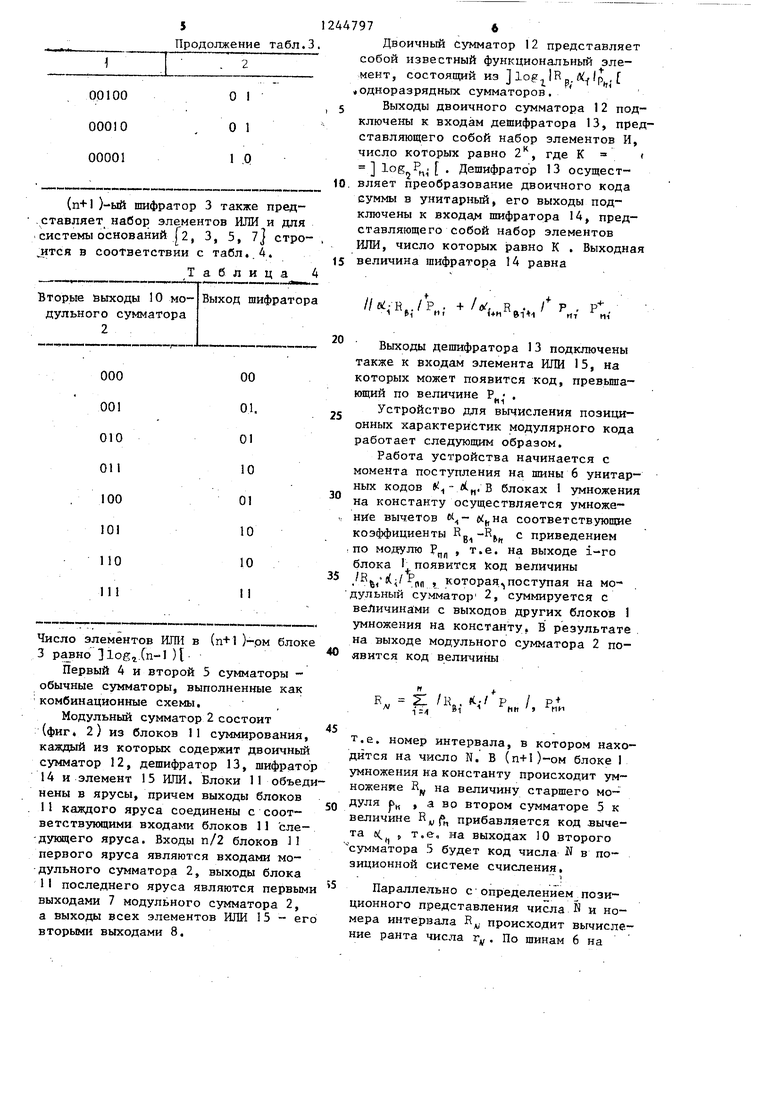

В силу того, что вычеты подаются в унитарном коде, блоки 1 умножения на константу можно выполнить в виде набора элементов ИЛИ,- Для рассмотренного примера (f |2,3,5,7j третий, например, блок 1 строится в соответствии с табл. 1.

Таблица 1 Величина на входе Величина н& выходе

Продолжение табл.1

Величина на входе

Величина на выходе

, код

IR

65 so

Унитар-| ный

Позицион-j ный

Двоичный

6

24 12

001 10 11000

опоо

15

Наибольшее число элементов ИЛИ в блоке I равно njlog Pn -(п+О-ый блок .5 умножения на константу осущест-t, вляет умножение своей входной величи- . 20 ны R, на величину модуля р, и пред-

20 А ijv-o ri-ij- j. .-. p-f, X. t-v,

ставляет собой набор элементов И и

ставляет собой набор элементов И и

ИЖ. Для оснований р, Г2,3,5,7j он синтезируется в соответствии с табл.

табл. 2.

Таблица 2

(9} 30

40

11111

1100101

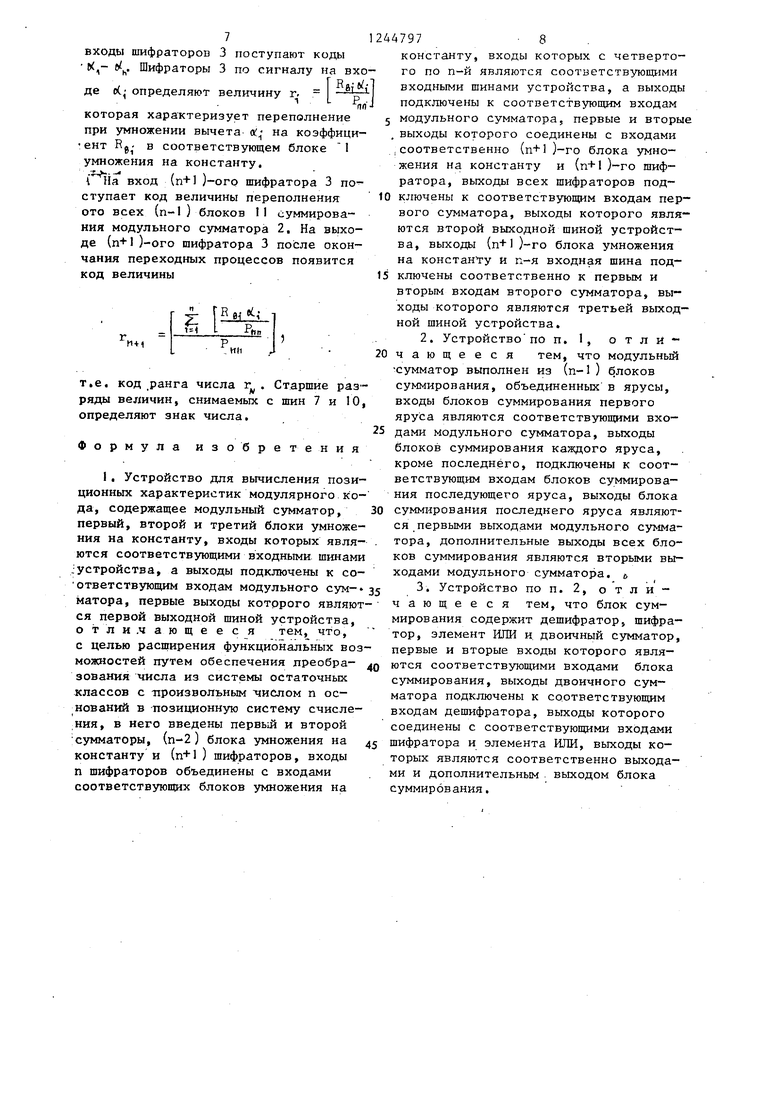

Шифратор 3 представляет собой набор элементов ИЛИ. Число элементов ИЛИ равно К Z: J log макс но

Для системы основанийЛ { 2,3,5,. третий, например, шифратор 3 сйнтези- руется в соответствии с табл. 3.

Продолжение табл.3.

10

(n+l )-ый шифратор 3 также пред- .ставляет набор элементов ИЛИ и для системы оснований , 3, 5, стро- ится в соответствии с табл..4.

Таблица 4

Вторые выходы 10 модульного сумматора 2

Выход шифратора Hei-R /Р . -f /, R .

1 ft; И1 {+И

20

Выходы дешифратора 13 п также к входам элемента ИЛ которых может появится код ющий по величине Р.. .

00

01.

01

10

01

10

10

11

25

30

35

Число элементов ИЛИ в (п+ )-рм блоке 3 равно logj.Cn-I )1Первый 4 и второй 5 сумматоры - обычные сумматоры, выполненные как комбинационные схемы.

Модульный сумматор 2 состоит (фиг 2) из блоков 11 суммирования, каждый из которых содержит двоичный сумматор 12, дешифратор 13, шифратор 14 и элемент 15 ИЛИ. Блоки 11 объединены в ярусы, причем выходы блоков 11 каждого яруса соединены с соответствующими входами блоков 11 сле- -дующего яруса. Входы п/2 блоков J1 первого яруса являются входами модульного сумматора 2, выходы блока 1I последнего яруса являются первыми выходами 7 модульного сумматора 2, а выходы всех элементов ИЛИ 15 - его вторыми выходами 8.

Двоичный Сумматор 12 представляет собой известный функциональный элемент, состоящий из J log IR и. Y Рь f «одноразрядных сумматоров.

Выходы двоичного сумматора 12 подключены к входам дешифратора 13, представляющего собой набор элементов И, число которых равно 2, где К ( log Р,,. . Дешифратор 13 осуществляет преобразование двоичного кода еуммы в унитарный, его выходы подключены к входа шифратора 14, представляющего собой набор элементов ИЛИ, число которых равно К . Выходная величина шифратора 14 равна

Р Р ,

мт П1

Выходы дешифратора 13 подключены также к входам элемента ИЛИ 15, на которых может появится код, превьша- ющий по величине Р.. .

1

Устройство для вычисления позиционных характеристик модулярного кода работает следующим образом.

Работа устройства начинается с момента поступления на шины 6 унитарных кодов --Х„.В блоках I умножения на константу осуществляется умножение вычетов ( соответствующие коэффициенты с приведением по модулю Pj, , т.е. на выходе i-ro блока 1. появится код величины . пп которая.поступая на модульный сумматор 2, суммируется с веЛичина1МИ с выходов других блоков 1 умножения на константу, В результате на выходе модульного сумматора 2 появится код величины

%Ф, V PHH/, РМ И

т.е. номер интервала, в котором находится на число N. В (п+1)-ом блоке 1 умножения на константу происходит умножение R|y на величину старшего модуля ц , а во втором сумматоре 5 к величине Rj/ft, прибавляется код вычета щ „ т.е« на выходах Ю второго сумматора 5 будет код числа N в позиционной системе счисления,

1

Параллельно с определением позиционного п)едставления числа N и номера интервала В. происходит вычисление ранта числа г., . По шинам 6 на

входы шифраторов 3 поступают коды б,- s . Шифраторы 3 по сигналу на вхо,,-

де л., определяют величину г. - I р

пп которая характеризует переполнение

при умножении вычета е.- на коэффици- ент Е. в соответствующем блоке 1 умножения на константу.

( lia вход (п+1 )-ого шифратора 3 поступает код величины переполнения ото всех (п-1 ) блоков 11 суммирования модульного сумматора 2, На выходе (п+1 )-ого шифратора 3 после окончания переходных процессов появится код величины

S

2jiJLL L

И + 1

. ни

т.е. код ранга числа г

N

ряды величин, снимаемых определяют знак числа.

Формула изобретения

I. Устройство для вычисления позиционных характеристик модулярного кода, содержащее модульный сумматор, первый, второй и третий блоки умножения на константу, входы которых явля- ются соответствующими входными шинами .устройства, а выходы подключены к со- ответствующим входам модульного сум- матора, первые выходы которого являют ся первой выходной шиной устройства, о т л и ,ч а ю щ е е с я тем, что, с целью расщирения функциональных возможностей путем обеспечения лреобра- зования числа из системы остаточных классов с произвольным -чкйпок п оснований в позиционную систему счисления, в него введены первый и второй сумматоры, (п-2 ) блока умножения на константу и (п+1 ) шифраторов, входы п шифраторов объединены с входами соответствующих блоков умножения на

30 . 5 Q

244797 8

константу, входы которых с четвертого по п-й являются соответствующими входными шинами устройства, а выходы подключены к соответствующим входам 5 модульного сумматора, первые и вторые выходы которого соединены с входами ,соответственно (п+1)-го блока умножения на константу и (п+1 )-го шифратора, выходы всех шифраторов под-

10 ключены к соответствующим входам первого сумматора, выходы которого являются второй выходной шиной устройства, выходы (п+1 )-го блока умножения на KOHCTaHYy и п-я входная шина под-

15 ключены соответственно к первым и вторым входам второго сумматора, выходы которого являются третьей выходной шиной устройства.

2.Устройство по п. 1, о т л и 20 чающееся тем, что модульный

сумматор выполнен из (п-1 ) блоков суммирования, объединенных в ярусы, входы блоков суммирования первого яруса являются соответствующими вхо- 25 дамн модульного сумматора, выходы блоков суммирования каждого яруса, кроме последнего, подключены к соответствующим входам блоков суммирования последующего яруса, выходы блока суммирования последнего яруса являются, первыми выходами модульного сумматора, дополнительные выходы всех блоков суммирования являются вторыми выходами модульного сумматора, t

3.Устройство по п. 2, отли

чающееся тем, что блок суммирования содержит дешифратор, шифратор, элемент ИЛИ и двоичный сумматор, первые и вторые входы которого являются соответствующими входами блока суммирования, выходы двоичного сумматора подключены к соответствующим входам дешифратора, выходы которого соединены с соответствующими входами шифратора и элемента ИЛИ, выходы которых являются соответственно выходами и дополнительным выходом блока суммирования.

Составитель о. Ревинский Редактор М. Товтин Техред Н.Вонкало Корректор Л. Патай

3927/58

Тираж 816 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,, г, Ужгород, ул. Проектная, 4

в

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Устройство для нормализации чисел в модулярной системе счисления | 1986 |

|

SU1332317A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| Устройство для вычисления позиционных характеристик модулярного кода | 1989 |

|

SU1608660A1 |

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2006 |

|

RU2318238C1 |

| Устройство для формирования позиционных характеристик непозиционного кода | 1981 |

|

SU968802A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2006 |

|

RU2313124C1 |

Изобретение предназначено для создания устройств обработки информации, использующих представления чисел в виде вычетов в системе остаточных классов. Цель изобретения - расширение функциональных возможностей путем обеспечения преобразования числа, представленного вычетами, в позиционную форму. Устройство содержит (п+1) блоков 1 умножения на константу, (п+1) шифраторов 3, первый и второй сумматоры 4, 5 и модульный сумматор 2, состояпщй из блоков 11 суммирования, в каждый из которых входят двоичньй сумматор, дешифратор, шифратор и элемент ИЛИ. Введение шифраторов 3 и сумматоров 4, 5 позволило получить ранг числа, представленного в системе остаточных классов по произвольному числу оснований, а также позиционное представление числа. 2 з.п.ф-лы, 2 ил. (О (Л 4 СО

| Авторское свидет,ельство СССР 554536, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования позиционных признаков непозиционного кода | 1980 |

|

SU898418A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-15—Публикация

1984-11-05—Подача