I . 12446652

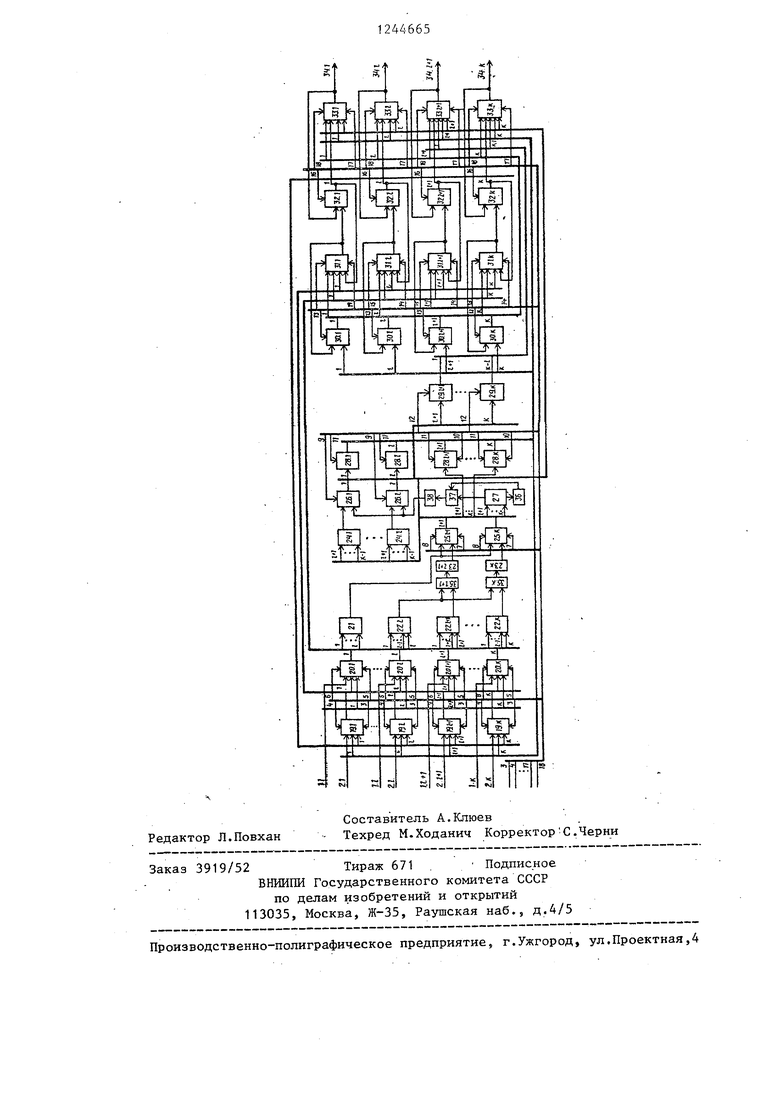

Изобретение относится к вычисли- четов второй группы, группу блоков тельной технике и предназначено для 23. 1+1, . ..,, 23, К деления нд 1-й мо- использования в быстродействующих дуль, блоки 24.1,...24 1 суммирования арифметических устройствах, работаю- вычетов первой группы, счетчики 25. щих в модулярном коде, для вьшолне- 5 l+t,...,25. К группы, сумматоры . ния операции, умножения дробей. 26,1,..,,26. 1 группы; блрк 27 сум- ,

Целью изобретения является расши- -мирования вычетов интервального ин- рение функщюнальных возможностей за декса; группу вспомогательных ре- счет выполнения умножения.гистров 28.1,...,28. К; угчножители На чертеже представлена схема вы- ш 29.1+1,...29 К на константу группы; числительного устройства в модуляр- умножители 30,1,.,.,30. К группы;

вспомогательные регистры 3151..,,31. ,К; сумматоры 32,1,...,32, К группы; выходные регистры 33.1,...33.К груп15 пы; вьжоды 34, устройства,

вьгчитатели 35, 1+1,.,.35.К группы, схему 36 сравнения с константой, „вычитатель 37, умножитель 38 на константу,

20 Перечень сигналов, подаваемых на тактрв;ые входы, представлен в таблице

ной системе счисления.

Вычислительное устройство в моду- лярной системе счисления содержит входы 1.1, . .. , 1 .К первого опер.анда и 2.1,...,2. К второго операнда устройства, тактовые входы 3-18 устройства, группы регистров 19.1,«..,19. К и 20.1,,,.,20. К соответственно второго и первого, операндов; формирователь 21 поправки Амербаева, блоки 22,. 1, . .., 22 К суммирования вы11 Вьщача кода , .,j+4,. Tg+Т,j+6,

2Tg+2T,,p +7

,

Вьщача кода

Вьщача кода .g+3, 1 g+Т|., Tg+Tj.j+6 Прием кода

.Е+з, .е+4, Tg+T.e+6

2Tp+2 r j +8

Вьщача кода Аналогично входу 14

Tj+3, Tj+4, Tj+Tg +5, 2T(+2T|.j+8

Вьщача кода

17 Прием кода , .+3, 2Tg+2Т|.+7,2Т +

+2Т. +8

18 Вьздача кода , Tj+T.j +5,2Tg+2T j +7,2Tg +

+2Vj,+8

Формирователь 21 поправки Амсрбае ва является известным устройством, осуществляющим формирование по входному остаточному коду числа поправки Амербаева для его интегральных характеристик модулярного кода, принимающего два значения: О или 1. В предлагаемом устройстве используется формирователь поправки Амербаева, как и в известном устройстве.

Блоки суммирования вычетов служат для вычисления за Т. тактов модульных линейных комбинаций из V вычетов ,

Блоки 23 деления вьшолняют деление 5 и 3 устройства, через входы

на mj, по соответствующему модулю. Блок 23 деления и cooтвeтcтвyюш й вычитатель 35 могут быть реализованы в виде одного постоянного запоминающего устройства. Схема 36 сравнения выполняет сравнение с константой (т -К+1-2). Умножитель 38 выпол- ня.ет умножение на константу С - Mj:,:: Мл

где М. П

m

, т„

., , ...,„.| - система попарно взаимно простых модулей, причем m /2р+К-1+4; р - фиксированное натуральное число.

Вычитатель 37 пр и единичном сигнале с выхода схемы 36 сравнения с константой вычитает из значения с выхода блока 27 константу т. Схема 36 сравнения с константой, умножитель 38 на константу, вычитатель 37 и сумматоры 26 могут быть реализованы в виде группы постоянных запоминающих устройств.

Вычислительное устройство в модулярной системе счисления осуществля „ А В ет умножение дробей -г- и -т- в

ответствии с формулой

l-(Ng(A).N,(B) +

Nt(A)i/B/Me +

-м7

Ne.(B)i/A/Mi М

), А

В

гдеЫ,(А) .j. N,(B) |-интервальные номера соответственно чисел А и В относительно системы модулей.

Основной вспомагательной операцией при умножении дробей является

округление чисел. При отом вычисление интервального NO (х) произвольного числа X производится по Формуле

NP (х) Те(х) + ), где F (х) - ядерный интервальный индекс числа, а 3(х) поправка Амербаева, соответствующая числу.

Вычислительное устройство в модулярной системе счисления работает следующим образом.

Модулярные коды (/S-, к. , . . . Jt) и ( |1, PJ , . . . , f) чисел А и В по сигналам, поступающим с тактовых входов

1.1,...3,1.К и 2.1,...,2.К записываются соответственно во входные регистры 20,1,...,20.К и 19,1,,..19.К, после чего начинается первый такт операции.

На первом такте по сигналу, поступающему с входа 6 устройства, цифра oL с выхода соответствующего регистра 20 передается в регистр 31 по сигналу приема кода, поступающему с входа 14. Одновременно с этим входные величины сс J. . ., fti подаются на входы формирователя 21 поправки Амербаева, а с,. . . , N, и поступают на входы блока 22j суммирования вычетов.

.Б ходе очередных Т тактов в блоке суммирования вычетов 22j определяется вычет - , представляющий собой цифру модулярного кода интервалького индекса Ig (А) числа.

На (Tg+1)-M такте вычет с Bfci- хода блока 22.1 поступает на входы вычитаемого вычитателей 35.1+1-35.К, на входы уменьщаемых которых с соответствующих блоков 22 подаются величины j . Результаты поступают на соответствующие блоки.23J, где делятся на 1-й модуль. Сформированная цифра j модулярного кода числа J (А) по сигналу приема кода с входа 7 пе- р едается в счетчик 25. j через информационный его вход. Одновременно с этим формирователь 21 поправки Амербаева по истечении ()-го такта

определяет поправку 6 (А), которая с выхода формирователя 21 подается на счетные входы счетчиков 25.1+ +1,...,25.К. В результате чего в них в соответствии сформируется модулярный код интервального номера Nj(А). По сигналу вьщачи кода, поступающему с входа 8, цифра ttf4-j с выхода соответствующего счетчика 25 подается

на j-e входы блоков суммирования вычетов 24.1 и 27, которые в течение очередных T.j тактов получают соответственно величины q| и q.

Кроме того на ()-M такте дифра 11„ по сигналу приема кода, пос- тупающему с входа 10, записывается в регистр 28.j и подается на вход модульного умножителя на константу 29.J, определяющего вычет .Mj/mj j , который по сигналу приема кода, поступающему с входа 17, поступает в регистр 33.j. Таким образом, по окончании ()-го такта в регистрах 33.1 будет находится модулярный код.(О,...О, hj,.,.,h)

На (Tj +3)-м такте по сигналу выдачи кода, поступающему с входа 18, с выхода регистра 33.1 вычет h поступает на первьй вход сумматора 32.1 на второй вход которого поступает цифра t. с выхода регистра 31.1 по сигналу выдачи кода, поступающему с входа 15. На выходе сумматора 321 появляется 1-я цифра . /ix -ьЦ/т числа, которая по сигналу приема кода , поступающему с входа 3, записы- вается в регистр 19.1.

На (Tp+T.f +2)-ом такте схема 36 сравнения с константой анализирует значение q . Если q больше или равен константе, то на вычитателе 38 из qj, вычитается т. Полученное значение умножается на константу умножителя 38 и складывается на соответствующем сумматоре 261 с qjj . Цифра et. числа Nj (А) с выхода сумматора 26.1 по сигналу выдачи кода, поступающему с входа 9, передается в регистр 281.

Благодаря конвейерной структуре формирователя 21 поправки Амербаева и блоков суммирования вьшетов, используемых в устройстве, вьшеописан- ные действия повторяются над числом В, начиная со второго такта операции. При этом в отличие от вышеизложенного содержимое ; счетчика 25.j, получаемое на (Т{+2)-м такте, в регистр 28.j не передается, а сохраняется в счетчике} а модулярный ко числа /В/м, формируемьй модульньши

сумматорами 32,132К на ()-м

такте по сигналу выдачи кода с выхода 16 передается в регистры 31,1,...,31.К. Модулярньш код ( р,, ) числа Nj(B) в регистрах 28.1 появляется на (Т.+Т| +3)-м такте. С этой целью на данном такте

10

20

25

446656содержимое счетчиков 25.j пересьша- ется в.регистры 28.j.

Предварительно на этом же такте

содержимое регистров 19.1,19 К

передается в регистры 31.1,...31.К, а coдepшiмoe регистров 28,1,...28.К пересыпается в регистры 19.1,...,19.К и поступает на вторые входы модульных умножителей 30,1,...,ЗО.К, на первые входы которых по сигналу вьщачи кода, поступающему с входа 15, подается содержимое ( if, ,. . . ,, ц) регистров 31. 1,. . . 31.К. Величина

/

/о - , , полученная модульным ножителем 30.1, по сигналу выдачи кода. Поступающему с входа 13, передается в регистр 331.

На следующем такте модульные умножители 30.15...,ЗО.К получают модулярный код числа N(B//A/A, ко- торьш с выходов умножителей передается в регистры 31.1,..i, 31.К.

На следующем такте операции сумматоры 32.1,...,32 К, складывая по мо-. дулям системы счисления содержимое регистров 31 . 1,. ... ,31 .К и 33.1, .-,.,33.К, поступающее соответственно на вторые и первые входы сумматоров , находят модульный код числа 30 С Ng(B) (А)/В/мИ„ который с вых:одов сумматоров передается во .. входные регистры 20,1,...,20.К.

. В ходе очередных . +2 тактов выполняется операция округления над числом С так, как это было описано выше.

Параллельно с этим на (Tj+T. + +6)-м такте содержимое (, ц) регистров 19,1s-.°5l9.K пересылается в регистры 31,1,...э31.К, а на следующем такте умножителя 30. I . . . ,30.К умножая по модулям,системы счис- , ления содержимое регистров 31.1, ...,31.К и ( Э,...,) регистров 28.1,...,28.К, находят модулярный код произведения Ng(А) Np(B), который с выходов умножителей передается в регистры 31.1,...,31.К. .

В соответствии с вышеуказанным по истечении ( +7)-го такта в регистрах 33.1,...,ЗЗ.К получают модулярный код числа N(С). На заключительном (2Tg+2Tj.g-|-8)-м такте операции содержимое регистров 33.1,...,ЗЗ.К поступает на первые входы сумматоров 32.1,...,32.К, на вторые входы которых из регистров 31.1,...,31.К подается код числа. Б результате на выходах с маторов

35

40

45

50

55

32.1,...,32.К формируется модульный код числителя искомой дроби, которы с выходов сумматоров передается в выходные регистры 33.1, . . . ЗЗ.К. Полученный модулярный код снимается с выходов 34.1,.. . ,34. К устройства - и на этом операции умножения дробей завершаются.

Формула изобретения

Вычислительное устройство в модулярной системе счисления, содержи группу регистров первого операнда, две группы блоков суммирования вычетов, блок суммирования вычетов интервального индекса,первую группу вспомогательных регистров, группу блоков деления на 1-й модуль (, k - число модулей), первую группу сумматоров, группу вычитателей, схему сравнения с константой, вычитатель, умножитель на константу, группу выходных регистров, причем входы вого операнда устройства соединены с первыми информационными входами соответствующих регистров первого операнда группы, выходы блоков суммирования вычетов первой группы соединены с входами первого слагаемого соответствующих сумматоров первой группы, входы второго слагаемого которых соединены с выходом умножителя на константу, вход которого соединен с выходом вычитателя, входы уменьшаемого и вычитаемого которого соединены соответственно с выходами блока суммирования вычетов интервального индекса и схемы сравнения с константой, вход схемы сравнения с константой соединен с выходом блока суммирования вычетов интервального индекса, выходы регистров первого операнда с первого по (1-1)-и группы соединены- с соответствующими входами блоков суммирования вычетов второй группы, 1-2 входы которых соединены соответственно с выходами регистров первого операнда с 1-го по k-й группы, выходы блоков суммирования вычетов вт рой группы, кроме младшего,соединены с входами уменьшаемого соответствующих вычитателей группы, входы вычитаемого которых соединены с выходом младшего блока суммирования вы четов группы, вькоды вычитателей группы соединены с входами соответствующих блоков деления на 1-й мо-

0

5

0

5

0

5

0

5

0

5

дуль группы, выходы выходных регистров группы являются выходом устройства, входы приема и выдачи информации . регистров первого операнда группы соединены соответственно с первым и вторым тактовыми входами устройства, входы приема и выдачи информации вспомогательных регистров группы соединены соответственно с третьим и четвертым тактовыми входами устройства, входы приема и выдачи информации выходных регистров группы соединены соответственно с пятым и шестым тактовыми входами устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения умножении , оно содержит группу регисуров второго операнда, формирователь поправки Амербаева, группу счетчиков, группу умножителей на константу, группу умножителей, вторую группу вспомогательных регистров вторую группу сумматоров, причем входы второго операнда устройства соединены с первыми информационными входами соответствующих регистров второго операнда группы, выходы которых соединены с вторыми информационными входами соответствующих регистров первого операнда группы, выходы регистров первого операнда с первого по 1-й соединены с соответствующими входами формирователя поправки Амербаева, выход которого соединен со счетными входами счетчиков группы, информационные входы KOTopbix соединены с выходами соответствующих блоков деления на 1-й модуль, выходы счетчиков группы подключены к соответствующим входам блоков суммирования вычетов первой группы, к соответствующим входам блока суммирования вычетов интервального индекса, выходы сумматоров первой группы и счетчиков группы соединены соответственно с информационными входами вспомогательных регистров первой группы, выходы счетчиков группы соединены с информационными входами умножителей на константу группы, выходы вспомогательных регистров первой группы соединены с вторыми информационными входами соответствующих регистров второго операнда группы и с первыми информационными входами соответствующих умножителей группы, вторые информационные входы которых соединены с выходами соответствующих вспомогательных регистров второй группы и с входами первого слагаемого соответствующих сумматоров второй группы, входы второго слагаемого которых соединены с выходами соответствующих выходных регистров группы, выходы умножителей группы совдинены с первыми информационными входами соответствующих выходных регистров группы и вспомогательных регистров второй группы, вторые, т-ретьи и чет- верть е информационные входы вспомо- Тательных регистров второй группы соединены соответственно с выходами регистров первого операнда группу,регистров второго операнда группы,и сумматоров второй группы, второй и третий информационные входы выходных регистро группы соединены соответственно с выходами сумматоров второй группы и вспомо- гателдзных регистров первой группы,чет вертые информационные входы выходных регистров с первого по 1-й группы .соединены с выходами соответствующих

4/)й6510

сумматоров первой группы, четвертые и пятые информационные входы выходных регистров с (1+1)-го по k-й группы соединены соответственно с выхог; дами счетчиков группы и умножителей на константу группы, третьи информа-. гщонные входы регистров первого операнда группы и регистров второго операнда, группысоединены с выходами

10 соответствующих сумматоров второй группы, входы приема и выдачи информации регистров второго операнда группы, входы приема и вьщачи информации счетчиков группы, входы выдачи инфор(5 мации сумматоров первой группы, входы выдачи информации умножителей на константу группы, входы выдачи информации умножителей группы, входы приема и выдачи информации вспомо20 гател ьных регистров второй гр уп- пы и входы вьщачи информации сумматоров второй группы соединены соответственно с тактовыми входами с седьмого по шест25 надцатьш устройства.

Редактор Л.Повхан

Составитель А.Клюев

Техред М.Ходанич Корректор С.Черни

Заказ 3919/52Тираж 671 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

Изобретение относится к .вычислительной технике и может быть использовано в быстродействующих арифметических устройствах, работающих в модулярном коде, для выполнения операции умножения дробей. Цель изобретения - расширение функциональных возможностей за счет вьшолнения умножения. Поставленная цель достигается за счет реализации конвейерного режима обработки операндов и проме- жуточного результата. 1 ил. ьо 4: 4; Од о: ел

| Устройство для умножения в системе остаточных классов | 1980 |

|

SU962942A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| .Авторское свидетельство СССР № 1190381, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-15—Публикация

1984-10-02—Подача