Изобретение относится к вычислительной технике и предназначено для использования в арифметических устро ствах с плавающей запятой, функциони рующих в модулярной системе счисления.

Цель изобретения - расширение области применения за счет умножения чисел, представленных в модулярном коде с плавающей запятой.

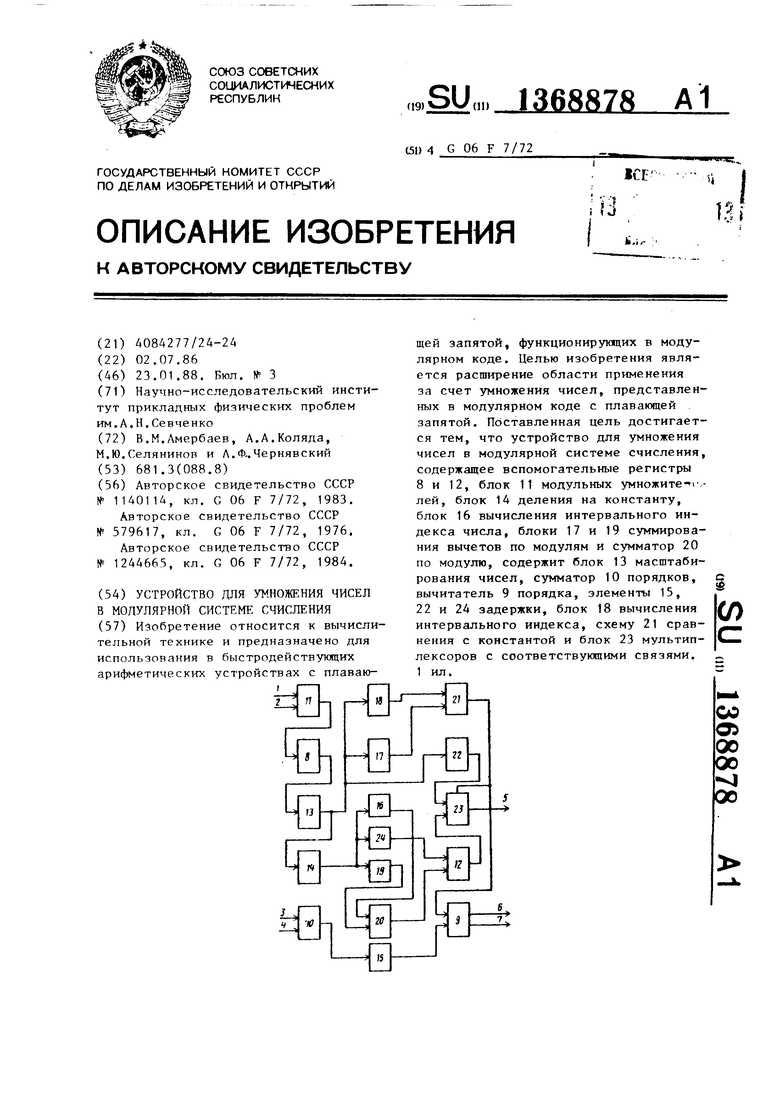

На чертеже представлена структурная схема устройства для умножения чисел в модулярной системе счисления

Устройство содержит входы 1 и 2 мантисс первого и второго сомножителей устройства, входы 3 и 4 порядков первого и второго сомножителей устройства, выход 5 мантиссы произведения устройства, выход 6 порядка про- изведения устройства, выход 7 признака переполнения устройства, первый вспомогательный регистр 8, вычитател 9 порядка, сумматор 10 порядков, бло 11 модульных умножителей, второй вспомогательный регистр 12, блок 13 масштабирования чисел, блок 14 деления на константу, первый элемент 15 задержки, первый блок 16 вычисления интервального индекса числа, блок 17 суммирования вычетов по (1-1)-му модулю, второй блок 18 вычисления интервального индекса числа, блок 19 суммирования вычетов по 1-му модулю, сумматор 20 по модулю, схему 21 срав нения с константой, второй злемент 22 задержки, блок 23 мультиплексоров, третий элемент 24 задержки.

Блок 13 масштабирования чисел (реализован как в известном устройстве) осуществляет за Т(Т+3) такта деление входного числа AED, заданного модулярным кодом на константу М, где D ,,. . . ,рМ(., диапазон изменения чисел; М П гл.; р - фик е:

сированное натуральное число, выбираемое из условия тпр 2р+1-2; т,. . .т - система попарно простых модулей, m 2p+k-2.

Результатом указанной операции является модулярный код числа А , являющегося опенкой дроби А/М, Т ,,k.

Блок 14 деления на константу может быт реализован на k-1 постоянных запоминающих устройствах, в память -го пз которых по адресу X; заппсывается константа / ,

X,, Y,,1m;-l i 11-1,

l-t-1,...,k.

Блок 18 вычисления интервального индекса числа служит для определени по входному модулярному коду (oij, ...,o6g) числа А, /Afm;, машиного интервального индекса числа по формуле

/M;j., с(;/га;/

/ +

т;/ m,

е-1

T(A)/i:

ir I

г

. IM

пе/mf

(1)

м /™« и имеет конвейерную структуру.

Блок 17 суммирования вычетов имеет Tg каскадную конвейерную структуру и осуществляет сложение за тактов (1-1) вычетов по модулю т., с формированием числа переполнений. Блок 17 суммирования вычетов на своем входе формирует величину

™enei;,e-i i1

ре-.

га

1

т;

(2)

/о1;МГ | /

m;

М

,М

Второй элемент 22 задержки осуществляет задержку на (Tj+2) тактов и представляет собой цепочку из (T«+2) последовательно соединенных регистров.

Блок 16 вычисления интервального индекса полностью аналогичен блбКу 18 вычисления интервального индекса числа и за Tg тактов находит машинный интервальный индекс 1(А) числа.

Блок 19 суммирования вычетов осуществляет сложение за Т тактов (1-1) вычетов по модулю т без формирования числа переполнений. Блок 19 суммирования вычетов на своем выходе формирует величину

,е.,.о,(,., /mg (3)

и имеет Tg каскадную конвейерную структуру.

Сумматор 20 по модулю является сумматором табличного типа, реализован с помощью постоянного запоминающего устройства и вычисляет ве 7ичину 1 /1 М{., -ьХ/та по входным X и I ,

где

если Т Р

в противном случае Первый элемент 15 задержки осуществляет задержку на (T+Tj-t-5) тактов.

.,

313688784

Трети} элемент 24 задержки осуще- сы результата принимается дробь С/М.

ствляет задержку на Tj тактов и представляет собор цепочку из Т. последо-) вательно соединенных регистров.

Схема 21 сравнения с константой реализуется на основе постоянного запоминающего устройства, к выходу которого подключен двухтактный элемент задержки и формирует по величинам I и X значение

П, если , p-l

0, в противном случае Вычитатель 9 порядка реализуется на основе постоянного запоминающего устройства, в память которого по адресу Я +2 записывается набор констант , (0, где ;) р, ,

U 1ТЗГТТЛГЛ TITJIT ч 1- / TT-tFTT i

(5)

$7

(4)

) -1,

j Г1 , -q ,q о, в противном слу

в противном случае

случае

Устройство осуществляет умножение чисел (a),- (а) (Е.),

При этом в первом случае порядок результата определяется соотношением

V (с) 5(а) + (Е,), а во втором - -)(с) (а)+(Ь)-1.

Рассмотрим, как работает устройство для умножения чисел в модулярной системе счисления.

10 На первом такте работы модулярные коды (о,, .. . ,ебк) числителя А мантиссы (ц(а) и. (3,,. . . ,/5k) числителя В мантиссы |li(b), (ci; (A)m; , , (A)m; со входов 1 и 2 устройства подаются со15 ответственно на первый и второй входы блока 11 модульных умножителей, который получает модулярный код (у,,..., у) произведения , записывающийся во вспомогательный регистр 8.

20 Одновременно с этим двоичные коды порядков ) первого операнда и -5 (Ь) второго операнда с входов 3 и 4 устройства соответственно поступают на первый и второй входы сумматора 10

(Ь), представленных в форме с пла- 25 порядка, который определяет величину

вающей запятой, где m(a)A/Mf и p(b) B/|U - мантисс ы, а и ), (Ь) - порядки операндов а и Ь соответственно, -q i-3 (а) , -О ({)feq ; А,В е D.

Модули системы счисления выбираются таким образом, чтобы произведение любых двух чисел из диапазона D не выходило за пределы диапазона модулярной системы счисления D, где

...,м,-1} ,

М.Ьр.М, .

Условие нормализации в рассматриваемой модулярной системе счисления для чисел а и Ь имеет вид

N(A), N(B)p-l, (6) где N(A) и N(b) - неточные интервальные номера чисел А и В, удовлетворяг ющие следующим соотношениям: N(A)l(A)+p(A); N(b)l(6)+ft(&),

где 1(А), ТСЮ - интервальные индексы, ар (А) и р (В) - неточные ранги соответственно чисел А и В. Если неточный интервальный номер N(C) числа С, являющегося оценкой дроби, С A B-S/M.AB/Mf, выходит за пр еделы интервала (-р-1, р-1), то число С(П (S - основание характеристики, ). В этом случае дробь c /Mg, где C A B/Mj является нормализованной и, следовательно, представляет собой мантиссу результата, в противном слугтае в качестве (с) -5(а) + (Ь), передающуюся в первый элемент 15 задержки.

На втором такте работы модулярный код числа С с выхода вспомогательного

30 регистра 8 подается на вход блока 13 масштабирования чисел, который по истечении (Т+4)-го такта работы устройства на своем выходе формирует модулярный код величины С-С/Мр., (у,

35 ) передающейся во второй элемент 22 задержки.

На (Т+5)-м такте работы первые 1

IА

остатков модулярного кода числа С 40 передаются на вход блока 18 вычисления интервального индекса числа, а первые (1-1) остатков модулярного кода числа С передаются на вход блока 17 суммирования вычетов. 45 Блок 18 вычисления интервального индекса числа и блок 17 суммирования вычетов в течение очередных Т тактов, считая текущий, вычисляют соответственно величины 1(С) и р., (С) 50 (формулы (1) и (2), Кроме этого, на д (Т+5)-м такте модулярный код числ§ С передается в блок 14 деления на константу, который на своем выходе формирует остатки числа С по модулям

55 Ь УР- «У е + которые поступают на вход третьего элемента 24 задержки.

На ()-м такте работы остатки f-i к передаются на вход

При этом в первом случае порядок результата определяется соотношением

(с) 5(а) + (Е,), а во втором - -)(с) (а)+(Ь)-1.

Рассмотрим, как работает устройство для умножения чисел в модулярной системе счисления.

На первом такте работы модулярные коды (о,, .. . ,ебк) числителя А мантиссы (ц(а) и. (3,,. . . ,/5k) числителя В мантиссы |li(b), (ci; (A)m; , , (A)m; со входов 1 и 2 устройства подаются соответственно на первый и второй входы блока 11 модульных умножителей, который получает модулярный код (у,,..., у) произведения , записывающийся во вспомогательный регистр 8.

Одновременно с этим двоичные коды порядков ) первого операнда и -5 (Ь) второго операнда с входов 3 и 4 устройства соответственно поступают на первый и второй входы сумматора 10

порядка, который определяет величину

(с) -5(а) + (Ь), передающуюся в первый элемент 15 задержки.

На втором такте работы модулярный код числа С с выхода вспомогательного

регистра 8 подается на вход блока 13 масштабирования чисел, который по истечении (Т+4)-го такта работы устройства на своем выходе формирует модулярный код величины С-С/Мр., (у,

) передающейся во второй элемент 22 задержки.

На (Т+5)-м такте работы первые 1

IА

остатков модулярного кода числа С передаются на вход блока 18 вычисления интервального индекса числа, а первые (1-1) остатков модулярного кода числа С передаются на вход блока 17 суммирования вычетов. Блок 18 вычисления интервального индекса числа и блок 17 суммирования вычетов в течение очередных Т тактов, считая текущий, вычисляют соответственно величины 1(С) и р., (С) формулы (1) и (2), Кроме этого, на д (Т+5)-м такте модулярный код числ§ С передается в блок 14 деления на константу, который на своем выходе формирует остатки числа С по модулям

Ь УР- «У е + которые поступают на вход третьего элемента 24 задержки.

На ()-м такте работы остатки f-i к передаются на вход

блока 16 вычисления интервального индекса числа, а набор остатков (|f,, ...,j ., ) передается на вход блока 19 суммирования вычетов, которые в течение очередных Т. тактов, считая текущий, вычисляют с оответственно величины 1(С ) и у. (формулы (1) и (3).

На (T+Tj-t-5)-M такте работы вели- чинь I (с) с выхода блока 18 вычисления интервального индекса числа и Р(., (с) с выхода блока 17 суммирования вычетов поступают на входы схемы 21 сравнения с константой.

На (T+Tj+6)-M такте работы величины I(c ) с выхода блока 16 вычисле 4

ния интервального индекса и у ,, с выхода блока 19 суммирования вычетов поступают соответственно на первый и второй входы сумматора 20 по модулю. Сумматор 20 по модулю определяет 1-й остаток числа С j p который совместно со значением с выхода элемента 24 задержки поступает на вход вспомогательного регистра 12, где будет сформирован модулярный код

/ А

(УК) числа с .

На заключительном (Т )-м такте работы устройства величина Q с выхода схемы 21 сравнения с константой поступает на управляющий вход блока 23 мультиплексоров, на первый и второй информационные входы которого поступают соответственно

А

величины С .и С . Одновременно поступает на вход заема вычитателя 9 порядка, на информационньй вход которого с выхода первого элемента 15 задержки поступает величина -(с).

В случае, если , на выходе 5 мантиссы произведения и выходе 6 порядка произведения устройства будут получены соответственно величины С и-(с)-, а в случае, еслиГг 1, величины С и 5(с). С выхода переполнения вычитателя 9 порядка на выход 7 устройства будет считан признак переполнения СО (формула (5) .

Из приведенного описания видно, что выполнение одной операции в устройстве для умножения чисел в модулярной системе счисления занимает (Т+Т,-t-7) тактов, при этом пропускная способность устройства составляет одну операцию умножения в одлн такт. Формула изобретения

Устройство для умножения чисел в модулярной системе счисления, содер1368878

жащее два вспомогательных регистра, , блок модульных умножителей, блок деления на константу, первый блок вы- 1 числения интервального индекса числа, блок суммирования вычетов по (1-1)-му модулю, блок суммирования вычетов по 1-му модулю и сумматор по модулю (1 - целое число, , К - количе- 10 ство модулей системы счисления), цри- чем входы мантисс первого и второго сомножителей устройства соединены соответственно с входами первого и второго сомножителей блока модульных 15 умножителей, выход произведения которого соединен с входом первого вспомогательного регистра, входы первого блока вычисления интервального индекса числа и блока суммирования выче- 20 тов по 1-му модулю объединены, выходы первого блока вычисления интервального индекса и блока суммирования вычетов по 1-му модулю соединены соответственно с входами первого и второго

25 слагаемых сумматора по модулю, отличающее ся тем, что, с целью расширения области применения за счет умножения чисел, представленных в модулярном коде с плавающей

30 запятой, оно содержит блок масштабирования чисел, сумматор порядков, вы- читатель порядка, три элемента задержки, второй блок вычисления интервального индекса числа, схему сравне35 ния с константой и блок мультиплексоров, причем входы порядков первого и второго сомножителей устройства соединены соответственно с входами первого и второго слагаемых суммато40 ров порядков, выход которого подключен к входу первого элемента задержки, выход первого вспомогательного регистра соединен с входом блока масштабирования чисел, выход которого

45 Соединен с входами второго элемента задержки, второго блока вычисления интервального индекса числа, блока суммирования вычетов по (1-1)-му модулю и блока деления на константу,

QQ выход которого соединен с входами блока суммирования вычетов по 1-му модулю и третьего элемента задержки, выходы разрядов второго блока вычисления интервального индекса числа и

gg блока суммирования вычетов по (1-1)- му модулю соединены соответственно с входами разрядов схемы сравнения с константой, выход которой соединен с управляющим входом блока мультиплек713688788

соров и с входом заема вычитателя по-гательного регистра соединены соотрядка, информационный вход котороговетственно с первым и вторым информасоединен с выходом первого элементационными входами блока мультиплексозадержки, выход третьего элемента за- ров, выход которого является выходом

держки и выходы разрядов сумматорамантиссы произведения устройства, выпо модулю соединены соответственно сходы разности и переполнения вычитавходами разрядов второго вспомога-теля порядка являются соответственно

тельного регистра, выходы второговыходом порядка произведения и выхоэлемента задержки и второго вспомо- IQдом признака переполнения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для нормализации чисел в модулярной системе счисления | 1986 |

|

SU1332317A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1985 |

|

SU1280625A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для нормализации чисел в модулярном коде | 1984 |

|

SU1242942A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих арифметических устройствах с плаваю( 1 щей запятой, функционирующих в модулярном коде. Целью изобретения является расширение области применения за счет умножения чисел, представленных в модулярном коде с плавающей запятой. Поставленная цель достигается тем, что устройство для умножения чисел в модулярной системе счисления, содержащее вспомогательные регистры 8 и 12, блок 11 модульных умножите г,- лей, блок 14 деления на константу, блок 16 вычисления интервального индекса числа, блоки 17 и 19 суммирования вычетов по модулям и сумматор 20 по модулю, содержит блок 13 масштабирования чисел, сумматор 10 порядков, вычитатель 9 порядка, элементы 15, 22 и 24 задержки, блок 18 вычисления интервального индекса, схему 21 сравнения с константой и блок 23 мультиплексоров с соответствующими связями. 1 ил. (Л со а 00 00 00

| УСТАНОВКА ДЛЯ КАРБЮРИРОВАНИЯ ВОЗДУХА С АВТОМАТИЧЕСКИМ ВКЛЮЧЕНИЕМ ВОЗДУШНОГО НАСОСА | 1924 |

|

SU1140A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1975 |

|

SU579617A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство в модулярной системе счисления | 1984 |

|

SU1244665A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-23—Публикация

1986-07-02—Подача