Изобретение относится к ядерной электронике и может быть использовано в спектрометрах заряженных частиц с полупроводниковыми детекторами.

Целью изобретения является повышение быстродействия за счет увеличения числа обрабатываемых импульсов в единицу времени при одновременном увеличении точности получаемой информации.

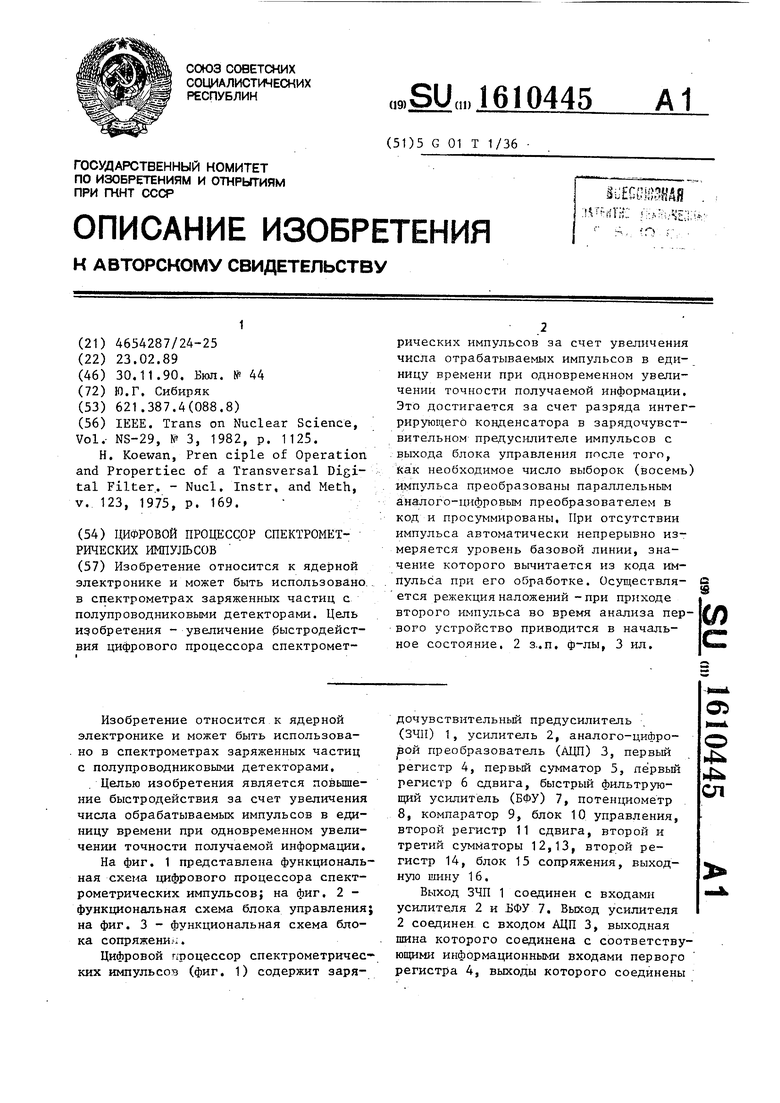

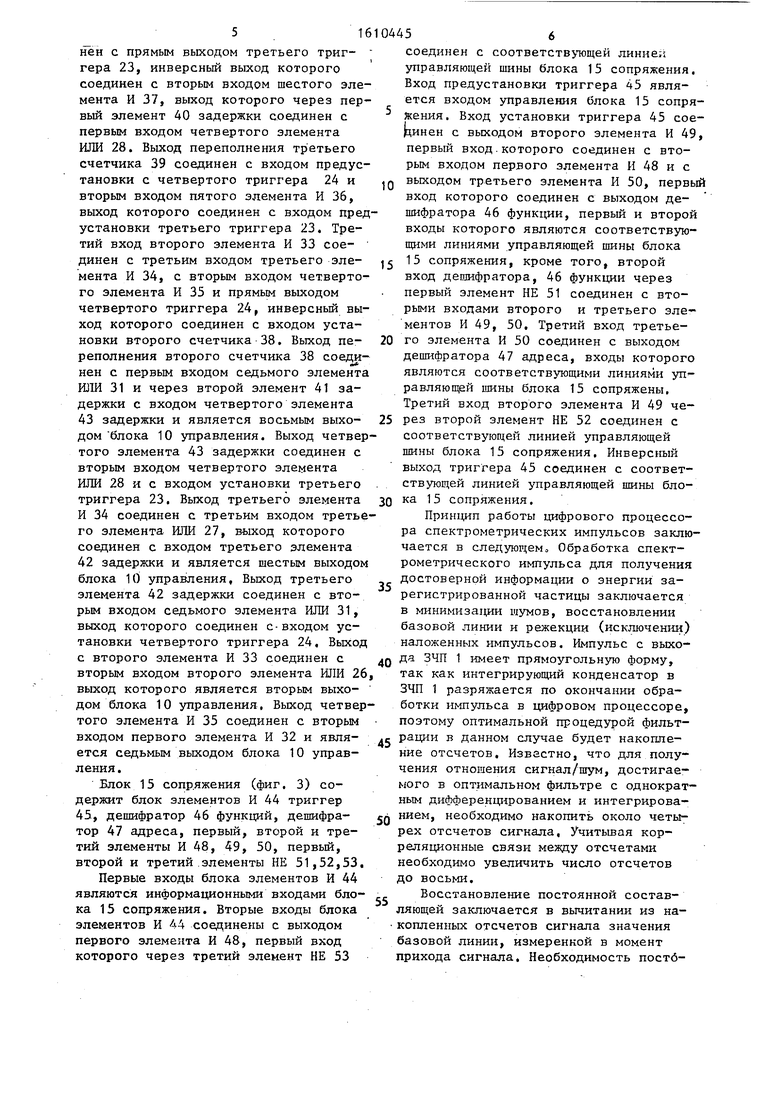

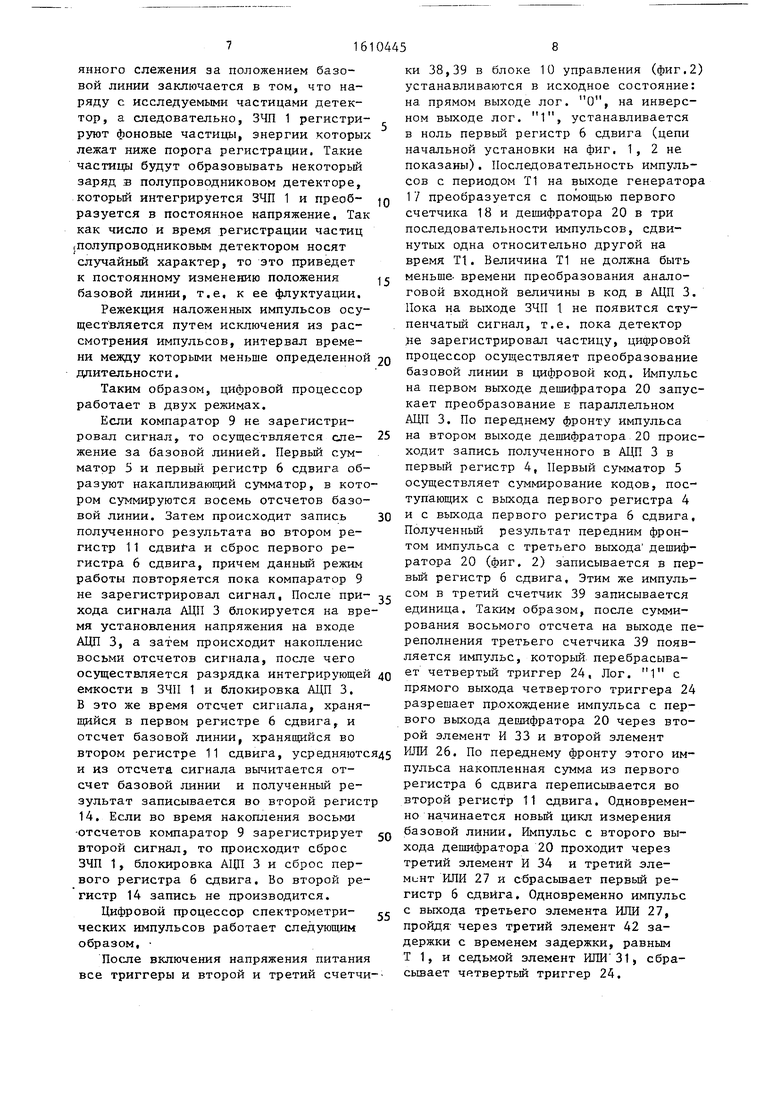

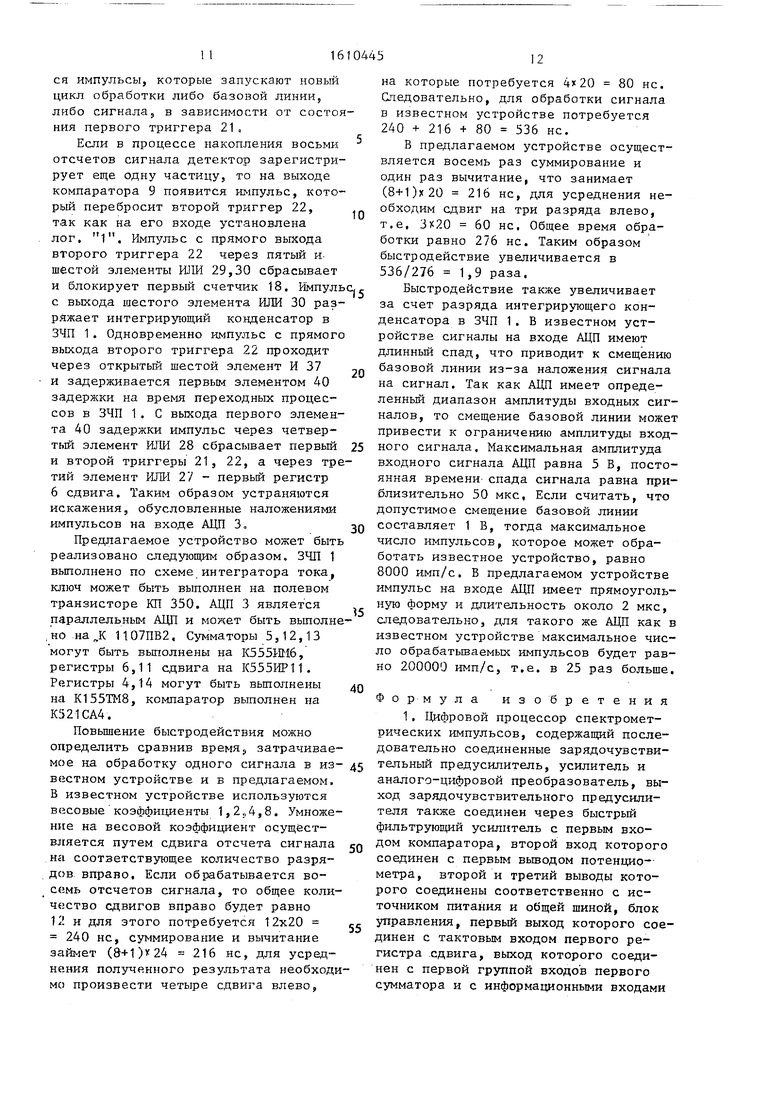

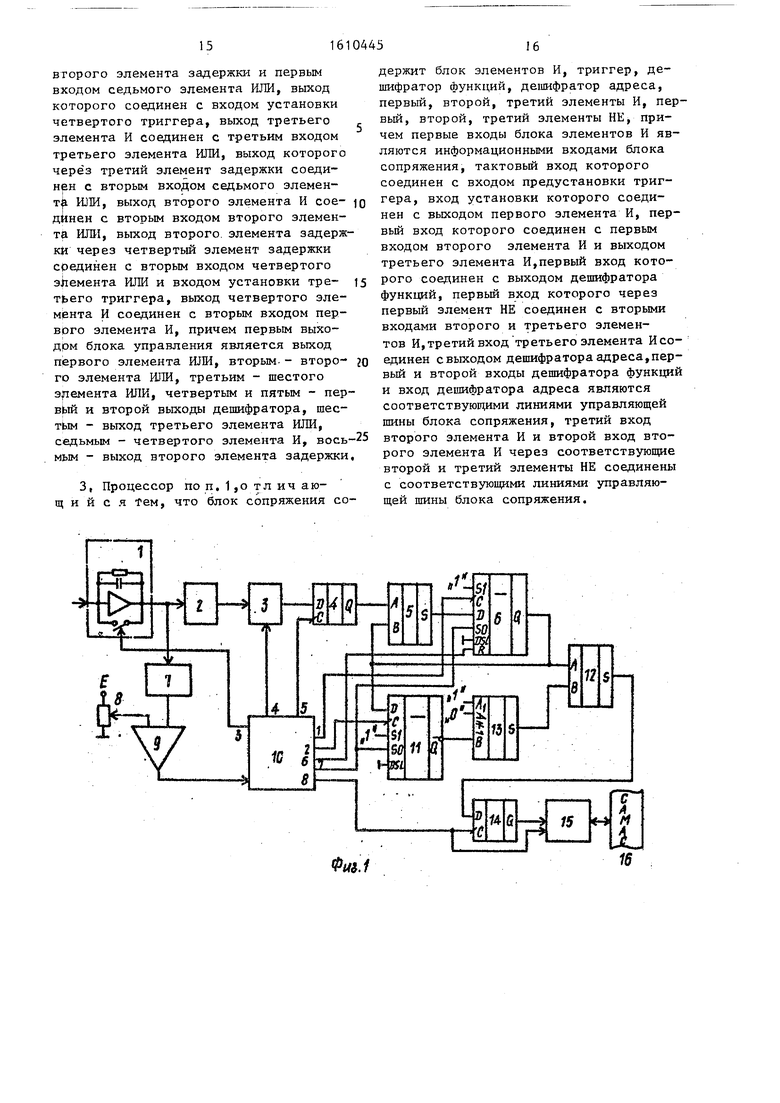

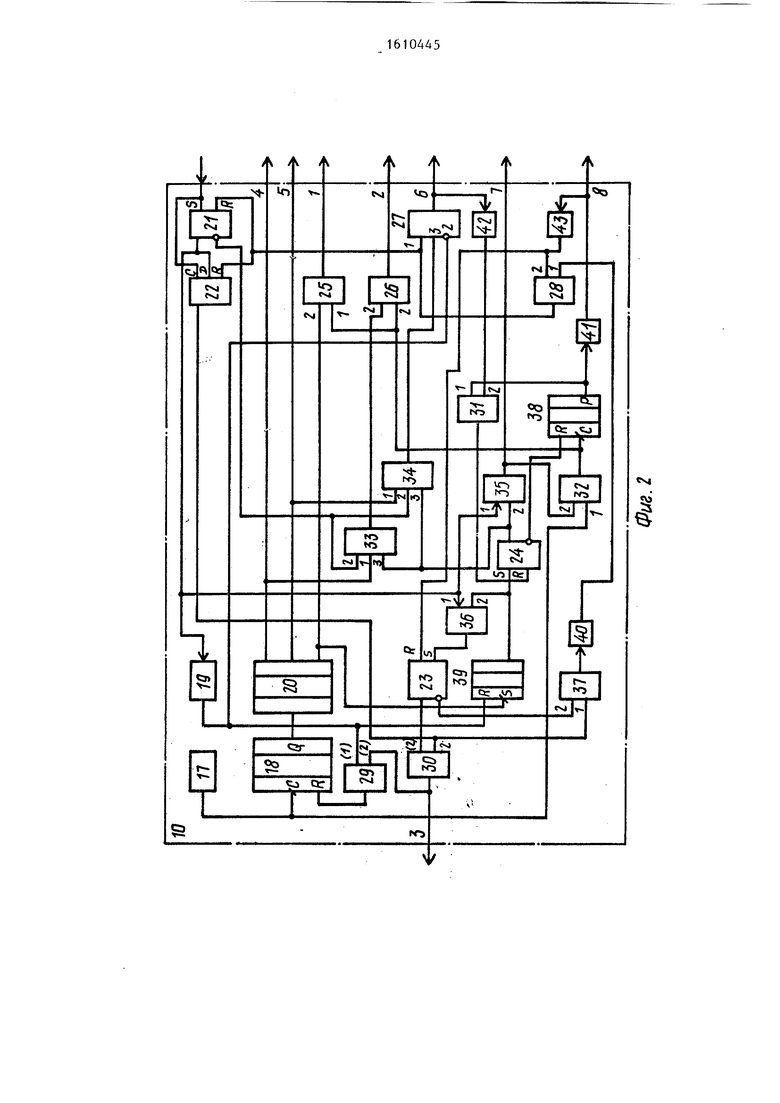

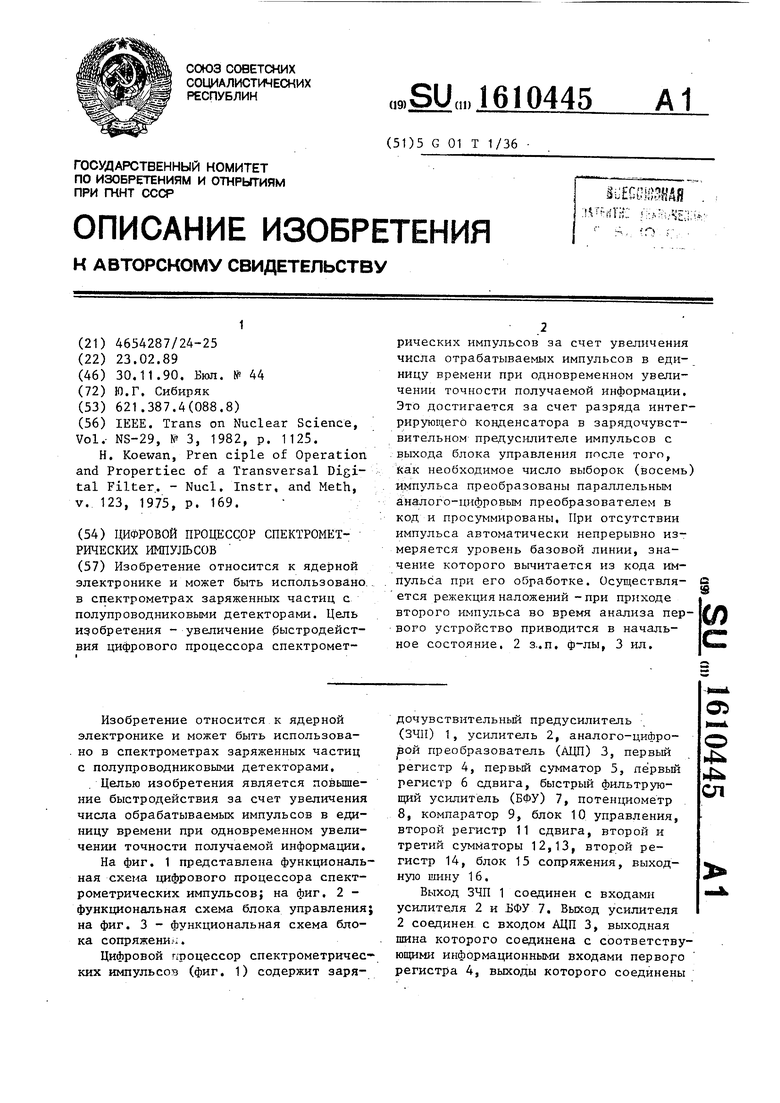

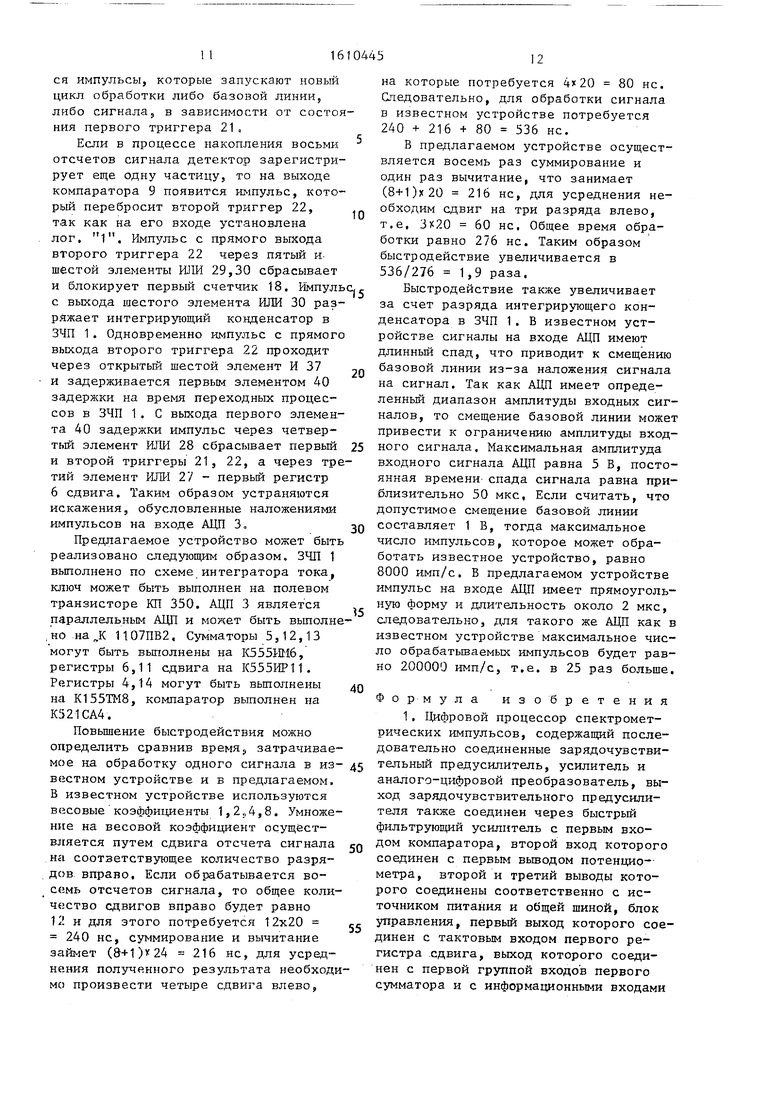

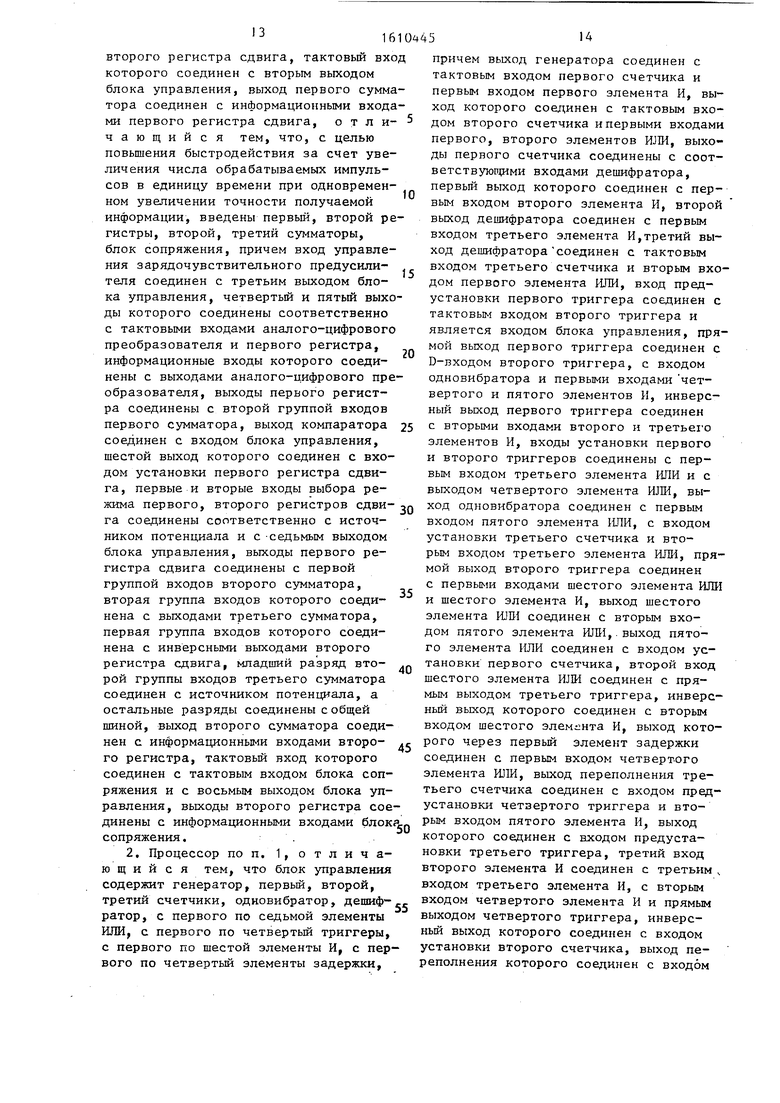

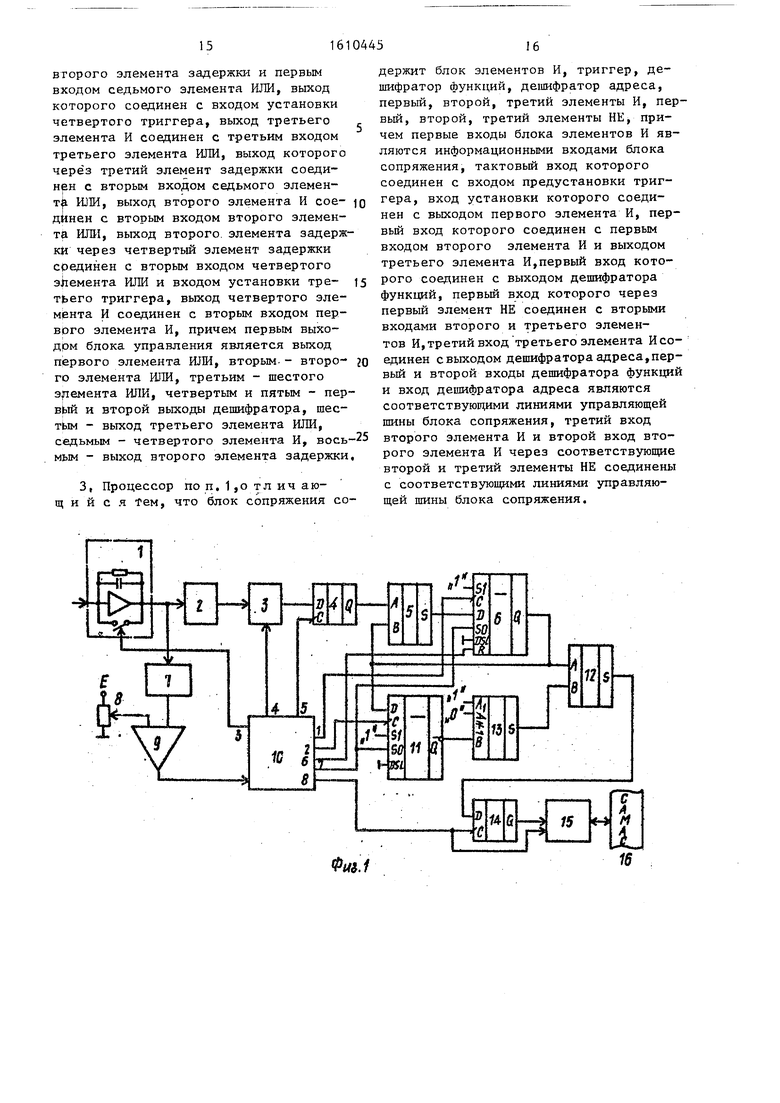

На фиг. 1 представлена функциональная схема цифрового процессора спектрометрических импульсов; на фиг, 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема блока сопряжение;.

Цифровой гфоцессор спектрометрических импульсов (фиг. 1) содержит зарядочувствительньй предусилитель (ЗЧП) 1, усилитель 2, аналого-цифро- рой преобразователь (АЦП) 3, первьй регистр 4, первый сумматор 5, первьй регистр 6 сдвига, быстрый фильтрующий усилитель (БФУ) 7, потенциометр 8, компаратор 9, блок jQ управления, второй регистр 11 сдвига, второй и третий сумматоры 12,13, второй регистр 14, блок 15 сопряжения, выходную шину 16,

Выход ЗЧП 1 соединен с входами усилителя 2 и БФУ 7. Выход усилителя 2 соединен с входом АЦП 3, выходная шина которого соединена с соответствующими информационными входами первого регистра 4, выходы которого соединены

У

сл

с первой группой входов первого сумматора 55 выходы которого соединены с информационными входами первого регистра 6 сдвига, выходы которого соединены с второй группой входов первого сумматора 5, с первой группой входов бторого сумматора 12 и с информационными входами второго регистра 11 сдвига.

Выход БФУ 7 соединен с первьм входом компаратора 9, второй вход которого соединен с первым выводом потенциометра 8, второй и третий выводы которого соединены соответственно с общей шиной и источником питания. Выход компаратора 9 соединен с входом блока 10 управления, первый и второй выходы которого соединены с тактовыми входами первого и второго регистров 6,11 сдвига.

Вход управления ЗЧП 1 соединен с третьим выходом блока 10 управления, четвертый и пятьш вьжоды которого соединены соответственно с тактовыми вхо дами АЦП 3 и первого регистра 4.

Младший разряд первой группы входов третьего сумматора 13 соединен с источником потенциала Лог. 1, остальные разряды соединены с общей ши- ной. Выходы второго регистра 11 сдвига соединены с второй группой входов третьего сумматора 13, выходы которого соединены с второй группой входов второго сумматора 12, выходы которого соединены с информа11(ионными входами второго регистра 14, тактовый вход которого соединен с тактовым входом блока 15 сопряжения. Первые входы выбора режима первого и второго ре- гистров сдвига 6 и 11 соединены с источником потенциала лог. 1. Вход установки первого регистра 6 сдвига соединен с шестым выходом блока 10 управления.

Вторые входы выбора режима первого и второго регистров 6,IT сдвига соединены с седьмым выходом блока ТО управления, входы информации при сдвиге данных влево первого и второго регист j)OB 6j 11 сдвига соединены с общей шиной. Выходы второго регистра 14 соединены с входами блока 15 сопряжения, выходы и входы управления которого соединены с соответствующими линиями выходной шины 16. Тактовый вход второго регистра 14 соединен с восьмым выходом блока 10 управления.

Q

(5 0

5

Q -., д д5

0

5

Блок 10 управления (фиг. 2) содержит генератор 17, первьш счетчик 18, одновибратор 19, дешифратор 20, пер- вьй, второй, третий и четвертый триггеры 21 - 24, первый - седьмой элементы ИЛИ 25-31, первый - шестой элементы И 32 - 37, второй и третий счетчики 38, 39, первый, второй, третий и четвертый элементы 40 - 43 задержки. Выход генератора 17 соединен с тактовым входом первого счетчика 18 и первым входом первого элемента И 32, выход которого соединен с тактовьм входом второго счетчика 38 и первыми входами первого и второго элементов ИЛИ 25, 26. Выходы первого счетчика 18 соединены с соответствующими входами дешифратора 20, первьй выход которого соединен с первым входом второ-. го элемента И 33 и является четвертым выходом блока 10 управления. Второй выход дершфратора 20. соединен с первым входом третьего элемента И 34 и является пятым выходом блока .10 управления. Третий выход дешифратора 20 соединен с тактовым входом третьего счетчика 39, вторым входом первого элемента ШШ 25, выход которого является первьм выходом блока 10 управления. Вход предустановки первого триггера 21 соединен с тактовым входом второго триггера 22 и является входом блока 10 управления, Прямой выход первого триггера 21 соединен с входом второго триггера 22, с входом одновибратора 19 и первыми входами четвертого и пятого элементов И 35, 36, Инверсньш выход первого триггера 21 соединен с вторыми входами второго и третьего элементов И.33, 34. Входы установки первого и второго триггеров :21, 22 соединены с первым входом тре- 1тьего элемента ИЛИ 27 и с выходом четвертого элемента РШИ 28. Выход одно- вибратора 19 соединен с первым входом пятого элемента ИЛИ 29, с входом установки третьего счетчика 39 и вторым входом третьего элемента ИЛИ 27. Прямой выход второго триггера 22 соединен с первыми входами шестого элемента ИЛИ 30, шестого элемента И 37. Выход шестого элемента ИЛИ 30 соединен с вторым входом пятого элемента ИЛИ 29 и является третьии выходом блока 10 управления. Выход пятого элемента ИЛИ 29 соединен с входом уста- 1новки первого счетчика 18. Второй вход шестого элемента ИЛИ 30 соеди-

51

нен с прямым выходом третьего триг- гера 23, инверсный выход которого соединен с вторым входом шестого элемента И 37, выход которого через первый элемент 40 задержки соединен с первым входом четвертого элемента ИЛИ 28. Выход переполнения третьего счетчика 39 соединен с входом предустановки с четвертого триггера 24 и вторым входом пятого элемента И 36, выход которого соединен с входом преустановки третьего триггера 23. Третий вход второго элемента И 33 сое- динен с третьим входом третьего элемента И 34, с вторым входом четвертого элемента И 35 и прямым выходом четвертого триггера 24, инверсный выход которого соединен с входом установки второго счетчика 38. Выход переполнения второго счетчика 38 соединен с первым входом седьмого элемент ИЛИ 31 и через второй элемент 41 задержки с входом четвертого элемента 43 задержки и является восьмым выходом блока 10 управления. Выход четветого элемента 43 задержки соединен с вторым входом четвертого элемента ИЛИ 28 и с входом установки третьего триггера 23. Выход третьего элемента И 34 соединен с третьим входом третьго элемента ИЛИ 27, выход которого соединен с входом третьего элемента 42 задержки и является шестым выходо блока 10 управления, Выход третьего элемента 42 задержки соединен с вторым входом седьмого элемента ИЛИ 31, выход которого соединен с-входом установки четвертого триггера 24, Выхо с второго элемента И 33 соединен с вторым входом второго элемента ИЛИ 2 выход которого является вторым выходом блока 10 управления. Выход четветого элемента И 35 соединен с вторым входом первого элемента И 32 и является седьмым выходом блока 10 управления .

Блок 15 сопряжения (фиг. 3) содержит блок элементов И 44 триггер 45, дешифратор 46 функций, дешифратор 47 адреса, первый, второй и третий элементы И 48, 49, 50, первьш, второй и третий .элементы НЕ 51,52,53

Первые входы блока элементов И 44 являются информационными входами блока 15 сопряжения. Вторые входы блока элементов И 44 соединены с выходом первого элемента И 48, первый вход которого через третий элемент НЕ 53

10

15

20

25

ЗО

соединен с соответств тощей линие;; управляющей шины блока 15 сопряжения. Вход предустановки триггера 45 является входом управления блока 15 сопряжения. Вход установки триггера 45 соединен с выходом второго элемента И 49, первый вход.которого соединен с вторым входом первого элемента И 48 и с выходом третьего элемента И 50, первьй вход которого соединен с выходом дешифратора 46 функции, первый и второй входы которого являются соответствую- линиями управляющей шины блока 15 сопряжения, кроме того, второй вход дешифратора, 46 функции через первый элемент НЕ 51 соединен с вторыми входами второго и третьего элементов И 49, 50, Третий вход третьего элемента И 50 соединен с выходом дешифратора 47 адреса, входы которого являются соответствующими линиями уп-- равляющгй шины блока 15 сопряжены. Третий вход второго элемента И 49 через второй элемент НЕ 52 соединен с соответствующей линией управляющей шины блока 15 сопряжения. Инверсный выход триггера 45 соединен с соответствующей линией управляющей шины блока 15 сопряжения.

Принцип работы цифрового процессора спектрометрических импульсов заключается в следуюр емо Обработка спектрометрического импульса для получения достоверной информации о энергии зарегистрированной частицы заключается в минимизацией шумов, восстановлении базовой линии и режекции (исключении) наложенных импульсов. Импульс с выхо- д0 да ЗЧП 1 имеет прямоугольную форму, так как интегрирующий конденсатор в ЗЧП 1 разряжается по окончании обработки импульса в цифровом процессоре, поэтому оптимальной процедурой фильт- дс рации в данном случае будет накоппе- ние отсчетов. Известно, что для получения отношения сигнал/шум, достигаемого в оптимальном фильтре с однократным диффepeнцIipoвaниeм и интегрированием, необходимо накопить около четырех отсчетов сигнала. Учитывая корреляционные связи между отсчетами необходимо увеличить число отсчетов до восьми.

Восстановление постоянной составляющей заключается в вычитании из накопленных отсчетов сигнала значения базовой линии, измеренной в момент прихода сигнала. Необходимость постб35

0

5

янного слежения за положением базовой линии заключается в том, что наряду с исследуемыми частицами детектор, а следовательно, ЗЧП 1 регистрируют фоновые частицы, энергии которых лежат ниже порога регистрации. Такие частицы будут образовывать некоторый заряд в полупроводниковом детекторе, который интегрируется ЗЧП 1 и преобразуется в постоянное напряжение. Так как число и время регистрации частиц (Полупроводниковым детектором носят случайный характер, то это приведет к постоянному изменению положения базовой линии, т.е. к ее флуктуации.

Режекция наложенных импульсов осу- щест вляется путем исключения из рассмотрения импульсов, интервал времени между которыми меньше определенной длительности.

Таким образом, цифровой процессор работает в двух режимах.

Если компаратор 9 не зарегистрировал сигнал, то осуществляется слежение за базовой линией. Первьй сумматор 5 и первый регистр 6 сдвига образуют накапливающий сумматор, в котором суммируются восемь отсчетов базовой линии. Затем происходит запись полученного результата во втором регистр 11 сдвига и сброс первого регистра 6 сдвига, причем данньш режим работы повторяется пока компаратор 9 не зарегистрировал сигнал, После прихода сигнала АЦП 3 блокируется на время установления напряжения на входе АЦП 3, а затем происходит накопление восьми отсчетов сигнала, после чего осуществляется разрядка интегрирующей емкости в ЗЧП 1 и блокировка АЦП 3. В это же время отсчет сигнала, хранящийся в первом регистре 6 сдвига, и отсчет базовой линии, хранящийся во втором регистре 11 сдвига, усредняютс и из отсчета сигнала вычитается отсчет базовой линии и полученный результат записывается во второй регист 14. Если во время накопления восьми отсчетов компаратор 9 зарегистрирует второй сигнал, то происходит сброс ЗЧП 1, блокировка АЦП 3 и сброс первого регистра 6 сдвига. Во второй регистр 14 запись не производится.

Цифровой процессор спектрометрических импульсов работает следующим образом,

После включения напряжения питания все триггеры и второй и третий счетчи

5

5

0

з

0

5

0

0

5

ки 38,39 в блоке 10 управления (фиг.2) устанавливаются в исходное состояние: на прямом выходе лог. О, на инверсном выходе лог. 1, устанавливается в ноль первый регистр 6 сдвига (цепи начальной установки на фиг. 1, 2 не показаны). Последовательность импульсов с периодом Т1 на выходе генератора 17 преобразуется с помощью первого счетчика 18 и дещифратора 20 в три последовательности импульсов, сдвинутых одна относительно другой на время Т1. Величина Т1 не должна быть меньше- времени преобразования аналоговой входной величины в код в АЦП 3. Пока на выходе ЗЧП t не появится сту- пенчатьй сигнал, т.е. пока детектор jje зарегистрировал частицу, цифровой процессор осуществляет преобразование базовой линии в цифровой код. Импульс на первом выходе дешифратора 20 запускает преобразование Е параллельном АЦП 3. По переднему фронту импульса на втором выходе дешифратора 20 происходит запись полученного в АЦП 3 в первый регистр 4, Первый сумматор 5 осуществляет суммирование кодов, поступающих с выхода первого регистра 4 и с выхода первого регистра 6 сдвига. Полученный результат передним фронтом импульса с третьего выхода дешифратора 20 (фиг. 2) записывается в пер- вьй регистр 6 сдвига. Этим же импульсом в третий счетчик 39 записывается единица. Таким образом, после суммирования восьмого отсчета на выходе переполнения третьего счетчика 39 появляется импульс, который перебрасывает четвертый триггер 24, Лог. 1 с прямого выхода четвертого триггера 24 разрешает прохождение импульса с первого выхода дешифратора 20 через второй элемент И 33 и второй элемент ИЛИ 26. По переднему фронту этого импульса накопленная сумма из первого регистра 6 сдвига переписьшается во второй регистр 11 сдвига. Одновременно начинается новьй цикл измерения базовой линии. Импульс с второго выхода дешифратора 20 проходит через третий элемент И 34 и третий эле- MUHT ИЛИ 27 и сбрасьшает первый регистр 6 сдвига. Одновременно импульс с выхода третьего элемента ИЛИ 27, пройдя через третий элемент 42 задержки с временем задержки, равным Т 1, и седьмой элемент ИЛИ 31, сбрасьшает четвертьй триггер 24.

После того, как на выходе ЗЧП 1 появляется сигнал, амплитуда которого превьшает порог, установленный с помощью потенциометра 8, срабатывает компаратор 9. БФУ 7 служит для формирования из ступенчатого напряжения на выходе ЗЧП 1 короткого импульса. Следовательно, на выходе компаратора 9 также будет короткий импульс, KOTOрьй перебрасывает первый триггер 21 (фиг, 2). Передним фронтом импульса с прямого выхода первого триггера 21 запускается одновибратор 19, импульс с выхода которого сбрасьшает и блоки- рует по установочным входам первый и третий счетчики 18, 39 и первый регистр 6 сдвига. Длительность импульса одновибратора 19 выбирается равной времени установления амплитуды импуль са на входе АЦП 3. После окончания импульса на выходе одновибратора 19 первым появляется импульс на первом выходе дешифратора 20, который запускает преобразование в А1Щ 3, Импуль- сом с второго выхода дешифратора 20 полученный код переписывается в первый регистр 4 и складьшается с нулевым кодом, хранящимся в первом регистре 6 сдвига. Полученная сумма перед- ним фронтом импульса с третьего выхода дешифратора 20 записывается в первый регистр 6 сдвига. Этим же импульсом содержание третьего счетчика 39 увеличивается на единицу.

После накопления восьми отсчетов сигнала на выходе переполнения третьего счетчика 39 появляется импульс, который взводит четвертый триггер 24 и через пятый открытьш элемент И 36 взводит третий триггер 23, Чет- вертьш элемент И 35 определяет включение режима усреднения полученных отсчетов базовой линии и сигнала, Усреднение осуществляется за счет сдви- га на три разряда влево кодов, хранящихся в первом и втором регистрах 6,11 сдвига (деление на восемь). Лог, 1 с выхода четвертого элемента И 35 переводит первый и второй ре- гистры 6,11 сдвига из режима приема параллельного кода в режим сдвига информации влево, который осуществляется по переднему фронту импульсов генератора 17, прошедших через откры- тый первый элемент И 32 и первый и второй элементы ИШ 25, 26 на тактовы входы первого и второго регистров 6,1 сдвига. В это время первый счетчик 18

заблокирован и сброшен ЗЧП 1 по установочному входу лог. 1 с прямого выхода третьего триггера 23 через пя- тьш и шестой элементы ШШ 29, 30,поэтому на выходах дешифратора 20 импульсы не формируются. После сдвига кодов в первом и втором регистрах 6,11 сдвига на три разряда влево на выходе переполнения второго счетчика 38 появляется импульс, который через седьмой элемент ИЛИ 31 сбрасывает чет вертьш триггер 24 и поступает на вход второго элемента 41 задержки, длительность которой равна времени вычитания кода во втором регистре 11 сдвига из кода в первом регистре 6 сдвига. Вычитание осуществляется следующим образом; обратный код из второго регистра 11 сдвига добавлением единицы к его младшему разряду с помощью третьего сумматора 13 преобразуется в допол нителъньш код, который затем складывается с прямым кодом из первого регистра 6 сдвига с помощью второго сумматора 12, на выходе которого получается разность между кодом в первом регистре 6 сдвига и кодом во втором регистре 11 сдвига. Этот код передним фронтом импульса с выхода второго элемента 41 задержки записывается во вто рой регистр 14, Одновременно с этим импульсом взводится триггер 45 (фиг. 3), который выставляет сигнал запроса LAM на выходную шину 16 (магистраль САМАС),

Считьшание данных из второго регистра 14 осуществляется под управлением контроллера Крейта (не показан) с помощью стандартной команды САМАС F (2). По строб-импульсу S1, формрфуемому контроллером, через блок элементов И 44 код из второго регистра 14 считывается на выходную шину .16. По строб-импульсу S2 сбрасьтается триггер 45 и сигнал запроса снимается

Импульс с выхода второго элемента 41 задержки задерживается на время записи во второй регистр 14 четвертым элементом 43 задержки, импульс с выхода которого, пройдя четвертьш элемент ШШ 25, сбрасьшает первый и третий триггеры 21, 23, и, пройдя на вы- ход третьего элемента ИЛИ 27, сбрасывает первьй регистр 6 сдвига. С установочного входа первого счетчика 18 снимается блокировка, он начинает пересчитывать импульсы генератора 17 и на выходе дешифратора 20 появляют

ся импульсы, которые запускают новый цикл обработки либо базовой линии, либо сигнала5 в зависимости от состояния первого триггера 21.

Если в процессе накопления восьми отсчетов сигнала детектор зарегистрирует еще одну частицу, то на выходе компаратора 9 появится импульс, который перебросит второй триггер 22, так как на его входе установлена лог, 1. Имлульс с прямого выхода второго триггера 22 через пятый и- шестой элементы Ш1И 29,30 сбрасывает и блокирует первый счетчик 18. Импуль с выхода шестого элемента ИЛИ 30 разряжает интегрирующий конденсатор в ЗЧП 1. Одновременно импульс с прямого выхода второго триггера 22 проходит через открытый шестой элемент И 37 и задерживается первым элементом 40 задержки на время переходных процессов в ЗЧП 1, С выхода первого элемента 40 задержки импульс через четвертый элемент ИГШ 28 сбрасывает первый и второй триггеры 21, 22, а через третий элемент ИЛИ 27 - первый регистр 6 сдвига. Таким образом устраняются искажения, обусловленные наложениями импульсов на входе АЦП Зо

Предлагаемое устройство может быть реализовано следующим образом. ЗЧП 1 выполнено по схеме интегратора тока ключ может быть выполнен на полевом транзисторе КП 350. АЦП 3 является параллельным АЦП и мох{ет быть выполне , но над И07ПВ2, Сумматоры 5,12,13 могут быть выполнены на IG55lIM6, регистры 6,11 сдвига на К555ИР11. Регистры 4,14 могут быть выполнены на К155ТМ8, компаратор выполнен на К521СА4.

Повьшение быстродействия можно определить сравнив время., затрачиваемое на обработку одного сигнала в из- вестном устройстве и в предлагаемом, В известном устройстве используются весовые коэффи1щенты 1, 2., 4,8. Умножение на весовой коэффициент осуществляется путем сдвига отсчета сигнала на соответствующее количество разрядов вправо. Если обрабатывается восемь отсчетов сигнала, то общее количество сдвигов вправо будет равно 12 и для этого потребуется 12x20 240 НС, суммирование и вычитание займет (8+1) 216 не, для усреднения полученного результата необходимо произвести четыре сдвига влево,

0

0

5 0

Q

5

5

на которые потребуется 4) 20 80 не. Следовательно, для обработки сигнала в известном устройстве потребуется 240 + 216 + 80 536 НС,

В предлагаемом устройстве осуществляется восемь раз суммирование и один раз вычитание, что занимает (8+0x20 216 НС, для усреднения необходим сдвиг на три разряда влево, т.е, 3x20 60 НС, Общее время обработки равно 276 НС. Таким образом быстродействие увеличивается в 536/276 1,9 раза.

Быстродействие также увеличивает за счет разряда интегрирующего конденсатора в ЗЧП 1, В известном устройстве сигналы на входе АЦП имеют длинный спад, что приводит к смещению базовой линии из-за наложения сигнала на сигнал. Так как АЦП имеет определенный диапазон амплитуды входных сигналов, то смещение базовой линии может привести к ограничению амплитуды входного сигнала. Максимальная амплитуда входного сигнала АЦП равна 5 В, постоянная времени спада сигнала равна приблизительно 50 МКС, Если считать, что допустимое смещение базовой линии составляет 1 В, тогда максимальное число импульсов, которое может обработать известное устройство, равно 8000 имп/с, В предлагаемом устройстве импульс на входе АЦП имеет прямоугольную форму и длительность около 2 мкс, следовательно, для такого же АЦП как в известном устройстве максимальное число обрабатьшаемьк импульсов будет равно 200000 имп/с, т,е. в 25 раз больше.

Формула изобретения 1, Цифровой процессор спектрометрических импульсов, содержащий последовательно соединенные зарядочувстви- тельный предусилитель, усилитель и аналого-цифровой преобразователь, выход зарядочувствительного предусили- теля также соединен через быстрый фильтруюищй усилитель с первым входом компаратора, второй вход которого соединен с первым вьшодом потенцио-- метра, второй и третий выводы которого соединены соответственно с источником питания и общей шиной, блок управления, первый выход которого соединен с тактовым входом первого регистра .сдвига, выход которого соединен с первой группой входов первого сумматора и с информационными входами

второго регистра сдвига, тактовый вх которого соединен с вторым выходом блока управления, выход первого суммтора соединен с информационными входми первого регистра сдвига, о т л и чающийся тем, что, с целью повьшения быстродействия за счет увеличения числа обрабатываемых импульсов в единицу времени при одновременном увеличении точности получаемой информации, введены первый, второй ргистры, второй, третий сумматоры, блок сопряжения, причем вход управления зарядочувствительного предусили- теля соединен с третьим выходом блока управления, четвертый и пятый выхды которого соединены соответственно с тактовыми входами аналого-цифровог преобразователя и первого регистра, информационные входы которого соединены с выходами аналого-цифрового пробразователя, выходы первого регистра соединены с второй группой входов первого сумматора, выход компаратора соединен с входом блока управления, шестой выход которого соединен с входом установки первого регистра сдвига, первые и вторые входы выбора режима первого, второго регистров сдвига соединены соответственно с источником потенциала и с -седьмым выходом блока управления, выходы первого регистра сдвига соединены с первой группой входов второго сумматора, вторая группа входов которого соединена с выходами третьего сумматора, первая группа входов которого соединена с инверсными выходами второго регистра сдвига, младший разряд второй группы входов третьего сумматора соединен с источником потенциала, а остальные разряды соединены с общей шиной, выход второго сумматора соединен с информационными входами второ- го регистра, тактовьш вход которого соединен с тактовым входом блока сопряжения и с восьмым выходом блока управления, выходы второго регистра сое

10

15

0445

5с

20

5

0

5

0

14

причем выход генератора соединен с тактовым входом первого счетчика и первым входом первого элемента И, выход которого соединен с тактовым входом второго счетчика и первыми входами первого, второго элементов ИЛИ, выходы первого счетчика соединены с соот- ветствуюпшми входами дешифратора, первьй выход которого соединен с первым входом второго элемента И, второй выход дешифратора соединен с первым входом третьего элемента И,третий выход дешифратора соединен с тактовым входом третьего счетчика и вторым входом первого элемента ИЛИ, вход предустановки первого триггера соединен с тактовым входом второго триггера и является входом блока управления, прямой выход первого триггера соединен с D-входом второго триггера, с входом одновибратора и первыми входами четвертого и пятого элементов И, инверсный выход первого триггера соединен с вторыми входами второго и третьего элементов И, входы установки первого и второго триггеров соединены с первым входом третьего элемента ИЛИ и с выходом четвертого элемента ИЛИ, выход одновибратора соединен с первым входом пятого элемента ИЛИ, с входом установки третьего счетчика и вторым входом третьего элемента ИЛИ, прямой выход второго триггера соединен с первыми входами шестого элемента ИЛИ и шестого элемента И, выход шестого элемента ШШ соединен с вторым входом пятого элемента КГШ,.выход пятого элемента ИЛИ соединен с входом установки первого счетчика, второй вход шестого элемента ИЛИ соединен с прямым выходом третьего триггера, инверсный выход которого соединен с вторым входом шестого И, выход которого через первьй элемент задержки соединен с первым входом четвертого элемента ИЛИ, выход переполнения третьего счетчика соединен с входом предустановки четвертого триггера и вто

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННЫЙ РЕНТГЕНОВСКИЙ СПЕКТРОМЕТРИЧЕСКИЙ КАНАЛ | 1999 |

|

RU2157553C1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2298297C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ ВЫСОКОЙ ЧЕТКОСТИ | 2001 |

|

RU2214693C2 |

| ЦИФРОВАЯ СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2003 |

|

RU2246801C1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1727134A1 |

Изобретение относится к ядерной электронике и может быть использовано в спектрометрах заряженных частиц с полупроводниковыми детекторами. Цель изобретения - увеличение быстродействия цифрового процессора спектрометрических импульсов за счет увеличения числа отрабатываемых импульсов в единицу времени при одновременном увеличении точности получаемой информации. Это достигается за счет разряда интегрирующего конденсатора в зарядочувствительном предусилителе импульсов с выхода блока управления после того, как необходимое число выборок (восемь) импульса преобразованы параллельным аналого-цифровым преобразователем в код и просуммированы. При отсутствии импульса автоматически непрерывно измеряется уровень базовой линии, значение которого вычитается из кода импульса при его обработке. Осуществляется режекция наложений - при приходе второго импульса во время анализа первого устройство приводится в начальное состояние. 2 з.п. ф-лы, 3 ил.

динены с информационными входами ,, сопряжения..

2, Процессор по п. 1, отличающийся тем, что блок управления содержит генератор, первьш, второй, третий счетчики, одновибратор, дешифратор, с первого по седьмой элементы ИЖ, с первого по четвертый триггеры, с первого по шестой элементы И, с первого по четвертьй элементы задержки,

55

рым входом пятого элемента И, выход которого соединен с входом предустановки третьего триггера, третий вход второго элемента И соединен с третьим входом третьего элемента И, с вторым входом четвертого элемента И и прямым выходом четвертого триггера, инверс- ньш выход которого соединен с входом установки второго счетчика, выход переполнения которого соединен с входом

второго элемента задержки и первым входом седьмого элемента ИЛИ, выход которого соединен с входом установки четвертого триггера, выход третьего элемента И соединен с третьим входом третьего элемента ИЛИ, выход которого через третий элемент задержки соединен с вторым входом седьмого элементу ИЛИ, выход второго элемента И сое- дйнен с вторым входом второго элемента ИЛИ, выход второго, элемента задержки через четвертый элемент задержки соединен с вторым входом четвертого элемента ИЛИ и входом установки тре- тЬего триггера, выход четвертого эле- MiBHTa И соединен с вторым входом первого элемента И, причем первым выходом блока управления является выход первого элемента ИЛИ, вторым-- второ- го элемента ИЛИ, третьим - шестого элемента ИЛИ, четвертым и пятым - пер- Bbift и второй выходы дешифратора, шес- TbiM - выход третьего элемента ИЛИ, седьмым - четвертого элемента И, вось- мым - выход второго элемента задержки

3, Процессор по п, 1 ,о тл ич аю- щ и и с я тем, что блок сопряжения соФМ.1

держит блок элементов И, триггер, дешифратор функций, дешифратор адреса, первый, второй, третий элементы И, первый, второй, третий элементы НЕ, причем первые входы блока элементов И являются информационными входами блока сопряжения, тактовый вход которого соединен с входом предустановки триггера, вход установки которого соединен с выходом первого элемента И, первый вход которого соединен с первым входом второго элемента И и выходом третьего элемента И,первый вход которого соединен с выходом дешифратора функций, первый вход которого через первый элемент НЕ соединен с вторыми входами второго и третьего элементов И,третийвход третьего элемента Исо- единен свыходом дешифратора адреса,первый и второй входы дешифратора функций и вход дешифратора адреса являются соответствующими линиями управляющей шины блока сопряжения, третий вход второго элемента И и второй вход второго элемента И через соответствующие второй и третий элементы НЕ соединены с соответствующими линиями управляющей шины блока сопряжения.

/У

П

.Ь

«

TJ

l5zl

BL

5/

| IEEE | |||

| Trans on Nuclear Science, Vol.- NS-29, № 3, 1982, p | |||

| КОЛЕСНЫЙ ТРАКТОР | 1923 |

|

SU1125A1 |

| H | |||

| Koewan, Pren ciple of Operation and Propertiec of a Transversal Digital Filter. | |||

| - Nucl | |||

| Instr, and Meth, V | |||

| Устройство для разметки подлежащих сортированию и резанию лесных материалов | 1922 |

|

SU123A1 |

| Универсальный двойной гаечный ключ | 1920 |

|

SU169A1 |

Авторы

Даты

1990-11-30—Публикация

1989-02-23—Подача