Изобретение относится к накоплению информации, а именно к аппаратуре для проверки накопителей на магнитных дисках.

Цель изобретения - повышение точности тестирования накопителей за счет устранения зависимости погрешности тестирования от распределения фазовых соотношений импульсов в воспроизведенном сигнале.

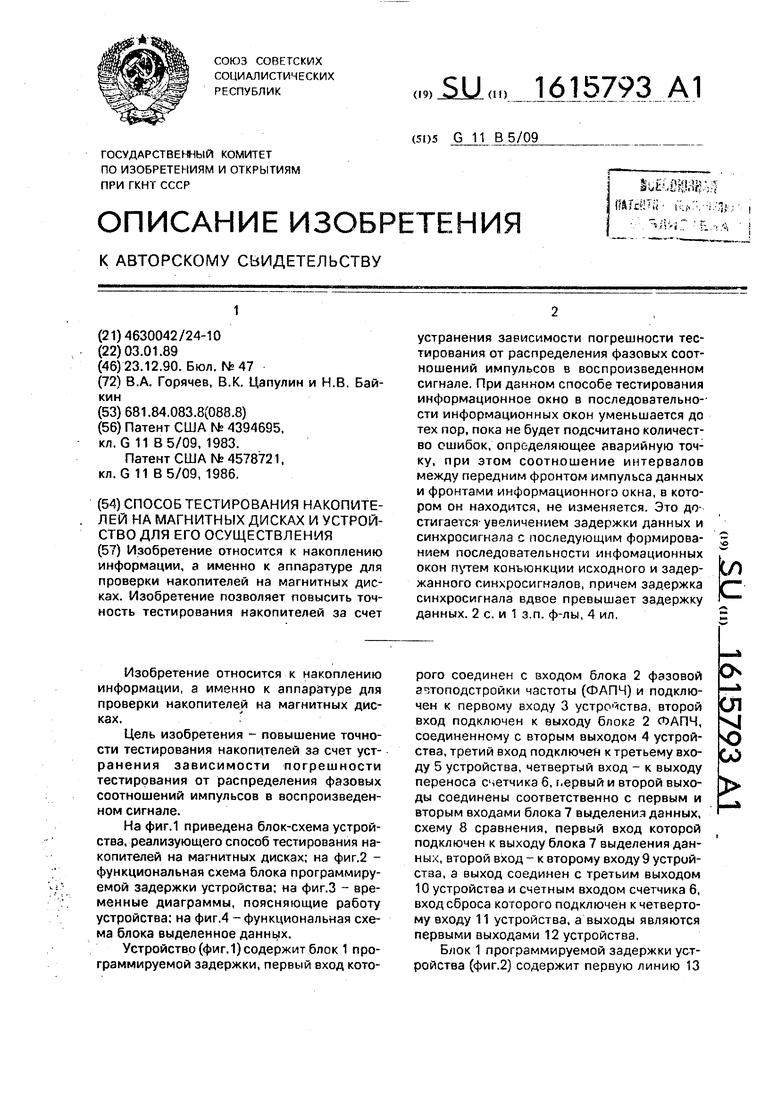

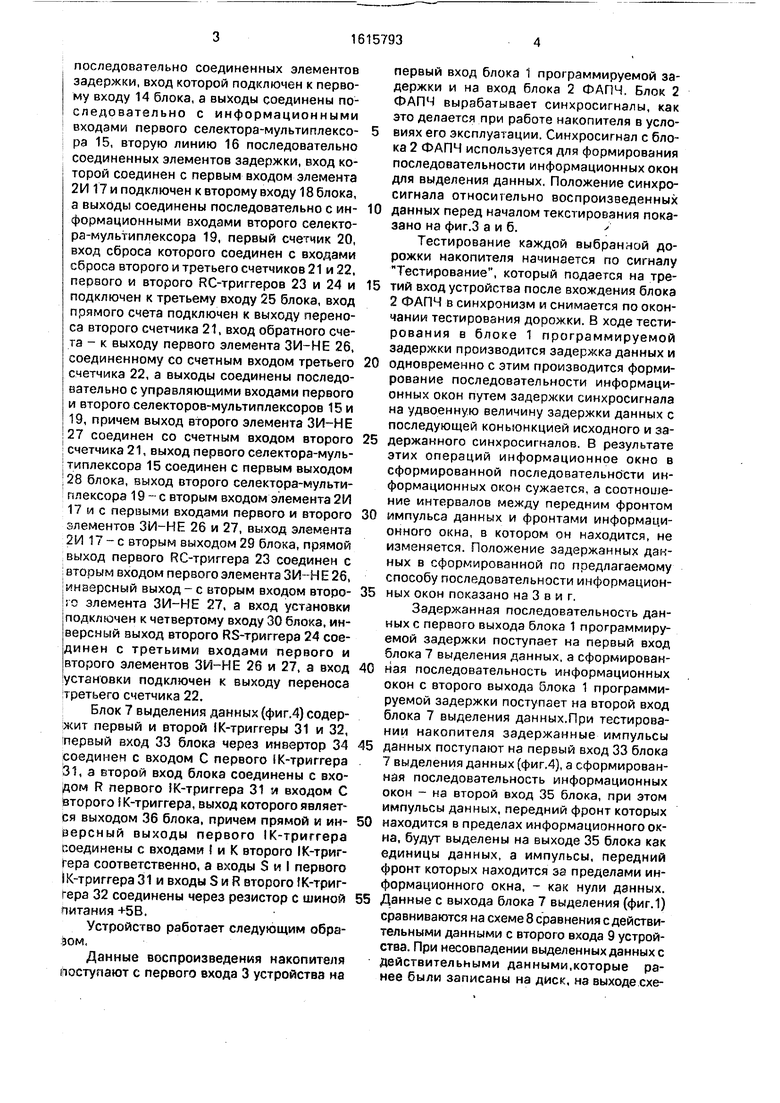

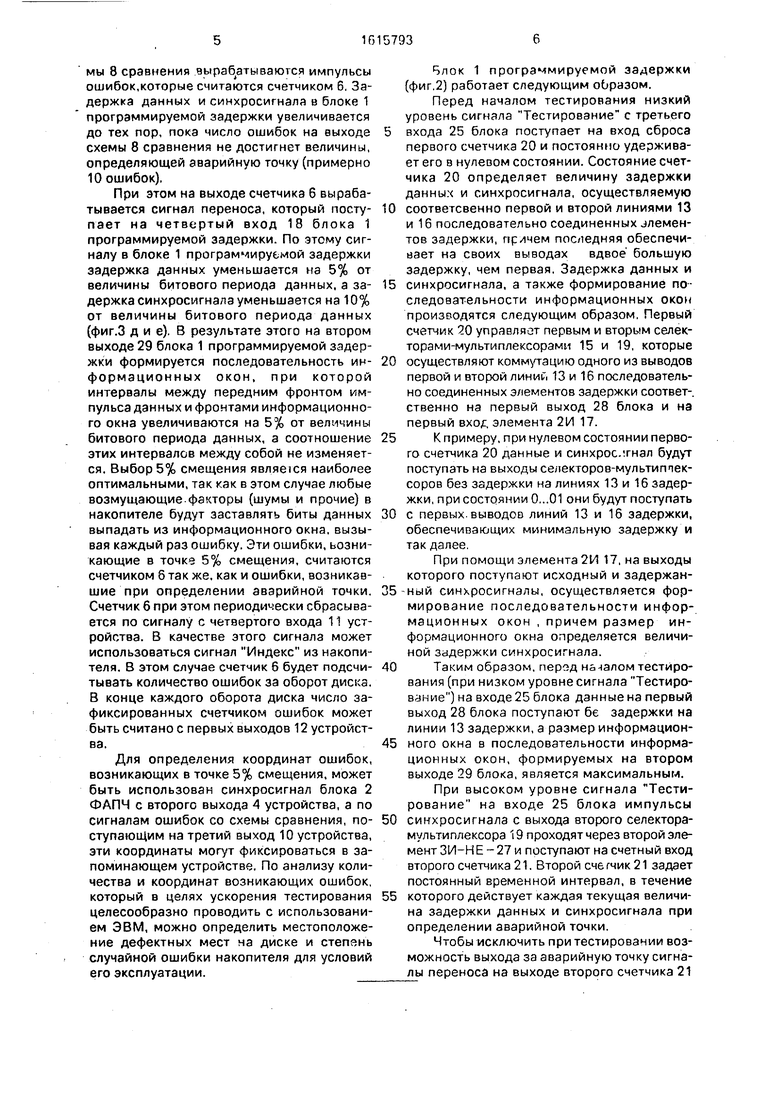

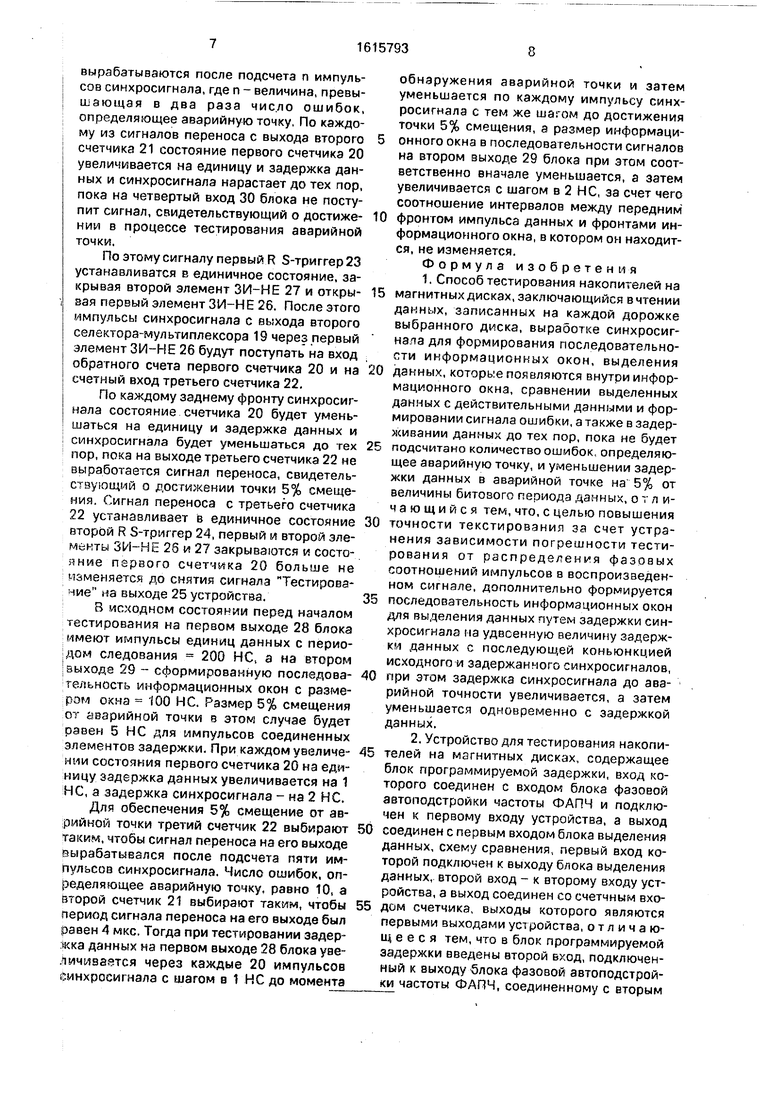

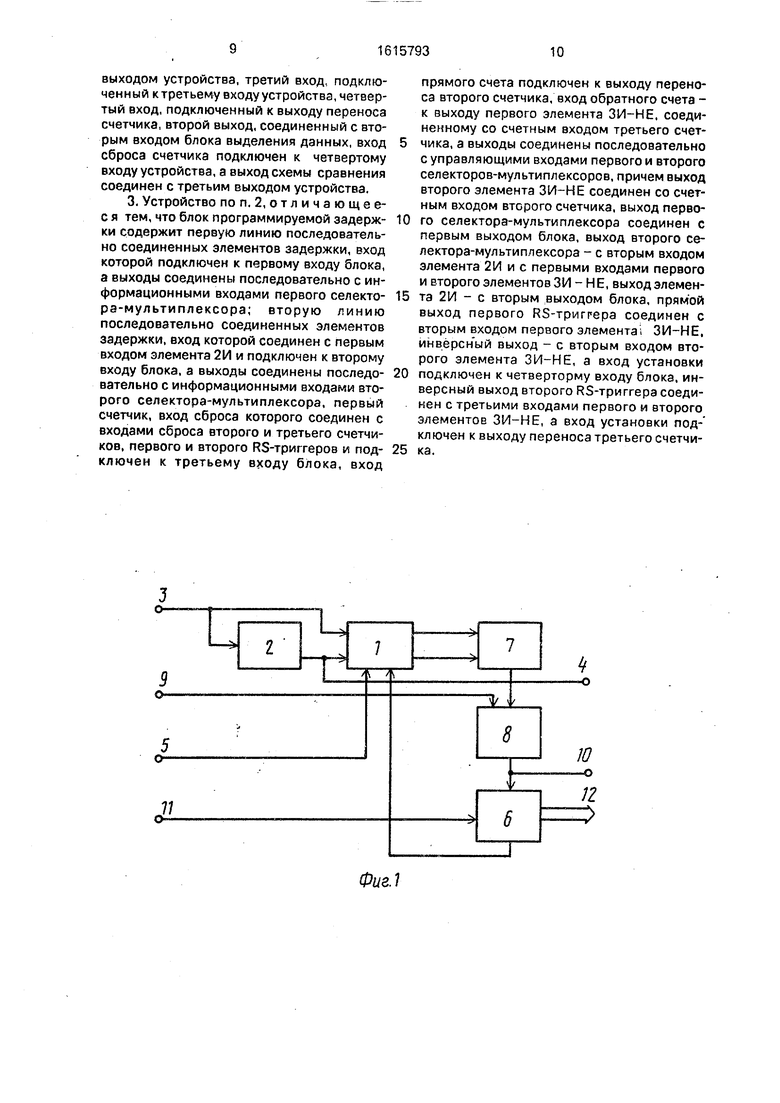

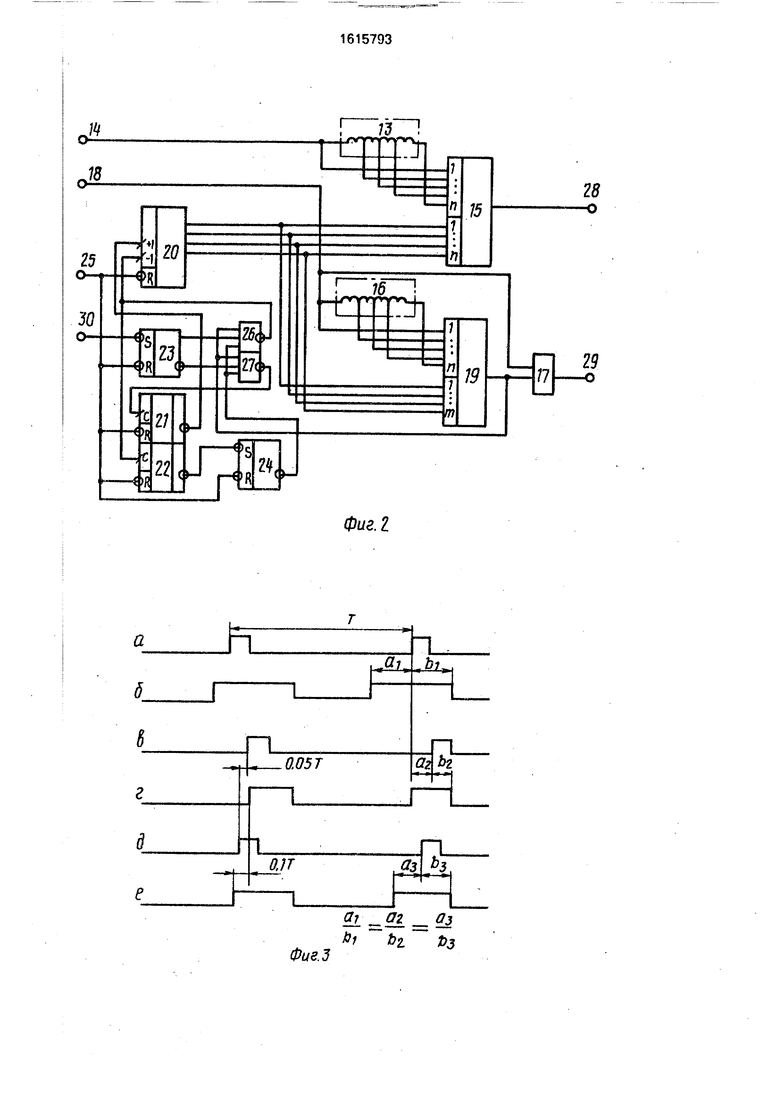

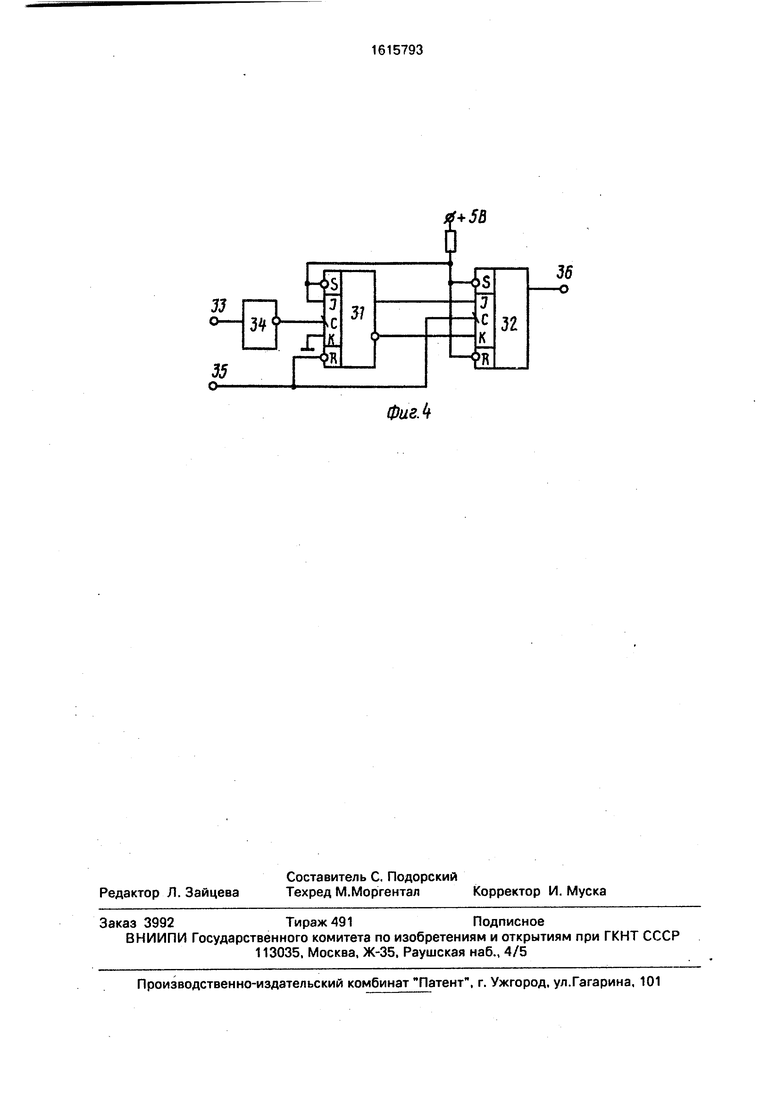

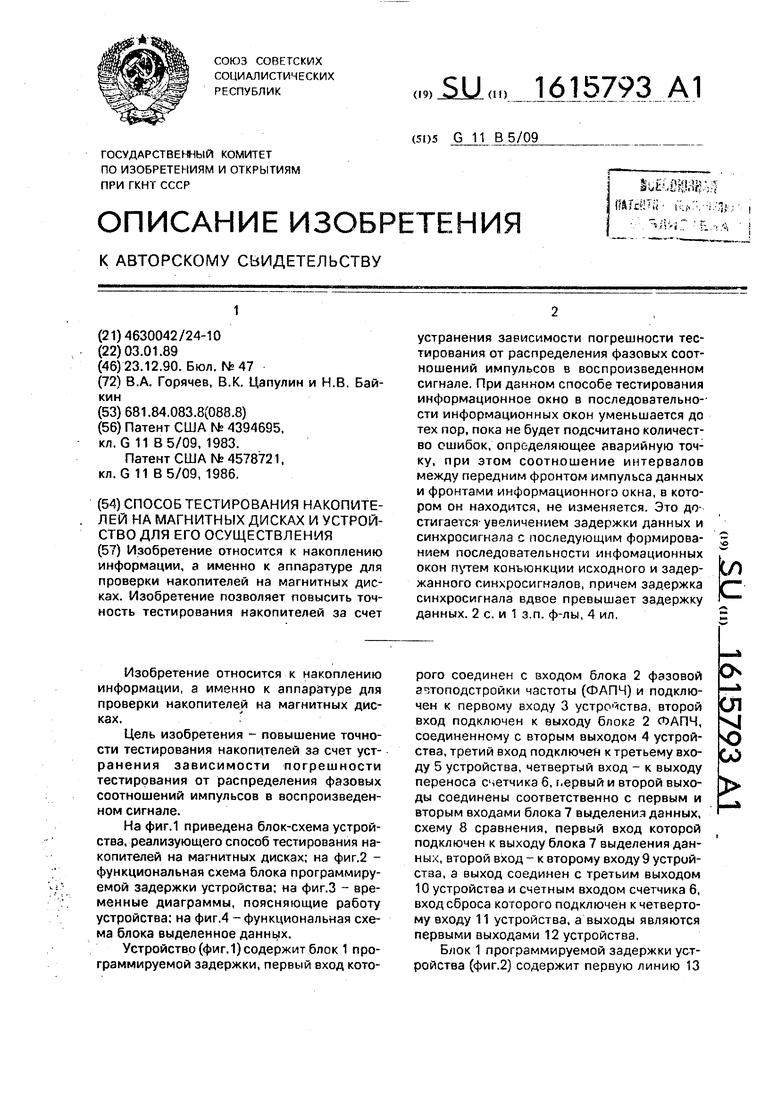

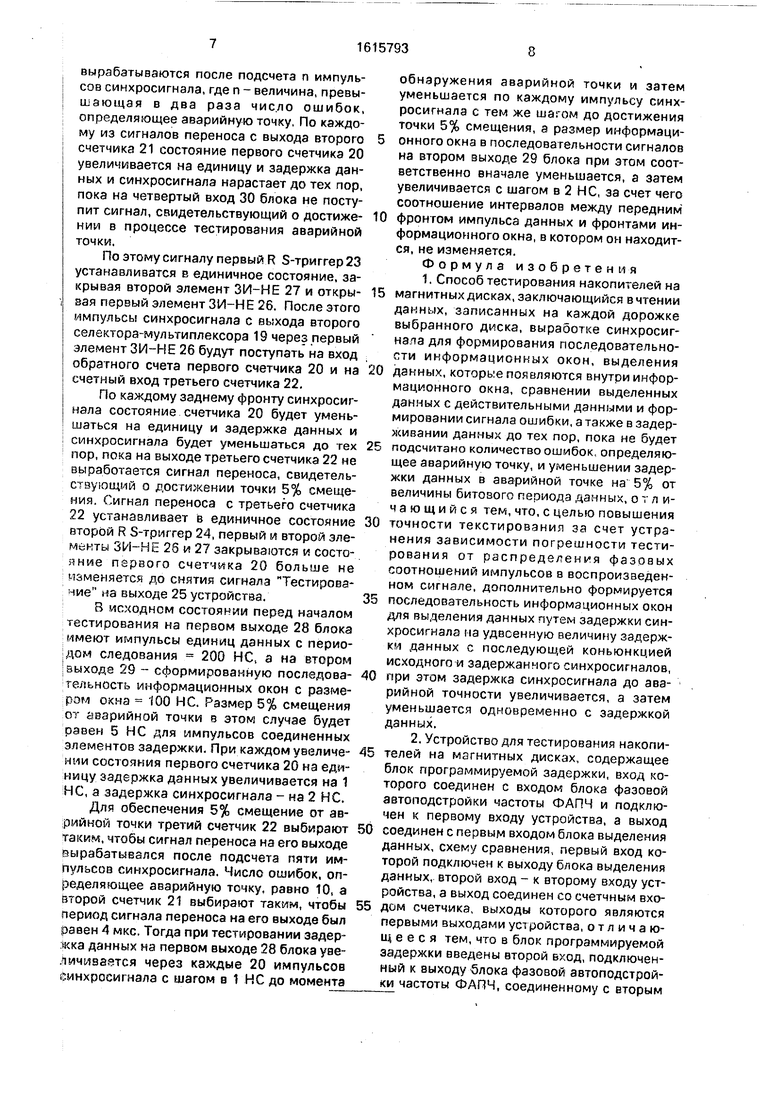

На фиг.1 приведена блок-схема устройства, реализующего способ тестирования накопителей на магнитных дисках: на фиг.2 - функциональная схема блока программируемой задержки устройства; на фиг.З - временные диаграммы, поясняющие работу устройства: на фиг.4 - функциональная схема блока выделенное даннь1х.

Устройство (фиг. 1) содержит блок 1 программируемой задержки, первый вход которого соединен с входом блока 2 фазовой а.топодстройки частоты (ФАПЧ) и подключен к первому входу 3 устройства, второй вход подключен к выходу блока 2 , соединенному с вторым выходом 4 устройства, третий вход подключен к третьему входу 5 устройства, четвертый вход - к выходу переноса счетчика 6, г.ервый и второй выходы соединены соответственно с первым и вторым входами блока 7 выделения данных, схему 8 сравнения, первый вход которой подключен к выходу блока 7 выделения данных, второй вход - к второму входу 9 устройства, а выход соединен с третьим выходом 10 устройства и счетным входом счетчика 6, вход сброса которого подключен к четвертому входу 11 устройства, а выходы являются первыми выходами 12 устройства,

Блок 1 программируемой задержки устройства (фиг.2) содержит первую линию 13

О

ся V ю со

последовательно соединенных элементов задержки, вход которой подключен к первому входу 14 блока, а выходы соединены последовательно с информационными i входами первого селектора-мультиплексо- I ра 15, вторую линию 16 последовательно : соединенных элементов задержки, вход которой соединен с первым входом элемента 2И 17 и подключен к второму входу 18 блока, а выходы соединены последовательно с ин- формационными входами второго селектора-мультиплексора 19, первый счетчик 20, вход сброса которого соединен с входами сброса второго и третьего счетчиков 21 и 22, первого и второго НС-триггеров 23 и 24 и подключен к третьему входу 25 блока, вход прямого счета подключен к выходу переноса второго счетчика 21, вход обратного счета - к выходу первого элемента ЗИ-НЕ 26, соединенному со счетным входом третьего счетчика 22, а выходы соединены последовательно с управляющими входами первого и второго селекторов-мультиплексоров 15 и 19, причем выход второго элемента ЗИ-НЕ I 27 соединен со счетным входом второго I счетчика 21, выход первого селектора-муль- |типлексора 15 соединен с первым выходом 128 блока, выход второго селектора-мультиплексора 19 - с вторым входом элемента 2И 17 и с первыми входами первого и второго элементов ЗИ-НЕ 26 и 27, выход элемента 2И 17-с вторым выходом29 блока, прямой выход первого RC-триггера 23 соединен с I вторым входом первого элемента ЗИ-НЕ 26, | нв8рсный выход- с вторым входом второ- |io элемента ЗИ-НЕ 27. а вход установки |подключен к четвертому входу 30 блока, ин- |версный выход второго RS-триггера 24 соединен с третьими входами первого и второго элементов ЗИ-НЕ 26 и 27, а вход |установки подключен к выходу переноса третьего счетчика 22,

Блок 7 выделения данных (фиг.4) содержит первый и второй 1К-триггеры 31 и 32, 1первый вход 33 блока через инвертор 34 соединен с входом С первого (К-триггера 31, а второй вход блока соединены с входом R первого К-триггера 31 я входом С Второго f К-триггера, выход которого является выходом 36 блока, причем прямой и ий- версный выходы первого 1К-триггера соединены с входами I и К второго 1К-триг- Гера соответственно, а входы S и I первого I К-триггера 31 и входы S и R второго 1К-триг- i-epa 32 соединены через резистор с шиной 5 питания +5В.

Устройство работает следующим обра:&ОМ,

Данные воспроизведения накопителя /поступают с первого входа 3 устройства на

первый вход блока 1 программируемой задержки и на вход блока 2 ФАПЧ. Блок 2 ФАПЧ вырабатывает синхросигналы, как это делается при работе накопителя в условиях его эксплуатации. Синхросигнал с блока 2 ФАПЧ используется для формирования последовательности информационных окон для выделения данных. Положение синхросигнала относительно воспроизведенных данных перед началом текстирования показано на фиг.З а и б.

Тестирование каждой выбранной дорожки накопителя начинается по сигналу Тестирование, который подается на третий вход устройства после вхождения блока 2 ФАПЧ в синхронизм и снимается по окончании тестирования дорожки. В ходе тестирования в блоке 1 программируемой задержки производится задержка данных и одновременно с этим производится формирование последовательности информационных окон путем задержки синхросигнала на удвоенную величину задержки данных с последующей коньюнкцией исходного и задержанного синхросигналов. В результате этих операций информационное окно в сформированной последовательнбсти информационных окон сужается, а соотношение интервалов между передним фронтом импульса данных и фронтами информационного окна, в котором он находится, не изменяется. Положение задержанных данных в сформированной по предлагаемому способу последовательности информационных окон показано на 3 в и г.

Задержанная последовательность данных с первого выхода блока 1 программируемой задержки поступает на первый вход блока 7 выделения данных, а сформированная последовательность информационных окон с второго выхода блока 1 программируемой задержки поступает на второй вход блока 7 выделения данных.При тестировании накопителя задержанные импульсы данных поступают на первый вход 33 блока 7 выделения данных (фиг.4), а сформированная последовательность информационных окон - на второй вход 35 е)лока, при этом импульсы данных, передний фронт которых находится в пределах информационного окна, будут выделены на выходе 35 блока как единицы данных, а импульсы, передний фронт которых находится за пределами информационного окна, - как нули данных. Данные с выхода блока 7 выделения (фиг.1) сравниваются на схеме 8 сравнения с действительными данными с второго входа 9 устройства. При несовпадении выделенных данных с действительными данными,которые ранее были записаны на диск, на выходе схемы 8 сравнения выраб атываются импульсы ошибок,которые считаются счетчиком 6. Задержка данных и синхросигнала в блоке 1 программируемой задержки увеличивается до тех пор, пока число ошибок на выходе схемы 8 сравнения не достигнет величины, определяющей аварийную точку (примерно 10 ошибок),

При этом на выходе счетчика 6 вырабатывается сигнал переноса, который поступает на четвертый вход 18 блока 1 программируемой задержки. По этому сигналу в блоке 1 программируемой задержки задержка данных уменьшается на 5% от величины битового периода данных, а задержка синхросигна/та уменьшается на 10% от величины битового периода данных (фиг.З д и е). В результате этого на втором выходе 29 блока 1 программируемой задержки формируется последовательность информационных окон, при которой интервалы между передним фронтом импульса данных и фронтами информационного окна увеличиваются на 5% от величины битового периода данных, а соотношение этих интервалов между собой не изменяется. Выбор 5% смещения являе1ся наиболее оптимальными, так как в этом случае любые возмущающие факторы (шумы и прочие) в накопителе будут заставлять биты данных выпадать из информационного окна, вызывая каждый раз ошибку. Эти ошибки, возникающие в точке 5% смещения, считаются счетчиком б так же, как и ошибки, возникавшие при определении аварийной точки. Счетчик 6 при этом периодически сбрасывается по сигналу с четвертого входа 11 устройства. В качестве зтого сигнала может использоваться сигнал Индекс из накопителя. В этом случае счетчик 6 будет подсчитывать количество ошибок за оборот диска. В конце каждого оборота диска число зафиксированных счетчиком ошибок может быть считано с первых выходов 12 устройства.

Для определения координат ошибок, возникающих в точке 5% смещения, может быть использован синхросигнал блока 2 ФАПЧ с второго выхода 4 устройства, а по сигналам ошибок со схемы сравнения, поступающим на третий выход 10 устройства, эти координаты могут фиксироваться в запоминающем устройстве. По анализу количества и координат возникающих ошибок, который в целях ускорения тестирования целесообразно проводить с использованием ЭВМ, можно определить местоположение дефектных мест на диске и степень случайной ошибки накопителя для условий его эксплуатации.

Блок 1 программируемой задержки (фиг,2) работает следующим оЬразом.

Перед началом тестирования низкий уровень сигнала Тестирование с третьего

входа 25 блока поступает на вход сброса первого счетчика 20 и постоянно удерживает его в нулевом состоянии. Состояние счетчика 20 определяет величину задержки данных и синхросигнала, осуществляемую

0 соответсвенно первой и второй линиями 13 и 16 последовательно соединенных злемен- тов задержки, причем последняя обеспечивает на своих выводах вдвое большую задержку, чем первая. Задержка данных и

5 синхросигнала, а также формирование последовательности информационных окон производятся следующим образом. Первый счетчик 20 управляет первым и вторым селекторами-мультиплексорами 15 и 19, которые

0 осуществляют комм упгацию одного из выводов первой и второй линиС| 13 и 16 последовательно соединенных элементов задержки соответ-. ственно на первый выход 28 блока и на первый вхо,; элемента 2И 17.

5К примеру, при нулевом состоянии первого счетчика 20 данные и синхрос.тнал будут поступать на выходы селекгоров-мультитек- соров без задержки на линиях 13 и 16 задержки, при состоянии О,..01 они будут поступать

0 с первых, выводов линий 13 и 16 задержки, обеспечивающих минимальную задержку и так далее.

При помощи элемента 2И 17, на выходы которого поступают исходный и задержан5-ный синхросигналы, осуществляется формирование последовательности информационных окон , причем размер информационного окна определяется величиной задержки синхросигнала.

0Таким образом, перод Началом тестирования (при низком уровне сигнала Тестирование) на входе 25 блока данные на первый выход 28 блока поступают бе задержки на линии 13 задержки, а размер информацион5 ного окна в последовательности информационных окон, формируемых на втором выходе 29 блока, является максимальным.

При высоком уровне сигнала Тестирование на входе 25 блока импульсы

0 синхросигнала с выхода второго селектора- мультиплексора 19 проходят через второй элемент ЗИ-Н Е - 27 и поступают на счетный вход второго счетчика 21. Второй сче гчик 21 задает постоянный временной интервал, в течение

5 которого действует каждая текущая величина задержки данных и синхросигнала при определении аварийной точки.

Чтобы исключить при тестировании возможность выхода за аварийную точку сигналы переноса на выходе второго счетчика 21

вырабатываются после подсчета п импульсов синхросигнала, где п - величина, превы- шающая в два раза число ошибок, определяющее аварийную точку. По каждому из сигналов переноса с выхода второго счетчика 21 состояние первого счетчика 20 увеличивается на единицу и задержка данных и синхросигнала нарастает до тех пор, пока на четвертый вход 30 блока не поступит сигнал, свидетельствующий о достиже- НИИ в процессе тестирования аварийной точки.

По этому сигналу первый R 5-триггер23 устанавливатся в единичное состояние, закрывая второй элемент ЗИ-НЕ 27 и откры- - вая первый элемент ЗИ-НЕ 26. После этого I импульсы синхросигнала с выхода второго I селектора-мультиплексора 19 через первый элемент ЗИ-НЕ 26 будут поступать на вход обратного счета первого счетчика 20 и на счетный вход третьего счетчика 22,

По каждому заднему фронту синхросигнала состояние счетчика 20 будет умень- ; шаться на единицу и задержка данных и i синхросигнала будет уменьшаться до тех пор, пока на выходе третьего счетчика 22 не выработается сигнал переноса, свидетельствующий о достижении точки 5% смещения. Сигнал переноса с третьего счетчика 22 устанавливает в единичное состояние второй R S-триггер 24, первый и второй элементы ЗИ-НЕ 26 и 27 закрываются и состояние первого счетчика 20 больше не изменяется до снятия сигнала Тестирование на выходе 25 устройства.

8 исходном состоянии перед началом тестирования на первом выходе 28 блока имеют импульсы единиц данных с перио- |Дом следования 200 НС. а на втором I выхода 29 - сформированную последова- 4 тельность информационных окон с размером окна 100 НС. Размер 6% смещения от аварийной точки в этом случае будет равен 5 НС для импульсов соединенных элементов задержки. При каждом увеличе- 4 ими состояния первого счетчика 20 на единицу задержка данных увеличивается на 1 НС, а задержка синхросигнала - на 2 НС. Для обеспечения 5% смещение от ав- рийной точки третий счетчик 22 выбирают 5 таким, чтобы сигнал переноса на его выходе |эырабатывался после подсчета пяти импульсов синхросигнала. Число ошибок, определяющее аварийную точку, равно 10 а йторой сметчик 21 выбирают таким, чтобы 5 период сигнала переноса на его выходе был равен 4 мкс. Тогда при тестировании задержка данных на первом выходе 28 блока увеличивается через каждые 20 импульсов (Синхросигнала с шагом в 1 НС до момента

5 0

5

обнаружения аварийной точки и затем уменьшается по каждому импульсу синхросигнала с тем же шагом до достижения точки 5% смещения, а размер информационного окна в последовательности сигналов на втором выходе 29 блока при этом соответственно вначале уменьшается, а затем увеличивается с шагом в 2 НС, за счет чего соотношение интервалов между передним фронтом импульса данных и фронтами информационного окна, в котором он находится, не изменяется.

Формула изобретения 1. Способ тестирования накопителей на магнитных дисках, заключающийся в чтении данных, записанных на каждой дорожке выбранного диска, выработке синхросигнала для формирования последовательности информационных окон, выделения данных, которые появляются внутри информационного окна, сравнении выделенных данных с действительными данными и формировании сигнала ошибки, а также в задерживании данных до тех пор, пока не будет подсчитано количество ошибок, определяющее аварийную точку, и уменьшении задержки данных в аварийной точке на 5% от величины битового периода данных, отличающийся тем, что, с целью повышения точности текстирования за счет устранения зависимости погрешности тестирования от распределения фазовых соотношений импульсов в воспроизведенном сигнале, дополнительно формируется последовательность информационных окон для выделения данных путем задержки синхросигнала на удвоенную величину задерж- км данных с последуюш,ей коньюнкцией исходного1 задержанного синхросигналов, при этом задержка синхросигнала до ава- рийной точности увеличивается, а затем уменьшается одновременно с задержкой данных.

2. Устройство для тестирования накопителей на магнитных дисках, содержащее блок программируемой задержки, вход которого соединен с входом блока фазовой автоподстройки частоты ФАПЧ и подключен к первому входу устройства, а выход соединен с первым входом блока выделения данных, схему сравнения, первый вход которой подключен к выходу блока выделения данных, второй вход - к второму входу устройства, а выход соединен со счетчным входом счетчика, выходы которого являются первыми выходами устройства, отличающееся тем, что в блок программируемой задержки введены второй вход, подключенный к выходу «лока фазовой автоподстройки частоты ФАПЧ, соединенному с вторым

выходом устройства, третий вход, подключенный ктретьему входу устройства, четвертый вход, подключенный к выходу переноса счетчика, второй выход, соединенный с вторым входом блока выделения данных, вход сброса счетчика подключен к четвертому входу устройства, а выход схемы сравнения соединен с третьим выходом устройства.

3, Устройство по п. 2, о т л и ч а ю щ е е- ся тем, что блок программируемой задерж- ки содержит первую линию последовательно соединенных элементов задержки, вход которой подключен к первому входу блока, а выходы соединены последовательно с информационными входами первого селекто- ра-мультиплексора; вторую линию последовательно соединенных элементов задержки, вход которой соединен с первым входом элемента 2И и подключен к второму входу блока, а выходы соединены последо- вательно с информационными входами второго селектора-мультиплексора, первый счетчик, вход сброса которого соединен с входами сброса второго и третьего счетчиков, первого и второго РЗ-триггеров и под- ключен к третьему входу блока, вход

прямого счета подключен к выходу переноса второго счетчика, вход обратного счета - к выходу первого элемента ЗИ-НЕ. соединенному со счетным входом третьего счетчика, а выходы соединены последовательно с управляющими входами первого и второго селекторов-мультиплексоров, причем выход второго элемента ЗИ-НЕ соединен со счетным входом второго счетчика, выход первого селектора-мультиплексора соединен с первым выходом блока, выход второго селектора-мультиплексора - с вторым входом элемента 2И и с первыми входами первого и второго элементов ЗИ - НЕ, выход элемента 2И - с вторым выходом блока, прямой выход первого RS-триггера соединен с вторым входом первого элемента ЗИ-НЕ. инвёрсн ый выход - с вторым входом второго элемента ЗИ-НЕ, а вход установки подключен к четверторму входу блока, инверсный выход второго RS-триггера соединен с третьими входами первого и второго элементов ЗИ-НЕ, а вход установки под- ключен к выходу переноса третьего счетчика.

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для восстановления информации | 1988 |

|

SU1561098A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1988 |

|

SU1518905A2 |

| Устройство для декодирования данных | 1988 |

|

SU1629912A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1783577A2 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Устройство для поиска зон информации на магнитном носителе | 1989 |

|

SU1644217A1 |

| Устройство коррекции временных искажений воспроизведенных самосинхронизирующихся сигналов | 1983 |

|

SU1123050A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

Изобретение относится к накоплению информации, а именно к аппаратуре для проверки накопителей на магнитных дисках. Изобретение позволяет повысить точность тестирования накопителей за счет устранения зависимости погрешности тестирования от распределения фазовых соотношений импульсов в воспроизведенном сигнале. При данном способе тестирования информационное окно в последовательности информационных окон уменьшается до тех пор, пока не будет подсчитано количество ошибок, определяющее аварийную точку, при этом соотношение интервалов между передним фронтов импульса данных и фронтами информационного окна, в котором он находится, не изменяется. Это достигается увеличением задержки данных и синхросигнала с последующим формированием последовательности информационных окон путем конъюнкции исходного и задержанного синхросигналов, причем задержка синхросигнала вдвое превышает задержку данных. 2 с.п. ф-лы, 4 ил.

Фиг.З

- -

} bz j&j

ФигЛ

| Патент США Ns 4394695 | |||

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США №4578721, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-12-23—Публикация

1989-01-03—Подача