Изобретение относится к вычислительной технике и может быть использовано для функционального контроля как отдельных корпусов микросхем оперативных запоминающих устройств (ОЗУ) динамического типа с мультиплексированными адресными входами, так и построенных на их основе массивов полупроводниковых ОЗУ произвольной емкости и организации. - Известно устройство для контроля блоков полупроводниковой памяти, содержащее генератор тактовых импульсов, генератор тестовой последовательности, блок управления, блок формирования временной диаграммы, блок согласования уровней, компаратор, адресный мультиплексор, преобразователь кодов и накопители. Это устройство позволяет проводить тестовую расщиренную программу испытаний микросхем памяти 1.

Недостатком этого устройства является низкое быстродействие, в связи с чем контроль памяти занимает значительное время, а также невысокая полнота контроля, поскольку регистрация результатов тестирования осуществляется только в режиме считывания выходного сигнала, минуя выходные реакции по всем состояниям таблицы истинности (запрет выборки при чтении, запрет выборки при записи разрешение выборки при записи).

Наиболее близким по технической сущности к изобретению является устройство для контроля оперативных накопителей, содержащее генератор, счетчик, дешифратор, элемент И, мультиплексор, триггер, элемент задержки, коммутатор и анализатор кодов, один из управляющих входов которого подключен к выходу генератора, одни входы коммутатора подключены к выходам мультиплексора, вход счетчика соединен с выходом генератора, входы дешифратора подключены к выходам счетчика, входы элемента И подключены к выходам дешифратора, другие входы коммутатора и входы мультиплексора подключены к соответствующим выходам счетчика. Известное устройство позволяет значительно уменьшить время тестирования и повысить полноту контроля БИС ОЗУ, так как регистрация результатов тестирования осуществляется не только в режиме считывания выходного сигнала, но и по всем состояниям таблицы истинности (запрет выборки при чтении, запрет выборки при записи, разрешение выборки при записи).

Особенность БИС ОЗУ динамического типа с произвольной выборкой заключается в том, что за время 2 мс необходимо обратиться к 128 строкам этих ОЗУ. Только при этом условии информация в динамической памяти (К565РУЗ, К565РУ5) сохраняется 2.

Недостатком известного устройства является отсутствие возможности проверки времени регенерации БИС ОЗУ, что сужает область применения устройства.

Цель изобретения - расширение области применения устройства путем обеспечения контроля времени регенерации информации.

Указанная цель достигается тем, что в устройство для контроля микросхем оперативной памяти, содержащее генератор импульсов, счетчик, дешифратор, мультиплексор, коммутатор, анализатор кодов, первый триггер, элемент задержки, первый элемент И, причем входы первой группы коммутатора подключены к выходам мультиплексора, информационные и адресные входы которого .подключены к соответствующим выходам счетчика, управляющий вход мультиплексора подключен к выходу первого триггера, установочный вход которого подключен к выходу элемента задержки, а информационный вход соединен с шиной нулевого потенциала, входы дешифратора соединены с соответствующими выходами счетчика, первый выход дешифратора соединен с одним из входов первого элемента И и с входом элемента задержки, второй выход дешифратора

соединен со счетньщ входом первого триггера и с другим входом первого элемента И, выход которого подсоединен к первому входу коммутатора, второй вход которого соединен с вторым выходом дешифратора, а третий вход и входы второй группы подключены

к соответствующим выходам счетчика, первый управляющий вход анализатора кодов подключен к одному из выходов коммутатора, другие выходы которого являются выходами устройства, входами которого являются информационные входы анализатора

кодов, введены элемент регулируемой задержки, второй и третий триггеры, второй и третий элементы И, причем выход второго элемента И соединен со вторым управляющим входом анализатора кодов и счетным

входом счетчика, первый вход - с выходом генератора импульсов, с первым входом третьего элемента И и счетным входом второго триггера, второй вход - с выходом второго триггера, установочные входы второго и третьего триггеров подключены к выходу

элемента регулируемой задержки, информационные входы - к шине нулевого потенциала, вход элемента регулируемой задержки соединен с выходом третьего элемента И, второй вход которого подключен к

выходу третьего триггера, третий вход и группа входов третьего элемента И подключены к соответствующим выходам счетчика, счетный вход третьего триггера соединен с одним из выходов коммутатора.

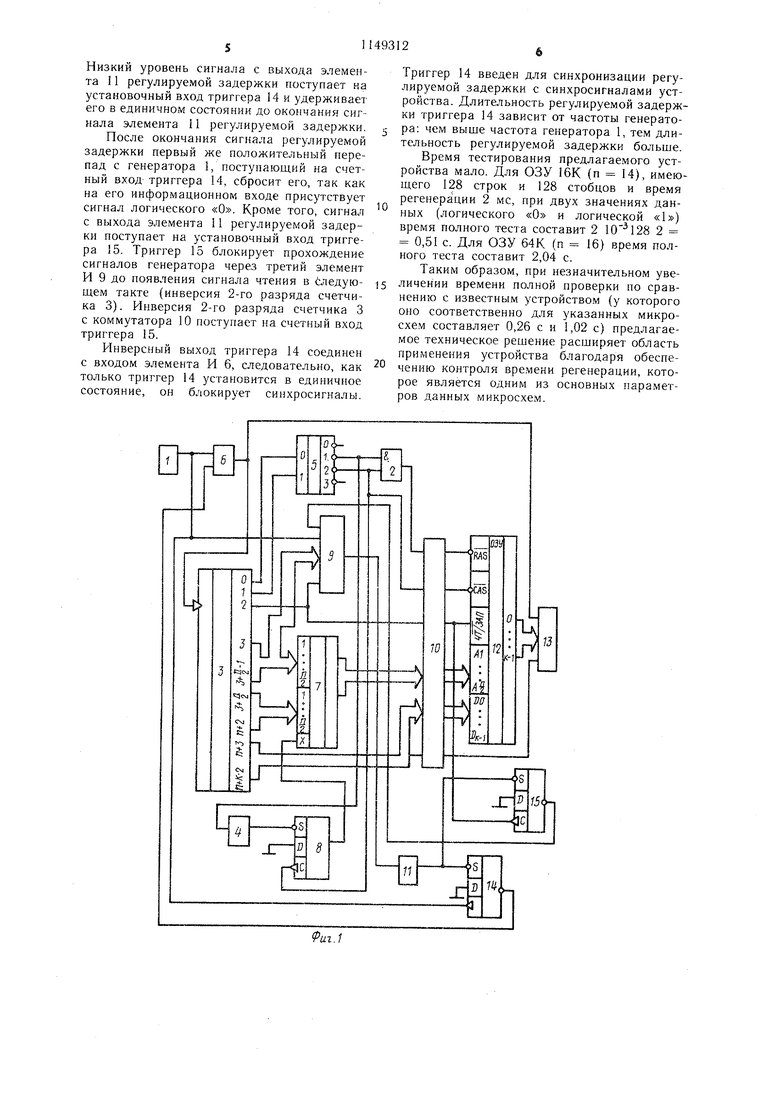

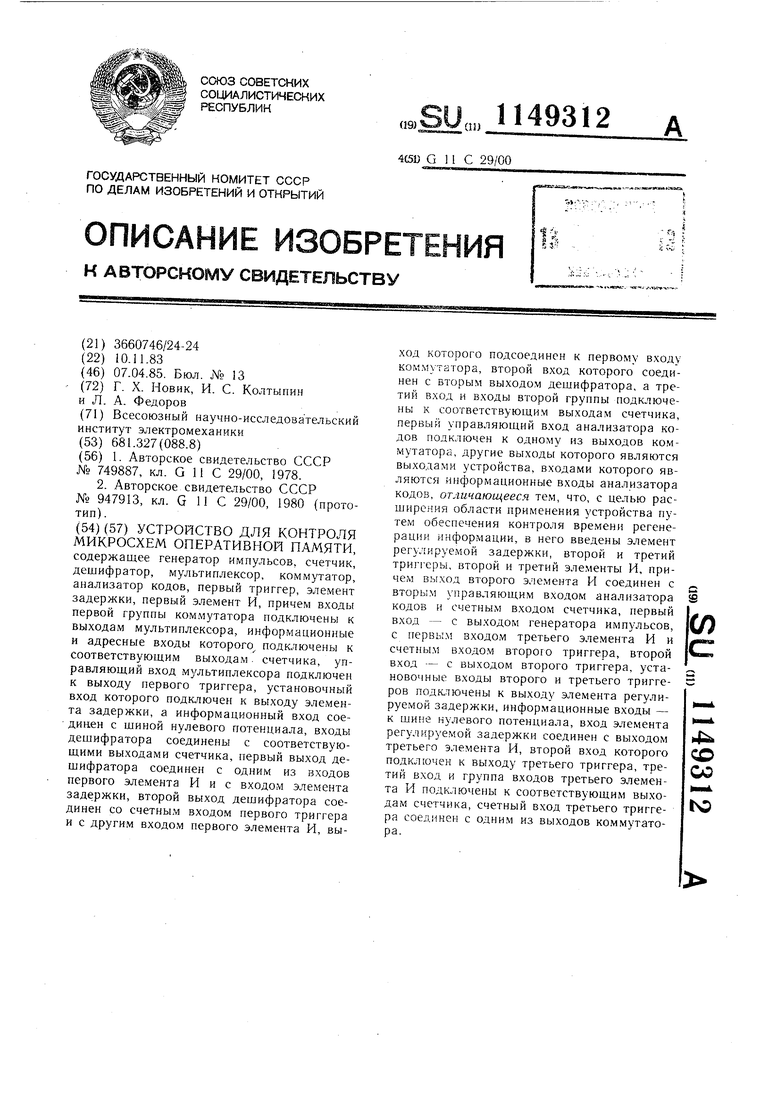

На фиг. 1 приведена структурная схема

предлагаемого устройства; на фиг. 2 - временные диаграммы работы устройства на примере динамического ОЗУ емкостью 16кх1 (64кх1).

Устройство состоит из генератора 1 импульсов, первого элемента И 2, счетчика 3 с количеством разрядов п + К + 2, где п - количество адресных входов, К - количество информационных разрядов (для ОЗУ 16кх1 п 14, К 1), элемента 4 задержки, дешифратора 5, второго элемента И 6, мультиплексора 7, первого триггера 8, третьего элемента И 9, коммутатора 10, элемента 11 регулируемой задержки. Устройство подключается к тестируемой микросхеме ОЗУ 12. Устройство также содержит анализатор 13 кодов, второй 14 и третий 15 триггеры. Тестируемая микросхема 12 соединена с элементами устройства с помощью коммутатора 10, представляющего интерфейсную коммутационную матрицу, различную для различных цоколевых корпусов. В качестве анализатора 13 кодов может быть использован сигнатурный анализатор.

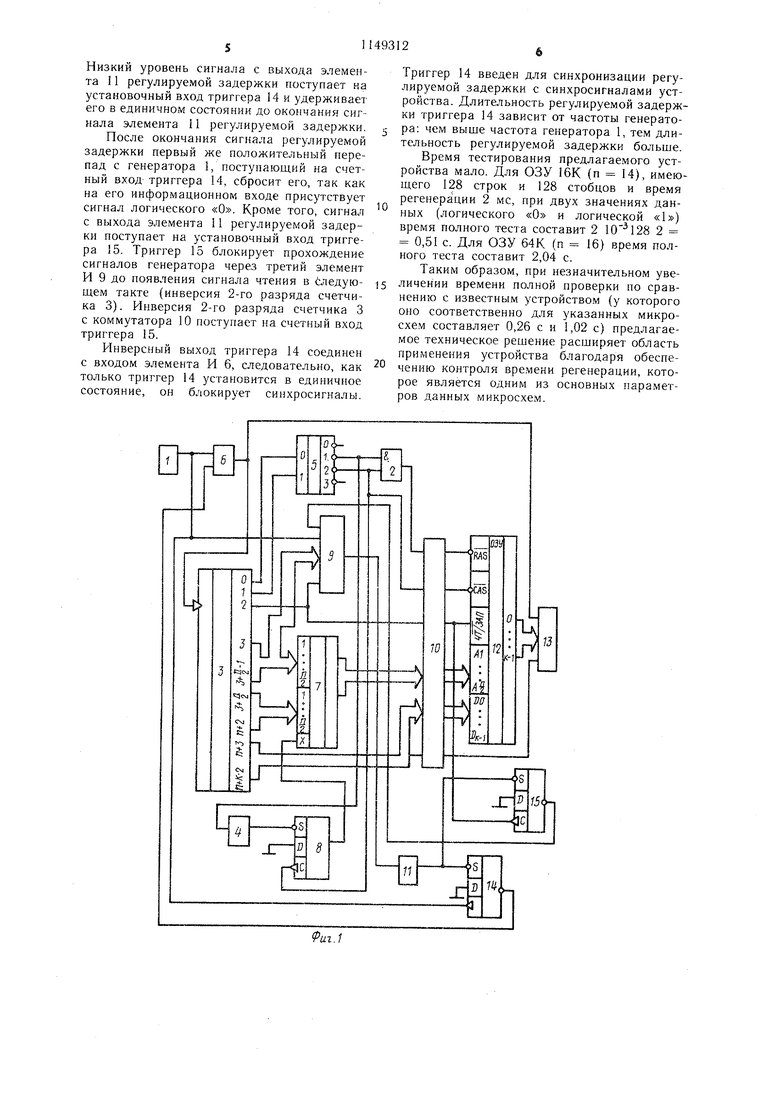

На временной диаграмме (фиг. 2) обозначены импульсы 16 генератора, синхроимпульсы 17, разряд «О (18) счетчика 3, разряд «1 (191 счетчика 3, сигнал RAS 20, сигнал CAS 21, сигнал «Чтение/Запись 22, статус «1 (23) дешифратора 5, сигнал 24 управления мультиплексора 7 на входе X, разряды с 3 по 9 обозначены позициями 25-31, сигнал 32 на входе элемента 11 регулируемой задержки, сигнал 33 на выходе элемента 11 регулируемой задержки, сигнал 34 на выходе второго триггера 14, сигнал 35 на выходе третьего триггера 15, команда 36 чтения, команда 37 записи, младшая половина адреса 38, старшая половина адреса 39, временная задержка 40 элемента 4.

Устройство работает следующим образом.

Генератор 1 формирует импульсы, которые проходят через элемент И 6, и запускает счетчик 3, который, работая в режиме непрерывного пересчета, вырабатывает еледующие друг за другом сигналы дешифрируемых статусов «О, «1, «2, «3 длительностью каждый по такту (периоду) синхросигнала, имеюшие активное нулевое значение. Дешифратор 5 формирует сигнал двойной ширины, имеющий также активное нулевое значение и используемый в качестве сигнала первого разрешения выборки RAS. Такое формирование сигнала RAS гарантирует его переключение внутри сигналов «Чтение/Запись входа данных и адресов. Выход статуса «2 дешифратора 5 используется в качестве сдвинутого на длительность, равную одному такту синхросигнала, сигнала второго разрешения выборки .

Таким образом, согласно временной ди аграмме (фиг. 2) во время каждой команды «Чтение и каждой команды «Запись имеют место два сдвинутых друг относительно друга сигнала разрешения выборки RAS, CKS

адресные сигналы подаются на корпус тестируемой микросхемы 12 от счетчика 3 через мультиплексор 7, который коммутирует во времени последовательно две половины адресных сигналов. Младшая половина адресных линий передается на выход мультиплексора 7 и, следовательно, на адресные входы (Aj, ..., An/2) текстируемой микросхемы 12 при нулевом значении управляющего входа мультиплексора 7, а старшая половина - при единичном значении. Прием адресных частей в корпус микросхемы 12осуществляется по спаду сигнала RAS (младшая половина адреса). Для реализации мультиплексирования половин адресных линий используется триггер 8, который по окончании сигнала CAS фронтом последнего устанавливается всегда в нулевое состояние по счетному входу. Поскольку прямой выход триггера 8 соединен с управляющим входом мультиплексора 7, то сразу по завершении определенной операции на выходе мультиплексора 7 устанавливается младшая половина адреса, которая и принимается спадом сигнала RAS следующей операции. Как известно, на прием младщей половины адреса фронтом сигнала RA требуется время не менее 50 не, поэтому фронтом сигнала «Статус 1 дешифратора 5 запускается элемент 4 задержки, который устанавливает триггер 8 в единичное состояние и соответственно на управляющем входе мультиплексора 7 устанавливается единичное состояние, которое обеспечивает передачу на выход мультиплексора старшей половины адресных линий до. возникновения сигнала . По спаду сигнала CAS осуществ-1яется прием старшей половины адресных линий в тестируемую микросхему 12.

Для микросхем К565РУЗ и К565РУ5 семь младщих разрядов адреса, прини.маемых по сигналу RAS, определяют адрес одной из 128 строк, по которой произойдет регенерация информации. Следовательно, чтобы проверить время регенерации динамических ОЗУ, необходимо каждое обращение (здесь два обращения: одно - с чтением, другое - с записью) к одноименной строке делать через 2 мс.

В предлагаемом устройство задержка обращения к одноименной строке осуществляется с помощью элементов И 6 и 9, элемента 11 регулируемой задержки, триггеров 14 и 15. После установки разрядов 2-9 счетчика в состояние логической «1 разряды 3-9 определяют все 128 строк БИС ОЗУ, участвующих в регенерации информации в начале команды записи. Элемент И 9 при поступлении на него сигнала высокого уровня с генератора 1 вырабатывает положительный импульс (длительностью, равной положительному значению синхросигнала), по заднему фронту которого запускается элемент 11 регулируемой задержки.

Низкий уровень сигнала с выхода элемента 11 регулируемой задержки поступает на установочный вход триггера 14 и удерживает его в единичном состоянии до окончания сигнала элемента 11 регулируемой задержки.

После окончания сигнала регулируемой задержки первый же положительный перепад с генератора 1, поступающий на счетный вход триггера 14, сбросит его, так как на его информационном входе присутствует сигнал логического «О. Кроме того, сигнал с выхода элемента 11 регулируемой задерки поступает на установочный вход триггера 15. Триггер 15 блокирует прохождение сигналов генератора через третий элемент И 9 до появления сигнала чтения в Следующем такте {инверсия 2-го разряда счетчика 3). Инверсия 2-го разряда счетчика 3 с коммутатора 10 поступает на счетный вход триггера 15.

Инверсный выход триггера 14 соединен с входом элемента И 6, следовательно, как только триггер 14 установится в единичное состояние, он блокирует синхросигна.ты.

Триггер 14 введен для синхронизации регулируемой задержки с синхросигналами устройства. Длительность регулируемой задержки триггера 14 зависит от частоты генератора: чем выше частота генератора 1, тем длительность регулируемой задержки больше.

Время тестирования предлагаемого устройства мало. Для ОЗУ 16К (п 14), имеющего 128 строк и 128 стобцов и время регенерации 2 мс, при двух значениях данных (логического «О и логической «1) время полного теста составит 2 2 0,51 с. Для ОЗУ 64К (п 16) время полного теста составит 2,04 с.

Таким образом, при незначительном увеличении времени полной проверки по сравнению с известным устройством (у которого оно соответственно для указанных микросхем составляет 0,26 с и 1,02 с) предлагаемое техническое решение расширяет область применения устройства благодаря обеспечению контроля времени регенерации, которое является одним из основных параметров данных микросхем.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1336123A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Устройство для контроля блоков оперативной памяти | 1990 |

|

SU1751821A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1336239A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОСХЕМ ОПЕРАТИВНОЙ ПАМЯТИ, содержащее генератор импульсов, счетчик, дешифратор, мультиплексор, коммутатор, анализатор кодов, первый триггер, элемент задержки, первый элемент И, причем входы первой группы коммутатора подключены к выходам мультиплексора, информационные и адресные входы которого подключены к соответствующим выходам. счетчика, управляющий вход мультиплексора подключен к выходу первого триггера, установочный вход которого подключен к выходу элемента задержки, а информационный вход соединен с щиной нулевого потенциала, входы дешифратора соединены с соответствующими выходами счетчика, первый выход дешифратора соединен с одним из входов первого элемента И и с входом элемента задержки, второй выход дешифратора соединен со счетным входом первого триггера и с другим входом первого элемента И, выход которого подсоединен к первому входу ком.мутатора, второй вход которого соединен с вторым выходом дешифратора, а третий вход и входы второй группы подключены к соответствующим выходам счетчика, первый управляющий вход анализатора кодов подключен к одному из выходов коммутатора, другие выходы которого являются выходами устройства, входами которого являются информационные входы анализатора кодов, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения контроля времени регенерации информации, в него введены элемент регулируе.мой задержки, второй и третий три1теры, второй и третий элементы И, причем выход второго элемента И соединен с iS вторым управляющим входом анализатора кодов и счетным входом счетчика, первый W вход - с выходом генератора импульсов, с первым входом третьего элемента И и счетным входом второго триггера, второй вход - с выходом второго триггера, установочные входы второго и третьего триггеров подк.;1ючевы к выходу элемента регулируемой задержки, информационные входы - к шине нулевого потенциала, вход элемента 4: регулируемой задержки соединен с выходом «:о третьего элемента И, второй вход которого подключен к выходу третьего триггера, тресо тий вход и группа входов третьего элемента И подключены к соответствующим выхоtvD дам счетчика, счетный вход третьего триггера соединен с одним из выходов коммутатора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля полупроводниковой памяти | 1978 |

|

SU749887A1 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-04-07—Публикация

1983-11-10—Подача