Изобретение относится к вычислительной технике и может быть использовано при построении запоминаюо х устройств на цилиндрических магнитных доменах различной информационной емкости.

Цель изобретения - повышение надежности модуля доменной памяти за счет использования общего стробирую- щего импульса при считывании и расширение области применения модуля доменной памяти в накопителях различной информационной емкости.

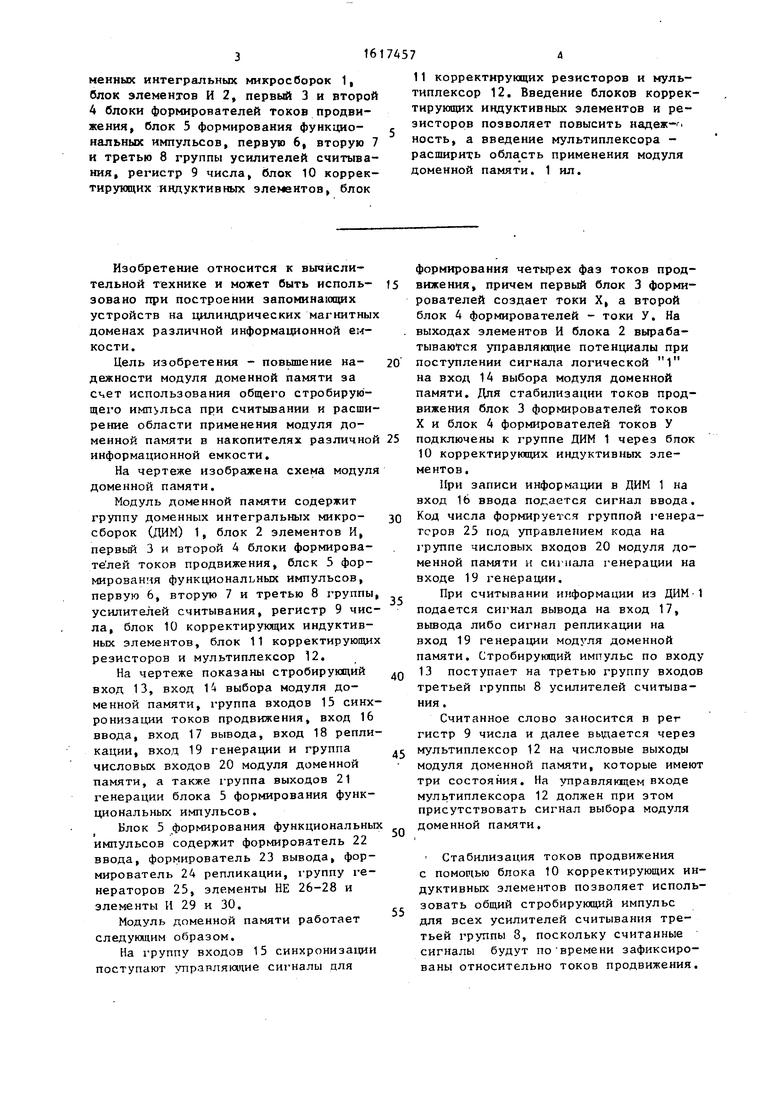

На чертеже изображена схема модуля доменной памяти.

Модуль доменной памяти содержит группу доменных интегральных микросборок (ДИМ) 1, блок 2 элементов И, первьй 3 и второй А блоки формирова- те лей токов продвижения, блек 5 формирования функциональных импульсов, первую 6, вторую 7 и третью 8 группы, усилителей считывания, регистр 9 числа, блок 10 корректирующих индуктивных элементов, блок 11 корректирующих резисторов и мультиплексор 12.

На чертеже показаны стробирующий вход 13, вход 14 выбора модуля доменной памяти, группа входов 15 синхронизации токов продвижения, вход 16 ввода, вход 17 вывода, вход 18 репликации, вход 19 генерации и группа числовых входов 20 модуля доменной памяти, а также группа выходов 21 генерации блока 5 формирования функциональных импульсов.

Блок 5 формирования функциональных импульсов содержит формирователь 22 ввода, формирователь 23 вывода, формирователь 24 репликации, группу генераторов 25, элементы НЕ 26-28 и злементы И 29 и 30.

Модуль доменной памяти работает следующим образом.

На группу входов 15 синхронизации поступают управляюи1ие сигналы для

0

0

5

5

0

5

формирования четырех фаз токов продвижения, причем первый блок 3 формирователей создает токи X, а второй блок 4 формирователей - токи У. На выходах элементов И блока 2 вырабатываются управляющие потенциалы при поступлении сигнала логической 1 на вход 14 выбора модуля доменной памяти. Для стабилизации токов продвижения блок 3 формирователей токов X и блок 4 формирователей токов У подключены к группе ДИМ 1 через бпок 10 корректирующих индуктивных элементов.

При записи инфop saции в ДИМ 1 на вход 16 ввода подается сигнал ввода. Код числа формируется группой генераторов 25 под управлением кода на группе числовых входов 20 модуля доменной памяти и сигнала генерации на входе 19 генерации.

При считывании информации из ДИМ-1 подается сигнал вывода на вход 17, вьшода либо сигнал репликации на вход 19 генерации модуля доменной памяти. Стробирующий импульс по входу 13 поступает на третью группу входов третьей группы 8 усилителей считывания .

Считанное слово заносится в per гистр 9 числа и далее вьщается через мультиплексор 12 на числовые выходы модуля доменной памяти, которые имеют три состояния. На управлягацем входе мультиплексора 12 должен при этом присутствовать сигнал выбора модуля доменной памяти.

Стабилизация токов продвижения с помощью блока 10 корректирующих индуктивных элементов позволяет использовать общий стробирующий импульс для всех усилителей считывания третьей группы 8, поскольку считанные сигналы будут по времени зафиксированы относительно токов продвижения.

516

Использование блока 11 корректирующих резисторов позволяет регулировать коэффициенты усиления усилителей считывания первой 6 и второй 7 групп с целью использования одного строби- рукщего импульса и одного уровня дискриминации в усилителях группы 8. Использование мультиплексора 12 с тремя состояниями позволяет использовать модуль доменной памяти в накопителях различной емкости, объединяя выходы аналогичных модулей.

Таким образом, введение блоков корректирующих индуктивных элементов и резисторов позволяет повысить надежность, а введение мультиплексора - расширить область применения модуля доменной памяти.

Формула изобретения

I Модуль доменной памяти, содержащий группу доменных интегральных микросборок, блок элементов И, первый и второй блоки формирователей токов продвижения, блок формирования функциональных импульсов, первую, вторую и третью группы усилителей считывания и регистр числа, причем входы первой групп ы блока элементов И соединены с входами выбора модуля доменной памяти, а входы второй группы блока элементов И являются группой входов синхронизации токов продвижения модуля доменной памяти, первый и второй выходы блока элементов И подключены соответственно к первому и второму входам первого блока формирователей токов продвижения, первый и второй выходы которого соединены соответственно с входами первой и второй групп доменных интегральных микросборок, входы третьей и четвертой i-pynn которых подключены соответственно к первому и второму выходам второго блока формирователей токов продвижения, первый и второй входы которого соединены соответственно с третьим и четвертым выходами блока элементов И, первый, второй, третий, четвертый входы и группа пятых входов блока формирования функциональных импульсов являются соответственно входами ввода

5

5

0

5

0

5

0

вывода, репликации, генерации и группой числовых входов модуля доменной памяти, выходы ввода и вывода блока формирования функциональных импульсов соединены соответственно с входами пятой и шестой групп доменных интегральных микросборок группы, входы седьмой группы которых подключены к группе выходов генерации блока формирования функциональных импульсов, выходы первой и второй групп доменных интегральных микросборок группы соединены с входами первых групп усилителей считывания первой и второй групп соответственно, выходы которых подключены соответственно к входам первой и второй групп усилителей считывания третьей группы, входы третьей группы которых соединены со стробиру- гацим входом модуля доменной памяти, выходы усилителей считывания третьей группы подключены к группе разрядных входов рег истра числа, отличающийся тем, что, с целью повышения надежности модуля за счет использования общего стробирукяцего импульса при считывании и расширения области применения модуля доменной памяти в накопителях различной информационной емкости, D него введены блок корректирующих индуктивных элементов, блок корректирующих резисторов и мультиплексоров, управляющий вход которого подключен к входу выбора модуля доменной памяти, информационные входы соединены с выходами ре- гис;,тра числа, а выходы мультиплексора являются числопыми выходами модуля доменной памяти, входы первой и второй групп блока корректирующих индуктивных элементов соединены с третьими выходами соотпетствешю первого и второго блоков формирователей токов продвижения, выходы первой и второй групп блока корректирующих индуктивных элементов подключены соответственно к входам восьмой и девятой групп доменных интегральных микросборок группы, в|-1ходы первой и второй групп блока корректирующих резисторов сое-. динены с входами группы усилителей считывания первой и второй групп соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Доменное запоминающее устройство | 1986 |

|

SU1336105A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Имитатор изображения точечных объектов | 1987 |

|

SU1425761A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1674221A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Доменный аналого-цифровой преобразователь | 1982 |

|

SU1172012A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1989 |

|

SU1675949A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на цилиндрических магнитных дисках различной информационной емкости. Цель изобретения - повышение надежности за счет использования общего стробирующего импульса при считывании и расширение области применения модуля доменной памяти в накопителях различной информационной емкости. Модуль доменной памяти содержит группу доменных интегральных микросборок 1, блок элементов И 2, первый и второй блоки формирователей 3 и 4 токов продвижения, блок 5 формирования функциональных импульсов, первую, вторую и третью группы усилителей 6, 7 и 8 считывания, регистр 9 числа, блок 10 корректирующих индуктивных элементов, блок 11 корректирующих резисторов и мультиплексор 12. Введение блоков корректирующих индуктивных элементов и резисторов позволяет повысить надежность, а введение мультиплексора - расширить область применения модуля доменной памяти. 1 ил.

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Electronic Design, 22, p | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1990-12-30—Публикация

1988-12-09—Подача