J3Tjp9

Finrr.ii

а Г --

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для отображения информации | 1989 |

|

SU1741123A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162248C2 |

| Устройство для вывода графической информации | 1986 |

|

SU1399809A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство поворота изображения на экране телевизионного приемника | 1987 |

|

SU1424028A1 |

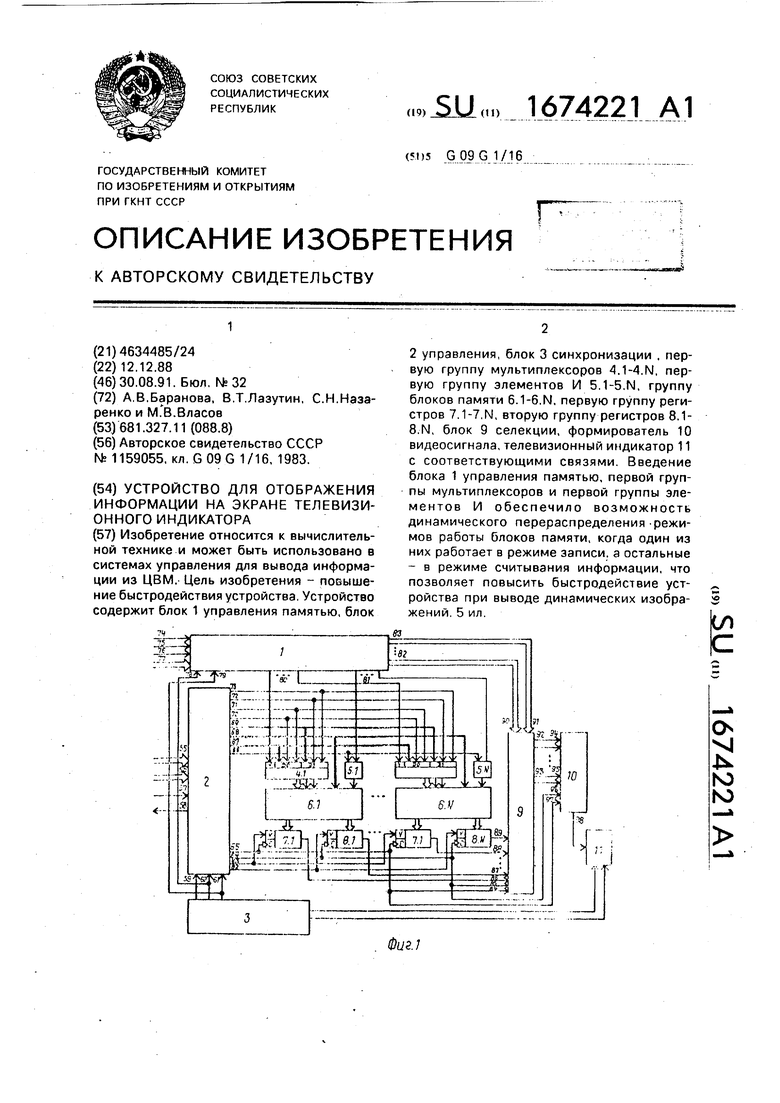

Изобретение относится к вычислительной технике и может быть использовано в системах управления для вывода информации из ЦВМ. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 управления памятью, блок 2 управления, блок 3 синхронизации, первую группу мультиплексоров 4.1 - 4.N, первую группу элементов И 5.1 - 5.N, группу блоков памяти 6.1 - 6.N, первую группу регистров 7.1 - 7.N, вторую группу регистров 8.1 - 8.N, блок 9 селекции, формирователь 10 видеосигнала, телевизионный индикатор 11 с соответствующими связями. Введение блока 1 управления памятью, первой группы мультиплексоров и первой группы элементов И обеспечило возможность динамического перераспределения режимов работы блоков памяти, когда один из них работает в режиме записи, а остальные - в режиме считывания информации, что позволяет повысить быстродействие устройства при выводе динамических изображений. 5 ил.

5 Л

Ј

« I

ж1р

I .

.&J4

61

;ЗЕ: ;ж

Ч

я «

ю

О VJ

N5 1ГО

Физ;

Изобретение относится к вычислительной технике и может быть использовано в системах управления для вывода информации из ЦВМ.

Цель изобретения - повышение быстродействия устройства.

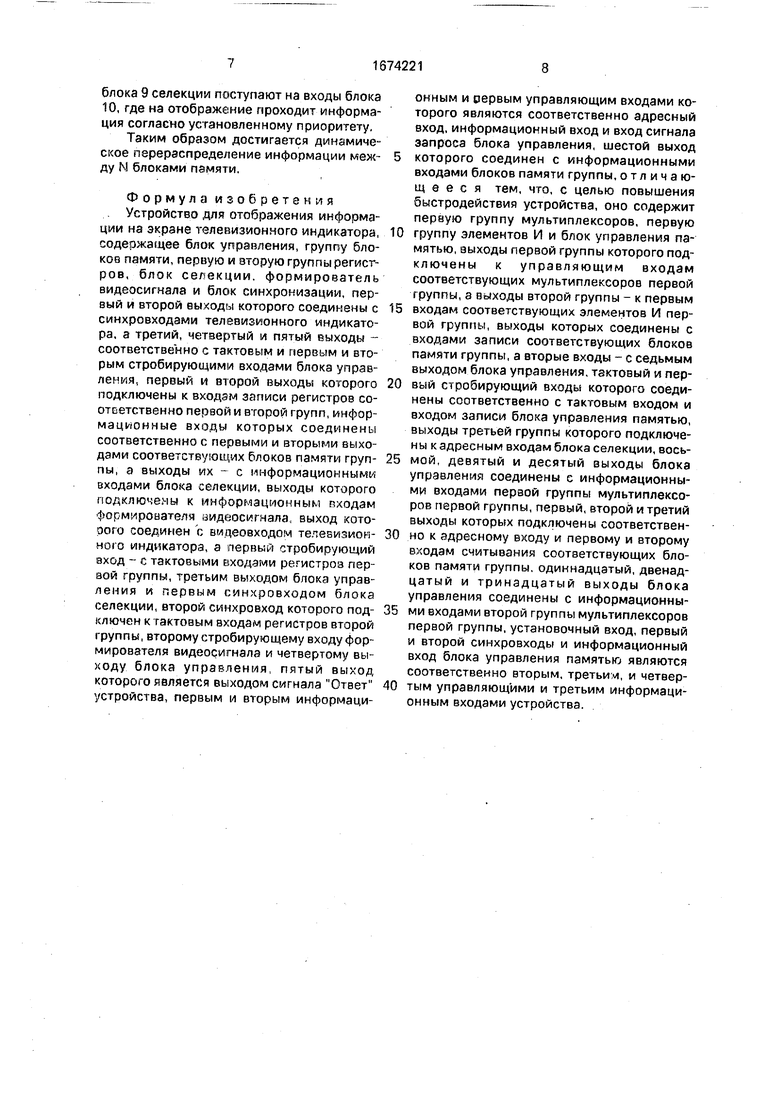

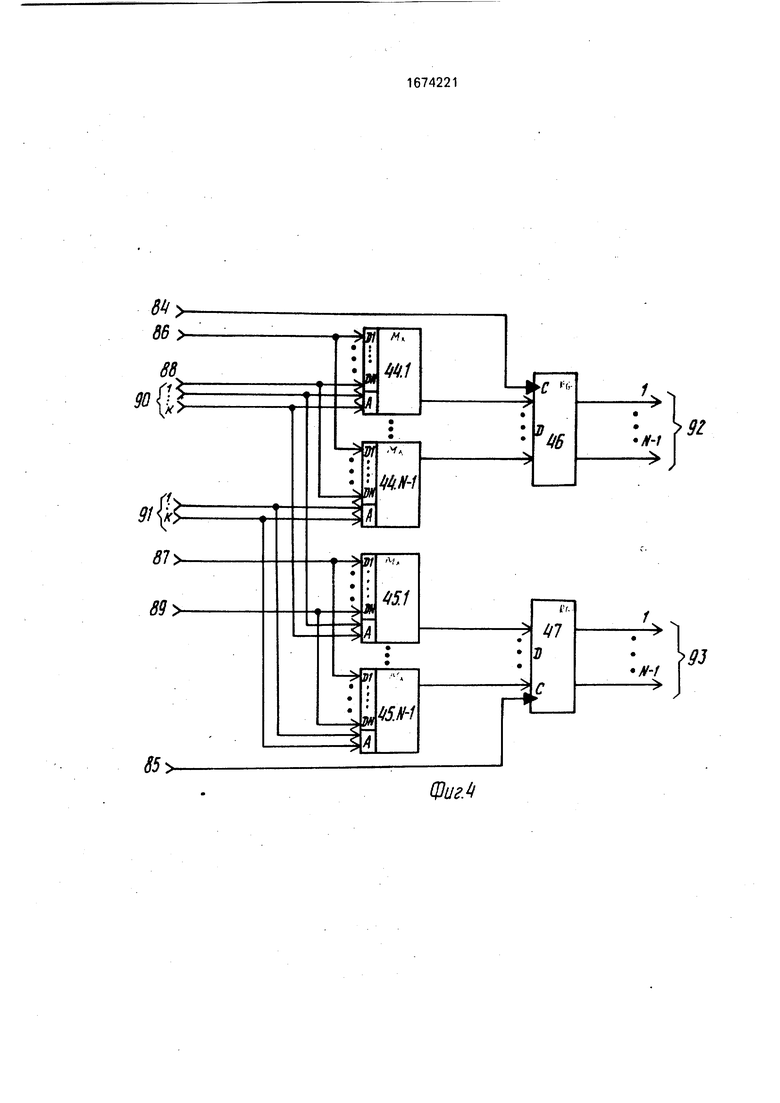

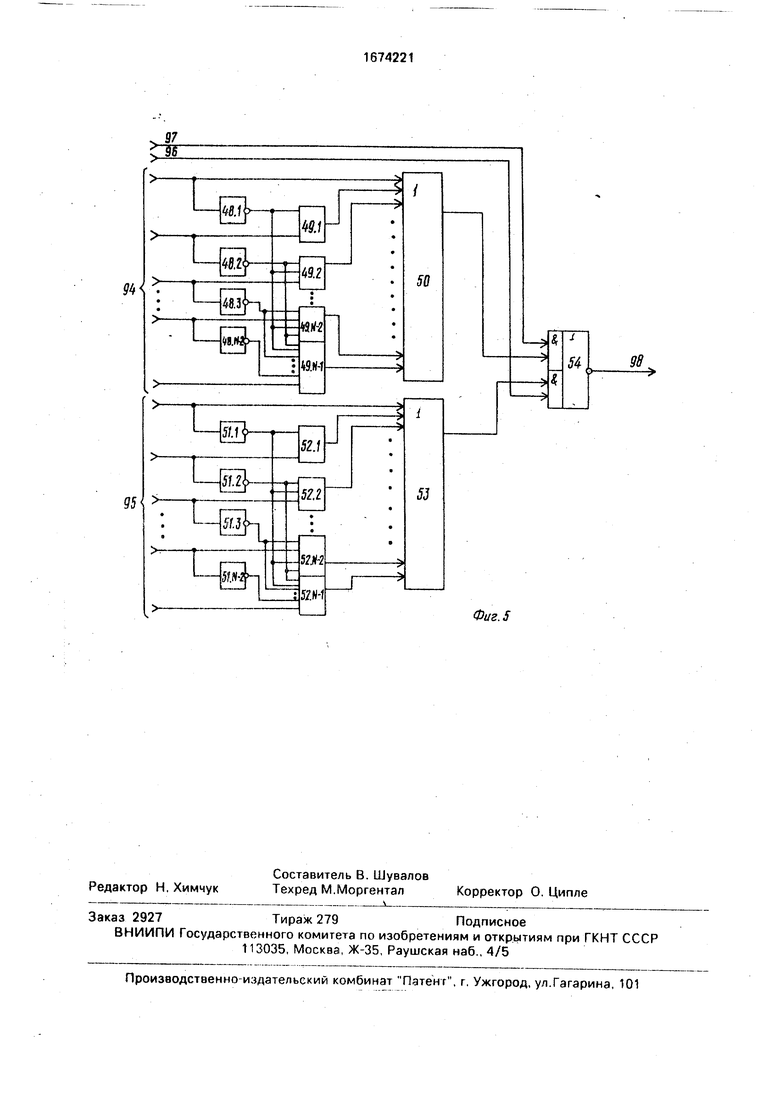

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - функциональная схема блока управления, на фиг. 3 - функциональная схема блока управления памятью; на фиг. 4 - функциональная схема блока селекции; на фиг. 5 - функциональная схема формирователя видеосигнала.

Устройство содержит блок 1 управления памятью, блок 2 управления, блок 3 синхронизации, первую группу мультиплексоров 4, первую группу элементов 5 И, группу блоков 6 памяти, первую группу регистров 7, вторую группу регистров 8, блок 9 селекции, формирователь 10 видеосигнала, телевизионный индикатор 11.

Блок 2 управления содержит первый счетчик 12, первый элемент 13 И, первый элемент 14 И-НЕ, первый регистр 15 сдвига, регистр 16 адреса, регистр 17 данных, второй элемент 18 И-НЕ. второй элемент 19 И, второй регистр 20 сдвига, элемент 21 НЕ. второй счетчик 22, третий элемент 23 И, третий счетчик 24, первый 25 и второй 26 элементы ИЛИ, четвертый счетчик 27. четвертый элемент 28 И, третий 29 и четвертый 30 элементы ИЛИ.

Блок 1 управления памятью содержит третий регистр 31 сдвига, первый 32 и второй 33 регистры, мультиплексор 34, первый дешифратор 35, третий регистр 36, второй дешифратор 37, третью группу регистров 38, четвертый регистр 39, вторую группу мультиплексоров 40, третью группу мультиплексоров 41, третий дешифратор 42, пятый регистр 43.

Блок 9 селекции содержиi че ертую группу мультиплексоров 44, пятую группу мультиплексоров 45 шестой 46 и седьмой 47 регистры.

Формирователь 10 видеосигнала содержит первую группу элементов 48 НЕ, вторую rp/ппу элементов 49 И пятый элемент 50 ИЛИ, вторую группу элементов 51 НЕ. третью группу элементов 52 И, шестой элемент 53 ИЛИ, элемент 54 2-2И-ИЛИ-НЕ

Позициями 55-73, 74-83, 84-93 94-98 обозначены входы и выходы соответственно блока 2 управления блока 1 управления памятью, блока 9 селекции и формирователя 10 видеосигнала.

Устройство обеспечивает возможность динамического перераспределения режимов работы блоков 6 памяти, когда один из них работает в режиме записи, а остальные

- в режиме считывания информации, что повышает быстродействие устройства при выводе динамических изображений.

Устройство работает следующим образом.

По сигналу 74 установки в исходное состояние блока 1 мультиплексор 34 подключает выходы К-разрядного регистра 32 к соответствующим входам регистров 38.138.N-1 и устанавливает К разрядный регистр 39 и регистр 36 в состояние логической единицы. По сигналу синхронизации команды 75 и 76. 2К разрядов команды переписываются следующим образом: в регистр 32 первые К разрядов по второму сигналу синхронизации 76 и в регистр 33 вторые К разрядов, по первому сигналу синхронизации 75. кроме этого на сдвиговом регистре

31формируется последовательность так- тов с длительностью, равной периоду следования тактовой частоты (вход 79)

К разрядов команды с выхода регистра

32поступают на вход дешифратора 35 и через мультиплексор 34 на входы регистра

36 и регистры 38 1-38N-1. К разрядов команды с выхода регистра 33 поступают на адресные входы мультиплексоров 40 1-40.К. Второй такт со сдвигового регистра 31 поступает на стробирующий вход дешифратора 35 и на соответствующем выходе дешифратора появляется сигнал синхронизации одного из регистров 38.1- 38.N-1. По этому сигналу К-разрядный код со входа регистров 38 1-38 N-1 переписывается в один из этих регистров.

Таким образом по сигналу установки в исходное и подаче N-1 сигналов синхронизации и N-1 «-разрядных команд, происходит начальное упорядочное распределение

блоков памяти по типу хранимой в них информации и установка N о го б юка памяти в режим записи

N выходов дешифраторов 37 и 42 управляют подключением шин адргса и сигналов

управления от блока 2 управления через мультиплексоры 4,1-4 N и элементы 5 И к соответствующим блокам 6 памяти

После снятия CHI нала установки в исходное состояние устройство готово к работе

Количество регистров 38.1-38.N-1 соответствует количеству информационных слоев одновременно огоГрлжаемых на экране индикатора, в каждом из них хранится физмческий код (номер) Ьлока памяти,формирующего слой информации.

От внешнего блока сопряжения по сигналу синхронизаци 76 в регистр 32 осущест- вл-ется запись кода одного из регистров

Вторым тактом со сдвигового регистра 31 осуществляется выделение сигнала на соответствующем выходе дешифратора 35 и запись им в один из регистров 38.1-38.N-1 данных, хранимых в регистре 39, поступающих на вход этих регистров через мультиплексор 34, управляемый сигналом Установка в исходное состояние.

Третьим тактом синхронизации осуществляется перезапись информации из регистра 43 в регистр 39.

Кроме того сигналом синхронизации 75 от внешнего блока сопряжения осуществляется запись информации в регистр 33. Выходная информация регистра составляет адрес мультиплексоров 40.1-40.К для прохождения информации от одного из регистров 38.1-38.N-1 на дешифратор 42, который выделяет сигнал разрешения прохождения сигнала записи (элементы 5.1-5.N) в один из блоков б. 1-6.N памяти.

В блоке 2 управления (фиг. 2) по сигналам синхронизации по кадру, строке и тактовой частоте, поступающих из блока синхронизэ.ции, формируются необходимые сигналы управления и адрес для циклического считывания из блоков памяти информации синхронно с телевизионной разверткой.

Счетчик 12 и элемент И 13 формируют тактовый сигнал запуска для формирования на сдвиговых регистрах 15 и 20 управляющих сигналов для блоков памяти, работающих в режиме записи и считывания информации. Элементы 18 разрешают прохождение сигнала запуска на последовательный вход сдвигового регистра 20 только во время, определенное сигналами синхронизации по строке и кадру, что позволяет формировать необходимые управляющие сигналы элементами 25 и 26 и перебор ад- сов на счетчике 27 синхронно с регулярной телевизионной разверткой. Элемент 19 формирует прохождение тактовой частоты только во время, определенное сигналами синхронизации по строке и кадру, для синхронизации нечетных сдвиговых регистров 7.1-7.N блока 9 селекции, блока 10 и формирования счетчиком 22 и элементом 23 И управляющего сигнала записи для вышеуказанных регистров сдвига. Элемент 21 НЕ формирует инверсное значение тактовой частоты для синхронизации четных сдвиговых регистров 8.1-8.N блока 9 селекции, блока 10 и формирования счетчиком 24 и элементом 23 Л управляющего сигнала записи для соответствующих сдвиговых регистров.

Адрес (55) и данные (56) из устройства сопряжения, поступающие соответственно на регистры 16 и 17,сопровождаются сигналом запроса (57), который, поступая на вход

элемента 14 блока 2 управления, разрешает прохождение сигнала запуска от элемента 13 И на последовательный вход сдвигового регистра 15. Это позволяет формировать на элементах 29 и 30 ИЛИ и пятом выходе сдви0 гового регистра 15 необходимые управляющие сигналы для блока памяти, работающего в режиме записи, а также сигнал ответа в устройство сопряжения и синхронизацию записи в регистры 16 и 17

5 соответственно со второго и первого выходов сдвигового регистра 15. Управляющие сигналы с выходов элементов 29 и 30 ИЛИ и адрес с регистра 16 поступают на входы мультиплексоров 4.1-4.N, а сигнал записи на

0 входы элементов 5 И.

Управляющие сигналы выходов элементов 25 и 26 ИЛИ и адрес со счетчика 27 поступают на другие входы мультиплексоров 4.1-4.N.

5 Отсутствие сигнала синхронизации команды из блока сопряжения сохраняет в блоке 1 состояние выходов, сформированное по сигналу установки в исходное состояние, которое соответствует установке для

0 записи N-oro блока памяти. При этом на N выходах дешифраторов 37 и 42 устанавливается сигнал О, а на остальных - сигнал 1, что позволяет подключить первую группу управляющих сигналов и адрес с мульти5 плексора4.М и разрешить прохождение сигнала записи от элемента 5.N на вход N блока памяти. Таким образом, осуществляется запись данных из блока 2 управления в выбранный для записи блок памяти. Для

0 остальных блоков памяти остается подключена другая группа управляющих сигналов и адрес с мультиплексоров 4.1-4.N-1 и блокировка сигнала записи от элементов 5.1- 5.N-1, что соответствует установке блоков

5 памяти 6.1-6.N-1 в считывание.

Блок 9 селекции позволяет осуществить динамическое распределение слоев на выходе схемы для отображения на экран индикатора.

0 Адресным сигналом мультиплексоров 44.1. 45.1 являются выходные данные регистра 38.1, а мультиплексоров 44.N-1, 45.N-1 выходные данные регистра 38.N-1.

Информационные входы мультиплексо5 ров 44.1-44.N-1 подключены к соответствующим выходам сдвиговых регистров нечетной информации, а информационные входы мультиплексоров 45.1-45.N-1 к соответствующим выходам сдвиговых регистров четной информации. Сигналы с выходов

блока 9 селекции поступают на входы блока 10, где на отображение проходит информация согласно установленному приоритету.

Таким образом достигается динамическое перераспределение информации между N блоками памяти,

Формула изобретения Устройство для отображения информации на экране телевизионного индикатора, содержащее блок управления, группу блоков памяти, первую и вторую группы регистров, блок селекции, формирователь видеосигнала и блок синхронизации, первый и второй выходы которого соединены с синхровходами телевизионного индикатора, а третий, четвертый и пятый выходы - соответственно с тактовым и первым и вторым стробирующими входами блока управления, первый и второй выходы которого подключены к входам записи регистров соответственно первой и второй групп, инфор- мационные входы которых соединены соответственно с первыми и вторыми выходами соответствующих блоков памяти группы, а выходы их - с информационными входами блока селекции, выходы которого подключены к информационным входам формирователя ьидеосигнала, выход кото- оого соединен с видеовходом телевизионною индикатора, а первый стробирующий вход - с тактовыми входами регистров первой группы, третьим выходом блока управления и первым синхровходом блока селекции, второй синхровход которого подключен к тактовым входам регистров второй группы, второму стробирующему входу формирователя видеосигнала и четвертому выходу блока управления, пятый выход которого является выходом сигнала Ответ устройства, первым и вторым информационным и оервым управляющим входами которого являются соответственно адресный вход, информационный вход и вход сигнала запроса блока управления, шестой выход

которого соединен с информационными входами блоков памяти группы, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит первую группу мультиплексоров, первую

группу элементов И и блок управления памятью, выходы первой группы которого под- глючены к управляющим входам соответствующих мультиплексоров первой группы, а выходы второй группы - к первым

входам соответствующих элементов И первой группы, выходы которых соединены с входами записи соответствующих блоков памяти группы, а вторые входы - с седьмым выходом блока управления, тактовый и первый стробирующий входы которого соединены соответственно с тактовым входом и входом записи блока управления памятью, выходы третьей группы которого подключены к адресным входам блока селекции, восьмой, девятый и десятый выходы блока управления соединены с информационными входами первой группы мультиплексоров первой группы, первый, второй и третий выходы которых подключены соответственно к адресному входу и первому и второму входам считывания соответствующих блоков памяти группы, одиннадцатый, двенадцатый и тринадцатый выходы блока управления соединены с информационными входами второй группы мультиплексоров первой группы, установочный вход, первый и второй синхровходы и информационный вход блока управления памятью являются соответственно вторым, третьим, и четвертым управляющими и третьим информационным входами устройства.

а

IZZW.91

| Авторское свидетельство СССР № 1159055, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1991-08-30—Публикация

1988-12-12—Подача