I-1 3-й строб записи t

гистр 2, формирователь 3 псевдослучайной последовательности, I блоков 4 одределе- ния входов-выходов, первый дешифратор 5, регистр 6 задания режима работы, I элементов 7 задержки, блок 8 индикации, второй дешифратор 9, регистр 10 задания вида синхронизации, I мультиплексоров 11, регистр 12 задания входов синхронизации, блок 13 элементов И, блок 14 задания исходных данных и подключено к ОК 15.1 блоков 1 формирования воздействий и приема результатов предназначены для реализации следующих функций: 1) генерации циклических воздействий на k-разрядную шину ОК, 2) генерации последовательности на шину данных ОК, 3) формирования сигнатур с выходов ОК, 4) генерации синхроимпульсов на р-входы синхронизации ОК. Сформированные сигнатуры индицируются блоком 8 индикации. 12 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1987 |

|

SU1506450A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Генератор псевдослучайной последовательности импульсов | 1985 |

|

SU1277362A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1520521A1 |

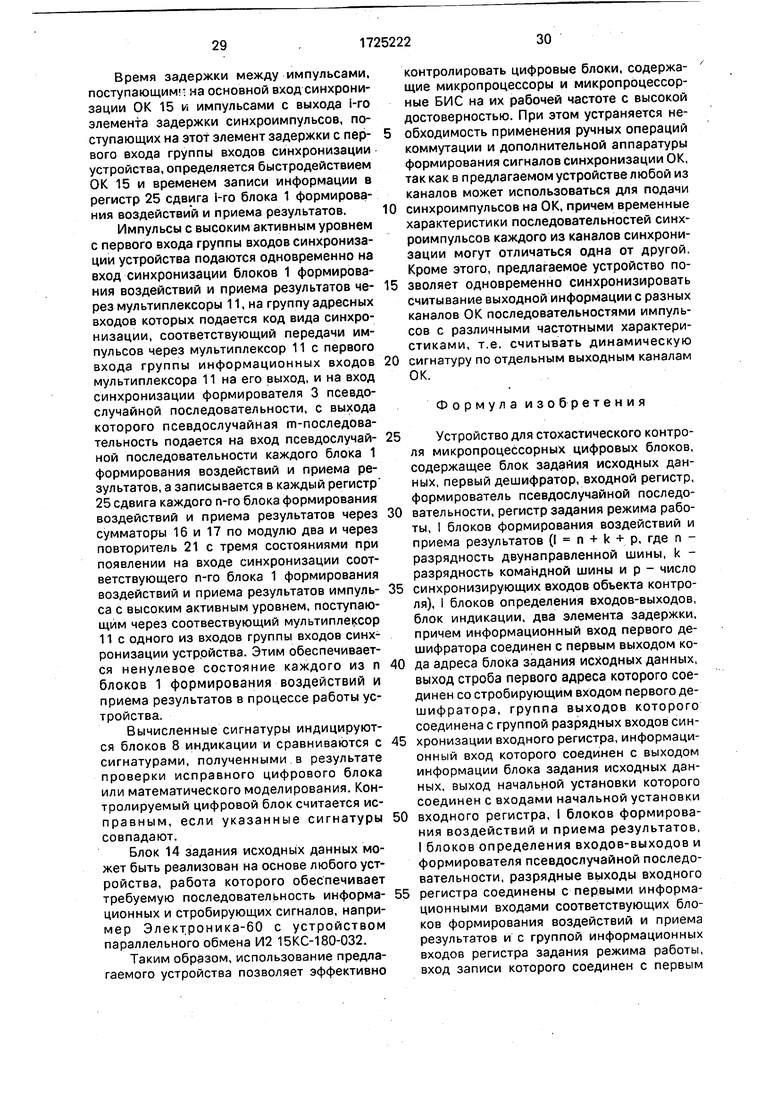

Изобретение относится к цифровой вычислительной технике и может использоваться для автоматизированного контроля блоков ЦВМ, содержащих микропроцессорные БИС. Цель изобретения - расширение функциональных возможностей устройства за счет считывания динамической сигнатуры и формирования воздействий, отличающихся по временным характеристикам, по отдельно выбранным каналам. Устройство содержит 1 блоков 1 формирования воздействий и приема результатов (I п + к + р, п - разрядность командной шины OK, p - число синхронизирующих входов О К), входной ре

Изобретение относится цифровой вычислительной технике и может использоваться для автоматизированного контроля блоков ЦВМ, содержащих микропроцессорные БИС.

Известно устройство для контроля микропроцессорных цифровых блоков, содержащее блок управления, 21 формирователей остатка (где I - разрядность двунаправленной шины данных контролируемого цифрового блока), I сумматоров по модулю два, k кольцевых сдвиговых регистров (где k - разрядность командной шины контролируемого цифрового блока), дешифратор, регистр, элемент задержки, I повторителей с тремя состояниями, блок индикации, причем первый выход блока управления соединен с входами записи с первого по k-й кольцевых сдвиговых регистров, вход начальной установки устройства подключен к входам сброса с первого по 21-й формирователей остатка, к входу сброса регистра, к входу начальной установки блока управления и к входам сброса с первого по k-й кольцевых сдвиговых регистра, второй выход блока управления соединен с входами синхронизации с первого по 21-й формирователей остатка, с входами синхронизации с первого по k-й кольцевых сдвиговых регистров и через элемент задержки с выходом устройства для подключения к синхровходу контролируемого блока, выходы с первого по (Ы)-й формирователей остатка соединены с информационными входами соответственно с второго по 1-й формирователей остатка и с первыми входами соответственно с первого по (1-1) сумматоров по модулю два, выход 1-го формирователя остатка соединен с первым входом 1-го сумматора по модулю два, вход кода номера кольцевого регистра устройства подключен к информационному входу дешифратора, группа выходов которого соединена с группой разрядных входов синхронизации регистра, информационный вход которого является информационным

входом устройства, выходы разрядов регистра соединены с информационными входами с первого по k-й кольцевых сдвиговых регистров, выходы которых образуют выход

устройства для подключения к входу команд контролируемого блока, выходы с первого по 1-й сумматоров по модулю два соединены с информационными входами соответственно с (1+1)-го по формирователей остатка,

первый и второй входы логических условий блока управления являются соответственно входами кода длины команды и кода числа испытаний устройства, первый, второй и третий входы синхронизации блока управления являются соответственно первым, вторым и третьим синхровходами устройства, третий выход блока управления является выходом готовности устройства, группа входов-выходов устройства для подключения к

входам-выходам данных контролируемого блока подключена к выходам соответственно с первого по 1-й повторителей с третмя состояниями-и к вторым входам соответственно с первого по 1-й сумматоров по модулю два, выходы с (1 + 1)-го по 21-й формирователей остатка соединены с информационными входами соответственно с первого по 1-й повторителей с тремя состояниями, входы направления передачи которых подключены к входу направления передачи устройства, группы выходов с (1+1)-го по 21-й формирователей остатка соединены с группой входов блока индикации, вход синхронизации дешифратора подключен к входу записи, первый и второй входы константы блока управления подключены к входам соответственно нулевого и единичного потенциалов устройства, причем блок управления содержит два буферных регистра, два счетчика, два дешифратора, два формирователя импульсов, три триггера, элемент задержки, три элемента НЕ, три элемента И, элемент ИЛИ-НЕ, элемент ИЛИ и генератор тактов, причем вход начальной установки блока управления подключей к входам сброса первого и второго буферных регистров и к входу первого элемента НЕ, выход которого соединен с входами сброса первого и второго счетчиков, первый вход синхронизации блока управления подключен к счетному входу первого счетчика, информационный вход которого соединен с выходом первого буферного регистра, информационный вход котрого является первым входом логических условий блока управления, второй вход синхронизации блока управления подключен к синхровходу первого буферного регистра и через элемент задержки к первому входу первого элемента И, выход которого соединен с входом записи первого счетчика, выход которого соединен с информационным входом первого дешифратора, выход которого через второй элемент НЕ соединен с синхровходом первого триггера и первым входом элемента ИЛИ-НЕ, выход которого соединен с входом первого формирователя импульсов и является вторым выходом блока управления, информационный вход второго буферного регистра является вторым входом логических условий блока управления, третий вход синхронизации блока управления подключен к синхровходу второго буферного регистра, выход которого соединен с информационным входом второго счетчика, выход которого соединен с информационным входом второго дешифратора, выход которого через третий элемент НЕ соединен с вторым входом элемента ИЛИ- НЕ, с J, К- и S-входами первого триггера и с S-входами второго и третьего триггеров, выход генератора тактов соединен с первыми входами второго и третьего элементов И, выход первого формирователя импульсов соединен с входом второго формирователя импульсов, с первым входом элемента ИЛИ и синхровходом второго триггера, инверсный выход которого соединен с вторым входом второго элемента И, выход которого соединен с синхровходом третьего триггера, инверсный выход которого соединен с вторым входом третьего элемента И, выход которого соединен со счетным входом второго счетчика и с вторым входом элемента ИЛИ, выход которого является первым выходом блока управления, выход второго формирователя импульсов соединен с входом записи второго счетчика и с вторым входом первого элемента И, выход первого триггера яв- ляется третьим выходом блока управления, J-вход третьего триггера подключен к первому входу константы блока управления, второй вход константы блока

управления подключен к J- и К-входам второго триггера и к К-входу третьего триггера. Недостатком данного устройства является наличие отличающихся по структуре и

функциям блока для генерации потоков команд и данных, а также жесткой связи известного устройства с микропроцессорным цифровым блоком - объектом контроля (ОК). Такое разделение функций приводит к до0 полнительным временным затратам на коммутацию входных сигналов при смене типа проверяемого устройства, либо при изменении функции входных линий в ОК. Кроме того, при работе формирователей остатка

5 известного устройства на двунаправленную шину ОК необходим предварительный анализ входных потоков команд для определения направления передачи информации по шине ОК, что приводит также к увеличению

0 времени контроля, в случае же отсутствия информации о системе команд ОК, контроль последних вообще невозможен.

Наиболее близким по технической сущности к предлагаемому является устройство

5 для стохастического контроля микропроцессорных цифровых блоков, содержащее блок задания исходных данных, дешифратор, входной регистр, формирователь псевдослучайной последовательности, блок

0 индикации, регистр задания режима работы, I блоков формирования воздействий и приема результатов (I n + k, n - разрядность двунаправленной шины данных ОК, k - разрядность командной шины ОК), I бло5 ков определения входов-выходов, два элемента задержки, причем группа информационных входов дешифратора соединена с группой адресных выходов блока задания исходных данных, строб адреса ко0 торого соединен со стробирующим входом дешифратора, группа выходов которого соединена с группой синхронизирующих входов входного регистра, информационный вход которого соединен с информаци5 онным выходом блока задания исходных данных, выход начальной установки которого соединен с входами начальной установки входного регистра, формирователя псевдослучайной последовательности I бло0 ков формирования воздействий и приема результатов и I блоков определения входов- выходов, i-й выход входного регистра соединен с i-м информационным входом регистра задания режима работы и с первым инфор5 мационным входом i-ro блока формирования воздействий и приема результатов, где

1 1,2I, вход задания режима работы i-ro

блока формирования входных воздействий и приема результатов соединен с i-м выходом регистра задания режима работы, вход

Записи которого является первым выходом строба записи блока задания исходных данных, выход синхронизации которого соединен с входом синхронизации формирователя псевдослучайной последовательности, с входами первого и второго элементов задержки и с входом синхронизации I блоков формирования воздействий и приема результатов, входы строба записи которых объединены и подключены к второму выходу строба записи блока задания исходных данных, входы псевдослучайной последовательности блоков формирования воздействий и приема результатов объединены и подключены к выходу формирователя псевдослучайной последовательности, входы синхронизации блоков определения входов-выходов объединены и подключены к выходу второго элемента задержки, выход 1-го блока формирования воздействий и приема результатов соединен с информационным входом 1-го блока определения входов-выходов, вход-выход которого соединен с вторым информационным входом 1-го блока формирования воздействий и приема результатов и является i-м входом-выходом группы информационных входов-выходов устройства для подключения к контролируемому блоку, выход первого элемента задержки является выходом синхронизации устройства для подключения к соответствующему входу контролируемого блока, группа информационных выходов 1-го блока формирования воздействий и приема результатов соединена с 1-й группой входов блока индикации.

Недостатком известного устройства является невозможность динамического изменения режимов синхронизации процессов формирования воздействий и снятия реакций по произвольно выбранным каналам. Это приводит к необходимости применения ручных операций коммутации и дополнительной аппаратуры формирования сигналов синхронизации контролируемого блока, а также не позволяет считывать динамическую сигнатуру.

Цель изобретения - расширение функциональных возможностей устройства путем считывания динамической сигнатуры и формирования воздействий, отличающихся по временным характеристикам, по отдельно выбранным каналам.

Поставленная цель достигается тем, что в устройство для стохастического контроля микропроцессорных цифровых блоков, содержащее блок задания исходных данных, первый дешифратор, входной регистр, формирователь псевдослучайной последовательности, регистр задания режима работы, I блоков формирования воздействий и приема результатов (I п + к + р, п - разрядность двунаправленной шины данных ОК, к- разрядность командной шины ОК, р - число синхронизирующих входов ОК), I блоков определения входов-выходов, блок индикации, два .элемента задержки, причем информационный вход первого дешифрато0 ра соединен с первым выходом кода адреса блока задания исходных данных, выход строба первого адреса которого соединен со стробирующим входом первого дешифратора, группа выходов которого соединена

5 с группой разрядных входов синхронизации входного регистра, информационный вход которого соединен с выходом информации блока задания исходных данных, выход начальной установки которого соединен с вхо0 дами начальной установки входного регистра, I блоков формирования воздействий и приема результатов, I блоков определения входов-выходов и формирователя псевдослучайной последовательности, раз5 рядные выходы входного регистра соединены с первыми информационными входами соответствующих блоков формирования воздействий и приема результатов и с группой информационных входов регистра зада0 ния режима работы, вход записи которого соединен с первым выходом строба записи блока задания исходных данных, разрядные выходы регистра задания режима работы соединены с входами задания режима рабо5 ты соответствующих блоков формирования воздействий и приема результатов, вход синхронизации устройства соединен с входом синхронизации формирователя псевдослучайной последовательности, выход

0 каждого блока формирования и приема результатов соединен с установочные входом соответствующего блока определения входов-выходов, вход-выход каждого блока определения входов-выходов соединен с

5 вторым информационным входом соответствующего блока формирования воздействий и приема результатов и является соответствующим входом-выходом устройства для подключения к соответствующим

0 входам-выходам контролируемого объекта, информационные входы I блоков определения входов-выходов подключены к шине константы нуля устройства, группы выходов блоков формирования воздействий и при5 ема результатов соединены с группой входов блока индикации, выход формирователя псевдослучайной последовательности соединен с входами псевдослучайной последовательности I блоков формирования воздействий и приема результатов, установочные входы формирователя псевдослучайной последовательности и входного регистра подключены к шине константы единицы устройства, введены второй дешифратор, регистр задания вида синхронизации, регистр задания входов синхронизации, блок элементов И, I мультиплексоров, I-2 элементов задержки, причем информационный вход второго дешифратора соединен со вторым выходом адреса блока задания исходных данных, выход строба второго адреса которого соединен со стро- бирующим входом второго дешифратора, группа выходов которого соединена с группой входов синхронизации регистра зада- ния вида синхронизации, группа информационных входов которого соединена с выходом кода вида синхронизации блока задания исходных данных, второй и третий выходы строба записи которого соединены со стробирующими входами соответственно регистра задания входов синхронизации и блока элементов И, группа информационных входов которого соединена с выходами регистра задания входов син- хронизации, группа информационных входов которого соединена с разрядными выходами входного регистра, выходы блока элементов И соединены с входами строба записи соответствующих блоков формирования воздействий и приема результатов, выход каждого мультиплексора соединен с входом синхронизации соответствующего блока формирования воздействий и приема результатов и через соответствующий элемент задержки с входом синхронизации соответствующего блока определения входов-выходов, группа входов синхронизации устройства соединена с группами информационных входов I мультиплексоров, адресные входы которых соединены с соответствующими группами выходов регистра задания вида синхронизации, выход начальной установки блока задания исходных данных соединен с входом начальной установки регистра задания вида синхронизации, установочный вход которого соединен с шиной константы единицы устройства.

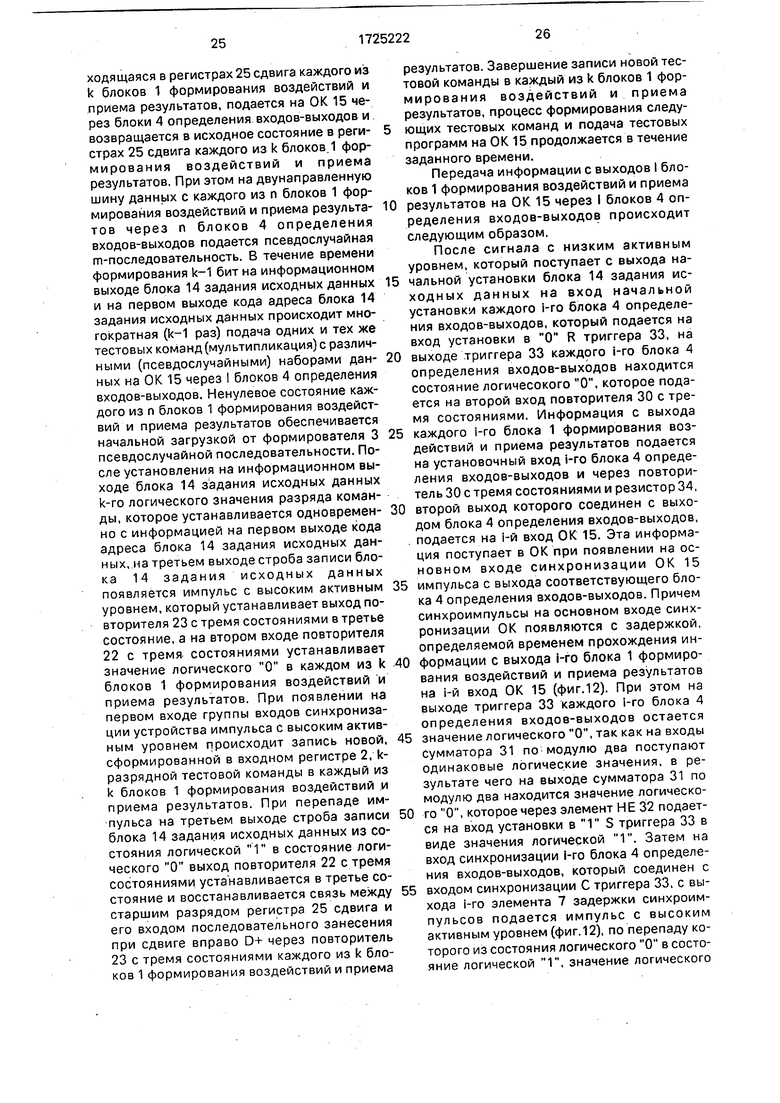

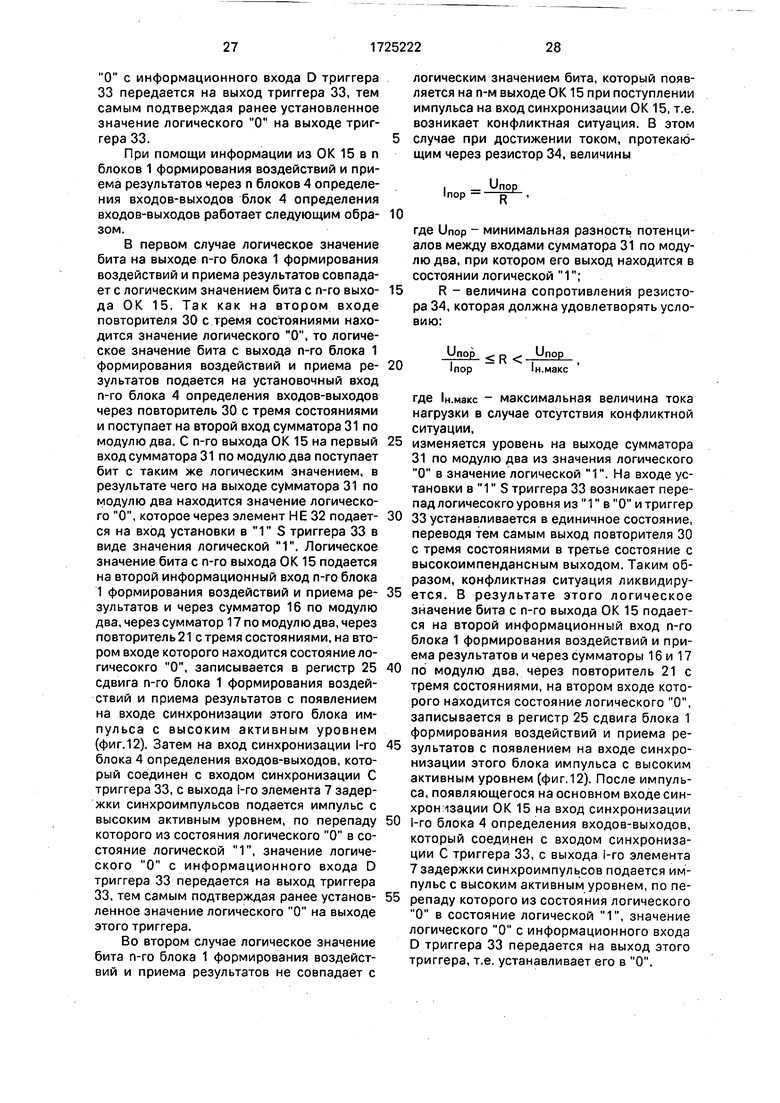

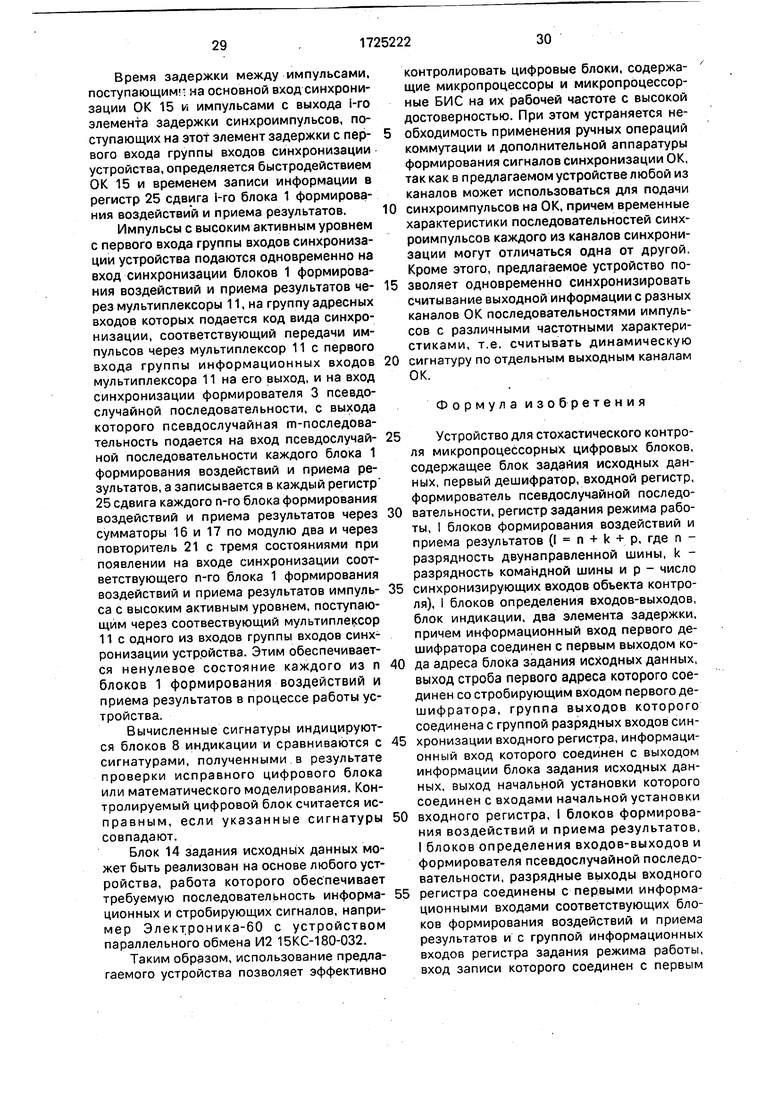

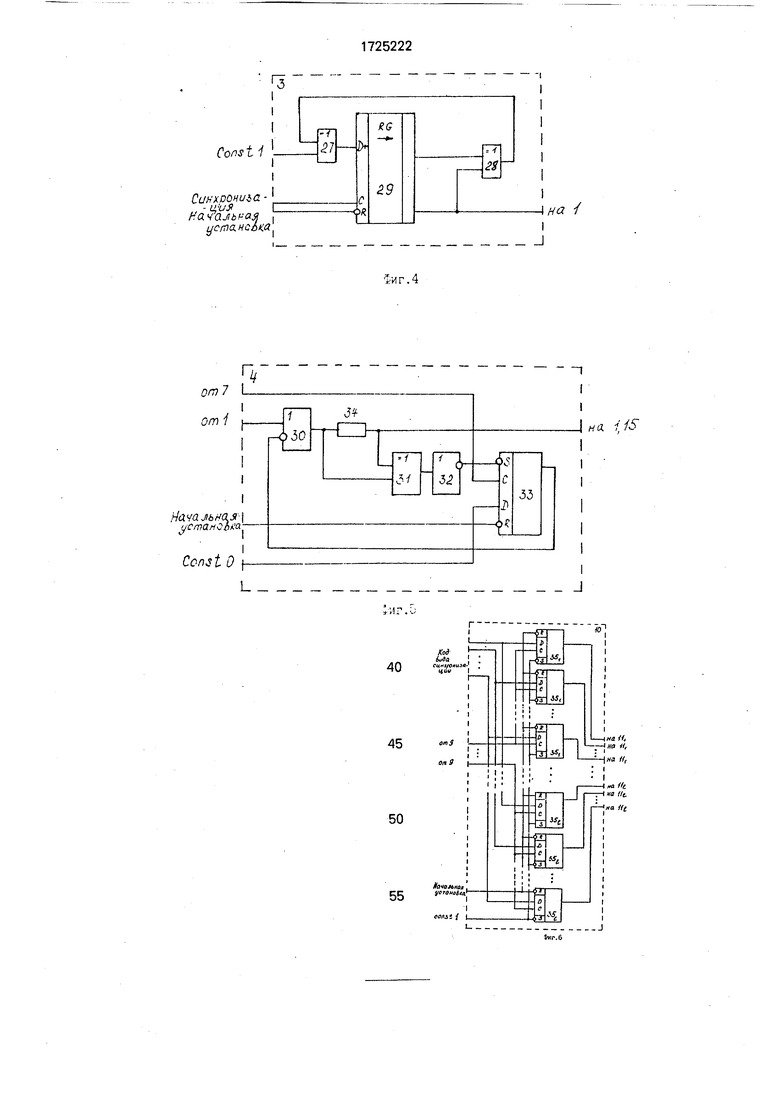

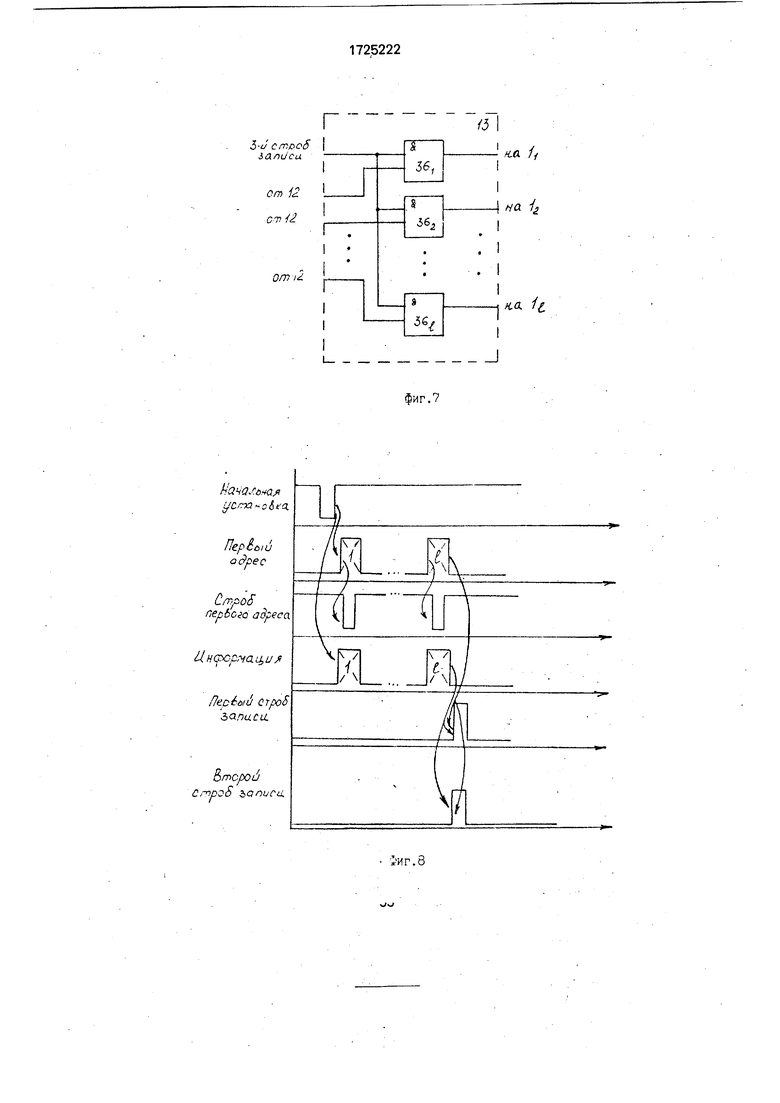

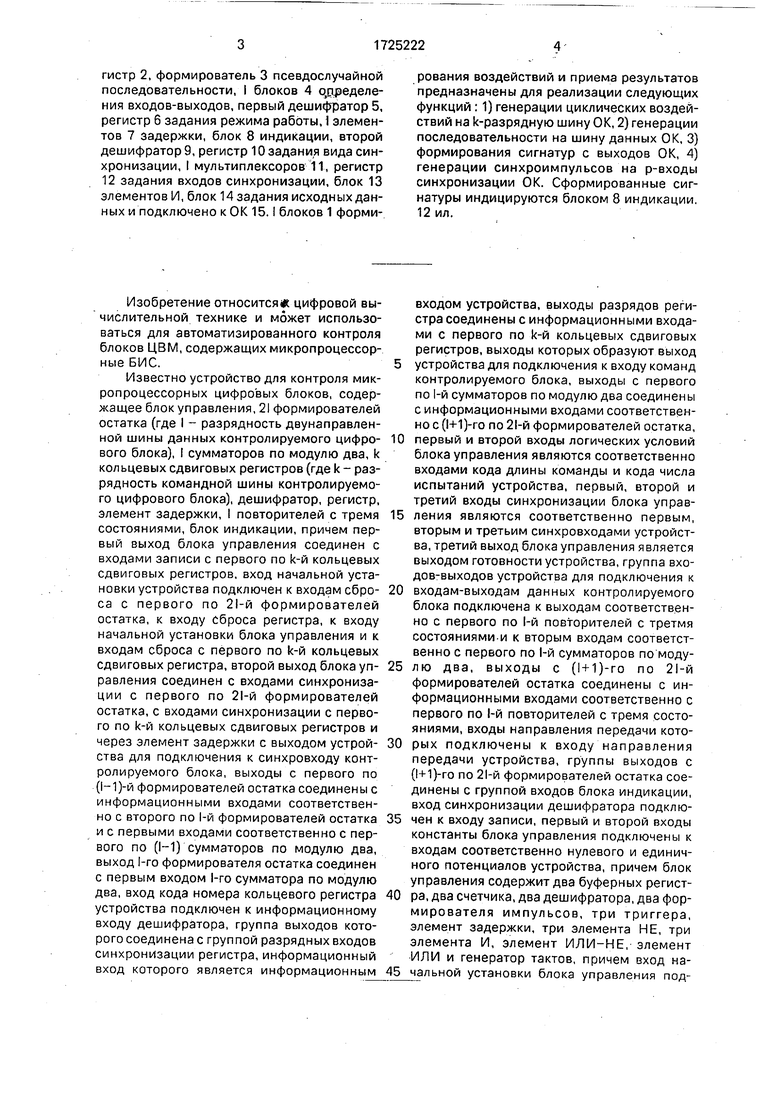

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - .блок-схема блока формирования воздействий и приема результатов; на фиг.З - блок- схема входного регистра; на фиг.4 - блок-схема формирователя псевдослучайной последовательности; на фиг.5 - блок- схема блока определения входов-выходов; на фиг.6 - блок-схема регистра задания вида синхронизации; на фиг.7 - блок-схема блока элементов И; на фиг.8-12 - временные диаграммы работы устройства для стохастического контроля микропроцессорных цифровых блоков.

Предлагаемое устройство содержит I блоков 1 формирования воздействий и

приема результатов, входной регистр 2, формирователь 3 псевдослучайной последовательности, I блоков 4 определения входов-выходов, первый дешифратор 5, регистр 6 задания режима работы, I элемен0 тов 7 задержки, блок 8 индикации, второй дешифратор 9, регистр 10 задания вида синхронизации, I мультиплексоров 11, регистр 12 задания входов синхронизации, блок 13 элементов И, блок 14 задания исходных дан5 ных и подключено к ОК 15 (фйг.1).

Блок 1 формирования воздействий и приема результатов (фиг.2) содержит сумматоры 16-18 по модулю два, элементы 2 И-Н Е 19 и 20, повторители 21-23 с тремя состоя0 ниями, элемент НЕ 24, регистр 25 сдвига.

Входной регистр 2 содержит I триггеров 26 (фиг.З).

Формирователь 3 псевдослучайной последовательности (фиг.4) содержит сумма5 торы 27 и 28 по модулю два, регистр 29 сдвига.

Блок 4 определения входов-выходов (фиг.5) содержит повторитель 30 с тремя состояниями, сумматор 31 по модулю два, эле0 мент НЕ 32, триггер 33, резистор 34.

Регистр 10 задания вида синхронизации (фиг.6) содержит t (где t I flog2 s, s - число входов синхронизации в группе входов синхронизации устройства) триггеров

5 35.

Блок 13 элементов И содержит I элементов 2И 36 (фиг.7).

Информационный вход первого дешифратора 5 соединен с первым выходом кода

0 адреса блока 14 задания исходных данных, выход строба первого адреса которого соединен со стробирующим входом первого дешифратора 5, группа выходов которого соединена с группой разрядных входов син5 хронизации входного регистра 2, информационный вход которого соединен с выходом информации блока 14 задания исходных данных, выход начальной установки которого соединен с входами начальной установки

0 входного регистра 2,1 блоков4 определения входов-выходов, I блоков 1 формирования воздействий и приема результатов, формирователя 3 псевдослучайной последовательности и регистра 10 задания вида

5 синхронизации, разрядные выходы входного регистра 2 соединены с первыми информационными входами соответствующих блоков 1 формирования воздействий и приема результатов, с группой информацион- ных входов регистра 12 задания входов

синхронизации, с группой информационных входов регистра 6 задания режима работы, вход записи которого соединен с первым выходом строба записи блока 14 задания исходных данных, разрядные выходы регистра 6 задания режима работы соединены с входами задания режима работы соответствующих блоков 1 формирования воздействий и приема результатов, первый вход синхронизации устройства соединен с входом синхронизации формирователя 3 псевдослучайной последовательности, выход каждого блока 1 формирования воздействий и приема результатов соединен с установочным входом соответствующего блока 4 определения входов-выходов, вход-выход каждого блока 4 определения входов-выходов соединен с вторым информационным входом соответствующего блока 1 формирования воздействий и приема результатов и является соответствующим входом-выходом устройства для подключения к соответствующим входам-выходам О К 15, информационные входы I блоков 4 определения входов-выходов подключены к шине константы нуля устройства, группы выходов блоков 1 формирования воздействий и приема результатов соединены с группой входов блока 8 индикации, выход формирователя 3 псевдослучайной последовательности соединен с входами псевдослучайной последовательности блоков 1 формирования воздействий и приема результатов, установочные входы входного регистра 2, формирователя 3 псевдослучайной последовательности и регистра 10 задания вида синхронизации подключены к шине константы единицы устройства, информационный вход второго дешифратора 9 соединен с вторым выходом кода адреса блока 14 задания исходных данных, выход строба второго адреса которого соединен со стро- бирующим входом второго дешифратора 9, группа выходов которого соединена с группой входов синхронизации регистра 10 задания вида синхронизации, группа информационных входов которого соединена с выходом кода вида синхронизации блока 14 задания исходных данных, второй и- третий выходы строба записи которого соединены со стробирующими входами соответственно регистра 12 задания входов синхронизации и блока 13 элементов И, группа информационных входов которого соединена с выходами регистра 12 задания входов синхронизации, выходы блока 13 элементов И соединены с входами строба записи соответствующих блоков 1 формирования воздействий и приема результатов, выход каждого мультиплексора 11 соединен

с входом синхронизации соответствующего блока 1 формирования воздействий и приема результатов и через соответствующий элемент 7 задержки с входом синхронизации соответствующего блока 4 определения входов-выходов, группа входов синхронизации устройства соединена с группами информационных входов I мультиплексоров 11, адресные входы которых соединены с

0 соответствующими группами выходов регистра 10 задания вида синхронизации, причем первый информационный вход блока 1 формирования воздействий и приема результатов соединен с первым входом повто5 рителя 22 с тремя состояниями, вход задания режима работы блока 1 формирования воздействий и приема результатов соединен с вторым входом повторителя 21 с тремя состояниями, с первым входом эле0 мента 2И-НЕ 19 и с первым входом элемента 2И-НЕ 20, выход которого соединен с вторым входом повторителя 23 с тремя состояниями, выход элемента 2И-НЕ 19 соединен с вторым входом повторителя 22 с

5 тремя состояниями, вход строба записи блока 1 формирования воздействий и приема результатов соединен с вторым входом элемента 2И-НЕ 19 и с входом элемента НЕ 24, выход которого соединен с вторым входом

0 элемента 2И-НЕ 20, вход синхронизации блока 1 формирования воздействий и приема результатов соединен с входом синхронизации С регистра 25 сдвига, выходы повторителей 21-23 с тремя состояниями

5 объединены и соединены с входом последовательного занесения D+ при сдвиге вправо регистра 25 сдвига, четвертый выход которого соединен с первым входом сумматора 1.8 по модулю два, выход которого соединен

0 с первым входом сумматора 17 по модулю два, выход которого соединен с первым входом повторителя 21 с тремя состояниями, девятый выход регистра 25 сдвига соединен с вторым входом сумматора 18 по модулю

5 два, десятый выход регистра 25 сдвига соединен с выходом блока 1 формирования воздействий и приема результатов, с первым входом повторителей 23 с тремя состояниями, группа объединенных выходов регистра

0 25 сдвига является группой выходов блока 1 формирования воздействий и приема результатов и соединена с группой входов блока 8 индикации, второй информационный вход блока 1 формирования воздейст5 вий и приема результатов соединен с вторым входом сумматора 16 по модулю два, вход начальной установки блока 1 формирования воздействий и приема результатов соединен с входом установки в О R регистра 25 сдвига, вход псевдослучайной

последовательности блока 1 формирования воздействий и приема результатов соединен с первым входом сумматора 16 по модулю два, выход которого соединен с вторым входом сумматора 17 по модулю два, при- чем группа разрядных входов синхронизации входного регистра 2 поразрядно соединена с группой входов синхронизации С триггеров 26, информационный вход входного регистра 2 соединен с информацией- ным входом D каждого триггера 26, вход начальной установки входного регистра 2 соединён с входом установки в О R каждого триггера 26, установочный вход входного регистра 2 соединен с входом установки в 1 S каждого триггера 26, выходы триггеров 26 являются разрядными выходами входного регистра 2, причем установочный вход формирователя 3 псевдослучайной последовательности соединен с вторым входом сумматора 27 по модулю два, выход которого соединен с входом последовательного занесения D+ при сдвиге вправо регистра 29 сдвига, четвертый разряд которого соединен с первым входом сумматора 28 по модулю два, выход которого соединен с первым входом сумматора 27 по модулю два, вход синхронизации формирователя 3 псевдослучайной последовательности соединен с входом синхронизации С регистра 29 сдвига, вход начальной установки формирователя 3 псевдослучайной последовательности соединен с входом установки в О R регистра 29 сдвига, старший разряд которого соединен с вторым входом сумматора 28 по модулю два и является выходом формирователя 3 псевдослучайной последовательности.

В качестве формирователя 3 псевдослучайной последовательности используется известное устройство на основе генератора m-последовательности, выполняющее деление последовательности импульсов на полином вида: g (х) х9 + х4 + 1. Количество разрядов регистра 29 сдвига формиро- вателя 3 псевдослучайной последовательности определяет достоверность сигнатурного анализа и при необходимости может быть увеличено с соответствующими изменениями обратной связи для сохранения выполнения условий генерации последовательности максимальной длины. Регистр 29 сдвига представляет собой известное устройство.

Вход синхронизации блока 4 определе- ния входов-выходов соединен с входом синхронизации С триггера 33, установочный вход блока 4 определения входов-выходов соединен с первым входом повторителя 30 с тремя состояниями, выход которого соединен с первым выводом резистора 34 и с вторым входом сумматора 31 по модулю два, первый вход которого соединен с вторым выводом резистора 34 и является входом-выходом блока 4 определения входов-вы ходов, вход начальной установки блока 4 определения входов-выходов соединен с входом установки в О R триггера 33, выход которого соединен с вторым входом повторителя 30 стремя состояниями, выход сумматора 31 по модулю два соединен с входом элемента НЕ 32, выход которого соединен с входом установки в 1 S триггера 33, информационный вход D которого соединен с информационным входом блока 4 определения входов-выходов.

Регистр 25 сдвига представляет собой восьмиразрядный регистр сдвига, например интегральная микросхема К155ИР13. Причем управляющий вход U1 и вход последовательного занесения при сдвиге влево D - соединен с шиной нулевого потенциала, которая представляет собой провод, соединенный с нулевым полюсом источника питания. Управляющий вход U2 соединен с шиной единичного потенциала, которая представляет собой вывод резистора, другой вывод которого соединен с положительным полюсом источника питания. Для увеличения длины блока формирования воздействий и приема результатов восьмиразрядные регистры сдвига следует соединить последовательно: выход старшего разряда первого регистра сдвига следует соединить с входом последовательного занесения при сдвиге вправо D+ второго регистра сдвига, входы U1, U2, С и D-второго регистра сдвига следует соединить с аналогичными входами первого регистра сдвига.

Регистр 6 Задания режима работы представляет собой восьмиразрядный регистр сдвига, например интегральная микросхема К155ИР13. Причем вход последовательного занесения D+ при сдвиге вправо и D - при сдвиге влево соединены с шиной нулевого потенциала, которая представляет собой провод, соединенный с нулевым полюсом источника питания. Управляющие входы U1, U2 и вход установки в О R соединены с шиной единичного потенциала, которая представляет собой вывод резистора, другой вывод последнего соединен с положительным полюсом источника питания. Для увеличения длины регистра задания режима работы восьмиразрядные регистры сдвига следует соединить параллельно: входы U1, U2, R, D+ и D - второго восьмиразрядного регистра сдвига следует соединить с аналогичными входами первого восьмиразрядного регистра сдвига.

Триггеры 26, 33 и 35 представляют собой D-триггеры, например интегральная микросхема К155ТМ2.

В качестве сумматоров 16-18, 27, 28 и 31 по модулю два могут быть использованы двувходовые элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, например интегральная микросхема К155ЛП5.

В качестве элементов НЕ 24 и 32 могут быть использованы, например, элементы НЕ, входящие в состав интегральной микросхемы К155ЛН1.

В качестве первого дешифратора 5 и второго дешифратора 9 могут быть использованы, например, дешифраторы на четыре разряда К155ЙДЗ.

В качестве повторителей 21-23 и 30 с тремя состояниями может быть использован, например, повторитель с тремя состояниями, входящий в состав интегральной микросхемы К155ЛП8.

В качестве элементов 2И-НЕ 19 и 20 может быть использован, например, логический элемент, входящий в состав интегральной микросхемы К155ЛАЗ.

Элементы 7 задержки синхроимпульсов представляют собой известное устройство, осуществляющее задержку синхроимпульсов, поданных на их вход. Величина времени задержки элемента 7 задержки синхроимпульсов определяется времененм, необходимым для прохождения информации через блок 1 формирования воздействий и приема результатов и блок 4 определения входов-выходов на командную шину и шину данных ОК 15. Элементы задержки могутбыть построены, например, по схеме последовательного включения элементов НЕ. Элементы 7 задержки синхроимпульсов должны состоять из четного количества элементов НЕ.

Блок 8 индикации представляет собой известное устройство.

Группа информационных входов регистра 10 задания вида синхронизации поразрядно соединена с каждой группой информационных входов D триггеров 35, i-й (1 1-1) вход группы входов синхронизации регистра 10 задания вида синхронизации соединен с входом синхронизации С каждого триггера 35, вход начальной установки регистра 10 задания вида синхронизации соединен с входом установки в нуль R каждого триггера 35, установочный вход регистра 10 задания вида синхронизации соединен с входом установки в 1 S каждого триггера 35, группы выходов триггеров 35 являются группами выходов регистра 10 задания вида синхронизации.

Мультиплексор 11 представляет собой коммутатор S-входов на один выход, например интегральная микросхема К155КП7. Причем стробирующий вход R соединен с шиной нулевого потенциала, которая представляет собой провод, соединенный с нулевым полюсом источника питания.

Регистр 12 задания входов синхронизации представляет собой восьмиразрядный

0 регистр сдвига, например интегральная микросхема К155ИР13. Причем вход последовательного занесения D+ при двиге вправо и D- при сдвиге влево соединены с шиной нулевого потенциала, которая пред5 ставляет собой провод, соединенный с нулевым полюсом источника питания. Управляющие входы U1, U2 и вход установки в нуль R соединены с шиной единичного потенциала, которая пред0 ставляет собой вывод резистора, другой вывод которого соединен с положительным полюсом источника питания. Для увеличения длины регистра задания входов синхронизации восьмиразрядные ре5 гистры сдвига следует соединить параллельно: входы U1, U2, R, D+ и D- второго восьмиразрядного регистра сдвига следует соединить с аналогичными входами первого восьмиразрядного

0 регистра сдвига.

Стробирующий вход блока 13 элементов И соединен с объединенными первыми входами элементов 2И 36, выходы которых являются выходами блока 13 элементов И,

5 группа информационных входов блока 13 элементов И порязрядно соединена с вторыми входами элементов 2И 36. В качестве элементов 2И 36 могут быть использованы, например, элементы 2И, входящие в

0 состав интегральной микросхемы К155ЛИ1.

Каждый i-й блок 1 формирования воздействий и приема результатов используется в четырех режимах: в качестве

5 генератора тестовых воздействий, если i-й вывод ОК 15 является входом; в качестве формирователя сигнатуры, если i-й вывод ОК 15 является выходом; одновременно и как генератор m-последовательности и как

0 формирователь сигнатуры, если i-й вывод ОК 15 является линией двунаправленной шины данных, причем в те такты процесса контроля, когда шина данных включена в режим приема информаии блок 1 формиро5 вания воздействий и приема результатов используется в качестве генератора тестовых воздействий, когда же шина данных включена в режим выдачи информации с ОК 15, блок 1 формирования воздействий и при- ема результатов используется как формирователь сигнатуры; в качестве генератора синхроимпульсов, если i-й вывод ОК 15 является входом синхронизации.

Входной регистр 2 служит для записи новой тестовой команды, которая входит в состав тестовой программы.

Формирователь 3 псевдослучайной последовательности используется только как генератор m-последовательности для обеспечения функционирования блоков 1 формирования воздействий и приема результатов в качестве генераторов т-последовательнр- сти.

Каждый i-й блок 4 определения входов- выходов используется для определения на- правления передачи информации на двунаправленной шине данных ОК 15.

Первый дешифратор 5 и второй дешифратор 9 используются для организации доступа к любому i-му блоку 1 формирования воздействий и приема результатов.

Регистр 6 задания режима работы используется для установки каждого 1-го блока 1 формирования воздействий и приема результатов в требуемый режим работы.

Регистр 10 задания вида синхронизации используется для записи нового кода вида синхронизации для каждого канала.

Мультиплексор 11 используется для коммутации определенного входа синхронизации группы входов синхронизации устройства на вход синхронизации блока 1 формирования воздействий и приема результатов и вход элемента 7 задержки.

Регистр 12 заданий входов синхронизации используется для задания входов синхронизации ОК.

Блок 13 элементов И используется для разрешения записи тестовых команд в процессе контроля ОК только в те блоки 1 формирования воздействий и приема результатов, которые работают на выводы ОК, являющиеся входами командной шины ОК.

Устройство работает следующим образом.

При включении питания состояние триггеров, регистров сдвига может быть произвольным.

По сигналу, который представляет собой импульс с низким активным уровнем и поступает с выхода начальной установки блока 14 задания исходных данных на входы начальной установки входного регистра 2, каждого блока 1 формирования воздействий и приема результатов, каждого блока 4 определения входов-выходов, формирователя 3 псевдослучайной последовательности, регистра 10 задания вида синхронизации происходит сброс триггеров

26 входного регистра 2, каждого регистра 25 сдвига каждого блока 1 формирования воздействий и приема результатов, каждого триггера 33 каждого блока определения

входа-выхода, регистра 29 сдвига формирователя 3 псевдослучайной последовательности, каждого триггера 35 регистра 10 задания вида синхронизации. Значения логических передаются с выходов регистра

0 10 задания вида синхронизации на адресные входы каждого мультиплексора 11, разрешая тем самым передачу информации через каждый мультиплексор 11с первого входа информационной группы входов

5 мультиплексора 11 на его выходы.

На фиг.8 представлена последовательность информационных и стробирующих сигналов в режиме установки вида обратной связи для начальной загрузки блока 1 фор0 мирования воздействий и приема результатов. Информация с первого выхода кода адреса блока 14 задания исходных данных поступает на информационный вход первого дешифратора 5. При появлении на выходе

5 строба первого адреса блока 14 задания исходных данных импульса с низким активным уровнем, который поступает на стробирующий вход первого дешифратора 5, на i-м выходе первого дешифратора 5,

0 который соответствует коду адреса i-ro блока 1 формирования воздействий и приема результатов, появляется импульс с низким активным уровнем. Одновременно с передачей информаии по первому выходу кода

5 адреса блока 14 задания исходных данных устанавливается информация на информационном выходе блока 14 задания исходных данных. По перепаду импульса с низким активным уровнем с 1-го выхода первого де0 шифратора 5 из состояния логичесокого О в состояние логической 1 происходит запись информации с информационного выхода блока 14 задания исходных данных в i-й триггер 26 входного регистра 2.

5 После загрузки I триггеров 26 входного регистра 2 на первом выходе строба записи и на втором выходе строба записи блока 14 задания исходных данных появляются импульсы с высоким активным уровнем, кото0 рые поступают соответственно на вход записи регистра 6 задания режима работы и на стробирующий вход регистра 12 задания входов синхронизации и производится запись информации с выходов триггеров 26

5 входного регистра 2 в регистр 6 задания режима работы и в регистр 12 задания входов синхронизации. Для начальной загрузки каждого блока 1 формирования воздействий и приема результатов в регистр 6 задания режима работы и регистр 12

задания входов синхронизации заносится значение логической 1. При подаче значения логической 1 с i-ro выхода регистра б задания режима работы на вход задания режима работы i-ro блока 1 формирования воздействий и приема результатов, повторитель 21 с тремя состояниями устанавливается в третье состояние. Значение логической 1 подается с 1-го выхода регистра 12 задания входов синхронизации на i-й информационный вход блока 13 элементов И, который соединен с вторым входом i-ro элемента 2И 36, разрешая тем самым прохождение сигналов с третьего выхода строба записи через i-й элемент 2И 36 на вход строба записи i-ro блока 1 формирования воздействий и приема результатов. При наличии значения логического О на третьем выходе строба записи блока 14 задания исходных данных, оно передается через i-й элемент 2И 26 блока 13 элементов И на вход строба записи i-ro блока формирования воздействий и приема результатов, который соединен с вторым входом элемента 2И-НЕ 19, и устанавливает на выходе последнего значение логической 1, которое подается на второй вход повторителя 22 с тремя состояниями и устанавливает его в третье состояние. На выходе элемента 2И-НЕ 20 находится значение логического О, которое подается на второй вход повторителя 23 стремя состояниями. Этим обеспечивается связь старшего разряда регистра 25 сдвига с его входом последовательного занесения при сдвиге вправо D+. Устройство готово к начальной загрузке блоков 1 формирования воздействий и приема результатов.

Далее начинается процесс начальной загрузки блоков 1 формирования воздействий и приема результатов (фиг.9). Информация с первого выхода кода адреса блока 14 задания исходных данных поступает на информационный вход первого дешифратора 5. При появлении на выходе строба первого адреса блока 14 задания исходных данных импульса с низким активным уровнем, который поступает на стробирующий вход первого дешифратора 5, на i-м выходе первого дешифратора 5, который соответствует коду адреса i-ro блока 1 формирования воздействий и приема результатов, появляется импульс с низким активным уровнем. Одновременно с передачей информации по первому выходу кода адреса блока 14 задания исходных данных устанавливается информация на информационном выходе блока 14 задания исходных данных, которая может принимать значение логического О или логической единицы. По перепаду импульса с низким активным уровнем с i-ro

выхода первого дешифратора 5 из состояния логического О в состояние логической Г происходит запись информации с информационного выхода блока 14 задания 5 исходных данных в i-й триггер 26 входного регистра 2. После загрузки I триггеров 26 входного регистра 2 информация с каждого i-ro выхода входного регистра 2 появляется на первом информационном входе каждого

0 1-го блока 1 формирования воздействий и приема результатов и подается на первый вход повторителя 22 с тремя состояниями. Затем на третьем выходе строба записи блока 14 задания исходных данных появляется

5 импульс с высоким активным уровнем, при подаче которого через блок 13 элементов И на вход строба записи блока 1 формирования воздействий и приема результатов на втором входе повторителя 23 с тремя состо0 яниями устанавливается значение логической 1, которое переводит выход элемента 23 с тремя состояниями в третье состояние, чем обеспечивается обрыв связи между старшим разрядом регистра 25 сдвига и его

5 входом последовательного занесения при сдвиге вправо D+. Кроме этого, импульс с высоким активным уровнем со входа строба записи блока 1 формирования воздействий и приема результатов устанавливает на вы0 ходе элемента 2И-НЕ 19 значение логического О, так как на первом входе элемента 2И-НЕ 19 находится значение логической 1. Значение логического О с выхода элемента 2И-НЕ 19 подается на второй вход

5 повторителя 22 с тремя состояниями, что приводит к передаче информации с первого входа повторителя 22 с тремя состояниями на вход последовательного занесения при сдвиге вправо D+ регистра 25 сдвига. Затем

0 на первом входе группы входов синхронизации устройства, который соединен с первым входом группы информационных входов мультиплексора 11, появляется импульс с высоким активным уровнем, который пере5 дается через мультиплексор 11 на вход синхронизации блока 1 формирования воздействий и приема результатов, последний соединен с входом синхронизации С регистра 25 блока 1 формирования воздей0 ствий и приема результатов. В результате этого производится запись информации в первый разряд каждого регистра 25 каждого блока 1 формирования воздействий и приема результатов, При появлении перепада

5 из состояния логической 1 в состояние логического О на третьем выходе строба записи блока 14 задания исходных данных выход повторителя 22 с тремя состояниями вновь устанавливается в третье состояние и происходит восстановление связи между

выходом старшего разряда регистра 25 сдвига и его входом последовательного занесения при сдвиге вправо D+ через повто- ритель 23 с тремя состояниями. Аналогичным образом производится запись информации в k разряды регистра 25 сдвига каждого блока 1 формирования воздействий и приема результатов, где k 1Кмакс ОВмакс - максимальная длина тестовой команды), кроме блоков 1 формирования воздействий и приема результатов, работающих на выводы ОК, являющиеся входами синхронизации ОК. Одновременно в регистры 25 сдвига блоков 1 формирования воздействий и приема результатов, работающих на выводы ОК, являющиеся входами синхронизации ОК, аналогичным образом записывается последовательность логических О и 1, отображающая вид синхроимпульсов.

Одновременно с начальной загруз-г кой регистров 25 сдвига блоков 1 формирования воздействий и приема результатов производится загрузка регистра 29 сдвига формирователя 3 псевдослучайной последовательности. Эргодические свойства формирователя 3 псевдослучайной последовательности обеспечиваются соединением его установочного входа, который соединен с вторым входом сумматора 27 по модулю два, с шиной Const 1, которая представляет собой вывод резистора, другой вывод которого соединен с положительным полюсом источника питания. Таким образом, гарантируется ненулевое состояние регистра 29 сдвига уже после первого тактового импульса, который подается с первого входа группы входов синхронизации устройства, который соединен с входом синхронизации формирователя 3 псевдослучайной последовательности, последний соединен с входом синхронизации С регистра 29 сдвига формирователя 3 псевдослучайной последовательности.

Затем производится задание входов синхронизации ОК(фиг.8). Если i-й вывод ОК является одним из входов синхронизации ОК, то в i-й триггер 26 входного регистра 2 записывается значение логического О. В остальных случаях в i-й триггер 26 входного регистра 2 записывается значение логической 1. После загрузки I триггеров 26 входного регистра 2 на втором выходе строба записи блока 14 задания исходных данных появляется импульс с высоким активным уровнем, который поступает на стробирую- щий вход регистра 12 задания входов синхронизации и производит запись информации с выходов триггеров 26 входного регистра 2 в регистр 12 задания входов синхронизации.

Для синхронизации ОК по разным входам синхронизации часто необходимы последовательности .синхроимпульсов с различными временными характеристиками (например, синхронизация последовательностями с различными частотами следования импульсов, синхронизация от

0 ОК и др.). Эти последовательности синхроимпульсов подаются на различные входы группы входов синхронизации устройства, которая соединена с группами информационных входов мультиплексоров 11. Для пе5 редачи импульсов с определенного входа группы информационных входов мультиплексора 11 на его выход на адресные входы мультиплексора 11 подается код вида синхронизации с соответствующей группы выхо0 дов регистра 10 записи вида синхронизации. Для каждого входа синхронизации ОК код вида синхронизации записывается в регистр 10 записи вида синхронизации следующим образом

5 (фиг.10). Информация с второго выхода кода адреса блока 14 задания исходных данных поступает на информационный вход второго дешифратора 9. При появлении на выходе строба второго адреса блока 14 задания ис0 ходных данных импульса с низким активным уровнем, который поступает на стробирующий вход второго дешифратора 9, на 1-м выходе второго дешифратора 9, который соответствует коду адреса i-ro бло5 ка 1 формирования воздействий и приема результатов, появлется импульс с низким активным уровнем, который поступает на входы синхронизации С каждого 1-го триггера 35. Одновременно с передачей информа0 ции по второму выходу кода адреса блока 14 задания исходных данных на выходе кода вида синхронизации блока 14 задания исходных данных устанавливается код вида синхронизации 1-го вывода ОК, который пе5 редается на группу информационных входов регистра 10 задания вида синхронизации, которая поразрядно соединена с информационными входами D i-x триггеров 35. По перепаду импульса с низ0 ким активным уровнем с i-ro выхода второго дешифратора 9 из состояния логического О в состояние логической 1 происходит запись информации с выхода кода вида синхронизации блока 14 задания исходныхдан5 ных в группу i-x триггеров 35 регистра 10 задания вида синхронизации. Код вида синхронизации передается с i-й группы выходов регистра 10 задания вида синхронизации на адресные входы i-ro мультиплексора 11, разрешая тем самым передачу синхроимпульсов через i-й мультиплексор 11 с входа, соответствующего коду вида синхронизации, группы информационных входов 1-го мультиплексора 11 на его выход. Аналогичным образом производится запись в регистр 10 записи вида синхронизации кодов вида синхронизации тех каналов, по которым считывается динамическая сигнатура.

В зависимости от функционального назначения выводов ОК i-й блок 1 формирования воздействий и приема результатов устанавливается в следующий режим работы (фиг.8).

Если i-й вывод ОК является одним из входов командной шины или одним из входов синхронизации ОК, в i-й разряд регистра 6 задания режима работы заносится значение логической 1.

Если i-й вывод ОК является одним из входов-выходов двунаправленной шины данных ОК, в i-й разряд регистра 6 задания режима работы заносится значение логического О, которое подается на вход задания режима работы блока 1 формирования воздействий и приема результатов, который соединен с первым входом элемента 2И-НЕ 19. В результате этого на выходе элемента 2И-НЕ 19 появляется значение логической 1, которое подается на второй вход повторителя 22 стремя состояниями и устанавливает его выход в третье состояние. Значение логического О с входа задания режима работы блока 1 формирования воздействий и приема результатов также подается на первый вход элемента 2И-НЕ 20, на выходе которого появляется значение логической 1, которое подается на второй вход повторителя 23 с тремя состояниями, устанавливая его выход в третье состояние. Кроме того, значение логического О с входа задания режима работы блока 1 формирования воздействий и приема результатов подается на второй вход повторителя 21с тремя состояниями. В результате этого информация с четвертого и девятого выходов регистра 25 сдвига подается на входы сумматора 18 по модулю два, с выхода которого подается через сумматор 17 по модулю два и через повторитель 21 с тремя состояниями на вход последовательного занесения при сдвиге вправо D+ регистра 25 сдвига. Этим обеспечивается установление i-ro блока 1 формирования воздействий и приема результатов в режим генератора гл-последова- тельности - формирователя сигнатуры.

После установления режима работы блоков 1 формирования воздействий и приема результатов (адаптации устройства к

ОК), начинается процесс подачи тестовых команд на ОК (фиг.11).

Информация с первого выхода кода адреса блока 14 задания исходных данных поступает на информационный вход первого дешифратора 5. При появлении на выходе строба первого адреса блока 14 задания исходных данных импульса с низким активным уровнем, который поступает на

0 стробирующий вход первого дешифратора 5, на j-м выходе первого дешифратора 5 (j 1, 2k), который соответствует коду адреса j-ro блока 1 формирования воздействий и приема результатов, появляется импульс с

5 низким активным уровнем. Одновременно с передачей информации с первого выхода кода адреса блока 14 задания исходных данных на информационный вход первого дешифратора 5 устанавливается информация

0 на информационном выходе блока 14 задания исходных данных, которая может принимать значение логического О или логической 1. По перепаду импульса с низким активным уровнем с j-ro выхода первого

5 дешифратора 5 из состояния логического О в состояние логической 1 происходит запись информации с информационного выхода блока 14 задания исходных данных в j-й триггер 26 входного регистра 2. После

0 загрузки каждого из к-1 триггеров 26 входного регистра 2 информация с каждого j-ro выхода входного регистра 2 появляется на первом информационном входе каждого j- го блока 1 формирования воздействий и

5 приема результатов и подается на первый вход повторителя 22 с тремя состояниями. Затем на первом входе группы входов синхронизации устройства появляется последовательность из k (k разрядности

0 регистра 25 сдвига) импульсов, которая подается на вход синхронизации каждого блока 1 формирования воздействий и приема результатов, который соединен с входом синхронизации С регистра 25 сдвига. Так

5 как время формирования одного бита на первом выходе кода адреса блока 14 задания исходных данных и одного бита на информационном выходе блока 14 задания исходных данных больше времени геиера0 ции последовательности из k импульсов, которые подаются с первого входа группы входов синхронизации устройства через мультиплексоры 11 на входы синхронизации С регистров 25 сдвига каждого.из 1

5 блоков формирования воздействий и приема результатов, то до появления следующего бита на первом выходе кода адреса блока 14 задания исходных данных и на информационном выходе блока 14 задания исходных данных тестовая программа, находящаяся в регистрах 25 сдвига каждого из k блоков 1 формирования воздействий и приема результатов, подается на ОК 15 через блоки 4 определения входов-выходов и возвращается в исходное состояние в регистрах 25 сдвига каждого из k блоков. 1 формирования воздействий и приема результатов. При этом на двунаправленную шину данных с каждого из п блоков 1 формирования воздействий и приема результатов через п блоков 4 определения входов-выходов подается псевдослучайная m-последовательность. В течение времени формирования k-1 бит на информационном выходе блока 14 задания исходных данных и на первом выходе кода адреса блока 14 задания исходных данных происходит многократная (k-1 раз) подача одних и тех же тестовых команд (мультипликация) с различными (псевдослучайными) наборами данных на ОК 15 через I блоков 4 определения входов-выходов. Ненулевое состояние каждого из п блоков 1 формирования воздействий и приема результатов обеспечивается начальной загрузкой от формирователя 3 псевдослучайной последовательности. После установления на информационном выходе блока 14 задания исходных данных k-ro логического значения разряда команды, которое устанавливается одновременно с информацией на первом выходе кода адреса блока 14 задания исходных данных,;на третьем выходе строба записи блока 14 задания исходных данных появляется импульс с высоким активным уровнем, который устанавливает выход повторителя 23 с тремя состояниями в третье состояние, а на втором входе повторителя

22с тремя состояниями устанавливает значение логического О в каждом из k блоков 1 формирования воздействий и приема результатов. При появлении на первом входе группы входов синхронизации устройства импульса с высоким активным уровнем происходит запись новой, сформированной в входном регистре 2, k- разрядной тестовой команды в каждый из k блоков 1 формирования воздействий .и приема результатов. При перепаде импульса на третьем выходе строба записи блока 14 задания исходных данных из состояния логической 1 в состояние логического О выход повторителя 22 с тремя состояниями устанавливается в третье состояние и восстанавливается связь между старшим разрядом регистра 25 сдвига и его входом последовательного занесения при сдвиге вправо D+ через повторитель

23с тремя состояниями каждого из k блоков 1 формирования воздействий и приема

результатов. Завершение записи новой тестовой команды в каждый из k блоков 1 фор- мирования воздействий и приема результатов, процесс формирования следующих тестовых команд и подача тестовых программ на ОК 15 продолжается в течение заданного времени.

Передача информации с выходов I блоков 1 формирования воздействий и приема

0 результатов на ОК 15 через I блоков 4 определения входов-выходов происходит следующим образом.

После сигнала с низким активным уровнем, который поступает с выхода на5 чальной установки блока 14 задания исходных данных на вход начальной установки каждого 1-го блока 4 определения входов-выходов, который подается на вход установки в О R триггера 33, на

0 выходе триггера 33 каждого 1-го блока 4 определения входов-выходов находится состояние логичесокого О, которое подается на второй вход повторителя 30 с тремя состояниями. Информация с выхода

5 каждого i-ro блока 1 формирования воздействий и приема результатов подается на установочный вход i-го блока 4 определения входов-выходов и через повторитель 30 с тремя состояниями и резистор 34,

0 второй выход которого соединен с выходом блока 4 определения входов-выходов, . подается на i-й вход ОК 15. Эта информация поступает в ОК при появлении на основном входе синхронизации ОК 15

5 импульса с выхода соответствующего блока 4 определения входов-выходов. Причем синхроимпульсы на основном входе синхронизации ОК появляются с задержкой, определяемой временем прохождения ин0 формации с выхода i-ro блока 1 формирования воздействий и приема результатов на i-й вход ОК 15 (фиг.12). При этом на выходе триггера 33 каждого i-ro блока 4 определения входов-выходов остается

5 значение логического О, так как на входы сумматора 31 по модулю два поступают одинаковые логические значения, в результате чего на выходе сумматора 31 по модулю два находится значение логическо0 го О, которое через элемент НЕ 32 подается на вход установки в 1 S триггера 33 в виде значения логической 1. Затем на вход синхронизации i-ro блока 4 определения входов-выходов, который соединен с

5 входом синхронизации С триггера 33, с выхода i-ro элемента 7 задержки синхроимпульсов подается импульс с высоким активным уровнем (фиг.12), по перепаду которого из состояния логического О в состояние логической 1, значение логического

О с информационного входа D триггера 33 передается на выход триггера 33, тем самым подтверждая ранее установленное значение логического О на выходе триггера 33.

При помощи информации из ОК 15 в п блоков 1 формирования воздействий и приема результатов через п блоков 4 определения входов-выходов блок 4 определения входов-выходов работает следующим образом.

В первом случае логическое значение бита на выходе n-го блока 1 формирования воздействий и приема результатов совпадает с логическим значением бита с n-го выхода ОК 15. Так как на втором входе повторителя 30 с тремя состояниями находится значение логического О, то логическое значение бита с выхода n-го блока 1 формирования воздействий и приема результатов подается на установочный вход n-го блока 4 определения входов-выходов через повторитель 30 с тремя состояниями и поступает на второй вход сумматора 31 по модулю два. С n-го выхода ОК 15 на первый вход сумматора 31 по модулю два поступает бит с таким же логическим значением, в результате чего на выходе сумматора 31 по модулю два находится значение логического О, которое через элемент НЕ 32 подается на вход установки в 1 S триггера 33 в виде значения логической 1. Логическое значение бита с n-го выхода ОК 15 подается на второй информационный вход n-го блока 1 формирования воздействий и приема результатов и через сумматор 16 по модулю два, через сумматор 17 по модулю два, через повторитель 21 с тремя состояниями, на втором входе которого находится состояниело- гичесокго О, записывается в регистр 25 сдвига n-го блока 1 формирования воздействий и приема результатов с появлением на входе синхронизации этого блока импульса с высоким активным уровнем (фиг. 12). Затем на вход синхронизации 1-го блока 4 определения входов-выходов, который соединен с входом синхронизации С триггера 33, с выхода 1-го элемента 7 задержки синхроимпульсов подается импульс с высоким активным уровнем, по перепаду которого из состояния логического О в состояние логической 1, значение логического О с информационного входа D триггера 33 передается на выход триггера 33, тем самым подтверждая ранее установленное значение логического О на выходе этого триггера.

Во втором случае логическое значение бита n-го блока 1 формирования воздействий и приема результатов не совпадает с

логическим значением бита, который появляется на n-м выходе ОК 15 при поступлении импульса на вход синхронизации ОК 15, т.е. возникает конфликтная ситуация. В этом случае при достижении током, протекающим через резистор 34, величины

Inop -

где Unop - минимальная разность потенциалов между входами сумматора 31 по модулю два, при котором его выход находится в состоянии логической

R - величина сопротивления резистора 34, которая должна удовлетворять условию:

20

R

(н.макс

где н.макс - максимальная величина тока нагрузки в случае отсутствия конфликтной ситуации,

изменяется уровень на выходе сумматора 31 по модулю два из значения логического О в значение логической 1. На входе установки в 1 S триггера 33 возникает перепад логичесокго уровня из 1 в О и триггер

33 устанавливается в единичное состояние, переводя тем самым выход повторителя 30 с тремя состояниями в третье состояние с высокоимпендансным выходом. Таким образом, конфликтная ситуация ликвидируется. В результате этого логическое значение бита с n-го выхода ОК 15 подается на второй информационный вход п-го блока 1 формирования воздействий и приема результатов и через сумматоры 16 и 17

по модулю два, через повторитель 21 с тремя состояниями, на втором входе которого находится состояние логического О, записывается в регистр 25 сдвига блока 1 формирования воздействий и приема результатов с появлением на входе синхронизации этого блока импульса с высоким активным уровнем (фиг. 12). После импульса, появляющегося на основном входе синхронизации ОК 15 на вход синхронизации

1-го блока 4 определения входов-выходов, который соединен с входом синхронизации С триггера 33, с выхода i-ro элемента 7 задержки синхроимпульсов подается импульс с высоким активным уровнем, по перепаду которого из состояния логического О в состояние логической 1, значение логического О с информационного входа D триггера 33 передается на выход этого триггера, т.е. устанавливает его в О.

Время задержки между импульсами, поступающим - на основной вход синхронизации ОК 15 и импульсами с выхода 1-го элемента задержки синхроимпульсов, поступающих на этот элемент задержки с первого входа группы входов синхронизации устройства, определяется быстродействием ОК 15 и временем записи информации в регистр 25 сдвига i-ro блока 1 формирования воздействий и приема результатов.

Импульсы с высоким активным уровнем с первого входа группы входов синхронизации устройства подаются одновременно на вход синхронизации блоков 1 формирования воздействий и приема результатов через мультиплексоры 11, на группу адресных входов которых подается код вида синхронизации, соответствующий передачи импульсов через мультиплексор 11с первого входа группы информационных входов мультиплексора 11 на его выход, и на вход синхронизации формирователя 3 псевдослучайной последовательности, с выхода которого псевдослучайная т-последова- тельность подается на вход псевдослучайной последовательности каждого блока 1 формирования воздействий и приема результатов, а записывается в каждый регистр 25 сдвига каждого n-го блока формирования воздействий и приема результатов через сумматоры 16 и 17 по модулю два и через повторитель 21 с тремя состояниями при появлении на входе синхронизации соответствующего п-го блока 1 формирования воздействий и приема результатов импульса с высоким активным уровнем, поступающим через соотвествующий мультиплексор 11с одного из входов группы входов синхронизации устройства. Этим обеспечивается ненулевое состояние каждого из п блоков 1 формирования воздействий и приема результатов в процессе работы устройства.

Вычисленные сигнатуры индицируются блоков 8 индикации и сравниваются с сигнатурами, полученными в результате проверки исправного цифрового блока или математического моделирования. Контролируемый цифровой блок считается исправным, если указанные сигнатуры совпадают.

Блок 14 задания исходных данных может быть реализован на основе любого устройства, работа которого обеспечивает требуемую последовательность информационных и стробирующих сигналов, например Электроника-60 с устройством параллельного обмена И2 15КС-180-032.

Таким образом, использование предлагаемого устройства позволяет эффективно

контролировать цифровые блоки, содержащие микропроцессоры и микропроцессорные БИС на их рабочей частоте с высокой достоверностью. При этом устраняется необходимость применения ручных операций коммутации и дополнительной аппаратуры формирования сигналов синхронизации ОК, так как в предлагаемом устройстве любой из каналов может использоваться для подачи

синхроимпульсов на ОК, причем временные характеристики последовательностей синхроимпульсов каждого из каналов синхронизации могут отличаться одна от другой. Кроме этого, предлагаемое устройство позволяет одновременно синхронизировать Считывание выходной информации с разных каналов ОК последовательностями импульсов с различными частотными характеристиками, т.е. считывать динамическую

сигнатуру по отдельным выходным каналам ОК.

Формула изобретения

Устройство для стохастического контроля микропроцессорных цифровых блоков, содержащее блок задания исходных данных, первый дешифратор, входной регистр, формирователь псевдослучайной последовательности, регистр задания режима работы, I блоков формирования воздействий и приема результатов (I п + k + р, где п - разрядность двунаправленной шины, k - разрядность командной шины и р - число

синхронизирующих входов объекта контроля), I блоков определения входов-выходов, блок индикации, два элемента задержки, причем информационный вход первого дешифратора соединен с первым выходом кода адреса блока задания исходных данных, выход строба первого адреса которого соединен со стробирующим входом первого де- шифратора, группа выходов которого соединена с группой разрядных входов синхронизации входного регистра, информационный вход которого соединен с выходом информации блока задания исходных данных, выход начальной установки которого соединен с входами начальной установки

входного регистра, I блоков формирования воздействий и приема результатов, I блоков определения входов-выходов и формирователя псевдослучайной последовательности, разрядные выходы входного

регистра соединены с первыми информационными входами соответствующих блоков формирования воздействий и приема результатов и с группой информационных входов регистра задания режима работы, вход записи которого соединен с первым

выходом строба записи блока задания исходных данных, разрядные выходы регистра задания режима работы соединены с входами задания режима работы соответствующих блоков формирования воздействий и приема результатов, вход синхронизации устройства соединен с входом синхронизации формирователя псевдослучайной последовательности, выход каждого блока формирования воздействий и приема ре- зультатов соединен с установочным входом соответствующего блока определения входов-выходов, вход-выход каждого блока определения входов-выходов соединен с вторым информационным входом соответ- ствующего блока формирования воздействий и приема результатов и является соответствующим входом-выходом устройства для подключения к соответствующим входам-выходам контролируемого объекта, информационные входы блоков определения входов-выходов подключены к шине константы нуля устройства, группы выходов блоков формирования воздействий и приема результатов соединены с группой вхо- дов блока индикации, выход формирователя псевдослучайной последовательности соединен с входами псевдослучайной последо- вательности I блоков формирования воздействий и приема результатов, устано- вочный входы формирователя псевдослучайной последовательности и входного регистра подключены к шине константы единицы устройства, отличающееся тем, что, с целью расширения функциональ- ных возможностей за счет считывания дина- мической сигнатуры и формирования воздействий, отличающихся по временным характеристикам, но отдельно выбранным каналам, оно содержит второй дешифратор, регистр задания вида синхронизации, регистр задания входов синхронизации, блок

элементов И, I мультиплексоров, I-2 элементов задержки, причем информационный вход второго дешифратора соединен с вторым выходом адреса блока задания исходных данных, выход строба второго адреса соединен со стробирующим входом второго дешифратора, группа выходов которого соединена с группой входов синхронизации регистра задания вида синхронизации, группа информационных входов которого соединена с выходом кода вида синхронизации блока задания исходных данных, второй и третий входы строба записи которого соединены со стробирующими входами соответственно регистра задания входов синхронизации и блока элементов И, группа информационных входов которого соединена с выходами регистра задания входов син- хронизации, группа информационных входов которого соединена с разрядными выходами входного регистра, выходы блока элементов И соединены с входами строба записи соответствующих блоков формирования воздействий и приема результатов, выход каждого мультиплексора соединен с входом синхронизации соответствующего блока формирования воздействий и приема результатов и через соответствующий элемент задержки - с входом синхронизации соответствующего блока определения входов-выходов, группа входов синхронизации устройства соединена с группами информационных входов мультиплексоров, адресные входы которых соединены с соответствующими группами выходов регистра задания вида синхронизации, выход начальной установки блока задания исходных данных соединен с входом начальной установки регистра задания вида синхронизации, установочный вход которого соединен с шиной константы единицы устройства.

/ 9 / W

/ 9 ( VH

Ll

v.

jjVH

I

Ј0/0- ЬХ О/УШО

ЈDH4rObVtf jjOJO

шо

МШО

С) О/О ЈШО

./

гггзги

ZZZSZLI

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1987 |

|

SU1506450A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-07—Публикация

1990-02-16—Подача