быстродействия. Поставленная цель достигается за счет введения первых 8 и вторых 12 сумматоров, последовательно соединенных вычислительного блока 9 и блока 10 сравнения, а в каждом блоке 2 обработки сигналов - компенсатора межсимвольных искажений, первого и второго вычислительных блоков. Увеличение быстродействия приводит (( уменьшению длительности тактового интервала, и следовательно, при неизменности времени рассеяния в канале - к увеличению порядка системы, что практически не сказывается на частотных свойствах вычислительного блока 9. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1991 |

|

RU2065668C1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1994 |

|

RU2085047C1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1256213A1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1210225A1 |

| Устройство демодуляции двоичных сигналов | 1986 |

|

SU1394457A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В МНОГОЛУЧЕВОМ КАНАЛЕ СВЯЗИ И ДЛЯ ОЦЕНКИ ПАРАМЕТРОВ КАНАЛА | 2004 |

|

RU2271070C2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В МНОГОЛУЧЕВОМ КАНАЛЕ СВЯЗИ | 2004 |

|

RU2267230C1 |

| Устройство для приема бинарных сигналов | 1986 |

|

SU1385320A1 |

| Устройство для регенерации цифрового сигнала с компенсацией межсимвольных искажений | 1986 |

|

SU1327304A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

Изобретение относится к технике радиосвязи и может найти применение в системах передачи дискретных сообщений по каналам связи с рассеянием энергии принимаемых сигналов по времени и частоте, например в декаметровом канале связи. Целью изобретения является повышение быстродействия. Поставленная цель достигается за счет введения первых 8 и вторых 12 сумматоров, последовательно соединенных вычислительного блока 9 и блока сравнения 10, а в каждом блоке 2 обработки сигналов - компенсатора межсимвольных искажений, первого и второго вычислительных блоков. Увеличение быстродействия приводит к уменьшению длительности тактового интервала, и следовательно при неизменности времени рассеяния в канале - к увеличению порядка системы, что практически не сказывается на частотных свойствах вычислительного блока 9. 2 ил.

Изобретение относится к технике радиосвязи и может найти применение в системах передачи дискретных сообщений по каналам связи с рассеянием энергии принимаемых сигналов по времени и по частоте, например в декаметроЕюм канале связи.

Целью изобретения является повышение быстродействия.

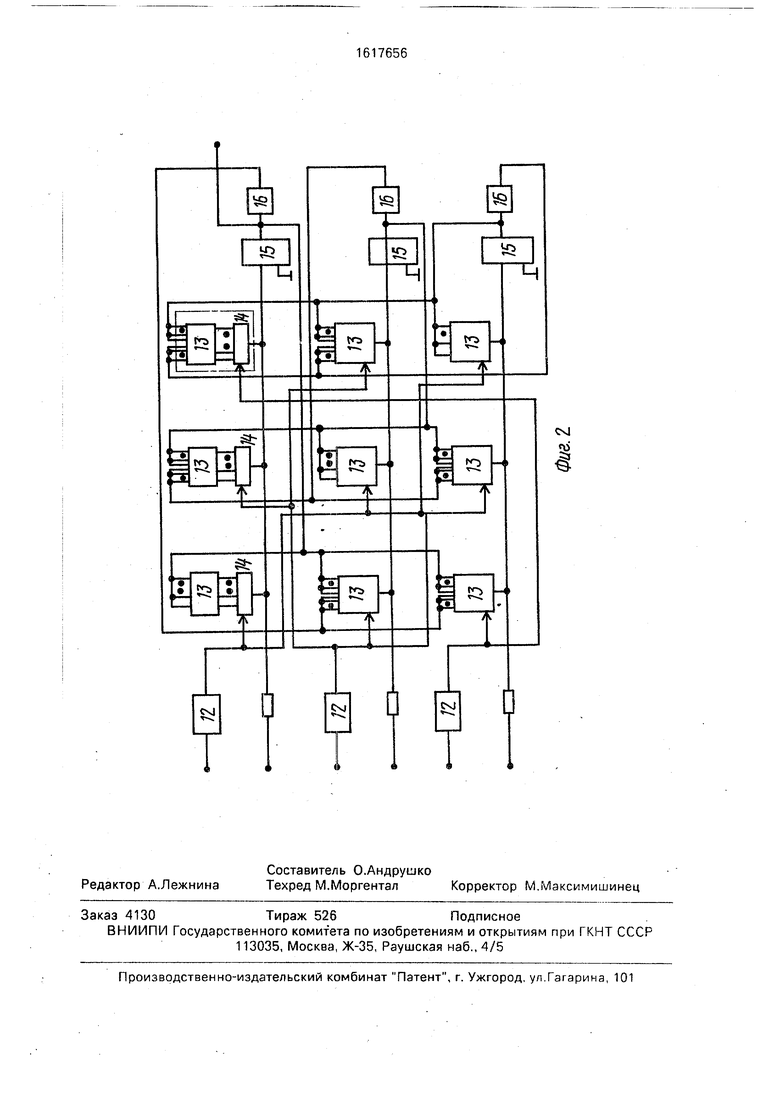

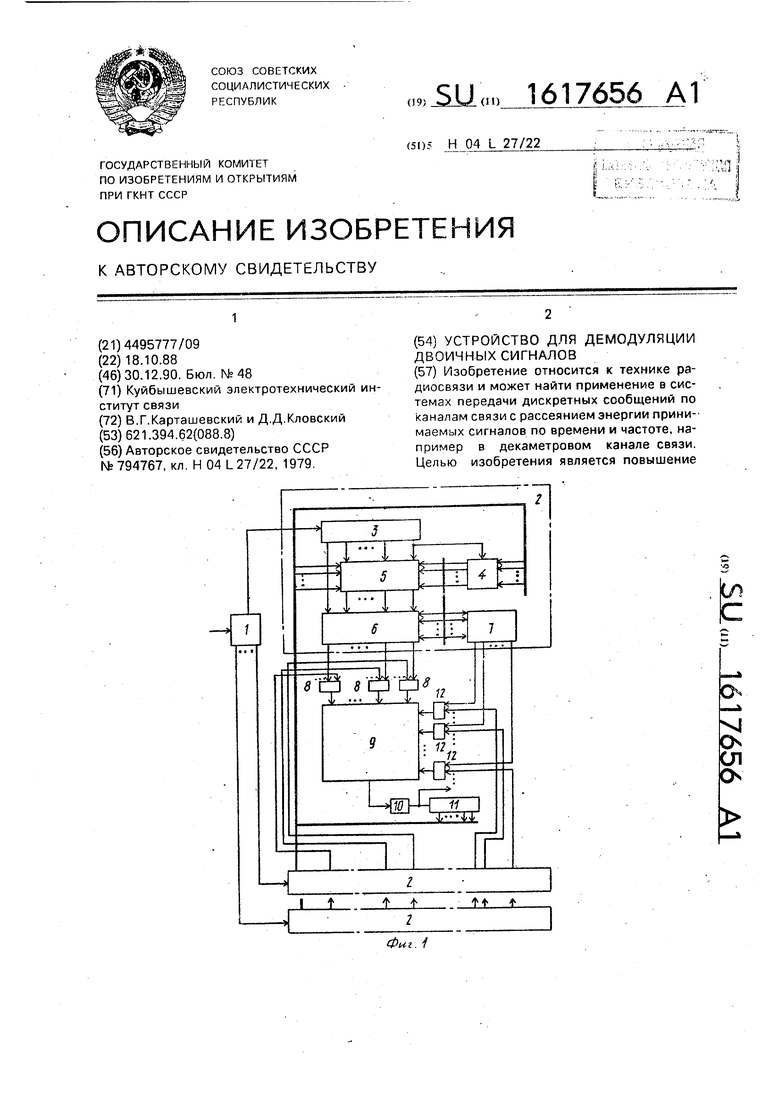

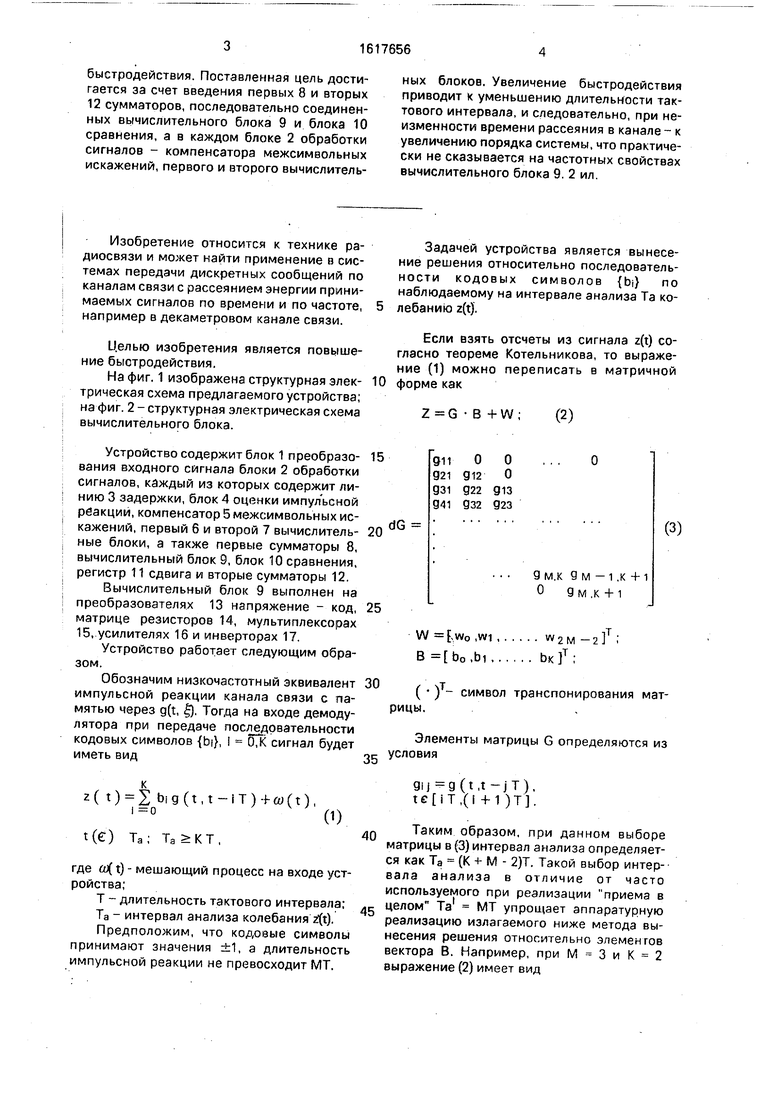

На фиг. 1 изображена структурная элек- трическая схема предлагаемого устройства; на фиг. 2 - структурная электрическая схема вычислительного блока.

Устройство содержит блок 1 преобразо- вания входного сигнала блоки 2 обработки сигналов, каждый из которых содержит линию 3 задержки, блок 4 оценки импул ьсной реакции, компенсатор 5 межсимвольных искажений, первый 6 и второй 7 вычислитель- ные блоки, а также первые сумматоры 8, вычислительный блок 9, блок 10 сравнения, регистр 11 сдвига и вторые сумматоры 12.

Вычислительный блок 9 выполнен на преобразователях 13 напряжение - код, матрице резисторов 14, мультиплексорах 15, усилителях 16 и инверторах 17.

Устройство работает следующим образом.

Обозначим низкочастотный эквивалент импульсной реакции канала связи с памятью через g(t, . Тогда на входе демодулятора при передаче последовательности кодовых символов {Ь|), I 0,К сигнал будет иметь вид

z( t) |; big(t,t-iT)-fw(t),

0) t(C) Та; ,

где йХ t) - мешающий процесс на входе устройства;

Т - длительность тактового интервала;

Та - интервал анализа колебанияХ1).

Предположим, что кодовые символы принимают значения ±1, а длительность импульсной реакции не превосходит МТ.

Задачей устройства является вынесение решения относительно последовательности кодовых символов {bi} по наблюдаемому на интервале анализа Та ко- лебанинэ z(t).

Если взять отсчеты из сигнала z(t) согласно теореме Котельникова, то выражение (1) можно переписать в матричной форме как

В +W

(2)

dG

(3)

9 М.К 9 М -1 .к +1 о 9м.к -М

25

30 35

40

5

W , Wo ,wiw 2 М - 2 :

,bibKf;

( ) - символ транспонирования матрицы.

Элементы матрицы G определяются из условия

(t,t-jT), ,(i +1 )Т.

Таким образом, при данном выборе матрицы в (3) интервал анализа определяется как Та (К + М - 2)Т. Такой выбор интервала анализа в отличие от часто используемого при реализации приема в целом Та МТ упрощает аппаратурную реализацию излагаемого ниже метода вынесения решения относительно элементов вектора В. Например, при М 3 и К 2 выражение (2) имеет вид

Если бы wi (t) О . то уравнение Z: - G -В имело бы решение § при известной в месте приема матрице G (G обратная матрица). Решения Во, .I io

можно было бы получить из системы уравнений

. : .

УОО bo +уо1 bi +.. .уо,к -Ьк fo;

УЮ Ьо +У11 bi +. . .у.к Ьк fi (5) 15

УК.о bo +ук,1 bi +. . .ук.К Ьк fK,

являющейся эквивалентной формой записи выражения (2) при W О, где20

2М -2 .

yKj 2 giK

91 j

(6)

25

30

2М -2

УК 2 9i К Zi ;

j,K 0,1М-1.

В случае ш (t) 5 О система(5) может оказаться несовместной или определитель системы будет близок к нулю, т.е. символ G Z может не иметь смысла Для того, чтобы гарантировать возможность получения решений о, i1зм-1 из (2), можно рассматривать модифицированную сие- 35 тему уравнений, отличающуюся от системы 5) наличием смещения а в коэффициентах ij, ,K, т.е. в диагональных элементах (а О). При этом получающееся решение имеет вид40

B2(),

(7)

где I - единичная матрица.

Когда К и М соизмеримы, можно считать, что параметры канала остаются практически неизменными, что упрощает вид матрицы G и соответственно вычисл ение коэффициентов ук j в выражении (6). Так, для системы (4), решение относительно Ьо из (7) имеет вид

bA (fo Cyo+a)2-yi2

-i1Y(Yo+a}-Y2 + + (yo+or)n)};

: io

.

15

20

25

30

3540

45

50

55

А (уо+а)(уо+а)2-). -2yi2(yo+a)(yo+a) (8)

УО УОО yil У22 91 +92

У2 Уо2 уг2 91 дз; to 9iZo +92Zi +g3Z2 ; fi 9lZi+g2Z2-I-93Z3; f2 9iZ2+g2Z3-J-gaZ,

где предполагается равенство параметров канала:

91 911 912 913;

92 921 922 923;

93 931 932 933.

Отличительная особенность решения (8) заключается в том, чтоЪо может принимать все возможные значения на числовой прямой и для окончательного формирования ре- шения нужно DO сравнить с нулевым порогом, т.е. формировать решение по правилу.

Vл

Ьо sl9n bo(9)

При К - 00 данным методом можно пользоваться, сдвигая интервал анализа Та (2М - 2) Т I к-м по оси времени на тактовый интервал и вынося решение каждый раз о символе, занимающем первую позицию, внутри Та, с предварительным вычитанием последействия от символов, по которым уже принято решение с помои1ью обратной связи по решению. Этот метод реализован в устройстве.

Блок 1, на вход которого поступает канальный- сигнал, выбирает и запоминает отсчеты, причем число выходов блока 1 N 2FT, так что последовательность отсчетов на каждом выходе может рассматриваться как ветвь разнесения (F - полоса частот сигнала).

Блок 3 представляет собой дискретно- аналоговую линию задержки, которая в течение тактового интервала Т сохраняет на своих (2М-1) отводах 2, i 1,{2М-1)входногй сигнала.

Блок 4 оценки импульсной реакции по наиболее задержанному отсчету входного сигнала.с использованием обратной связи по решению создает на своих М выходах оценки отсчетов импульсной реакции, обновляемые на каждом тактовом интервале, Т, т.е. осуществляет слежение за изменяющимися параметрами канала связи.

Компенсатор 5 межсимвольных искажений осуществляет вычитание последействия от символов, по которым ранее приняты решения, хранящиеся в регистре 11 сдвига. Пусть, например, М 3 и на выходе линии 3 задержки в i-й момент времени зафиксировано (2М-1) отсчетов входного сигнала: Zi, Zi-i, Zi-2, Zi-3, Zi-4. При этом в регистре 11 .сдвига хранятся решения bi-i, 01-2, 81-3, ей, Di-5, DI-6. Компенсация межсимвольных искажений заключается в формировании очищенных отсчетов по правилу

- Ь| - 2 92 - Ь| - 3 дз;

7v - A-jt4 3 - -Ь,-зд2-Ь,--,дз, ,oj

Zi-3 Zi -3 --bi -3gi iJ л|Vл

-bi - 4 g2 - bf -- 5 g ;

Zj-4 -bi--4gl -bi -5g2 - bi - бдз .

В выражении (10) gi, дз, дз - оценки отсчетов импульсной реакции, полученные в блоке 4. Отсчет Zi не обрабатывается в компенсаторе 5, так как решение 6i еще только предстоит получить внутри данного тактового интервала на выходе блока 10. Так как все решения принимают значения +1, реализовать (10) можно с использованием ключевых перемножителей и операционных усилителей, включенных по схеме инвертирующего сумматора.

В первом вычислительном блоке 6 осуществляется вычисление значений fk, К 0,1М-1, согласно (6) по очищенным отсчетам входного сигнала и оценкам импульсной характеристики. Для рассматриваемого примера (М 3):

fo, gi Zi + g2 Z| -1 Ч- дз Zi - 2

JCл -ч, Л -,. л -,

Т1 g 1 Zi - 1 -t- g2 Zi - 2 -f дз Zi - 3 ;

f2 gi Zi -2 -bg2 Zi -3 -fgaZi -4. (11)

Реализовать вычисление значений bk, К 0,1, М-1, можно на основе перемножителей и сумматоров, выполненных с использованием операционных усилителей.

Во втором вычислительном блоке 7 формируются коэффициенты из (6). В силу особенностей матрицы G, когда параметры канала связи на интервале анализа предполагаются неизменными, общее число отличающихся друг от друга коэффициен- тов ykj , которые надо вычислить для решения системы (5), равно М. В рассматриваемом примере это уо ,yi, yi . Вычисляются они согласно формулам (8), где вместо отсчетов импульсной реакции берутся их оценки на выходе блока 4. Структура выражений (11) и (8) совпадает (содержатся операции умножения и сложения), поэтому и практическая реализация схемных решений по вы- числению fk, К О, М-1, и ykj J О, М-1, совпадает.

В N-входовых сумматорах 8 осуществляется сложение одноименных значений ко- эффициентов f и у различных ветвей разнесения, что обеспечивает когерентное сложение ветв,ей.

По сформированным значениям коэффициентов f и у по выбранному значению а, которое добавляется к диагональным коэффициентам системы (5) для обеспечения устойчивости получаемых решений, в вы- 0 числительном блоке 9 находятся оценки о, 1DM-I. Резисторы, определяющие коэффициенты системы (5) с учетом смещения диагональных элементов } i , выбираются

0

5

5

из условий:

30

(11)

Rij

5

0

1 1,2,3.

В силу того, что У| i и У| J - непрерывные величины, при 1имающие произвольные значения обоих знаков (за исключением У| I, которые положительны), весь диапазон изменения каждого коэффициента разбит на интервалы и количество резисторов в каждой матрице 14 резисторов определяется числом интервалов, а значение каждого резистора определяется средним значением интервала(для коэффициентов/ i добавляется смещение а ). Нужный резистор подключается к схеме мультиплексором 15, управляемым преобразователем 13 напряжение - код, на вход которого подается соответствующее напряжение из второго вычислительного блока 7. Решение системы осуществляется методом компенсации токов на входе каждого операционного усилителя практически мгновенно, независимо от порядка системы.

5 Увеличение быстродействия приводит к уменьшению длительности тактового интервала Т и при неизменности времени рассеяния в канале это к увеличению порядка системы (5), что практически не сказывается

5

0

на частотных свойствах вычислительного, блока 9.

На выходе вычислительного блока 9 формируется оценка Ьо. которая для правра- щения в решение Ьо подается на блок 10 сравнения, представляющий собой пороговое устройство с нулевым порогом. Полученное на выходе блока 10 сравнение решение подается получателю сообщений и запоминается в регистре 11 сдвига для вы- читания последействия от него на следующем тактовом интервале.

Повышение быстродействия достигается без ухудшения технических характеристик из-за ограниченных частотных свойств ключевых перемножителей при дискретном характере перебора гипотез относительно реализации передаваемой двоичной последовательности за счет отказа от дискретно го характера перебора гипотез и перехода к 2 аналоговому перебору, позволяющему использовать в данном случае схему на опера- ционных усилителях.

Формула изобретения

Устройство для демодуляции двоичных сигналов, содержащее регистр сдвига и блок преобразования входного сигнала, выходы которого подключены к сигнальным входам блоков обработки сигналов, каждый из которых содержит последовательно соединенные линию задержки и блок оценки импульсной реакции, причем вход линии задержки является сигнальным входом блока обработки сигналов, а вход блока преобра,

5 10

15 20

5

0 5

зования входного сигнала и вход регистра сдвига являются соответственно входом и выходом устройства, отличающееся тем, что, с целью повышения быстродействия, введены первые и вторые сумматоры и последовательно соединенные вычислительный блок и блок сравнения, а в каждом блоке обработки сигналов - компенсатор межсимвольных искажений, первый и второй вычислительные блоки, при этом первые и вторые выходы блоков обработки сигналов подключены к входам соответственно первых и вторых сумматоров, выходы которых подключены к вычислительному блоку, выход блока сравнения подключен к входу регистра сдвига,- выходы которого подключены к управляющим входам блоков обработки сигналов, в каждом из которых соответствующие выходы линии задержки подключены к первому входу первого вычислительного блока и первым входам компенсатора межсимвольных искажений, выходы которого Подключены к вторым входам первого вычислительного блока, выходы блока оценки импульсной реакции подключены к входам второго вычислительного блока, вторым входам компенсатора межсимвольных искажений и третьим входам первого вычислительного блока, выходы которого, а также выходы второго вычислительного блока являются соответственно первыми и вторыми выходами блока обработки сигналов, управляющими входами которого являются вторые входы блока оценки импульсной реакции и третьи входы компенсатора межсимвольных искажений.

Ч

fr

ю

&

rrs

ira

ГГ5

D

C4J

Ч

Ж

to

CSJ

i

ш

0

Cxt

| Устройство для демодуляциидВОичНыХ СигНАлОВ | 1979 |

|

SU794767A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-12-30—Публикация

1988-10-18—Подача