(Л

00

СП

00

14D

реакции, с М выходов блока 15 отсчеты поступают на 2-е входы перемножителей 16 соответствующей группы из N перемножителей. К 1-му входу каждого перемножите-; ля 1.6 подключен один из (N + M-1) выходов счетчика 3. За цикл перебора на 1-х (N-fM-I) выходах счетчика 3 формиру-: ются 2 комбинаций дискретных символов. С перемножителей 16 сигналы поступают на М-входовые С 13. На выходах N-x С 13 за цикл перебора формируются комбинаций последовательности эталонных сигналов. С выхода каждого С 13 эталонные сигналы

поступают на i2-e входы соответствующего блока. 12, на выходе к-рых формируются разности между принимаемыми и эталонными сигналами. На выходе С 14 формируется общая мера близости между последовательностями этих сигналов. В качестве меры отклонения м.б. квадрат разности, либо модуль разности. Дискриминатор 5 регистрирует момент, когда какая-то из очередных 2 комбинаций последовательностей эталонных сигналов менее отличается от принимаемой, чем предыдущие. 1 табл. I ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для демодуляции двоичных сигналов | 1987 |

|

SU1515386A2 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1989 |

|

SU1809739A1 |

| Устройство для демодуляции двоичных сигналов | 1982 |

|

SU1078662A1 |

| Устройство для демодуляции двоичных сигналов | 1985 |

|

SU1332559A2 |

| Устройство для демодуляциидВОичНыХ СигНАлОВ | 1979 |

|

SU794767A1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1991 |

|

RU2065668C1 |

| Регенератор бинарных сигналов | 1987 |

|

SU1467773A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2102836C1 |

| Регенератор бинарных сигналов | 1987 |

|

SU1434553A1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1256213A1 |

Изобретение относится к электррсвязи. Цель изобретения ,- повышение помехоустойчивости. Устр-во содержит блок 1 преобразования сигналов, блок 2 обработкЙГ сигналов, счетчик 3, дискриминатор 5 уровня, регистр (Р) 6, сумматор (С) 9. Блок 2 содержит линию 11 задержки , вычиГаю- щие блоки 12, С 13 и 14, блок 15 определения импульсной реакции и перемножители 16. Введены блок 4 задержки, Р 7, триггер 8, компаратор 10. Р 6 и 7 содержат ячейки 17 памяти: С блока 1 демодулиро- вакные отсчеты сигнала поступают на ли- нию П, с выходов к-рой отсчеты сигнала подаются на 1-е входы N блоков 12, а с дополнительного выхода на блок 15, в к-ром производится оценка отсчетов импульсной

Изобретение относится к электросвязи и. может найти применение в устройствах для приема бинарных сигналов, передаваемых по каналам систем связи и физическим Цепям.

Целью изобретения является повыщение помехоустойчивости.

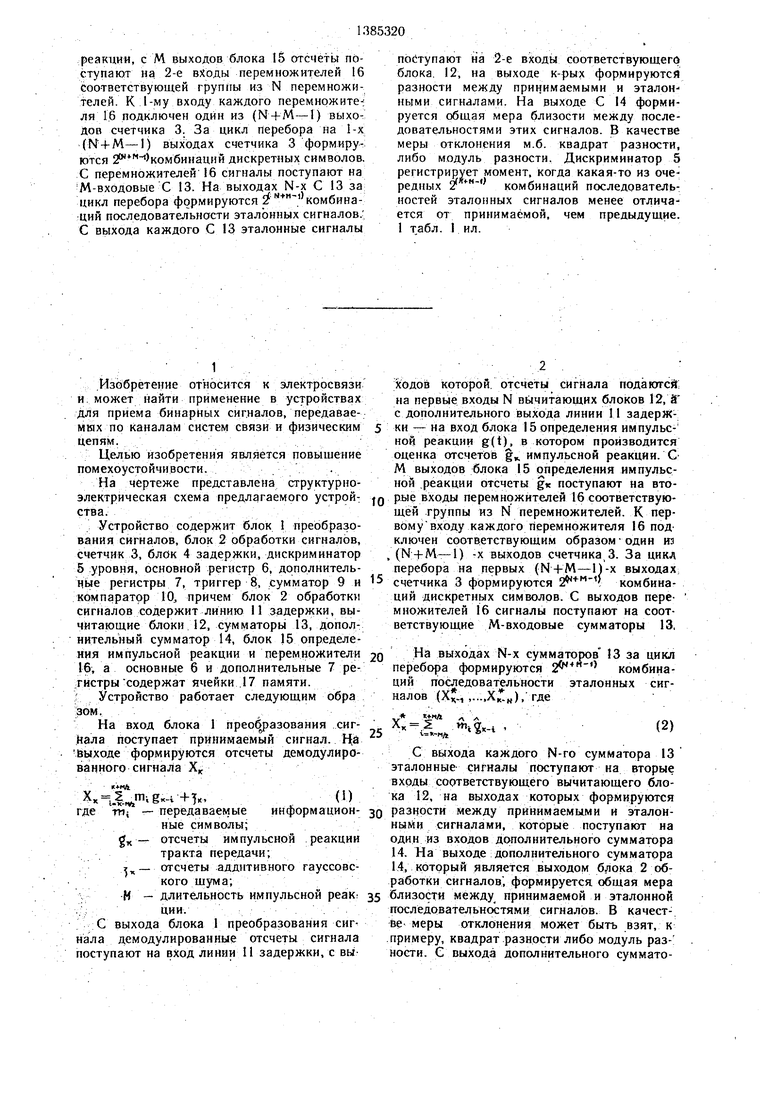

На чертеже представлена структурно- электрическая схема предлагаемого устрой: ства.

Устройство содержит блок 1 преобразования сигналов, блок 2 обработки сигналов, счетчик 3, блок 4 задержки, дискриминатор 5 :уровня, основной регистр 6, дополнительные регистры 7, триггер 8, сумматор 9 и компаратор 10,, причем блок 2 обработки сигналов содержит линию 11 задержки, вычитающие блоки 12, сумматорь 13, дополнительный сумматор 14, блок 15 определения импульсной реакции и теремножители 16, а основные 6 и дополнительные 7 регистры содержат ячейки 17 памяти. Устройство работает следующим обра зом.

На вход блока 1 преобразования сиг- Мала поступает принимаемый сигнал. На йыходе формируются отсчеты демодулиро- ванного сигнала X,f

ittf

X.2 mvgK-i -I-V(1)

где ти; -- передаваемые информационные символы; g - отсчеты импульсной реакции

тракта передачи; отсчеты аддитивного гауссовского щума; М - длительность импульсной реак:

. ;ЦИИ.

с выхода блока 1 преобразования сигнала демодулированные отсчеты сигнала поступают на вход линии II задержки, с вь1ходов которой, отсчеты сигнала подаютсй; на первые входы N вычитающих блоков 12, И с дополнительного выхода линии 11 задержки - на вход блока 15 определения импульсной реакции g(t), в котором производится оценка отсчетов g, импульсной реакции. С М выходов блока |5 определения импульсной .реакции отсчеты gK поступают на вторые входы перемножителей 16 соответствующей группы из N перемножителей. К первому входу каждого перемножителя 16 подключен соответствующим образом-один ш (N-fM-1) -X выходов счетчика 3. За цикл перебора на первых (N+M-1)-х выходах

счетчика 3 формируются комбинаций дискретных символов. С выходов перемножителей 16 сигналы поступают на соответствующие М-входовые сумматоры 13,

На выходах N-x сумматоров 13 за цикл перебора формируются комбинаций последовательности эталонных сигналов (Х.,,...,), где

«+«д

Л -мЛ

-,2x-i

(2)

С выхода каждого N-ro сумматора 13 эталонные сигналы поступают на вторые входы соответствуиэщего вычитающего блока 12, на выходах которых формируются

0 разности между принимаемыми и эталонными сигналами, которые поступают на один из входов дополнительного сумматора 14. На выходе дополнительного сумматора 14, который является выходом блока 2 работки сигналов , формируется общая мера

5 близости между принимаемой и эталонной последовательностями сигналов. В качестве меры отклонения может быть взят, к примеру, квадрат разности либо модуль раз-; ности. С выхода дополнительного суммато10

pa 14 сигнал поступает на вход дискриминатора 5 уровня, который регистрирует момент, когда какая-то из очередных -х комбинаций последовательности эталонных сигналов менее отличается от принимаемой, е «ем предыдущие.

По этому сигналу последовательность символов, соответствующая данной эталонной комбинации сигиалов, с первых (N-f-M-1)-х выходов счетчика 3 записывается в соответствующие ячейки 17 памяти осиовного 6 и дополнительных 7 регистров сдвига и триггера 8, в которых после окончания цикла перебора записана наиболее правдоподобная последовательность символов.

Дискриминатор 5 уровня работает следующим образом.

В начале цикла перебора при получении первой комбинации эталонной последовательности сигналов общая норма близости записывается в элемент памяти дискриминатора 5 уровня, а соответствующие ей (N-FM-1) дискретных символор с первых (N-fM-1) выходов счетчика 3 записываются в ячейки 17 памяти и триггер 8. На

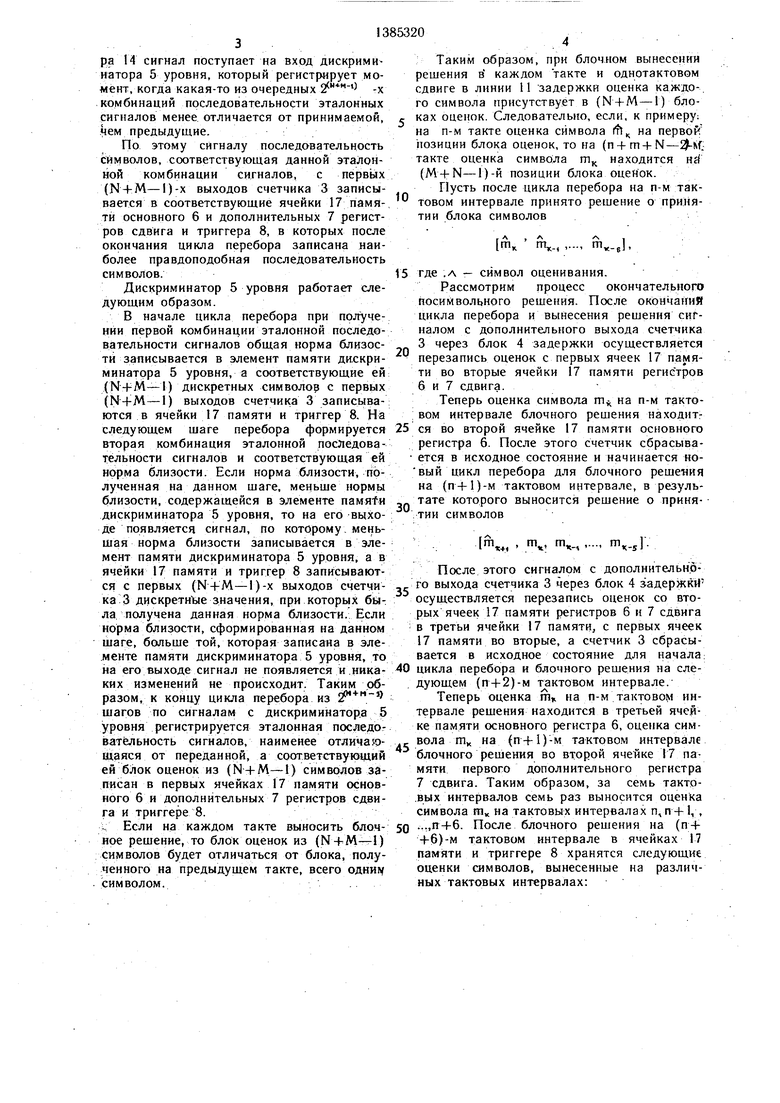

Таким образом, при блочном вынесении решения в каждом такте и однртактовом сдвиге в линии 11 задержки оценка каждо-. го символа присутствует в (N+M-1) блоках оценок. Следовательно, если, к примеру: на п-м такте оценка символа ffl на первой позиции блока оценок, то на (n + m-fN- КГ.; такте оценка символа ш находится Hd (Мч-N-1)-й позиции блока оценок.

Пусть после цикла перебора на п-м тактовом интервале принято решение о принятии блока символов

т„

-,

т.

15 где .А - символ оценивания.

Рассмотрим процесс окончательного посимвольного решения. После окончаний цикла перебора и вынесения решения сигналом с дополнительного выхода счетчика 3 через блок 4 задержки осуществляется перезапись оценок с первых ячеек 17 памяти во вторые ячейки 17 памяти регис тров 6 и 7 сдвига.

Теперь оценка символа т. на п-м тактовом интервале блочного решения находит:

20

следующем щаге перебора формируется 25 ся во второй ячейке 17 памяти основного вторая комбинация эталонной посЛедова- регистра 6. После этого счетчик сбрасыва- тельности сигналов и соответствующая ей норма близости. Если норма близости, полученная на данном шаге, меньше нормы

т.

т, т..

ш

x-sJ

После этого сигналом с дополнительнЬется в исходное состояние и начинается но- вый цикл перебора для блочного рещеиия на (п + 1)-м тактовом интервале, в резуль- близости, содержащейся в элементе памяти -. тате которого выносится решение о приня- дискриминатора 5 уровня, то на его выхо- тии символов де появляется сигнал, по которому, меньшая норма близости записывается в элемент памяти дискриминатора 5 уровня, а в ячейки 17 памяти и триггер 8 записываются с первых (N+M-1)-х выходов счетчи- выхода счетчика 3 через блок 4 задержки- каЗ дискретные значения, при которь|Х бы- осуществляется перезапись оценок со вторых ячеек 17 памяти регистров 6 и 7 сдвига в третьи ячейки 17 памяти, с первых ячеек 17 памяти во вторые, а счетчик 3 сбрасывается в исходное состояние для начала:

на его выходе сигнал не появляется и ника- 40 цикла перебора и блочного решения на сле- кях изменений не происходит. Таким об- , дующем (пЧ-2)-м тактовом интервале.

Теперь оценка т на п-м тактовом интервале решения находится в третьей ячейке памяти основного регистра 6, оценка символа ш на (п + 1)-м тактовом интервале блочного решения во второй ячейке 17 памяти первого дополнительного регистра 7 сдвига. Таким образом, за семь такто- .вых интервалов семь раз выносится оценка символа т на тактовых интервалах п, n-f 1,л

Если на каждом такте выносить блоч- 50 -мП+б. После блочного решения на (п + ное решение, то блок оценок из () +6)-м тактовом интервале в ячейках 17 символов будет отличаться от блока, полу- и триггере 8 хранятся следующие ченного на предыдущем такте, всего одни1у оценки символов, вынесенные на различ- символом.ных тактовых интервалах:

ла получена данная норма близости.; Если норма близости, сформированная на данном шаге, больше той, которая записана в элементе памяти дискриминатора 5 уровня, то

разом, к концу цикла перебора из 2 щагов по сигналам с дискриминатора 5 уровня регистрируется эталонная последовательность сигиалов, наименее отличаяэ- вдаяся от переданной, а соответствующий ей блок оценок из (N-fM-1) символов записан в первых ячейках 17 памяти основ ного 6 и дополнительных 7 регистров сдвига и триггере 8.

45

Таким образом, при блочном вынесении решения в каждом такте и однртактовом сдвиге в линии 11 задержки оценка каждо-. го символа присутствует в (N+M-1) блоках оценок. Следовательно, если, к примеру: на п-м такте оценка символа ffl на первой позиции блока оценок, то на (n + m-fN- КГ.; такте оценка символа ш находится Hd (Мч-N-1)-й позиции блока оценок.

Пусть после цикла перебора на п-м тактовом интервале принято решение о принятии блока символов

т„

-,

т.

где .А - символ оценивания.

Рассмотрим процесс окончательного посимвольного решения. После окончаний цикла перебора и вынесения решения сигналом с дополнительного выхода счетчика 3 через блок 4 задержки осуществляется перезапись оценок с первых ячеек 17 памяти во вторые ячейки 17 памяти регис тров 6 и 7 сдвига.

Теперь оценка символа т. на п-м тактовом интервале блочного решения находит:

т.

т, т..

ш

x-sJ

одное состояние и начин перебора для блочного -м тактовом интервале, рого выносится решение лов счетчика 3 через блок 4 з яется перезапись оценок 17 памяти регистров 6 и чейки 17 памяти, с перв во вторые, а счетчик 3 исходное состояние для

После этого сигналом с дополнительнЬя в исходное состояние и начинается но- й цикл перебора для блочного рещеиия (п + 1)-м тактовом интервале, в резуль- е которого выносится решение о приня- символов выхода счетчика 3 через блок 4 задержки ществляется перезапись оценок со втох ячеек 17 памяти регистров 6 и 7 сдвига ретьи ячейки 17 памяти, с первых ячеек памяти во вторые, а счетчик 3 сбрасытся в исходное состояние для начала

45

m

л m.

л

m.

л

A ,

та..

n

m.

С выходов регистров 6 и 7 сдвига и триг- 8 оценки символа т полученные на п,п +1 ,...,п+f)-M тактовых интервалах, поступают на сумматор 9, с пыхода сумматора 9 - на первый вход компаратора 10.

По сигналу с дополнительного выхода счетчика 3 компаратор 10 выносит оконча- тельное посимвольное рен1ение по следующему правилу:

1:.:

,

если Vj если ,

n+e /

где Vj 2. т,

ifn

напряжение на выходе

сумматора 9.,

После этого сигналом управления с дополнительного выхода счетчика 3 -через блок 4 задержки осуществляется перезапись оценок символов с 1-х ячеек 17 памяти в (I-f-l)-e ячейки памяти регистров сдвига, где I-N + M-2, N + M-3,...,1, а, счетчик 3 сбрасывается в исходное состояние для начала цикла перебйра и блочного ре- шения на следующем (n-f 7)-м тактовом интерпале. После блочного решения аналогичным образом с помощью сумматора 9, компаратора 10 мажоритарным способом выносится посимвольное рещение о символе гп и т.д.

Таким образом, введенная совокупность отличительных признаков позволяет повыл

m,

m.

Xt-l

л

m,

5

0

5

0

сить помехоустойчивость приема при воздействии межсимвольных искажений и аддитивных шумов.

Формула изобретения

Устройство для приема бинарных сиг-, налов, содержащее счетчик, ос.новной регистр сдвига, сумматор, последовательно соединенные блок преобразования сигналов, блок обработки сигналов, дискриминатор уровня, причем первые выходы счетчика подключены к вторым входам блока обработки сигналов, отличающееся тем, что, с целью повыщения помехоустойчивости, введены блок задержки, дополнительные регистры сдвига, триггер, компаратор, при этом первые выходы счетчика подключены к информационным входам основного и дополнительных регистров сдвига и триггера, выход дискриминатора уровня подключен к первым управляющим входам основного и дополнительных регистров сдвига и управляющему входу триггера, выход блока задержки подключен к вторым управляющим входам основного и дополнительных регистров сдвига, выходы которых, а также выход триггера подключены к входам сумматора, выход которого подключен к первому входу компаратора, второй вход которого соединен с вторым выходом счетчика и входом блока задержки.

| Устройство для демодуляциидВОичНыХ СигНАлОВ | 1979 |

|

SU794767A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-03-30—Публикация

1986-03-14—Подача