сравнения и блоками 10, 11 и 13 памя- контроля на центральном посту, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дистанционного управления транспортным средством | 1988 |

|

SU1604651A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Адаптивное устройство для защиты памяти | 1983 |

|

SU1103291A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для ввода информации | 1983 |

|

SU1151945A1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство сигнализации с по-дАчЕй СигНАлОВ ТРЕВОги HA цЕН-ТРАльНую СТАНцию | 1978 |

|

SU798939A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Адаптивный коммутатор | 1979 |

|

SU824264A1 |

Изобретение относится к железнодоожной автоматике и телемеханике.

Цель изобретения - повышение наежности устройства.

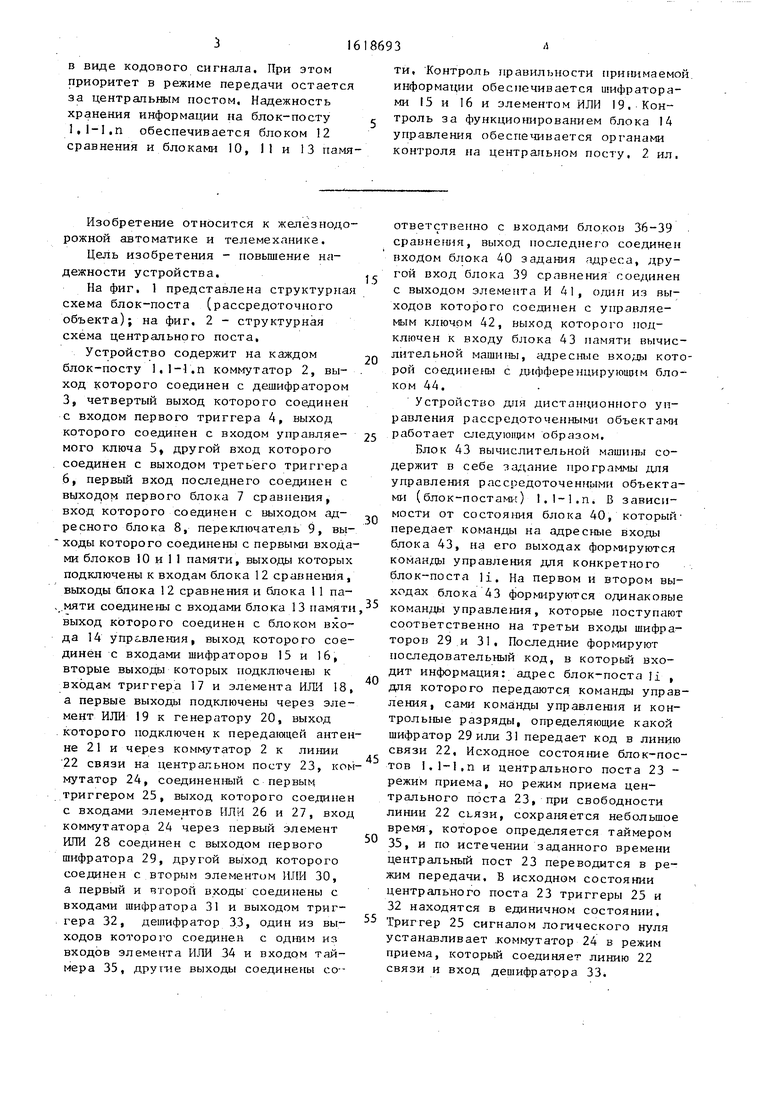

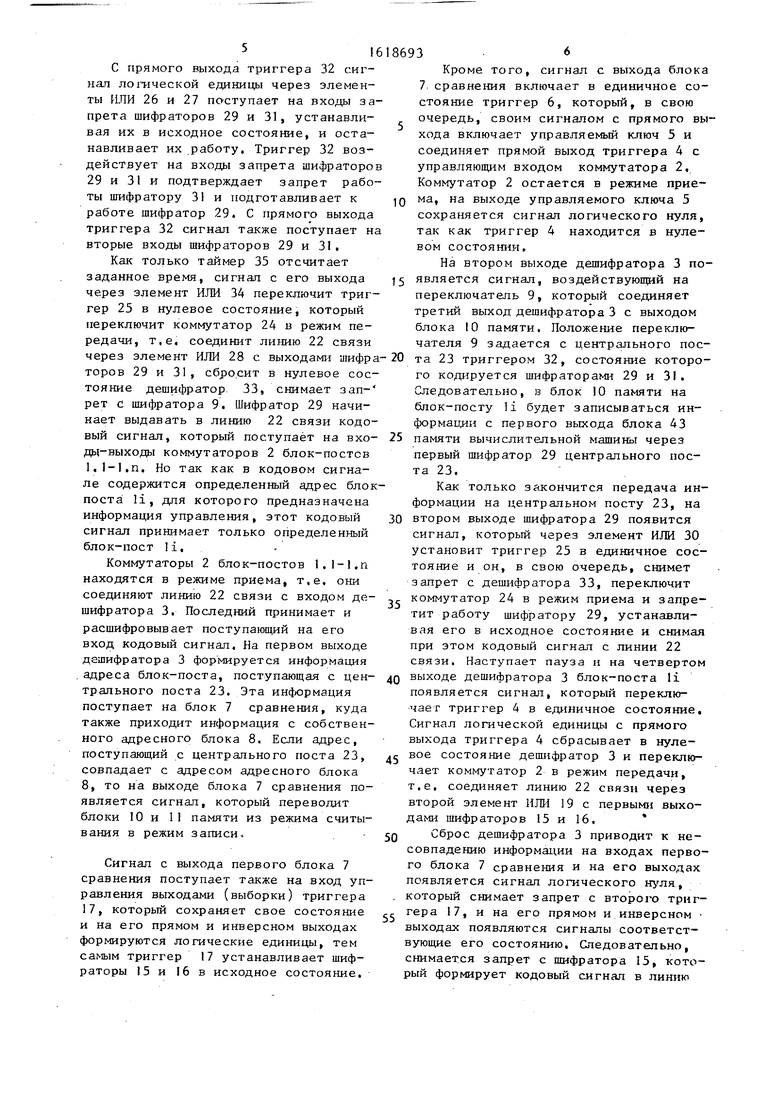

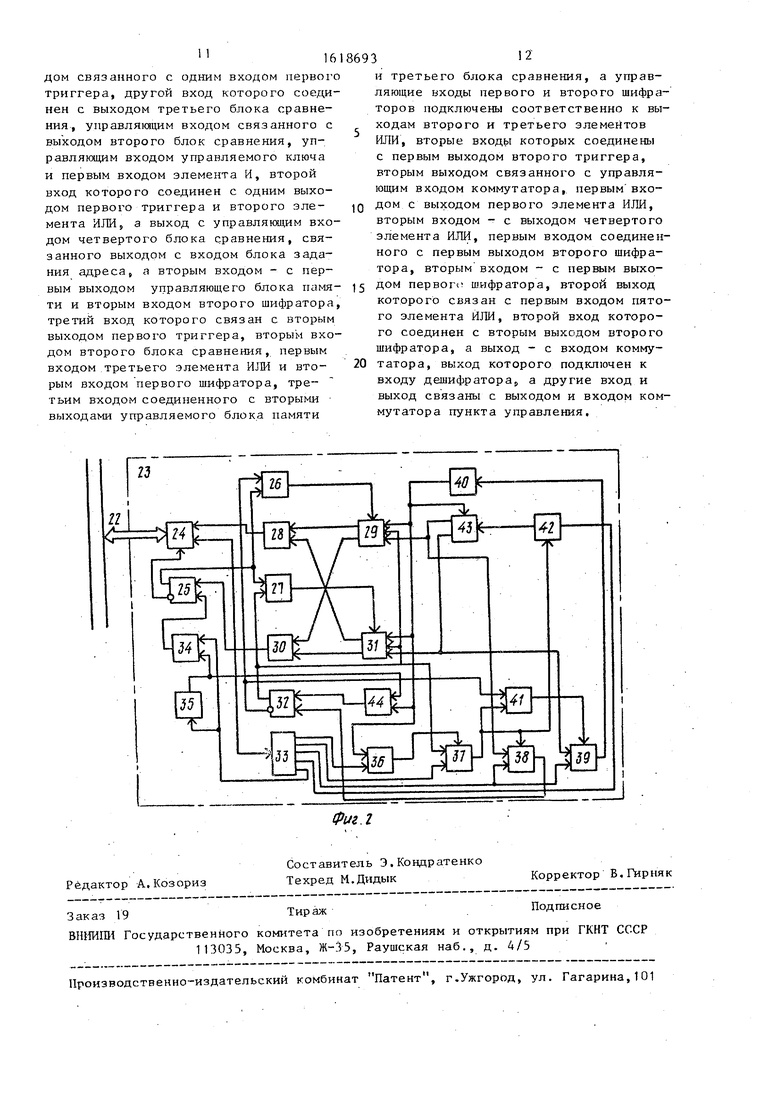

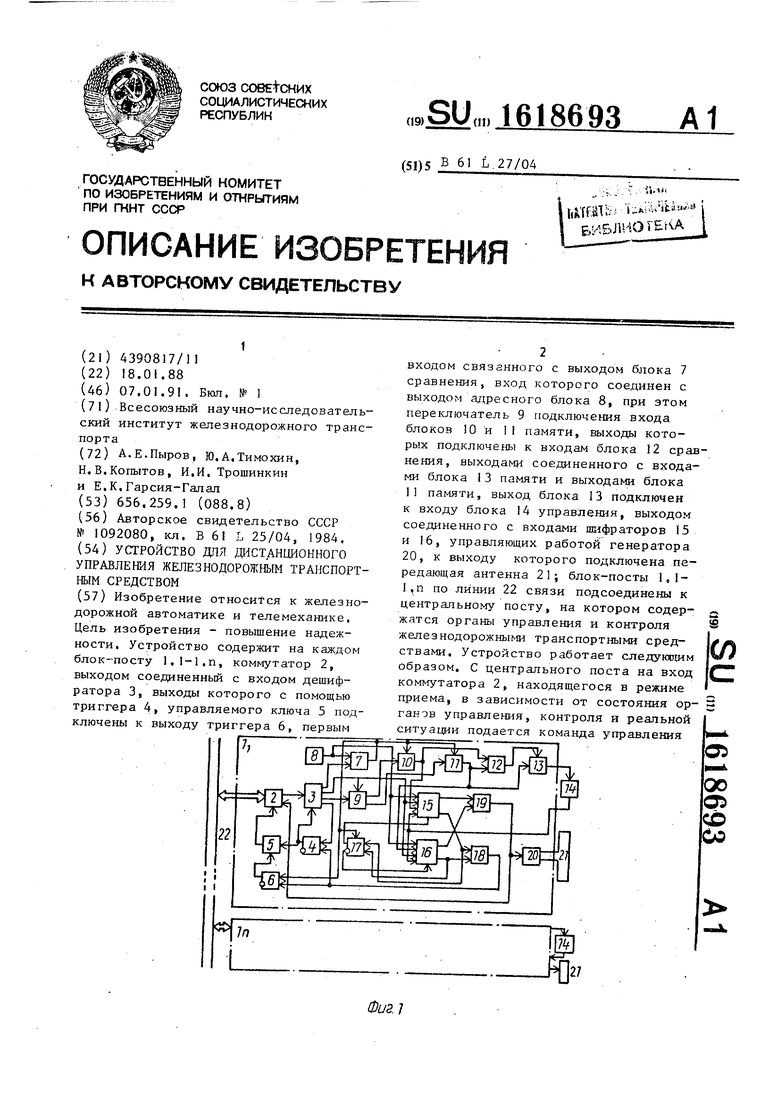

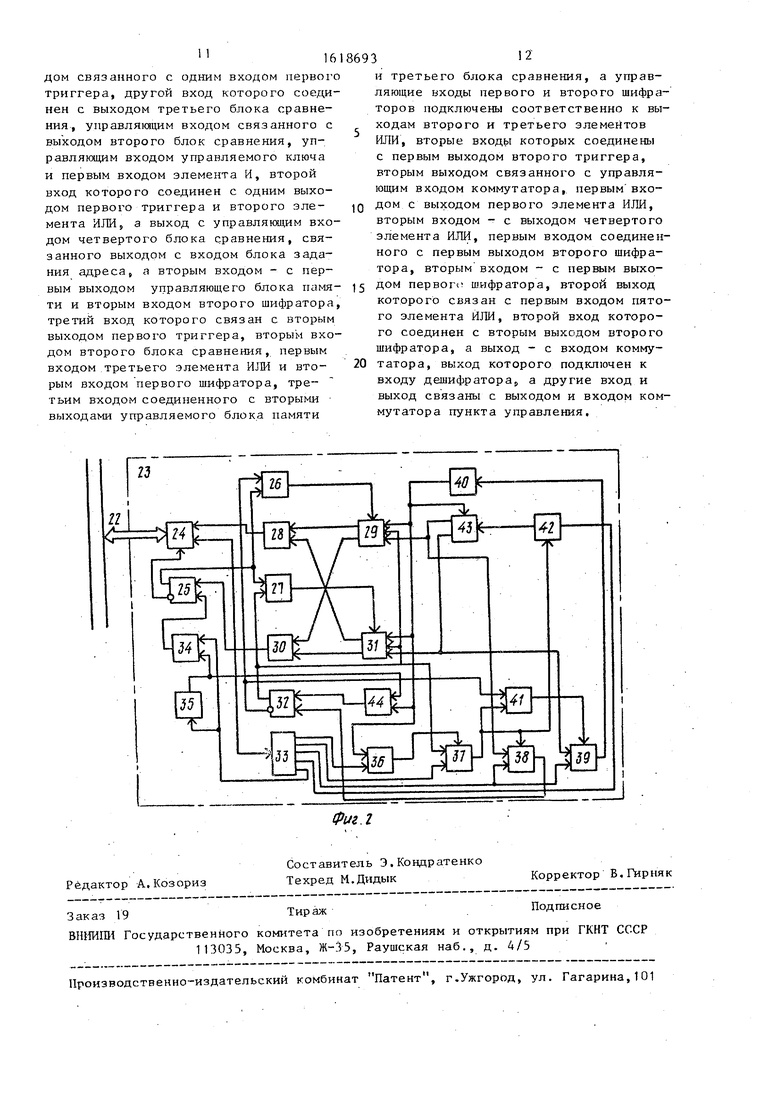

На фиг, 1 представлена структурная хема блок-поста (рассредоточного бъекта); на фиг, 2 - структурная хема центрального поста,

Устройство содержит на каждом блок-посту 1,-Г.п коммутатор 2, вы- . од которого соединен с дешифратором 3, четвертый выход которого соединен с входом первого триггера 4, выход которого соединен с входом управляемого ключа 5 другой вход которого соединен с выходом третьего триггера 6, первый вход последнего соединен с выходом первого блока 7 сравнения, вход которого соединен с выходом адресного блока 8, переключатель 9, вы-. ходы которого соединены с первыми входами блоков 10 и 1 1 памяти, выходы которых подключены к входам блока 12 сравнения, выходы блока 12 сравнения и блока 1 1 па- .мяти соединены с входами блока 13 памяти выход которого соединен с блоком входа 14 управления, выход которого соединен с входами шифраторов 15 и 16, вторые выходы которых подключены к входам триггера 17 и элемента ИЛИ 18, а первые выходы подключены через элемент ИЛИ 19 к генератору 20, выход которого подключен к передающей антенне 21 и через коммутатор 2 к линии 22 связи на центральном посту 23, коммутатор 24, соединенный с первым триггером 25, выход которого соединен с входами элементов ИЛИ 26 и 27, вход коммутатора 24 через первый элемент ИЛИ 28 соединен с выходом первого шифратора 29, другой выход которого соединен с.вторым элементом ИЛИ 30, а первый и второй входы соединены с входами шифратора 31 и выходом триггера 32, дешифратор 33, один из выходов которого соединен с одним из входов элемента ИЛИ 34 и входом таймера 35, другие выходы соединены со-

0

5

0

5

0

45

0

55

ответственно с входами блоков 36-39 сравнения, выход последнего соединен входом блока 40 задания адреса, другой вход блока 39 сравнения соединен с выходом элемента И 41, один из выходов которого соединен с управляемым ключом 42, выход которого подключен к входу блока 43 памяти вычислительной машины, адресные входы которой соединены с дифференцирующим бло- ком 44.

Устройство для дистанционного управления рассредоточенными объектами работает следующим образом.

Блок 43 вычислительной машины содержит в себе задание программы для управления рассредоточенными объектами (блок-постами) 1.1-1.п. В зависимости от состояния блока 40, который передает команды на адресные входы блока 43, на его выходах формируются команды управления для конкретного блок-поста Ц. На первом и втором выходах блока 43 формируются одинаковые команды управления, которые поступают соответственно на третьи входы шифраторов 29 и 31. Последние формируют последовательный код, в который входит информация: адрес блок-поста II , для которого передаются команды управления, сами команды управления и контрольные разряды, определяющие какой шифратор 29 или 31 передает код в линию связи 22, Исходное состояние блок-постов 1,1-1,п и центрального поста 23 - режим приема, но режим приема центрального поста 23, при свободности линии 22 сьязи, сохраняется небольшое время, которое определяется таймером 35, и по истечении заданного времени центральный пост 23 переводится в режим передачи. В исходном состоянии центрального поста 23 триггеры 25 и 32 находятся в единичном состоянии. Триггер 25 сигналом логического нуля устанавливает .коммутатор 24 в режим приема, который соединяет линию 22 связи и вход дешифратора 33.

516 С прямого выхода триггера 32 сигнал логической единицы через элементы ИЛИ 26 и 27 наступает на входы запрета шифраторов 29 и 31, устанавливая их в исходное состояние, и останавливает их работу. Триггер 32 воздействует на входы запрета шифраторов 29 и 31 и подтверждает запрет работы шифратору 31 и подготавливает к работе шифратор 29. С прямого выхода триггера 32 сигнал также поступает на вторые входы шифраторов 29 и 31 .

Как только таймер 35 отсчитает заданное время, сигнал с его выхода через элемент ИЛИ 34 переключит триггер 25 в нулевое состояние, который переключит коммутатор 24 в режим передачи, т.е. соединит линию 22 связи через элемент ИЛИ 28 с выходами шифраторов 29 и 31, сбросит в нулевое состояние дешифратор 33, снимает зап- рет С шифратора 9. Шифратор 29 начинает выдавать в линию 22 связи кодовый сигнал, который поступает на вхо- ды.-выходы коммутаторов 2 блок-постов 1,1-1.п. Но так как в кодовом сигнале содержится определенный адрес блокпоста 11, для которого предназначена информация управления, этот кодовый сигнал принимает только определенный блок-пост И,

Коммутаторы 2 блок-постов 1.1-l.n находятся в режиме приема, т.е. они соединяют линию 22 связи с входом дешифратора 3. Последний принимает и расшифровывает поступающий на его вход кодовый сигнал. На первом выходе дешифратора 3 формируется информация адреса блок-поста, поступающая с центрального поста 23. Эта информация поступает на блок 7 сравнения, куда также приходит информация с собственного адресного блока 8, Если адрес, поступающий с центрального поста 23, совпадает с адресом адресного блока 8, то на выходе блока 7 сравнения появляется сигнал, который переводит блоки 10 и 11 памяти из режима считывания в режим записи.

Сигнал с выхода первого блока 7 сравнения поступает также на вход управления выходами (выборки) триггера 17, который сохраняет свое состояние и на его прямом и инверсном выходах формируются логические единицы, тем самым триггер 17 устанавливает шифраторы 15 и 16 в исходное состояние.

36

Кроме того, сигнал с выхода блока 7 сравнения включает в единичное состояние триггер 6, который, в свою очередь, своим сигналом с прямого выхода включает управляемый ключ 5 и соединяет прямой выход триггера 4 с управляющим входом коммутатора 2, Коммутатор 2 остается в режиме приема, на выходе управляемого ключа 5 сохраняется сигнал логического нуля, так как триггер 4 находится в нулевом состоянии.

На втором выходе дешифратора 3 появляется сигнал, воздействующий на переключатель 9, который соединяет третий выход дешифратора 3 с выходом блока 10 памяти. Положение переключателя 9 задается с центрального поста 23 триггером 32, состояние которого кодируется шифраторами 29 и 31. Следовательно, в блок 10 памяти на блок-посту 11 будет записываться информации с первого выхода блока 43

памяти вычислительной машины через первый шифратор 29 центрального поста 23.

Как только закончится передача информации на центральном посту 23, на

втором выходе шифратора 29 появится сигнал, который через элемент ИЛИ 30 установит триггер 25 в единичное состояние и он, в свою очередь, снимет запрет с дешифратора 33, переключит

коммутатор 24 в режим приема и запретит работу шифратору 29, устанавливая его в исходное состояние и снимая при этом кодовый сигнал с линии 22 связи. Наступает пауза и на четвертом

выходе дешифратора 3 блок-поста 11 появляется сигнал, который переключает триггер 4 в единичное состояние. Сигнал логической единицы с прямого выхода триггера 4 сбрасывает в нулевое состояние дешифратор 3 и переключает коммутатор 2 в режим передачи, т.е. соединяет линию 22 связи через второй элемент ИЛИ 19 с первыми выходами шифраторов 15 и 16.

Сброс дешифратора 3 приводит к несовпадению информации на входах первого блока 7 сравнения и на его выходах появляется сигнал логического нуля, который снимает запрет с второго триггера 17, и на его прямом и инверсном

выходах появляются сигналы соответствующие его состоянию, Следовательно, снимается запрет с шифратора 15, который формирует кодовый сигнал в линию

22 связи на центральном посту 23, Этот кодовый сигнал состоит из собственного адреса блок-поста 1, информации с выхода блока 10 памяти, информации о состоянии переключателя 9 и контрольной информации с выходов блока 14 управления,

Кодовый сигнал с выхода коммутатора 2 блок-поста 11 поступает на центральный пост 23 и через .коммутатор 24 приходит на вход дешифратора 33, который принимает этот сигнал и расшифровывает его. На первом выходе дешифратора 33 формируется информация адреса блок-поста 11, которая поступает на первый блок 36 сравнения. Если эта информация совпадает с информа цией блока 40, то на выходе первого блока 36 сравнения появляется сигнал, который разрешает работу блока 37 сравнения.

С второго выхода дешифратора 33 информация о состоянии переключателя 9 на блок-посту 11 поступает на вход второго блока 37, которая должна соответствовать состоянию триггера 32. При совпадении этой информации на выходе блока 37 появляется сигнал, который разрешает блоку 38 и включает управляемый ключ 42, который подключает четвертый выход дешифратора 33 к входу блока 43 памяти вычислительной машины.

Информация третьего блока 38 сравнивается с информацией на первом выходе блока 43. Если информация на входах блока 38 одинаковая, то на выходе его появляется сигнал, который переключает триггер 32 в нулевое состояние, .тем самым подготавливая к работе шифратор 31 и запрещая работу шифратору 29. С четвертого выхода дешифратора 3 информация о состоянии работы блоков 1.4 управления блок-поста 11 поступает в блок 43 памяти,

Как только закончится передача информации с блок-поста шифратором 15, на втором его выходе появляется сигнал, который устанавливает триггер 17 в единичное состояние, а он, в свою очередь, запрещает работать шифратору 15 и, дает разрешение на работу шифратору 16 и через первый элемент ИЛИ 18 устанавливае-т триггеры 4 и 6 в нулевое состояние. Это приводит к снятию запрета с дешифратора 3, коммутатор 2 переключается в режим приема, выключается управляш-ый ключ 5.

0

5

0

5

0

5

В линии 22 связи наступает пауза, которая воспринимается на центральном посту 23 дешифратором 33, и на пятом его выходе появляется сигнал, который сбрасывает в нулевое состояние таймер 35, через третий элемент ИЛИ 34 устанавливает триггер 25 в нулевое состояние, который, в свою очередь, переключает коммутатор 24 в режиме передачи, сбрасывает дешифратор 33 в нулевое состояние, снимает запрет с шифратора 31, который будет передай ять кодовый сигнал через элемент ИЛИ 28 и коммутатор 24 в линию 22 связи для того же блок-поста 11, но этот кодовый сигнал шифратор 31 формирует из команд, поступающих с второго выхода блока 43, а .также с блока 40 и прямого выхода триггера 32, Эта информация, как ив первом случае, принимается на блок-посту 11 дешифратором 3 и обрабатывается так же, как и в первом случае, только переключатель 9 устанавливается в другое положение, так как второй триггер 32 на центральном посту 23 переключается, и информация на его выходе становится интенсивной и соеди- няет третий выход дешифратора 3 с входом блока 11 памяти, в который записывается информация управления.

По завершению передачи информации с центрального поста 23. происходят те же переключения блоков, как и в первом случае, с разницей только в том, что на блок-посту 11 информацию в линию связи выдает шифратор 16. На центральном посту 23 поступающий кодовый сигнал так же, как и в первом случае, обрабатывается дешифратором 33 и блоками 36 и 37, и при совпадении информации на входах блоков 36 и 37 сравнения на выходе блока 37 появляется сигнал логической единицы, который поступает на вход элемента И 41, на другом входе его. уже имеется логическая единица с инверсного выхода триггера 32, который переключается в состояние нуля сигналом с выхода блока 38, следовательно, на выходе элемента И 41 появляется сигнал, который разрешает производить сравнение информации с второго выхода блока 43 памяти и третьего выхода дешифратора 33. Если информация на входе блока 39 сравнения одинакова, на его выходе появляется сигнал, который поступает ча вход блока 40 задания адреса и изменяет в нем

у. адрес для обращения к следующему блок-посту 1.1 + 1. Изменение адреса н выходе блока 40 изменяет соответственно и команды управления на выходах блока 43, а также кратковременно включает дифференцирующий блок 4 который устанавливает триггер 32 в исходное единичное состояние.

После наступления паузы в линии 22 связи коммутатор 24 центрального поста 23 вновь включается в режим предачи и центральный пост 23 будет редавать информацию уже для следующго блок-поста l.i+li На предыдущем блок-посту 11 при равенстве на выходах многоразрядных блоков 10 и 11 пмяти сигнал с выхода второго блока 12 сравнения поступает на вход режи

ма Запись и трансляция блока 13 памяти, который перезаписывает информацию с выхода блока 11 памяти. С выхода блока 13 сигналы поступают на входы блока 14 управления данного объекта (блок-поста 11),

Формула изобретения

Устройство для дистанционного управления железнодорожным транспортным средством, содержащее на транспортном средстве дешифратор, первый выход которого соединен с первым входом блока сравнения, управляемый ключ, блок памяти и, управляемый переключатель, а на пункте управления - дешифратор, шифратор, блок сравнения, отличающееся тем что, с целью повышения надежности,, оно снабжено на транспортном средстве коммутатором, триггерами, элементами ИЛИ, дополнительными блоками памяти, шифраторами, дополнительными блоками сравнения, блоком адреса, выходом соединенным с первыми входами первого и второго шифраторов и вторым входом первого блока сравнения, выход которого соединен с управляющими входами первого и второго блоков памяти, управляющими входом первого триггера и одним входом второго триггера, выходом соединенного с входом управляемого ключа, а втором входом связанного с выходом первого элемента ИЛИ и одним входом третьего триггера, другим входом подключенного к второму входу дешифратора, а выходом - к управляющим входам дешифратора и управляемого ключа, выход которого подключен к комму10

8693

0

5

0

5

0

5

татору, выходом соединенному с входом дешифратора, третий выход которого соединен с управляющим входом управляемого переключателя и вторыми входами первого и второго шифраторов, четвертый выход - к входу управляемого переключателя, выходы которого соединены со входами соответственно первого и второго блоков памяти, выход первого из которых подключен к одному входу .второго блока сравнения и третьему входу первого шифратора, а выход вто- рсго блока памяти - к второму входу второго блока сравнения, третьему входу второго шифратора и входу третьего блока памяти, к управляющему входу которого подключен выход второго блока сравнения, а выход через блок управления подключен к четвертым входам первого и второго шифраторов, управляющие входы которых подключены к соответствующим выходам первого триггера, первый и второй входы которого соединены с первыми выходами соответственно первого и второго шифраторов и соответственно с первым и вторым входами первого элемента ИЛИ, а вторые выходы первого и второго шифраторов подключены к соответствующим входам второго элемента ИЛИ, выходом связанного с входом передатчика и коммутатора, а в пункте управления - .триггерами, элементами ИЛИ, дополнительным шифратором, элементом И, дополнительными блоками сравнения, блоком управления, передатчиком, блоком

0

0

5

зада ния адреса, таймером, дифференцирующим блоком, управляемым блоком памяти, управляемым ключом, выходом соединенным г. управляющим входом управляемого блока памяти, входом подключенного к выходу задания адреса, подключенному к первым входам первого и с второго шифраторов, дифференцирующего блока и первого блока сравнения, выт ход которого соединен с управляющим входом второго блока сравнения, второй вход которого соединен с первым выходом дешифратора, второй выход которого связан с первым входом второго блока сравнения, третий выход - с .первыми входами третьего и четвертого блоков, сравнения, четвертый выход -. с входом управляемого ключа, пятый выход - с входом таймера и первым входом первого элемента ИЛИ, второй вход которого подключен к выходу таймера и второму входу дифференцирующего блока, выхо11 161

дом связанного с одним входом первого триггера, другой вход которого соединен с выходом третьего блока сравнения, управляющим входом связанного с выходом второго блок сравнения, управляющим входом управляемого ключа и первым входом элемента И, второй вход которого соединен с одним выходом первого триггера и второго элемента ИЛИ, а выход с управляющим входом четвертого блока сравнения, связанного выходом с входом блока задания адреса, а вторым входом - с первым выходом управляющего блока памяти и вторым входом второго шифратора, третий вход которого связан с вторым выходом первого триггера, вторым входом второго блока сравнения, первым входом третьего элемента ИЛИ и вторым входом первого шифратора, третьим входом соединенного с вторыми выходами управляемого блока памяти

Редактор А.Козориз

Составитель Э. Кондратенко Техред М.Дидык

Заказ 19

Тираж

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

312

и третьего блока сравнения, а управляющие входы первого и второго шифраторов подключены соответственно к вы- ходам второго и третьего элементов ИЛИ, вторые входы которых соединены с первым выходом второго триггера, вторым выходом связанного с управляющим входом коммутатора, первым входом с выходом первого элемента ИЛИ, вторым входом - с выходом четвертого элемента ИЛИ, первым входом соединенного с первым выходом второго шифратора, вторым входом - с первым выходом первого шифратора, второй выход которого связан с первым входом пятого элемента ИЛИ, второй вход которого соединен с вторым выходом второго шифратора, а выход - с входом коммутатора, выход которого подключен к входу дешифратора„ а другие вход и выход связаны с выходом и входом коммутатора пункта управления.

Корректор В. Парняк

Подписное

Авторы

Даты

1991-01-07—Публикация

1988-01-18—Подача