импульсов, элемент И и триггер, вход установки в единицу которого подключен к выходу элемента ИЛИ, группа входов которого соединена с группой управляющих входов датчика и с группой входов п ифратора, группа выходов которого соединена с группой информациопных входов счетчика, счетный вход которого соединен с выходом элемента И, первый вход которого соединен с выходом генератора импульсов, выход переполнения счетчика соединен с входом установки в ноль триггера, выход которого соединен с выходом датчика и с вторым входом элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления углеродного потенциала | 1984 |

|

SU1257660A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Программируемый контроллер | 1983 |

|

SU1238032A1 |

| Матричный коммутатор | 1988 |

|

SU1596342A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

1. АДАПТИВНОЕ УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ, содержащее первый и второй элементы ИЛИ, элемент задержки, элемент запрета, счетчик, первый регистр, первый и второй коммутаторы, первый дешифратор, элемент И, блок триггеров, блок элементов И и датчик интервалов времени, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, группа входов которого соединена с группой управляющих входов датчика интервалов времени и с группой выходов блока элементов И, первая группа входов которого соединена с группой выходов блока триггеров, группа входов установки в единицу которого соединена с первой группой выходов первого коммутатора, вторая группа выходов которого соединена с второй группой входов блока элементов И, группа информационных входов первого коммутатора соединена с группой выходов первого дешифратора, группа входов которого соединена с группой ВХОДО.В первого элемента ИЛИ, с группой информационных входов второго коммутатора, с группой информационных входов первого регистра и с группой адресных входов устройства, выход первого элемента ИЛИ соединен через элемент задержки с прямым входом элемента запрета, инверсный вход которого соединен с выходом первого элемента И и с управляющим входом второго коммутатора, группа выходов которого является группой адресных выходов устройства, выход элемента запрета соединен со счетным входом счетчика, выход переполнения которого соединен с входами установки в ноль блока триггеров, с входом разрешения записи первого регистра и с первым выходом управления обращением к памяти устройства, группа выходов первого регистра соединена с группой выходов индикации несанкционированной адресации устройства, вход установки в ноль счетчика соединен с установочным входом устройства, отличающееся тем, что, с целью расширения области применения за счет реализации возможности работы в Бычислительны) системах, функционирующих в мультипрограммном режиме, оно дополнительно содержит группу п элементов И, группу п счетчиков, § второй дешифратор, сумматор, схему сравнения и второй регистр, группа выходов ко(Л торого соединена с первой группой информационных входов схемы сравнения, вторая с: группа информационных входов которой соединена с группой выходов сумматора, & i-я (i 1,2,...,п) группа входов которого соеS динена соответственно с информационным выходом i-ro счетчика группы, счетный вход которого соединен соответственно с выходом i-ro элемента И группы, первый вход которого соединен соответственно с i-м выходом со второго дешифратора, вторые входы элеменю тов И группы соединены с выходом элемен ;о та запрета, выходы переполнения счетчиков группы соединены с выходами индикации неправильного обращения к памяти устройства, группа входов второго дешифратора соединена с первой группой информационных входов устройства, выход схемы сравнения соединен с вторым выходом управления обращением к памяти устройства, группа информационных входов второго регистра соединена с второй группой информационных входов устройства. 2. Устройство по п. 1, отличающееся тем, что датчик интервалов времени содержит элемент ИЛИ, шифратор, счетчик, генератор

Изобретение относится к вычисительной технике, в частности к запоминающим устройствам.

Известно устройство для защиты памяти,. содержа.щее адресные 1пипы, блок регистрации, дешифратор, ключевые элементы, триггеры, дополнительные элементы И, датчик интервалов времени, элемент И, элемент ИЛИ. С помощью данного устройства осуществляется .защита памяти. Для этого по соответствующим адресам производится предварительная установка триггеров. Проверка возможности допуска программы осуществл яется сравнением требуемого и разрешенного адреса с помощью элементов И. Если программа допущена к памяти, то производится выдача сигнала в блок регистрации адреса, в результате код адреса поступает на выход устройства 1.

Недостатком данного устройства является низкая надежность защиты памяти.

Известно также устройство для защиты памяти, содержащее блок оперативной памяти, первый регистр числа, регистр ключевой информации, группы элементов И, блок контроля, второй регистр числа, блок управления, сумматор по модулю два, управляющий и информационный входы. В этом устройстве осуществляется запоминание ключей. При обращении к памяти осуществляегся сравнение ключевой информации и в случае ее идентичности выдается сигнал, разрешающий прохождение считанного кода на выход устройства 2.

Недостатком этого устройства явяется низкая надежность защиты.

Наиболее близким к предлагаемому явяется устройство для защиты памяти, со держащее блок регистрации адреса, дещифратор, ключевые элементы, триггеры, дополнительные элементы И, датчик интервалов времени, элемент И, элемент ИЛИ, адресные щины, элемент задержки, эемент И-НЕ, счетчик. Эементы известного устройства соединены следующим образом. Вход элемента задержки подключен к адресным шинам, а выход - к первому входу элемента И-НЕ, второй вход которого соединен с выходом элемента И, а выход - с входом счетчика, выход которого подключен к одному из входов

блока регистрации адреса и к одному из входов триггеров, выходы которых соединены с входами дополнительных элементов И, выходы которых соединены с входами датчика интервалов времени и входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом датчика интервалов времени, адресные шины соединены с первой группой входов дешифратора, выходы которого соединены с входами ключевых элементов, первые выходы-которых соединены с первыми входами триггеров, а вторые выходы соединены с входами дополнительных элементов И, выход элемента И соединен с вторым входом элемента И-НЕ и с третьим входом блока регистрации адреса. Известное устройство работает следующим образом. Вначале производится установка триггеров, для чего на адресные шины подаются коды адресов ячеек памяти, до0 ступных данной программе. При этом на соответствующих выходах дешифратора появляются сигналы, которые через ключевые элементы устанавливают соответствующие триггеры в единичное состояние, подготавливая тем самым срабатывание элементов И. Триггеры в единичном состоянии определяют допуск к соответствующим ячейкам памяти. Кодовый адрес запрашиваемой ячейки поступает в блок регистрации адреса и дешифратор. На соответствующем выходе де0 шифратора появляется сигнал, который через один из выходов ключевых элементов поступает на вход соответствующего элемента И. Если к запрашиваемой ячейке памяти разрешен допуск, то на вход этого элемента И подается сигнал с триггера. Элемент

5 И срабатывает и через элемент ИЛИ открывает элемент И, а также запускает датчик интервалов времени, который формирует временной интервал, в течение которого разрешается допуск к запрашиваемой ячейке памяти. Этот сигнал через открытый эле мент И .поступает в блок фиксации адреса, который выдает сигнал разрешения допуска. Одновременно с подачей кодового адреса на дешифратор он поступает на элемент задержки, выходной сигнал которого подается на вход элемента И-НЕ по истечении времени, величина которого определяется суммой времени срабатывания дешифратора, ключевых элементов, дополнительных элементов И, элемента ИЛИ, элемента И.

В случае обращения к закрытым ячейкам памяти сигнал на выходе элемента И не вырабатывается, т. е. на выходе элемента И-НЕ находится единичный сигнал, включающий счетчик, который построен таким образом, что выходной сигнал появляется только при достижении определенного числа обращений к защищаемым ячейкам памяти. Этот сигнал поступает в блок регистрации адреса и на триггеры, которые блокируют последующие обращения к ячейкам памяти. Для дальнейщего выполнения программы оператору ЭВМ необходимо принимать специальные решения 3.

Известное устройство позволяет производить защиту.ячеек памяти путем предварительной установки триггеров, каждый из которых соответствует защищаемой ячейке памяти.

При работе вычислительной системы в мультипрограммном режиме, реализованном, например, в виде разделения времени, такая установка триггеров должна производиться всякий раз, когда программа получает доступ к процессору на определенное количество квантов времени. Одновременно счетчик числа неправильных обращений должен обнуляться, чтобы исключить возможность ерабатывания защиты за счет накопления информации о сбоях при работе других программ. Любая программа может исключить срабатывание системы защиты за счет распределения обращений по различным квантам времени при условии непревыщения в каждом кванте порогового числа неправильных обращений, при котором происходит срабатывание системы защиты. При этом имеется возможность лбжного срабатывания устройства, в результате которого программа сможет обратитьсяк закрытой для нее области памяти.

Таким образом, недостатком известного устройства является отсутствие возможности работы в вычислительных системах, функционирующих в мультипрограммном режиме.

Цель изобретения - расширение области применения за счет реализации возможности работы в вычислительных системах, функционирующих в мультипрограммном режиме.

Поставленная цель достигается тем, что в адаптивное устройство для защиты памяти, содержащее первый и второй эементыИЛИ, элемент задержки, элемент запрета, счетчик, первый регистр, первый и второй коммутаторы, первый дешифратор, элемент И, блок триггеров, блок элементов И и датчик интервалов времени, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом

второго элемента-ИЛИ, группа входов которого соединена с группой управляющих входов датчика интервалов времени и с группой выходов блока элементов И, первая группа входов которого соединена с группой выходов блока триггеров, группа входов установки в единицу которого соединена с первой группой выходов первого коммутатора, вторая группа выходов которого соединена с второй группой входов блока элементов И, группа информационных входов первого коммутатора соединена с группой выходов первого дещифратора, группа входов которого соединена с группой входов первого элемента ИЛИ, с группой информационных входов второго коммутатора, с группой информационных входов первого регистра и е группой адресных входов устройства, выход первого элемента ИЛИ соединен через элемент задержки с прямым входом элемента запрета, инверсный вход которого соединен с выходом первого элемента И и с управляющим входом второго коммутатора, группа выходов которого является группой адресных выходов устройства, выход элемента запрета соединен со счетным входом счетчика, выход переполнения котЬрого соединен с входами установки в ноль блока триггеров, с входом разрешения записи первого регистра и с первым выходом управления обращением к памяти устройства, группа выходов первого регистра соединена с группой выходов индикации несанкционированной адресации устройства, вход установки в ноль счетчика соединен с установочным входом устройства, введены группа п элементов И, группа п счетчиков, второй дешифратор, сумматор, схема сравнения и второй регистр, группа выходов которого соединена с первой группой информационных входов схемы сравнения, вторая группа информационных входов которой соединена с группой выходов сумматора, i -я (i l, 2, ...,п) группа входов которого соединена соответственно с информационным выходом i -го счетчика группы, счетный вход которого соединен соответственно с выходом i -го элемента И группы, первый вход которого соединен соответственно с 1 -м выходом второго дещифратора, вторые входы элементов И группы соединены с выходом элемента запрета, выходы переполнения счетчиков группы соединены с выходами индикации неправильного обращения к памяти устройства, группа входов второго дещифратора соединена с первой группой информационных входов устройства, выход схемы сравнения соединен с вторым выходом управления обращением к памяти устройства, группа информационных входов второго регистра соединена с второй группой информационных входов устройства.

Кроме того, датчик интервалов времени содержит элемент ИЛИ, шифратор, счетчик, генератор импульсов, элемент И и тригrep, вход установки в единицу которого подключен к выходу элемента ИЛИ, группа входов которого соединена с группой управляющих входов датчика и с группой входов шифратора,, группа выходов которого соединена с группой информационных входов счетчика, счетный вход которого соединен с выходом элемента И, первый вход которого соединен с выходом генератора импульсов, выход переполнения счетчика соединен с входом установки в ноль триггера, выход которого соединен с выходом датчика и с вторым входом элемента И.

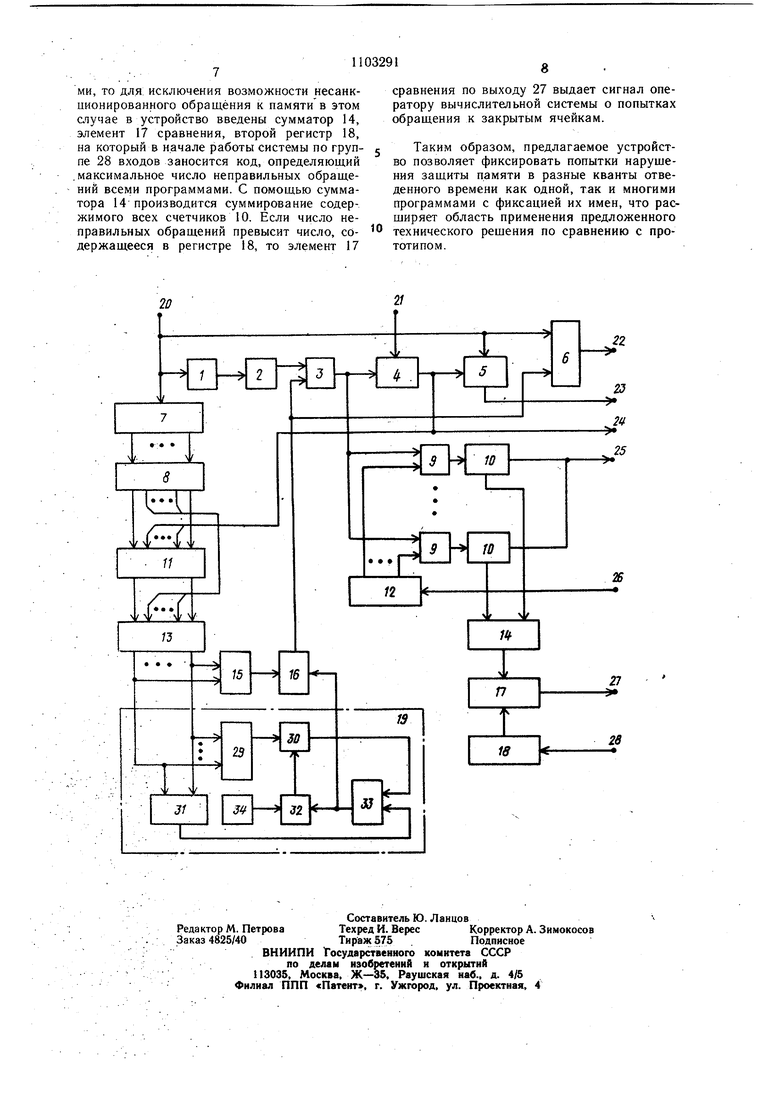

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит первый элемент ИЛИ 1, элемент 2 задержки, элемент 3 запрета, счетчик 4, первый регистр 5, второй коммутатор 6, первый дешифратор 7, первый коммутатор 8, группу 9 элементов И, группу 10 счетчиков, блок 11 триггеров, второй дешифратор 12, блок 13 элементов И, сумматор 14, второй элемент ИЛИ 15, элемент И 16, схему 17 сравнения, второй регистр 18, датчик 19 интервалов времени, группу 20 адресных входов, установочный вход 21, группу 22 адресных выходов, группу 23 выходов индикации несанкционированной адресаций, первый выход 24 управления обращением к памяти, выходы 25 индикации неправильного обращения к памяти, первая группа 26 информационных входов, второй выход 27 управления обращением к памяти, вторая группа 28 информационных входов, шифратор 29, счетчик 30, элемент ИЛИ 31, элемент И 32, триггер 33, генератор 34 импульсов.

Предлагаемое устройство работает следующим образом.

Перед выполнением программ производится установка в нулевое состояние всех счетчиков и триггеров. Входы обнуления не показаны. После этого производится установка блока II триггеров, для чего по группе 20 входов устройства подаются коды адресов ячеек памяти,, доступных данной программе. При этом на соответствующих выходах дешифратора появляются сигналы, которые через коммутатор 8 устанавливают соответствующие триггеры 11 в единичное состояние, подготавливая тем самым срабатывание элементов И 13. Триггеры 11 в единичном состоянии определяют допуск к соответствующим ячейкам памяти.

Кодовый адрес запращиваемой ячейки поступает на информационный вход коммутатора 6 и на дешифратор 7. На соответствующем выходе дешифратора 7 появляется сигнал, который через один из выходов коммутатора 8 поступает на вход соответствующего элемента И 13. Если к запрашиваемой ячейке памяти разрешен допуск, то на вход этого элемента И 13 подается разрешающий сигнал с соответствующего триггера 11. Один из элементов И 13 срабатывает и через элемент ИЛИ 15, открывает элемент И 16, а также запускает датчик 19 интервалов времени, который формирует временной интервал, в течение которого разрешается допуск к запрашиваемой ячейке памяти. Этот сигнал через открытий элемент И 16 поступает на вторые входы второго коммутатора 6 и разрешает выдачу адреса по группе 22 выходов устройства.

Одновременно с подачей адреса на пер0 вый дешифратор 7 этот адрес поступает на элемент ИЛИ I, с выхода которого через элемент 2 задержки, по истечении времени, величина которого определяется суммой времени срабатывания дешифратора 7, коммутатора 8, блока элементов И 13, элемента ИЛИ 15, элемента И 16, поступает на вход элемента 3 запрета.

В случае обращения к закрытым ячейкам памяти сигнал на вход элемента 3 запрета с выхода первого 16 элемента И не

0 подается, т. е. на счетный вход счетчика 4 поступит сигнал, увеличивающий код счетчика на единицу. Счетчик 4 построен таким образом, что выходной сигнал появляется только при достижении определенного, предельного числа неправильных обращений

к закрытым ячейкам памяти (для данной программы). Этот сигнал поступает на сброс триггеров 11 на вход разрешения записи первого регистра 5, в который записывается адрес, по которому было неправильное

- обращение. Установленные в ноль триггеры .11 блокируют последующие обращения к памяти. Одновременно по выходу 24 выдается сигнал оператору.

В случае, если программа, имя которой поступает по группе 26 входов устройства,

5 пытается обращаться к закрытой памяти в разные моменты времени, причем число неправильных обращений не превышает порога срабатывания счетчика 4, то устройство работает следующим образом.

При поступлении имени выполняемой

0 в данный момент программы на вход второго 12 дешифратора, на одном из его выходов выработается сигнал, который поступит на:второй вход одного из элементов И 9. При любом неправильном обрашении в счетчик, соответствующий имени программы, будет прибавляться единица при каждом неправильном обращении к памяти, для этого с выхода элемента 3 запрета на первые входы 9 группы элементов И подается сигнал о неправильном обращении к памяти.

0 При прёвыщении определенного числа неправильных обращений один из счетчиков выработает сигнал, который по группе 25 выходов поступит на выход устройства для сообщения оператору о попытках обращения к закрытым для данной программы ячей5 кам памяти. Номер счетчика однозначно определяет имя программы - нарушителя. Если пользователь пытается использовать несколько программ с разными именами, то для: исключения возможности несанкционированного обращения к памяти в этом случае в устройство введены сумматор 14, элемент 17 сравнения, второй регистр 18, на который в начале работы системы по группе 28 входов заносится код, определяющий .максимальное число неправильных обращений всеми программами. С помощью сумматора 14 производится суммирование содержимого всех счетчиков 10. Если число неправильных обращений превысит число, содержащееся в регистре 18, то элемент 17

20 сравнения по выходу 27 выдает сигнал оператору вычислительной системы о попытках обращения к закрытым ячейкам. Таким образом, предлагаемое устройство позволяет фиксировать попытки нарушения защиты памяти в разные кванты отведенного времени как одной, так и многими программами с фиксацией их имен, что расширяет область применения предложенного технического рещения по сравнению с прототипом.

| I | |||

| Авторское, свидетельство СССР № 574774, кл | |||

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-07-15—Публикация

1983-02-04—Подача