(21)4339131/21

(22)03.11.87

(46) 07.01.91. Бюл. № 1

(71)Украинский заочный политехнический институт им„ И. 3. Соколова

(72)В. А. Добрыдень

(53)621.374.4(088.8)

(56)Авторское свидетельство СССР 9 1018190, кл. Н 03 Н 19/10, 1982.

Авторское свидетельство СССР В 932002, кл. Н 03 К 23/00, 1980.

Авторское свидетельство СССР 1238194, кл. Н 03 В 19/00, 1984.

(54)УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

(57)Изобретение относится к импульсной технике и может быть использовано з системах автоматики и цифровой обработки информации. Цель изобретения - уменьшение быстродействия при

одновременном повышении точности умножения частоты. Устройство содержит входной формирователь 1, входную шину 2, формирователь 3 сигналов управ- декия, регистр 4 хранения, управляемый делитель 5 частоты, выходную шину 6, делитель 7 чзстоты5 генератор 8 опорной частоты, мультиплексор 9S де- мультигшексор 10, первый и второй счетчики 11 и 12 импульсов Управляемый делитель 5 частоты содержит формирователь 13 импульсов, компаратор 14 и счетчик 15 импульсов. Формирователь 3 сигналов управления содержит два триггера, три элемента И, элемент задержки, элемент разнозначности. Входной формирователь 1 содержит элемент И, элемент задержки, триггер, демультигатексор и блок синхронизации, 2 з.п. ф-ль;5 3 ил

е

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СЛЕДЯЩИЙ УМНОЖИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2042977C1 |

| Преобразователь серии импульсов в прямоугольный импульс | 1986 |

|

SU1422382A1 |

| КОРРЕЛЯЦИОННАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2007753C1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1631752A1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Умножитель частоты | 1988 |

|

SU1626315A1 |

| Статистический анализатор | 1986 |

|

SU1354211A1 |

| Умножитель частоты | 1989 |

|

SU1649538A1 |

| Умножитель частоты | 1983 |

|

SU1176439A1 |

д

ЈП

,&.

Изобретение пг к лнпулосло f янн к е н бы ь 1 Спол в системах автоматики и цифровой обработки информации „

Цель изобретения повышение быст родействия при одновременном повышении точности умножения частоты.

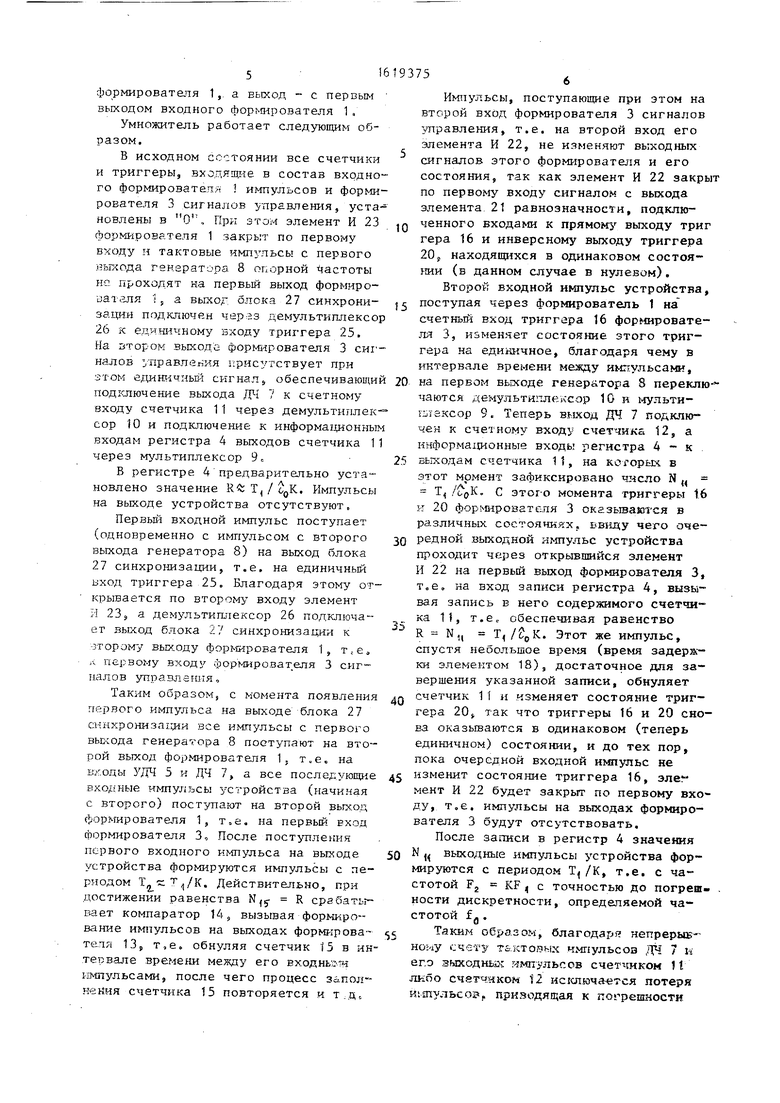

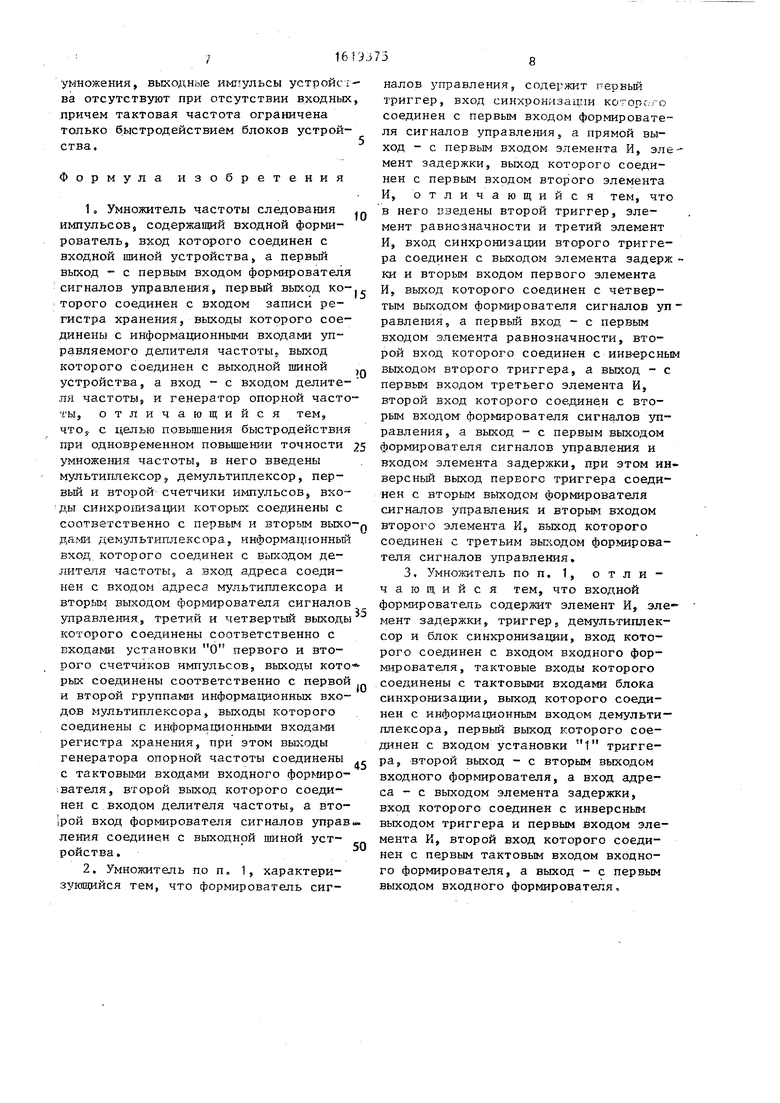

На фиг„ 1 лрепсгавлена структурная электрическая схема умножителя Ј на фиг, 2 и 3 - структурные электрически схемы соответственно формирователя сигналов управления и входного формирователя импульсов.

Умножитель содержит входной форми рователь 1, входную шину 2, формирователь 3 сигналов управленияз регистр 4 хранения, управляемый депитель 5 частоты (УДЧ), ви-одчую шин/ 6Э делитель 7 частоты (ДЧ)j генератор 8 опорной 4асготы мульшплексор 9, демультч - пексор 10 первый 11 п второй 12 гчегчики иинулъсов УДЧ 5 содержи1 июрмирователъ 13 импульсов, компарэ- р 14 и счетчик |5 импульсов , Фор- мирователь 3 сигналов управления содержит первый триггер 16, первый эле мент И 179 элемент 18 задержки, второй элемент И 19 второй триггер 20s злеаен-f 2 равнозначности, третий элемент И 22,

РХОДНОР формирователь 1 содержгп элемент И 23 элемент 4 чддержкк, триггер 25, демультиплексор 26, бло- 7 синхро шзаци

Б умножителе частот следования импульсой вход рггодного формирователя I соединен с вьоцлой шльой 2S a net- выи выход с первым входом формирователя 3 сигналов управления, первый выход котогсго соеялнен с входом записи пегтг-г ра 4 хранения, выходы которого соединены с информационными входами }1Ч 5, выход которого соепи- пен с выходной шчной 6 э а вход -с входом /И /о

Вхогты синчоонизацич первого 11 и второго 12 счетчиков импульсов соединены соответственно с первым и вторым выходами демультиплексоров 10S информационный вход которого соединен с выходом ДЧ 75 а вход адреса соединен с ЯУОДОМ адреса демультиплексора 9 ч Р выходом формирователя 3 сигна ,роч управления 9 третий и четвертый рыхочы которого соединены соответственно с входами установки О первого 1 1 и втор or-о 12 счетчиков импульсов , выходы которых соединены соот-,„

f.

fO }520 25JQ

о

55

встсгвенко с тервой и второй грукпэ- мз информационных входов мулыр тлек- сора 9} Вигходы когоро/о соедиг енг информационными входами регистра 4 хранения.

Выходы генератора 8 опорной чаете ты соединены с тактовыми входами г входного формирователя 1s второй выход которого соединен с входом УДЧ 59 а второй вход формирователя 3 сигналов управления соединен с выходной шиной 6.

В формирователе 3 сигналов управления вход синхронизации первого триг гера 16 соединен с первым входом формирователя 3 сигналов управления, а прямой выход - с первьш входом первого элемента И 17,. Выход элемента 18 задержки соединен с лервчпч входом вто рого элемента И 19„ Вход синхронизации второго триггера 20 соединен с выходом элемента 18 задержки и вторым входом первого элемента И 179 выход которого соединен с четвертым выходом формирователя 3 сигнапов управления, а первый вход - с первым входом элемента 21 равнозначности9 второй вход которого соединен с инверсным выходом второго ригтера 20, а выход - с первьш входом третьего элемента И 22, вюрой вход которого соединен с вторым входом Формирователя 3 сигналов управления., а выход - с первым выходом Формирователя 3 сигналов управле-0 ния н входом эаемента 18 задержки.

Инверсный выход первого триггера 16 соединен с вторым выходов формирователя 3 сигналов управления и вторым входом второго элемента II 19, выход которого соединен с третьим выхо- цом формирователя 3 сигналов управления, I

Вход блока 27 синхронизации соединен с входом входного формирователя 1, тактовые входы которого соединены с тактовыми входами блока 27 синхронизации э выход которого соединен с информационным входом демультиплексора 269 первый выход которого соединен с входом установки триггера 25,второй выход - с вторым выходом входного формирователя 19 а вход адреса - с выходом элемента 24 задержки, вход которого соединен с прямым выходом триггера 25 и первым входом элемента И 23, второй вход которого соединен с первым тактовым входом входного

формирователя 1, а выход - с первым выходом входного формирователя 1,

Умножитель работает следующим об- оазом.

В исходном сгстоянии все счетчики и триггеры, входящие в состав входного формироватет/- импульсов и форми- роватетя 3 сигналив управления, установлены в О1 , При атол элемент И 23 гЬормисоватепя 1 закрыт по первому входу ч тактовые импуаьсы с первого выхода генератора 8 опорной частоты н° проходят на первый выход формчро- аггля , з. выход опека 27 синхронизации подключен демультиплексор 1Ь л e.j.1 чичному зходу триггера 25. На второе выход., формирователя 3 сш- ;правпепкя iрисугствует при irом единичный сигнал,, обеспечивающий подключение выхода ДЧ , к счетному входу счетчика 11 через демультиплек сор 10 и подключение к информационным входам регистра 4 выходов счетчика 11 через мультиплексор 9„

Б регистре 4 предварительно установлено значение RЈ Т, / Ј0К. Импульсы на выходе устройства отсутствуют.

Первый входной импульс поступает (одновременно с импульсом с второго выхода генератора 8) на выход блока 27 синхронизации, т.е. на единичный ьход триггера 25. Благодаря этому ог- крывается по второму входу элемент Л 23, а демультиплексор 26 подключает выход бюка t.} синхронизации к горому выходу формирователя 1, т е„ ucjвому входу рормирователя 3 сигналов управления.

Таким образом, с момента появления ч рвого импульса на выходе блока 27 синхронизации все импульсы с первого БЫХОДЗ генератора 8 поступают на второй выход формирователя 1; т.е. на в/оды УДЧ 5 и ДЧ 7, а все последующие входные импульсы устройства (начиная с второго) поступают на второй выход формирователя 1, т.е. на первый вход Формирователя 3, После поступления первого входного импульса на выходе ус тройства формируются импульсы с периодом . Действительно, при достижении равенства R срабатывает компаратор 14, вызывая формирование импульсов на выходах формирователя 13„ т,е, обнуляя счетчик 15 в ин- теп вале времени между его входнь: ч кмпульсами, после чего процесс Заполнения счетчика 15 повторяется и т д..

Импульсы, поступающие при этом на второй вход формирователя 3 сигналов управления, т.е. на второй вход его элемента И 22, не изменяют выходных сигналов этого формирователя и его состояния, так как элемент И 22 закрыт по первому входу сигналом с выхода элемента 21 равнозначности, подключенного входами к пряному выходу триг гера 16 и инверсному выходу триггера 20, находящихся в одинаковом состоянии (в данном случае в нулевом).

Второй входной импульс устройства,

поступая через формирователь 1 на

счетный вход триггера 16 формирователя 3, изменяет состояние этого триггера на единичное, благодаря чему в интервале времени между импульсами,

0 на первом выходе генератора 8 переклю- - чаются демультиплексор 10 и мульти- Глгксор 9« Теперь выход ДЧ 7 подключен к счет ному вход} счетчика 12, а информационные входы регистра 4 - к

выходам счетчика 11, на которых в

этот момент зафиксировано число N н Т, /С0К. С этого момента триггеры 16 20 формирователя 3 оказываются в различных состояниях, ьвнд,у чего оче0 редкой выходной импульс устройства проходит через открывшийся элемент И 22 на первый выход формирователя 3, т.е. на вход записи регистра 4, вызывая запись в него содержимого счетчика 11, т.е. обеспечивая равенство

2 R - N,, Т4/Ј0К. Этот же импульс, спустя небольшое время (время задержки элементом 18), достаточное для завершения указанной записи, обнуляет

счетчик 1I и изменяет состояние триггера 20$ так что триггеры 16 и 20 снова оказываются в одинаковом (теперь единичном) состоянии, и до тех пор, пока очередной входной импульс не

изменит состояние триггера 16, эле мент И 22 будет закрыт по первому входу, т.е. импульсы на выходах формирователя 3 будут отсутствовать.

После записи в регистр 4 значения

к выходные импульсы устройства формируются с периодом /К, т.е. с частотой F2 KF 4 с точностью до погрешности дискретности, определяемой частотой f fl .

Таким образом, благодаря непрерывному 1.ЧС13 т&ктоянх импульсов ДЧ 7 ь его зыходньх мпульеев счетчиком 1 льбо счетчиком }2 исключается потеря и;тульеop. пркзодящая к погрешности

умножения, выходите имгульсы устройства отсутствуют при отсутствии входных, причем тактовая частота ограничена только быстродействием блоков устройства.

Формула изобретения

1, Умножитель частоты следования

1

импульсов, содержащий входной формирователь, вход которого соединен с входной шиной устройства, а первый выход - с первым входом формирователя сигналов управления, первый выход ко-, торого соединен с входом записи регистра хранения, выходы которого соединены с информационными входами управляемого делителя частоты, выход которого соединен с выходной шиной устройства, а вход - с входом делите- ля частоты, и генератор опорной частоты, отличающийся тем, что5 с целью повышения быстродействия при одновременном повышении точности 2 умножения частоты, в него введены мультиплексор, демультиплексор, первый и второй счетчики импульсов, входы синхронизации которых соединены с соответственно с первым и вторым ВЫХОда ми декультиплексора, информационный вход которого соединен с выходом делителя частоты, а вход адреса соединен с входом адреса мультиплексора и вторым выходом формирователя сигналов управления, третий и четвертый выходы которого соединены соответственно с входами установки О первого и второго счетчиков импульсов, выходы кото рых соединены соответственно с первой л второй группами информационных входов мультиплексора, выходы которого соединены с информационными входами регистра хранения, при этом выходы

3

Ш

генератора опорной частоты соединены с тактовыми входами входного формирователя, второй выход которого соединен с входом делителя частоты, а второй вход формирователя сигналов управ ления соединен с выходной шиной устройства.

0

5 Q

5

5

0

налов управления, содержит гервый триггер, вход синхронлзадчи о соединен с первым входом формирователя сигналов управления, а прямой выход - с первым входом элемента И, элемент задержки, выход которого соединен с первым входом второго элемента И, отличающийся тем, что в него введены второй триггер, элемент равнозначности и третий элемент И, вход синхронизации второго триггера соединен с выходом элемента задерж - ки и вторым входом первого элемента И, выход которого соединен с четвертым выходом формирователя сигналов уп - равления, а первый вход - с первым входом элемента равнозначности, второй вход которого соединен с инверсным выходом второго триггера, а выход - с первым входом третьего элемента И, второй вход которого соединен с вторым входом формирователя сигналов управления, а выход - с первым выходом формирователя сигналов управления и входом элемента задержки, при этом инверсный выход первого триггера соединен с вторым выходом формирователя сигналов управления и вторым входом второго элемента И, выход которого соединен с третьим выходом формирователя сигналов управления.

3, Умножитель по п. 1, отличающийся тем, что входной формирователь содержит элемент И, элемент задержки, триггер, демультиплексор и блок синхронизации, вход которого соединен с входом входного формирователя, тактовые входы которого соединены с тактовыми входами блока синхронизации, выход которого соединен с информационным входом демульти - плексора, первый выход которого соединен с входом установки 1 триггера, второй выход - с вторым выходом входного формирователя, а вход адреса - с выходом элемента задержки, вход которого соединен с инверсным выходом триггера и первым входом элемента К, второй вход которого соединен с первым тактовым входом входного формирователя, а выход - с первым выходом входного формирователя,

Фиг. 2

Авторы

Даты

1991-01-07—Публикация

1987-11-03—Подача