(Л

с

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки частотных сигналов

Цель изобретения - расширение области применения путем обеспечения обработки входных сигналов произвольной формы и упрощение конструкции.

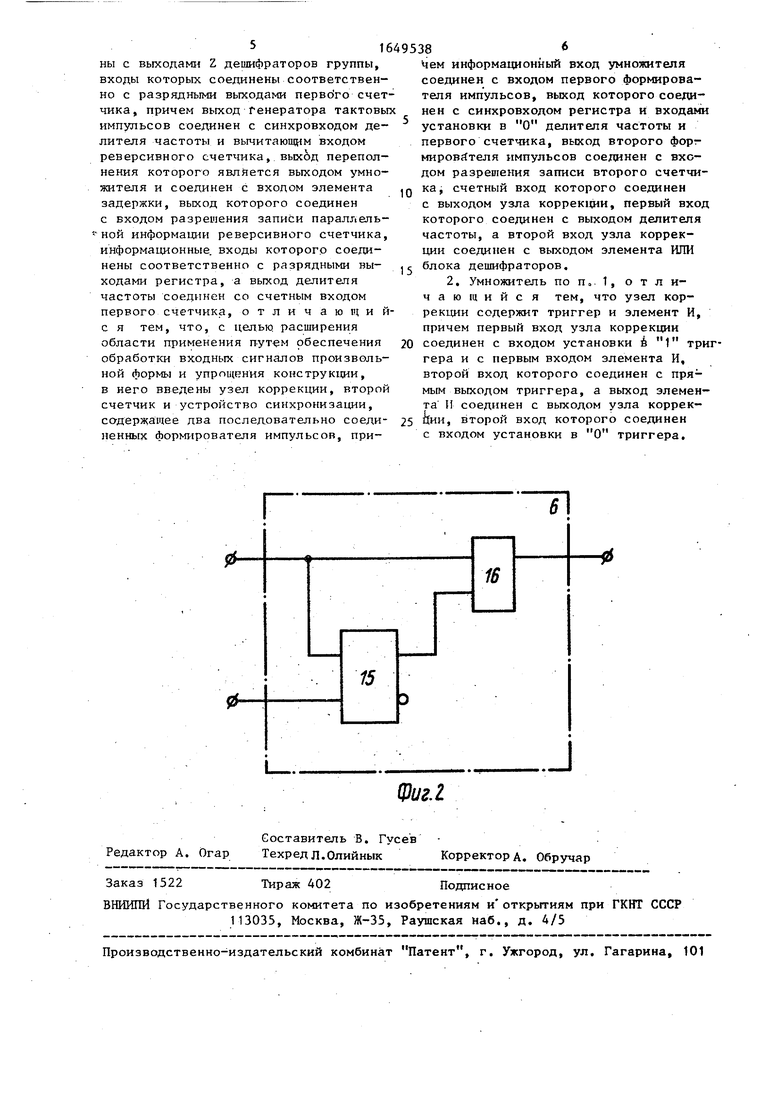

На фиг. 1 представлена функцио- нальиая схема умножителя частоты; на фиг. 2 - функциональная схема узла коррекции.

Умножитель частоты содержит генератор 1 тактовых импульсов, делитель 2 частоты, первый счетчик 3, регистр 4, второй счетчик 5, узел 6 коррекции, блок 7 дешифраторов, в который входят группа из Z дешифраторов 8 и элемент ИЛИ 9, устройство 10 син- хронизации, включающее первый и второй формирователи 11 и 12 импульсов, соединенные последовательно, реверсив ный счетчик 13 и элемент 14 задержки, соединенные между собой функционально

Узел 6 коррекции образует триггер 15 и элемент И 16, соединенные между собой функционально.

Умножитель частоты работает следующим образом.

Импульсы входной последовательности с частотой FX поступают на вход устройства 10 синхронизации, которое формирует два сдвинутых друг относительно друга импульса, что позволяет принимать входной сигнал произвольной формы. Первый управляющий сиг- , нал поступает на вход регистра 4, что обеспечивает передачу содержимого счетчика 5 в регистр 4. Кроме того, данный сигнал устанавливает делитель .2 частоты и счетчик 3 в О, подготавливая их к очередному циклу работы. Второй импульс с выхода устройства 10 синхронизации поступает на вход синхронизации счетчика 5 (импульсов). При этом в счетчик 5 (импульсов) записывается некоторый начальный код Nt, значение которого выбирается исходя из следующего. Поскольку период Т входного частотно-инпульс- ного сигнала связан с параметром измеряемой величины нелинейной зависимостью, то очевидно, что при максимальном значении параметра на входе умножителя устанавливается сиг- нал с периодом Ту Miwp (минимальный период реального сигнала), отличающимся от периода Ту мин ид идеального сиг

Q

0 5

5

нала, т.е. Тхд,ичр Тк МИ|( „ft. С учетом этого код N к определяется в виде

Nk (ухм«йр- м-1-тХМИЧиА Р0.н- ) (Т Алии.р ТХ Мпн мд) Таким образом, в счетчике 5 (импульсов) в течение интервала времени, равного т; ДАИМ Формируется код Мтмин Тх MWttx

+ N.. Здесь и далее рассматриваем работу устройства применительно к решению задачи линеаризации функций, имеющих выпуклый характер, т.е. вторая производная которых меньше нуля (f(p) : 0) . Для функций, имеющих вторую производную больше нуля, ffl(p) 0 (вогнутых функций), в счетчик 5 (импульсов) дрлжен заноситься код NK, т.е. обратный код.

Ч течение интервала времени, рав- нс Т, в счетчике 3 (импульсов) фо фуется код Nr FO M(, Содержимое счетчика 3 (импульсов) анализируется с помощью группы дешифраторов 8, входящих в блок 7 дешифраторов. Каждый из дешифраторов настроен на коды Nn; (i 1,2, ...), соответствующие границам участков аппроксимации. Импульсы, формируемые на выходах дешифраторов, проходят через элемент ИЛИ 9 на второй вход узла 6 коррекции. Узел 6 коррекции при этом исключает один импульс из последовательности импульсов с выхода делителя 2 частоты (для функций с второй производной f(р) 0).

Код Мт из счетчика 5 (импульсов) переписывается в регистр 4, содержимое которого периодически переписывается в реверсивный счетчик 13 (импульсов). На выходе реверсивного счетчика 13 ф ормируются импульсы с часто- той F F6/NTK F0(TX(ctr. F0)-

М/тхк M FKK , т.е. частота Fu, выходной последовательности пропорциональна откорректированной частоте импульсов входной последовательности.

Формула изобретения

1. Умножитель частоты, содержащий генератор тактовых импульсов, делитель частоты, первый счетчик, регистр, реверсивный счетчик, элемент задержки и блок дешифраторов, в который входят группы из Z дешифраторов и элемент ИЛИ, входы которого соедине-

ны с выходами Z дешифраторов группы, входы которых соединены соответственно с разрядными выходами перво го счетчика, причем выход генератора тактовых импульсов соединен с синхровходом делителя частоты и вычитающим входом реверсивного счетчика, выход переполнения которого является выходом умножителя и соединен с входом элемента задержки, выход которого соединен с входом разрешения записи параллельной информации реверсивного счетчика, информационные входы которого соединены соответственно с разрядными выходами регистра, а выход делителя частоты соединен со счетным входом первого счетчика, отличающий с я тем, что, с целью расширения области применения путем обеспечения обработки входных сигналов произвольной формы и упрощения конструкции, в него введены узел коррекции, второй счетчик и устройство синхронизации, содержащее два последовательно соединенных йормирователя импульсов, при

5

5

чем информационный вход умножителя соединен с входом первого формирователя импульсов, выход которого соединен с синхровходом регистра и входами установки в О делителя частоты и первого счетчика, выход второго фор- мирова теля импульсов соединен с входом разрешения записи второго счетчика, счетный вход которого соединен с выходом узла коррекции, первый вход которого соединен с выходом делителя частоты, а второй вход узла коррекции соединен с выходом элемента ИЛИ блока дешифраторов.

2. Умножитель по п, 1, отличающийся тем, что узел коррекции содержит триггер и элемент И, причем первый вход узла коррекции соединен с входом установки в 1 триггера и с первым входом элемента И, второй вход которого соединен с прямым выходом триггера, а выход элемента И соединен с выходом узла коррекции, второй вход которого соединен с входом установки в О триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для обработки первичной информации | 1984 |

|

SU1234851A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Измеритель переходных характеристик частотных прецизионных устройств | 1987 |

|

SU1620992A1 |

| Цифровой линейный экстраполятор | 1979 |

|

SU868769A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| Устройство для умножения частоты следования импульсов | 1986 |

|

SU1410027A1 |

Изобретение относится к вычислительной технике и монет быть использовано в устройствах обработки частотных сигналов. Цель изобретения - расширение области применения за счет обеспечения обработки входных сигналов произвольной формы и упрощение конструкции. Умножитель частоты содержит генератор 1 тактовых импульсов, делитель 2 частоты, первый счетчик 3, регистр 4, второй счетчик 5, узел 6 коррекции, блок 7 дешифраторов, в который входят группа из Z дешифраторов 8 и элемент ИЛИ 9, устройство 10 синхронизации, включающее в себя два последовательно соединенных формирователя 11, 12 импульсов, реверсивный счетчик 13 и элемент 14 задержки, соединенные между собой функционально. 1 ч.п.Л-лы, 2 ил. с 9

Г

16

.J

| Умножитель частоты | 1978 |

|

SU781832A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения частоты следования импульсов | 1986 |

|

SU1410027A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-15—Публикация

1989-03-09—Подача