Изобретение относится к вычислительной технике и может быть использовано при определении законов распределения случайных величин.

Целью изобретения является повышение точности определения закона распределения при малом числе измерений.

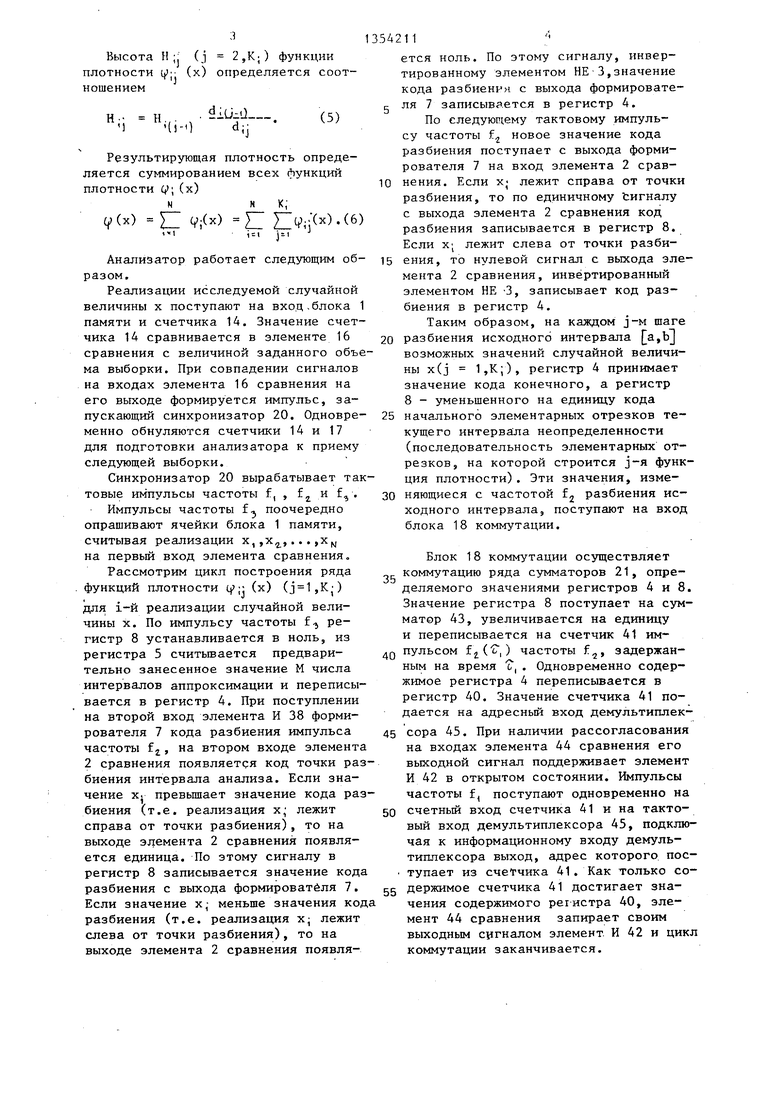

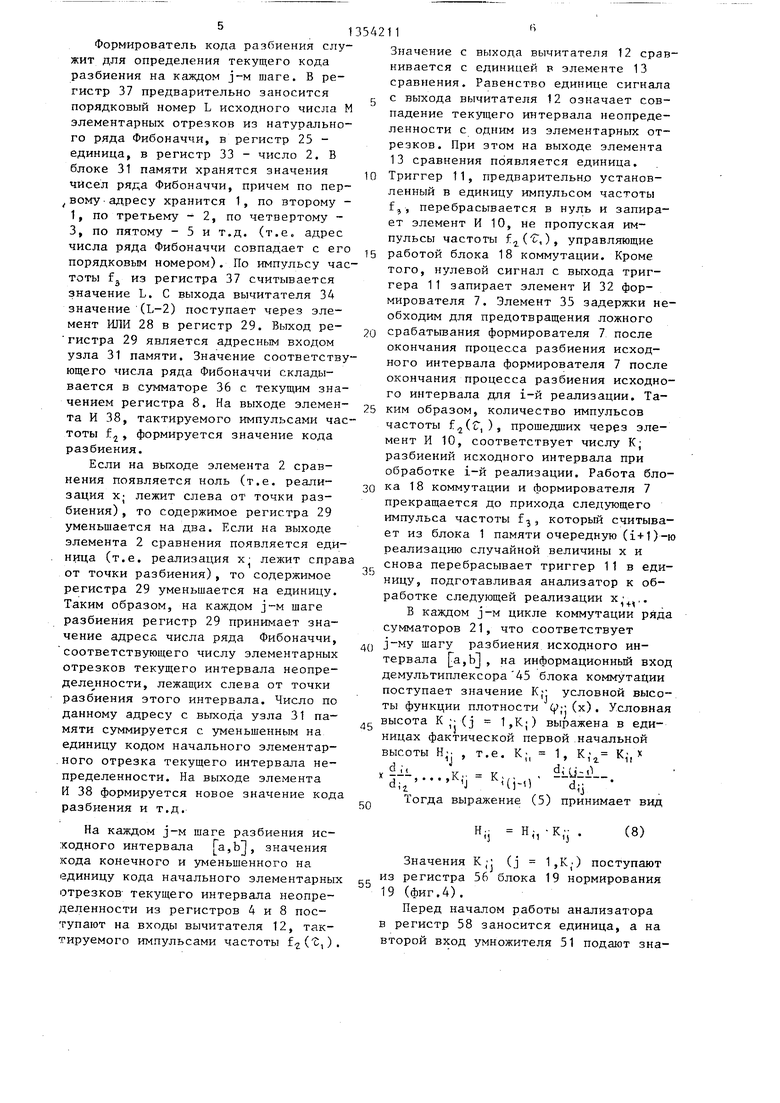

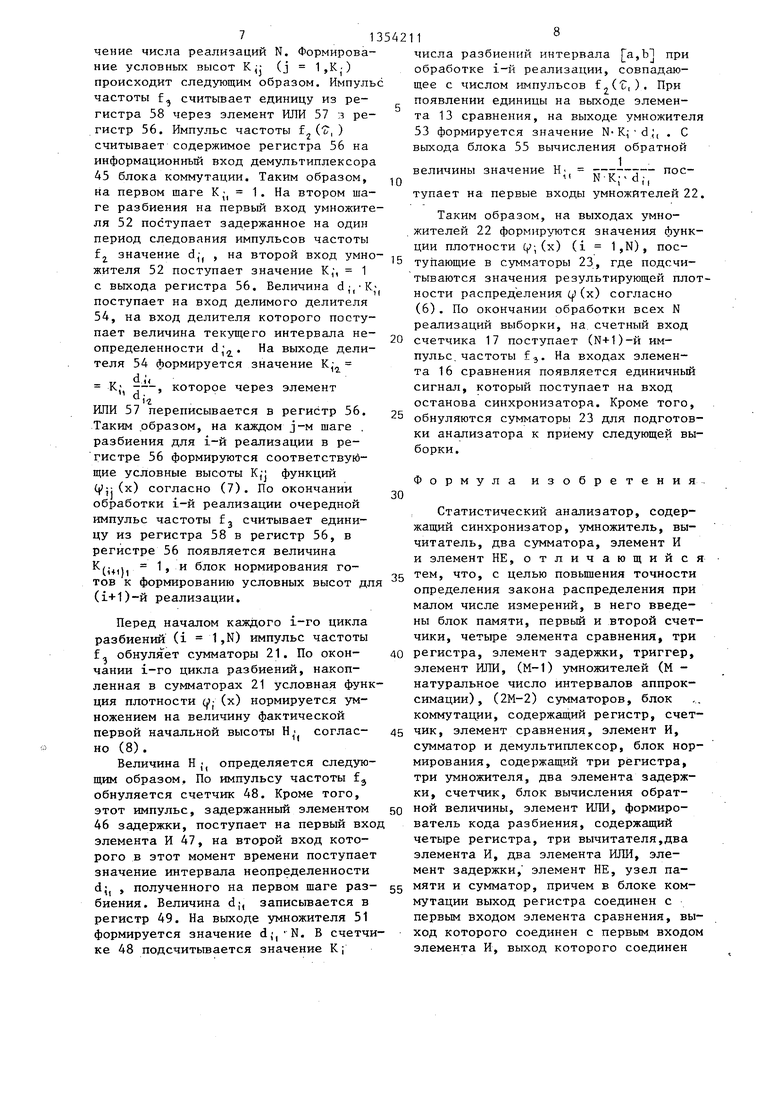

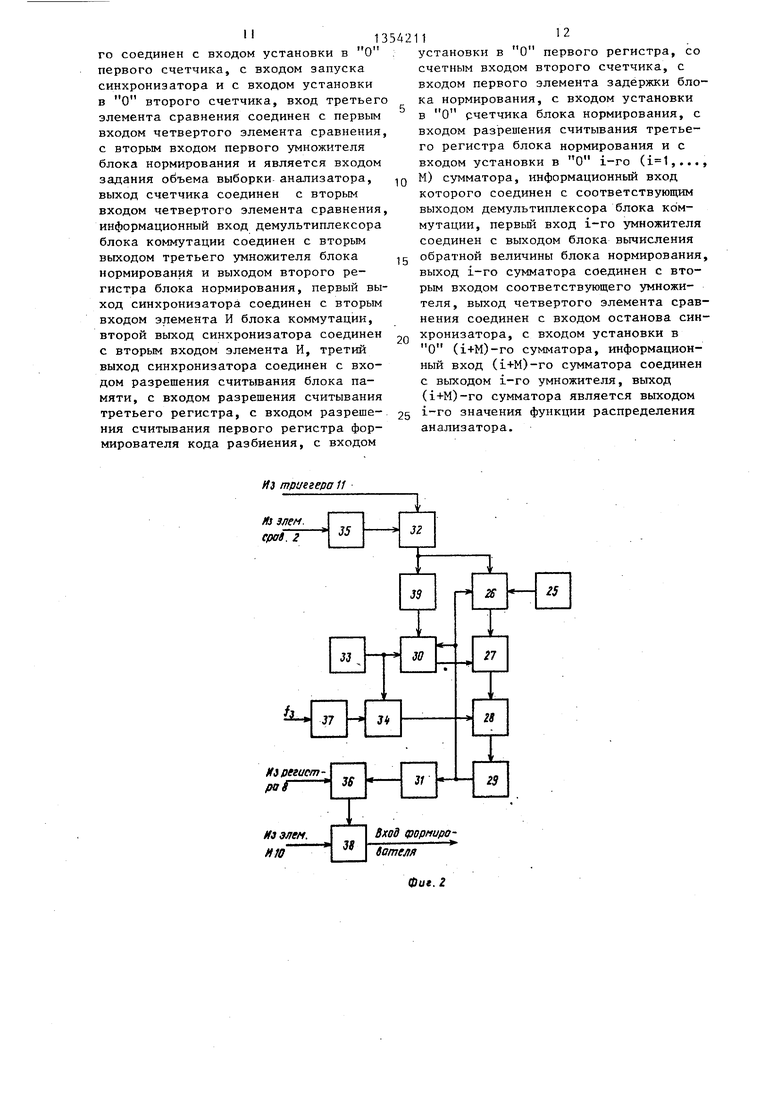

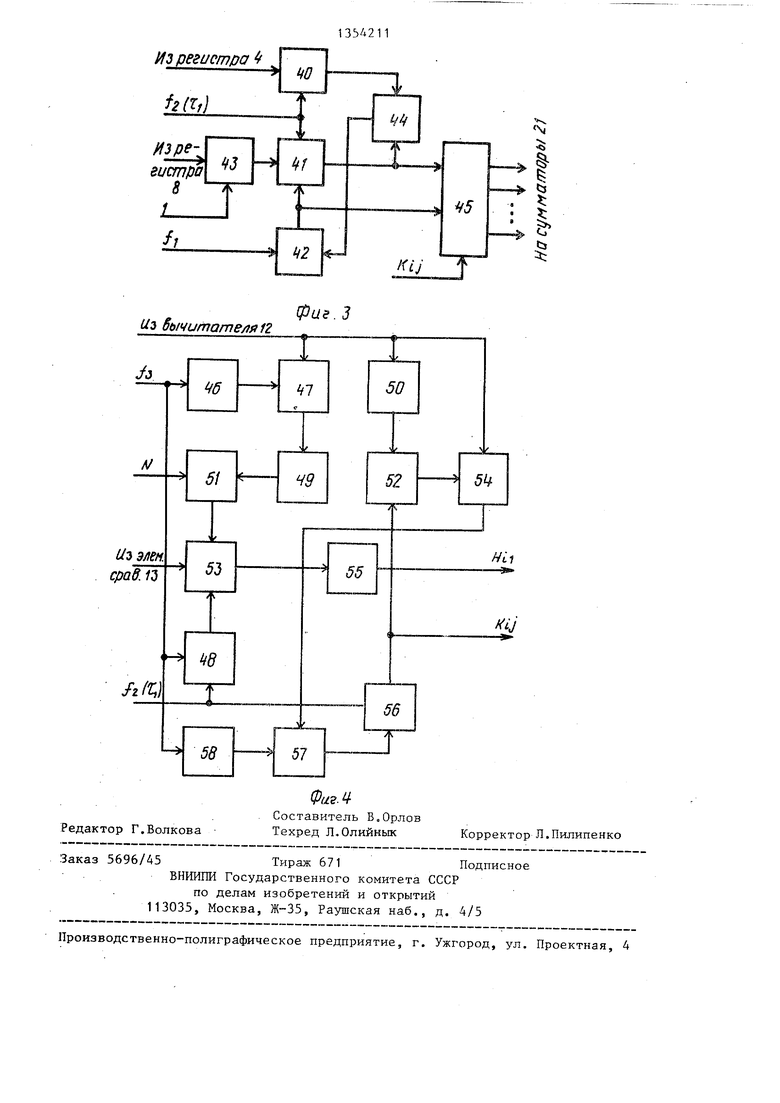

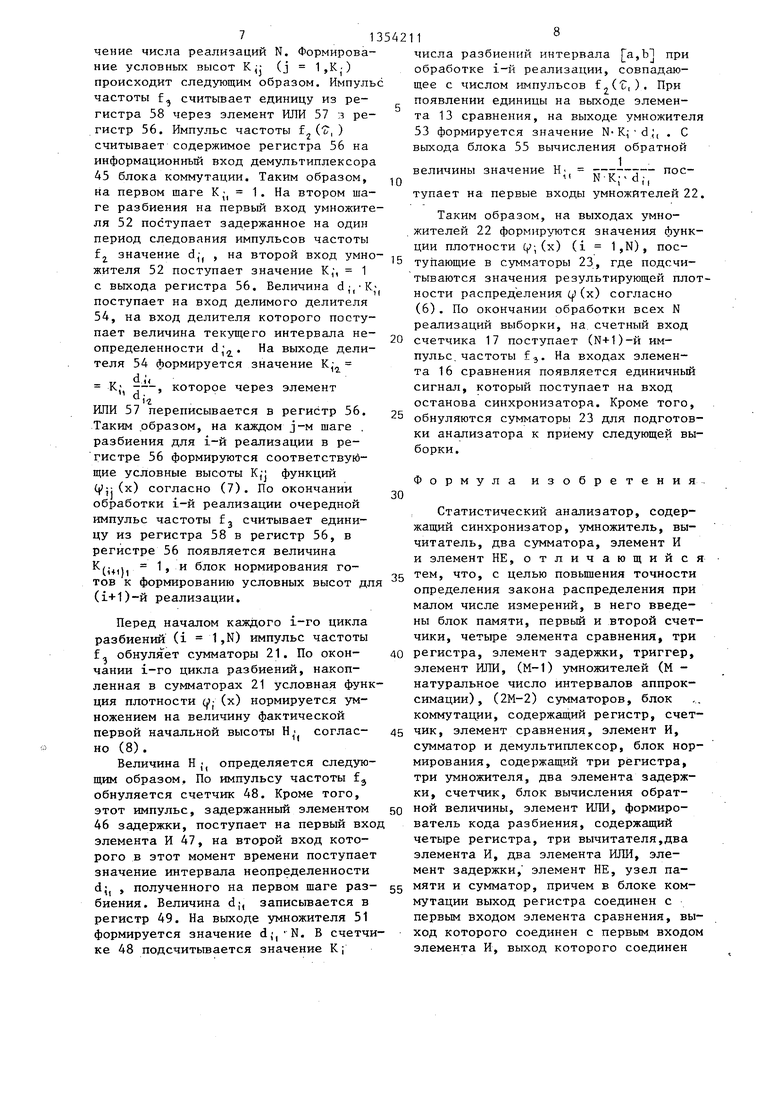

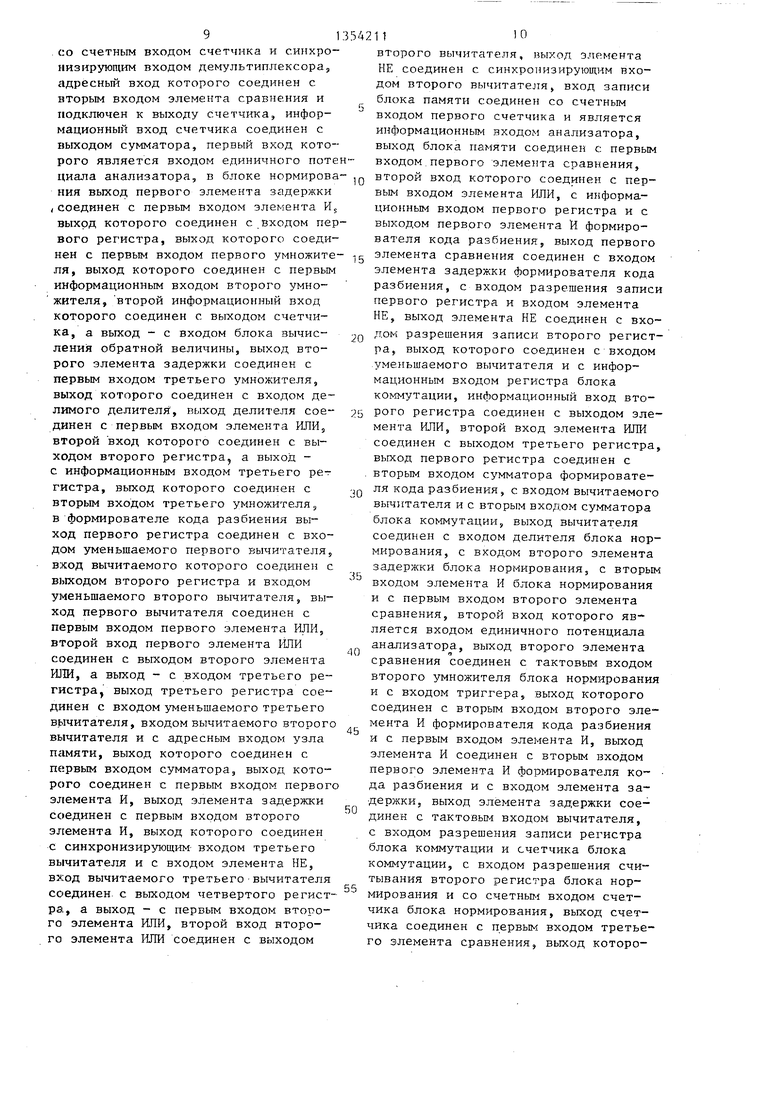

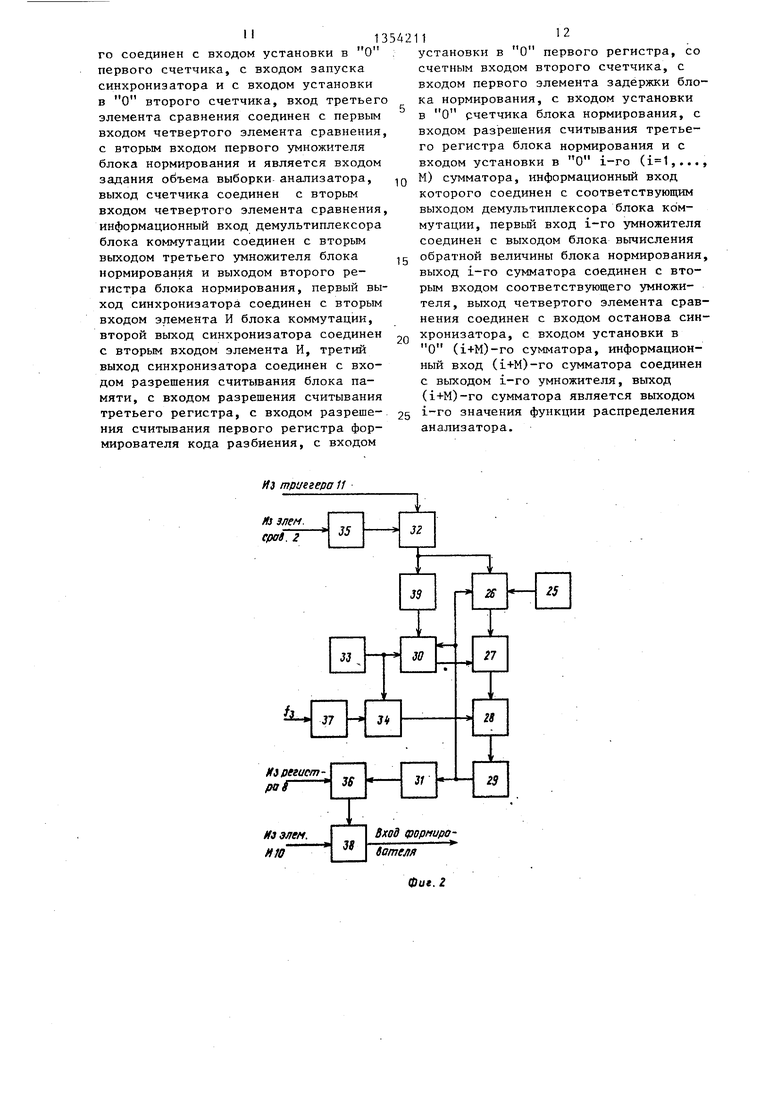

На фиг.1 приведена функциональная схема анализатора; на фиг.2 - функциональная схема формирователя кода разбиения; на фиг. 3 -функциональная схема блока коммутации; на фиг.4 - . функциональная схема блока нормирования.

Статистический анализатор (фиг.1) содержит блок 1 памяти, элемент 2 сравнения, элемент НЕ 3, регистры 4 и 5, элемент ИЛИ 6, формирователь 7 кода разбиения, регистр 8, элемент 9 задержки, элемент И 10, триггер 11, вычитатель 12, элемент 13 сравнения, счетчик 14, элементы 15 и 16 сравнения, счетчик 17, блок 18 коммутации, блок 19 нормирования, синхронизатор 20, М сумматоров 21, ,21 ,. . . ,21,, М умножителей 22 , ,22 ,... ,22, М сумматоров 23 ,,23 ,... ,23дд, группу выходов 24. Формирователь кода разбиения (фиг.2) содержит регистр 25, вычитатель 26, элементы ИЛИ 27 и 28, регистр 29, вычитатель 30, узел 31 памяти, элемент И 32, регистр 33, вычитатель 34, элемент 35 задержки, сумматор 36, регистр 37, элемент И 38, элемент НЕ 39. Блок коммутации (фиг.З) содержит регистр 40, счетчик 41, элемент И 42, сумматор 43, элемент 44 сравнения, демультиплексор 45. Блок нормирования (фиг„4) содержит элемент 46 задержки, элемент И 47, счётчик 48, регистр 49 j, элемент 50 задержки, умножители 51-53, делитель 54, блок 55 вычисления обратной величины, регистр 56, элемент ИЛИ 57 регистр 58.

Работа анализатора основана на следующих зависимостях. Функция плотности распределения имеет вид:

()(х) i О, при а X Ь; ((j(x) н О, при и ,

(1)

где а и b - границы интервала возмож- ных значений случайной величины X.

Для каждой реализации х- из выборки объема N строят ряд функций плотности (х) (J 1, К;), где количество разбиений исходного интервала а,Ь при обработке i-й реализа- ции. Исходный интервал а. ,ЬЗ предварительно разбивается на целое число М элементарных отрезков (интервалов аппроксимации), которое выбирается из натурального ряда чисел Фибоначчи: 1 2, 3, 5, 8, 13,... и т.д. При построении функций плотности используется следующее .свойство ряда Фибоначчи:

Ф Ф L Ьи

+ К

L-2

(2)

(Р где К - L-й член ряда Фибоначчи.

Работа анализатора основана на принципе асимметрии логики измерения.

Алгоритм построения при этом следующий. На первом шаге исходный интер-/

Ф

в ал, содержащий элементарных отрезков, разбивается на две части, причем левая часть содержит К.2 элементарных отрезков, а правая часть - К, элементарных отрезков. Часть, не содержащая реализации Xj, отбрасывается, а над оставшимся интервалом неопределенности строится функция плотности ф;, (х), представляющая собой плотность равномерного распределения

высотой Н

Полученный интервал

снова разбивается аналогичным образом, пустая часть отбрасывается, а над- оставшимся вкладом строится функция плотности ifi (х) высотой Н.;.

Процесс построения функции (j- (х) (J К;) для i-й реализации заканчивается при совпадении на очередном шаге величины текущего интервала неопределенности, содержащего реализацию X

1

и интервала аппроксима- Ь-а

ции, длина которого, равна П Функции плотности

(У;(х) . (3)

имеют одинаковый вес. Условие нормит ровки при этом выполняется соответствующим выбором высоты Hj, функции плотности ( , (.,N)

N K;- d;

(4)

где d(, - ширина интервала неопределенности для Xj , полученно1 о на первом шаге разбиения.

Высота Н ;: (j 2,К;) функции плотности ij)- (х) определяется соотношением

Н.. Н.,. .

) Ч1-0 d;j

(5)

Результирующая плотность определяется суммированием всех функций плотности V;(х)

N N к;

(fM V;(x) ф- (х).(6)

гм

Анализатор работает следующим об- разом.

Реализации исследуемой случайной величины X поступают на вход.блока 1 памяти и счетчика 14. Значение счетчика 14 сравнивается в элементе 16 сравнения с величиной заданного объема выборки. При совпадении сигналов на входах элемента 16 сравнения на его выходе формируется импульс, запускающий синхронизатор 20. Одновре- менно обнуляются счетчики 14 и 17 для подготовки анализатора к приему следующей выборки.

Синхронизатор 20 вырабатывает тактовые импульсы частоты f, , f и f.

Импульсы частоты f поочередно опрашивают ячейки блока 1 памяти, считывая реализации х,,х,...,х на первый вход элемента сравнения.

Рассмотрим цикл построения ряда функций плотности (х) (j 1,K )

J

для i-й реализации случайной величины X. По импульсу частоты f, регистр 8 устанавливается в ноль, из регистра 5 считьшается предвари- тельно занесенное значение М числа интервалов аппроксимации и переписывается в регистр 4. При поступлении на второй вход элемента И 38 формирователя 7 кода разбиения импульса частоты fг, на втором входе элемента 2 сравнения появляется код точки разбиения интервала анализа. Если значение X. превьшает значение кода разбиения (т.е. реализация х; лежит справа от точки разбиения), то на выходе элемента 2 сравнения появляется единица. По этому сигналу в регистр 8 записывается значение кода разбиения с выхода формирователя 7. Если значение х,- меньше значения код разбиения (т.е. реализация х- лежит слева от точки разбиения), то на выходе элемента 2 сравнения появля

5

5

0 5

о

0 5 0 g

ется ноль. По этому сигналу, инвертированному элементом НЕ 3,значение кода разбиения с выхода формирователя 7 записывается в регистр 4.

По следующему тактовому импульсу частоты f,j новое значение кода разбиения поступает с выхода формирователя 7 на вход элемента 2 сравнения. Если X; лежит справа от точки разбиения, то по единичному Ъигналу с выхода элемента 2 сравнения код разбиения записывается в регистр 8. Если X; лежит слева от точки разбиения, то нулевой сигнал с выхода элемента 2 сравнения, инвертированный элементом НЕ -3, записывает код разбиения в регистр 4.

Таким образом, на каждом j-м шаге разбиения исходного интервала а,Ь возможных значений случайной величины x(j 1,К;), регистр 4 принимает значение кода конечного, а регистр 8 - уменьшенного на единицу кода начального элементарных отрезков текущего интервала неопределенности (последовательность элементарных отрезков, на которой строится j-я функция плотности). Эти значения, изменяющиеся с частотой fj разбиения исходного интервала, поступают на вход блока 18 коммутации.

Блок 18 коммутации осуществляет коммутацию ряда сумматоров 21, определяемого значениями регистров 4 и 8. Значение регистра 8 поступает на сумматор 43, увеличивается на единицу и переписывается на счетчик 41 импульсом f( C ,) частоты f, задержанным на время сГ, . Одновременно содержимое регистра 4 переписывается в регистр 40. Значение счетчика 41 подается на адресный вход демультиплексора 45. При наличии рассогласования на входах элемента 44 сравнения его выходной сигнал поддерживает элемент И 42 в открытом состоянии. Импульсы частоты f, поступают одновременно на счетный вход счетчика 41 и на тактовый вход демультиплексора 45, подключая к информационному входу демультиплексора выход, адрес которого поступает из счетчика 41. Как только содержимое счетчика 41 достигает значения содержимого регистра 40, элемент 44 сравнения запирает своим выходным cv гнaлoм элемент. И 42 и цикл коммутации заканчивается.

Формирователь кода разбиения служит для определения текущего кода разбиения на каждом j-м шаге. В регистр 37 предварительно заносится порядковый номер L исходного числа М элементарных отрезков из натурального ряда Фибоначчи, в регистр 25 - единица, в регистр 33 - число 2. В блоке 31 памяти хранятся значения чисел ряда Фибоначчи, причем по пер вому-адресу хранится 1, по второму - 1, по третьему - 2, по четвертому - 3, по пятому - 5 и т.д. (т.е. адрес числа ряда Фибоначчи совпадает с его порядковым номером). По импульсу частоты fg из регистра 37 считывается значение L. С выхода вычитателя 34 значение (L-2) поступает через элемент ИЛИ 28 в регистр 29. Выход ре-

гистра 29 является адресным входом узла 31 памяти. Значение соответствующего числа ряда Фибоначчи складывается в сумматоре 36 с текущим значением регистра 8. На выходе элемен- та И 38, тактируемого импульсами частоты fj, формируется значение кода разбиения.

Если на выходе элемента 2 сравнения появляется ноль (т.е. реали- зация X; лежит слева от точки разбиения) , то содержимое регистра 29 уменьшается на два. Если на выходе элемента 2 сравнения появляется единица (т.е. реализация Х лежит справ от точки разбиения), то содержимое регистра 29 уменьшается на единицу. Таким образом, на каждом j-м шаге разбиения регистр 29 принимает значение адреса числа ряда Фибоначчи,

соответствующего числу элементарных отрезков текущего интервала неопре- деле нности, лежащих слева от точки разбиения этого интервала. Число по данному адресу с выхода узла 31 памяти суммируется с уменьшенным на единицу кодом начального элементар.него отрезка текущего интервала не- пределенности. На выходе элемента И 38 формируется новое значение кода разбиения и т.д.

На каждом j-м шаге разбиения исходного интервала а,Ь, значения кода конечного и уменьшенного на единицу кода начального элементарных отрезков- текущего интервала неопределенности из регистров 4 и 8 поступают на входы вычитателя 12, тактируемого импульсами частоты f( c:,).

Значение с выхода вычитателя 12 сравнивается с единицей Р элементе 13 сравнения. Равенство единице сигнала с выхода вычитателя 12 означает совпадение текущего интервала неопределенности с одним из элементарных отрезков. При этом на выходе элемента 13 сравнения появляется единица. Триггер 11, предварительна установленный в единицу импульсом частоты f, перебрасывается в нуль и запирает элемент И 10, Не пропуская импульсы частоты ( Г,), управляющие работой блока 18 коммутации. Кроме того, нулевой сигнал с выхода триггера 11 запирает элемент И 32 формирователя 7. Элемент 35 задержки необходим для предотвращения ложного срабатывания формирователя 7 после окончания процесса разбиения исходного интервала формирователя 7 после окончания процесса разбиения исходного интервала для i-й реализации. Таким образом, количество импульсов частоты f2(r, ), прошедших через элемент И 10, соответствует числу К; разбиений исходного интервала при обработке i-й реализации. Работа блока 18 коммутации и формирователя 7 прекращается до прихода следующего импульса частоты f, который считывает из блока 1 памяти очередную (i+1)-ю реализацию случайной величины х и снова перебрасывает триггер 11 в единицу, подготавливая анализатор к обработке следующей реализации х,,.

В каждом j-м цикле коммутации ряда сумматоров 21, что соответствует j-му шагу разбиения исходного интервала а,Ь, на информационный вход демультиплексора 45 блока коммутации поступает значение К;- условной высоты функции плотности ( - (х). Условная высота К ; (J - 1,К;) выражена в единицах фактической первой начальной высоты И- , т.е. К;, 1, К- К-, х

IL V - -к i.U-l dij Ui-O dij

Тогда выражение (5) принимает вид

Н;;

- Н;, -К(8)

Значения К;: (j 1,К;) поступают из регистра 56 блока 19 нормирования 19 (фиг.4).

Перед началом работы анализатора в регистр 58 заносится единица, а на второй вход умножителя 51 подают зна71

чение числа реализаций N. Формирование условных высот (J 1,К-) происходит следующим образом. Импуль частоты f считывает единицу из регистра 58 через элемент ИЛИ 57 з регистр 56. Импульс частоты (,) считывает содержимое регистра 56 на информационный вход демультиплексора 45 блока коммутации. Таким образом, на первом шаге К 1. На втором шаге разбиения на первый вход умножителя 52 поступает задержанное на один период следования импульсов частоты f значение d,-, , на второй вход умно жителя 52 поступает значение К;, 1 с выхода регистра 56. Величина d;, K поступает на вход делимого делителя 54, на вход делителя которого поступает величина текущего интервала не-

определенности d

12.

На выходе делителя 54 формируется значение К,-

К, --, которое через элемент

i-z ИЛИ 57 переписывается в регистр 56.

Таким образом, на каждом j-м шаге , разбиения для L-Й реализации в регистре 56 формируются соответствующие условные высоты Kjj функций (j);; (х) согласно (7) . По окончании обработки i-й реализации очередной импульс частоты fj считывает единицу из регистра 58 в регистр 56, в регистре 56 появляется величина (i+i)i 1 и блок нормирования готов к формированию условных высот дл (1+1)-й реализации.

Перед началом каждого 1-го цикла разбиений (i 1,N) импульс частоты f обнуляет сумматоры 21. По окон- чании i-ro цикла разбиений, накопленная в сумматорах 21 условная функция плотности ()jj (х) нормируется умножением на величину фактической первой начальной высоты Н соглас- но (8).

Величина Н( определяется следующим образом. По импульсу частоты fj обнуляется счетчик 48. Кроме того, этот импульс, задержанный элементом 46 задержки, поступает на первый вхо элемента И 47, на второй вход которого в этот момент времени поступает значение интервала неопределенности d;, , полученного на первом шаге раз- биения. Величина dj, записывается в регистр 49. На выходе умножителя 51 формируется значение d;, N. В счетчике 48 подсчитьтается значение К;

11

числа разбиений интервала а,Ь1 при обработке х-й реализации, совпадающее с числом импульсов fjC C, ). При появлении единицы на выходе элемента 13 сравнения, на выходе умножителя 53 формируется значение , . С выхода блока 55 вычисления обратной

величины значение Н :- пос N-Kpd;,

тупает на первые входы умножителей 22

Таким образом, на выходах умножителей 22 формируются значения функции плотности {у; (х) (1 1,N), пос- тупающие в сумматоры 23, где подсчитываются значения результирующей плотности распределения if (х) согласно (6). По окончании обработки всех N реализаций выборки, на счетный вход счетчика 17 поступает (Н+1)-й импульс, частоты fj. На входах элемента 16 сравнения появляется единичный сигнал, который поступает на вход останова синхронизатора. Кроме того, обнуляются сумматоры 23 для подготовки анализатора к приему следующей выборки.

Формула изобретения

Статистический анализатор, содержащий синхронизатор, умножитель, вы- читатель, два сумматора, элемент И и элемент НЕ, отличающийся тем, что, с целью повьшения точности определения закона распределения при малом числе измерений, в него введены блок памяти, первый и второй счетчики, четыре элемента сравнения, три регистра, элемент задержки, триггер, элемент ИЛИ, (М-1) умножителей (М - натуральное число интервалов аппроксимации) , (2М-2) сумматоров, блок коммутации, содержащий регистр, счетчик, элемент сравнения, элемент И, сумматор и демультиплексор, блок нормирования, содержащий три регистра, три умножителя, два элемента задержки, счетчик, блок вычисления обратной величины, элемент ИЛИ, формирователь кода разбиения, содержащий четыре регистра, три вычитателя,два элемента И, два элемента ИЛИ, элемент задержки, элемент НЕ, узел памяти и сумматор, причем в блоке коммутации выход регистра соединен с первым входом элемента сравнения, выход которого соединен с первым входом элемента И, выход которого соединен

c:o счетньш входом счетчика и синхронизирующим входом демультиплексора, адресный вход которого соединен с вторым входом элемента сравнения и подключен к выходу с.четчика, информационный вход счетчика соединен с выходом сумматора, первый вход которого является входом единичного потециала анализатора, в блоке нормирования выход первого элемента задержки /соединен с первым входом элемента Hj выход которого соединен с входом первого регистра, выход которого соединен с первым входом первого умножителя, выход которого соединен с первым информационным входом второго умножителя, второй информационный вход которого соединен с выходом счетчика, а выход - с входом блока вычисления обратной величины, выход второго элемента задержки соединен с первым входом третьего умножитешя, выход которого соединен с входом делимого делителя , выход делител51 соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго регистра, а выхоД - с информационным входом третьего регистра, выход которого соединен с вторым входом третьего умножителяj в формирователе кода разбиения выход первого регистра соединен с входом уменьшаемого первого вычитателя5 вход вычитаемого которого соединен с выходом второго регистра и входом уменьшаемого второго вычитателя, выход первого вычитателя соединен с первым входом первого элемента ИЛИ, второй вход первого элемента ИЛИ соединен с выходом второго элемента ИЛИ, а выход - с входом третьего регистра, выход третьего регистра соединен с входом уменьшаемого третьего вычитателя, входом вычитаемого второго вычитателя и с адресным входом узла Пс1мяти, выход которого соединен с первым входом сумматора, выход которого соединен с первым входом первог элемента И, выход элемента задержки соединен с первым входом второго элемента И, выход которого соединен с синхронизирующим- входом третьего вычитателя и с входом элемента НЕ, вход вычитаемого третьеговычитателя соединен, с выходом четвертого регистра, а выход - с первым входом второго элемента ИЛИ, второй вход второго элемента ИЛИ соединен с выходом

0

0

5

5

5

0

5

второго вычитателя, выход элемента НЕ соединен с синхронизирующим входом второго вычитателя, вход записи блока памяти соединен со счетным входом первого счетчика и является информационным входом анализатора, выход блока памяти соединен с первым входом,первого элемента сравнения, второй вход которого соединен с первым входом элемента ИЛИ, с информационным входом первого регистра и с выходом первого элемента И формирователя кода разбиения, выход первого элемента сравнения соединен с входом элемента задержки формирователя кода разбиения, с входом разрешения записи первого регистра и входом элемента НЕ, выход элемента НЕ соединен с входом разрешения записи второго регистра, выход которого соединен с входом .уменьшаемого вычитателя и с информационным входом регистра блока коммутации, информационный вход второго регистра соединен с выходом элемента ИЛИ, второй вход элемента ИЛИ соединен с выходом третьего регистра, выход первого регистра соединен с вторым входом сумматора формирователя кода разбиения, с входом вычитаемого вычитателя и с вторым входом сумматора блока коммутации, выход вычитателя соединен с входом делителя блока нормирования, с входом второго элемента задержки блока нормирования, с вторым входом элемента И блока нормирования и с первым входом второго элемента сравнения, второй вход которого является входом единичного потенциала анализатора, выход второго элемента сравнения соединен с тактовым входом второго умножителя блока нормирования и с входом триггера, выход которого соединен с вторым входом второго элемента И формирователя кода разбиения и с первым входом элемента И, выход элемента И соединен с вторым входом первого элемента И формирователя ко- да разбиения и с входом элемента задержки, выход элемента задержки соединен с тактовым входом вычитателя, с входом разрешения записи регистра блока коммутации и счетчика блока коммутации, с входом разрешения считывания второго регистра блока нормирования и со счетным входом счетчика блока нормирования, выход счетчика соединен с первым входом третьего элемента сравнения, выход которого соединен с входом установки в О первого счетчика, с входом запуска синхронизатора и с входом установки в О второго счетчика, вход третьег элемента сравнения соединен с первым входом четвертого элемента сравнения с вторым входом первого умножителя блока нормирования и является входом задания объема выборки анализатора, выход счетчика соединен с вторым входом четвертого элемента сравнения информационный вход демультиплексора блока коммутации соединен с вторым выходом третьего умножителя блока нормирования и выходом второго регистра блока нормирования, первый выход синхронизатора соединен с вторым входом элемента И блока коммутации, второй выход синхронизатора соединен с вторым входом элемента И, третий выход синхронизатора соединен с входом разрешения считывания блока памяти, с входом разрешения считывания третьего регистра, с входом разреше- ния считывания первого регистра формирователя кода разбиения, с входом

Из триггера 11

д 5

5

0

установки в О первого регистра, со счетным входом второго счетчика, с входом первого элемента задержки блока нормирования, с входом установки в О рчетчика блока нормирования, с входом разрешения считывания третьего регистра блока нормирования и с входом установки в О i-ro (,..., М) сумматора, информационный вход которого соединен с соответствующим выходом демультиплексора блока коммутации, первый вход i-ro умножителя соединен с выходом блока вычисления обратной величины блока нормирования, выход i-ro сумматора соединен с вторым входом соответствующего умножителя, выход четвертого элемента сравнения соединен с входом останова синхронизатора, с входом установки в О (i+M)-ro сумматора, информационный вход (i+M)-ro сумматора соединен с выходом i-ro умножителя, выход (i+M)-ro сумматора является выходом i-ro значения функции распределения анализатора.

срой. 2

:

:|

41

| название | год | авторы | номер документа |

|---|---|---|---|

| Статистический анализатор | 1986 |

|

SU1397939A1 |

| Статистический анализатор | 1990 |

|

SU1698892A1 |

| Статистический анализатор | 1986 |

|

SU1352518A1 |

| Статистический анализатор | 1985 |

|

SU1280395A1 |

| Статистический анализатор | 1989 |

|

SU1695328A1 |

| Статистический анализатор | 1987 |

|

SU1425716A1 |

| Устройство для сжатия информации | 1988 |

|

SU1536418A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| ТЕЛЕВИЗИОННЫЙ АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1988 |

|

SU1623536A1 |

Изобретение относится к вычислительной технике и может быть использовано при определении законов распределения случайных величин. Целью изобретения является повышение точности определения закона распределения при малом числе измерений. Статистический анализатор содержит блок 1 памяти, элементы сравнения 2, 13, 15 и 16, элемент НЕ 3, элемент ИЛИ 6, регистры 4, 5 и 8, формирователь 7 кода разбиения , элемент 9 задержки, элемент И 10, триггер 11, вычитатель 12, счетчик 14, счетчик 17, блок 18 коммутации, блок 19 нормирования, синхронизатор 20, М сумматоров 21, , 2,.,, М умножителей 22(,22,...,22д, К сумматоров 23,,23,...,23. Работа анализатора основана на последовательном делении интервала анализа в отношении, определяемом числами ряда Фибоначчи, причем над частью интервала, содержащей реализацию случайного процесса, строится равномерная функция распределения. 4 ил. (О

из 6ычитате/)я12

Фие.З

иътн. срав. 13

/2/д

Редактор Г.Волкова

fc.

Составитель В.Орлов Техред Л.Олийнык

Заказ 5696/45Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Л.Пилипенко

| Авторское свидетельство СССР | |||

| Статистический анализатор | 1980 |

|

SU964653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Статистический анализатор | 1974 |

|

SU551652A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-23—Публикация

1986-05-11—Подача