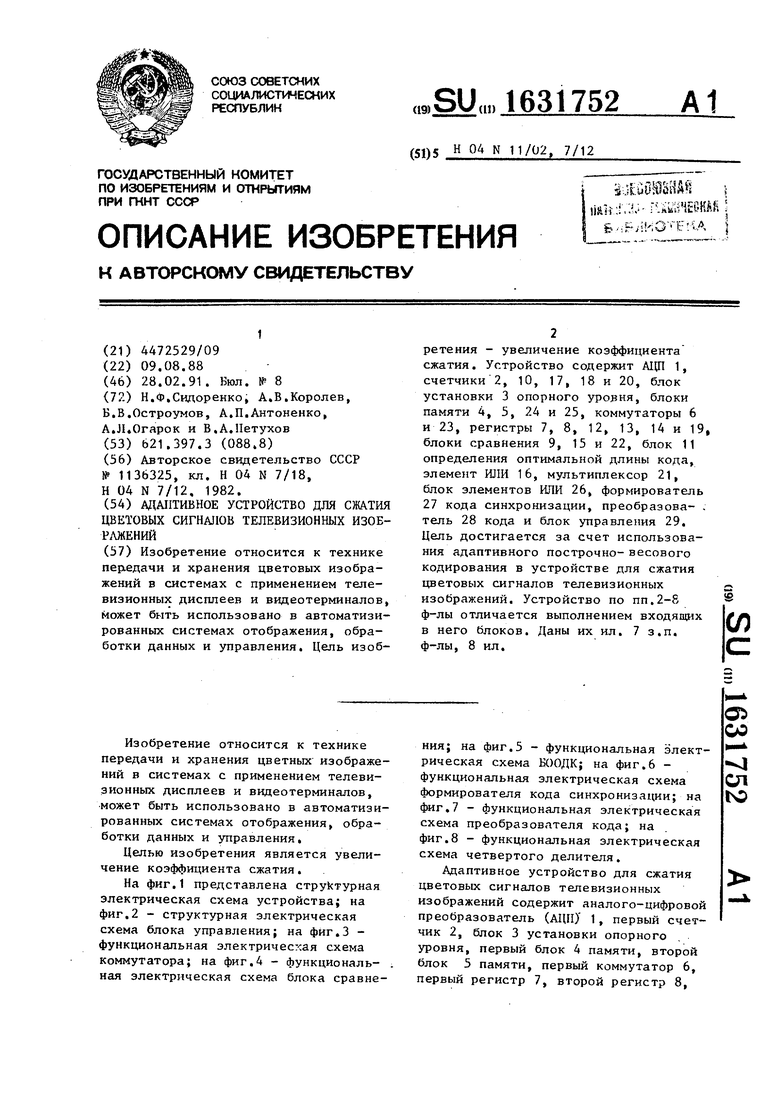

Изобретение относится к технике передачи и хранения цветных изображений в системах с применением телевизионных дисплеев и видеотерминалов, может быть использовано в автоматизированных системах отображения, обработки данных и управления.

Целью изобретения является увеличение коэффициента сжатия.

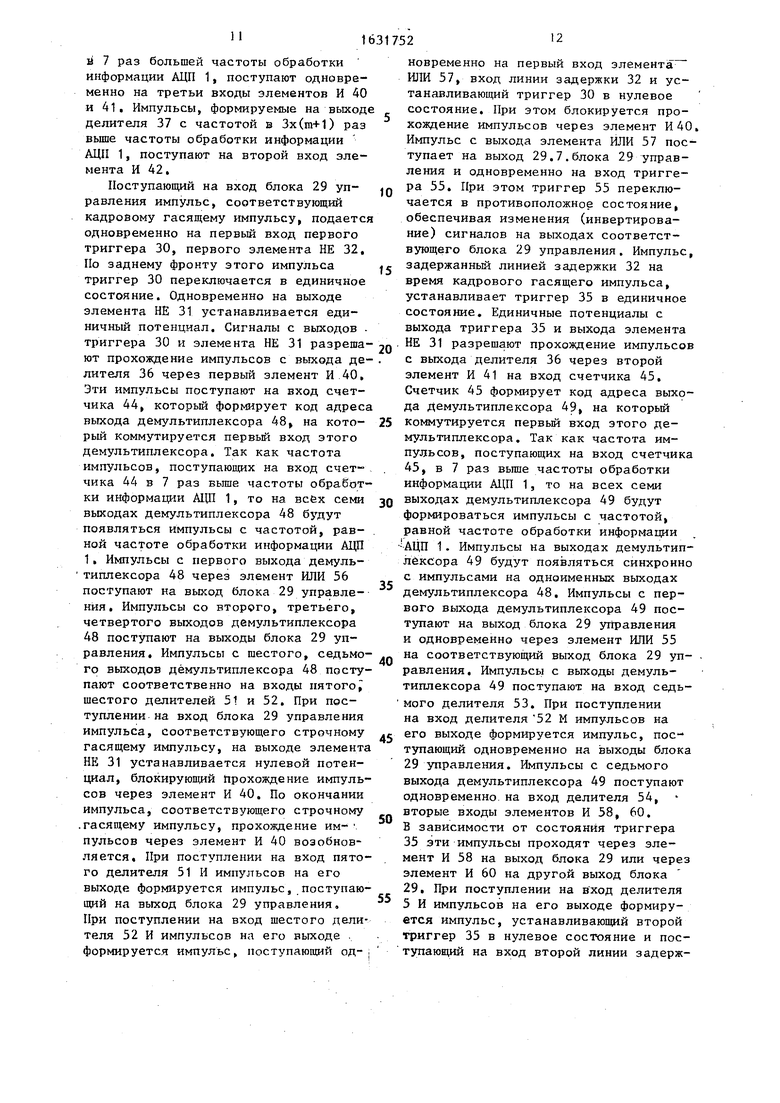

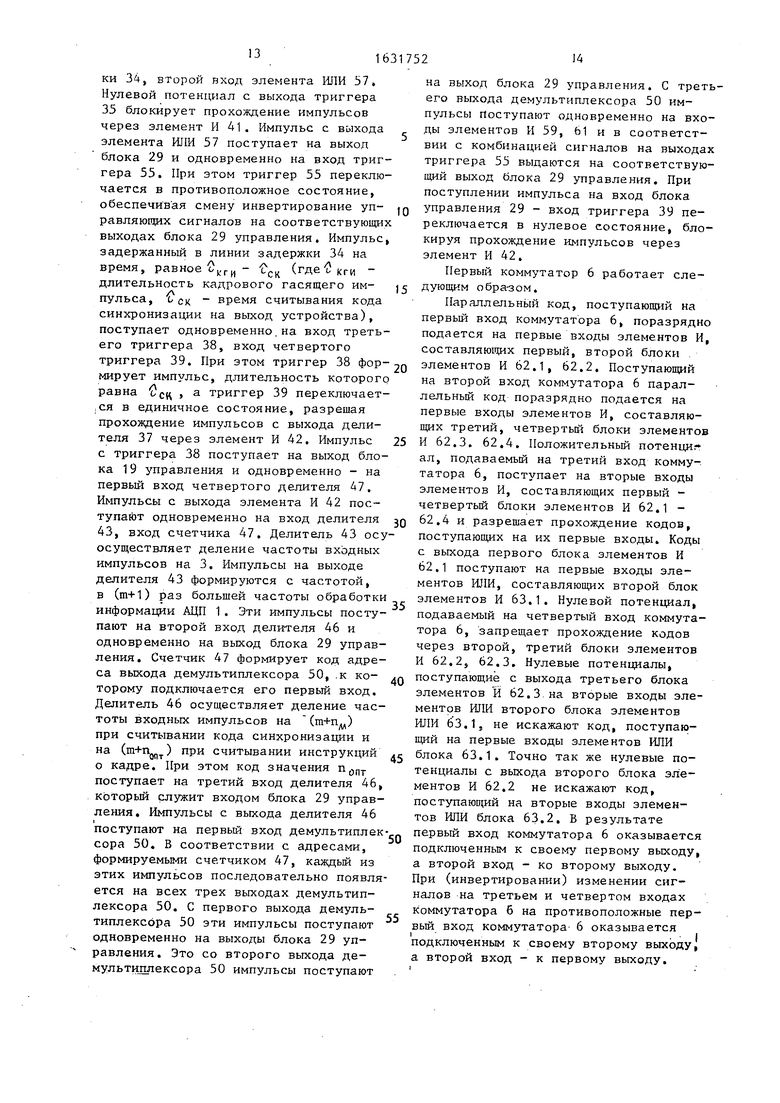

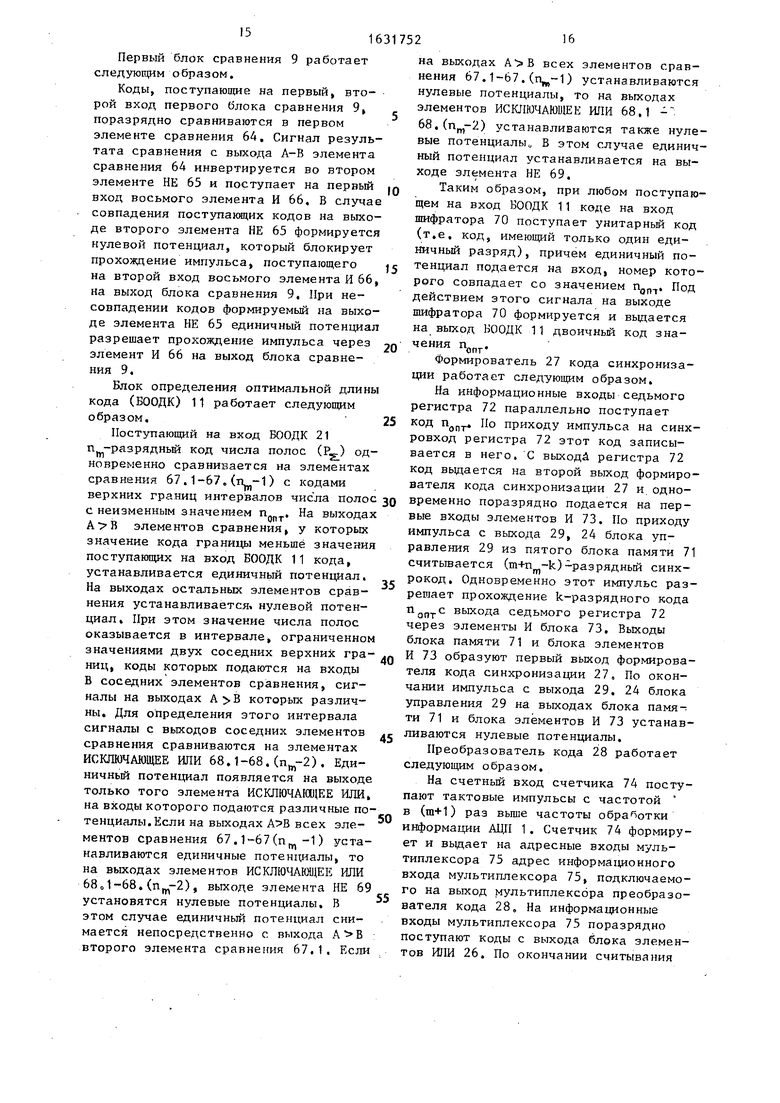

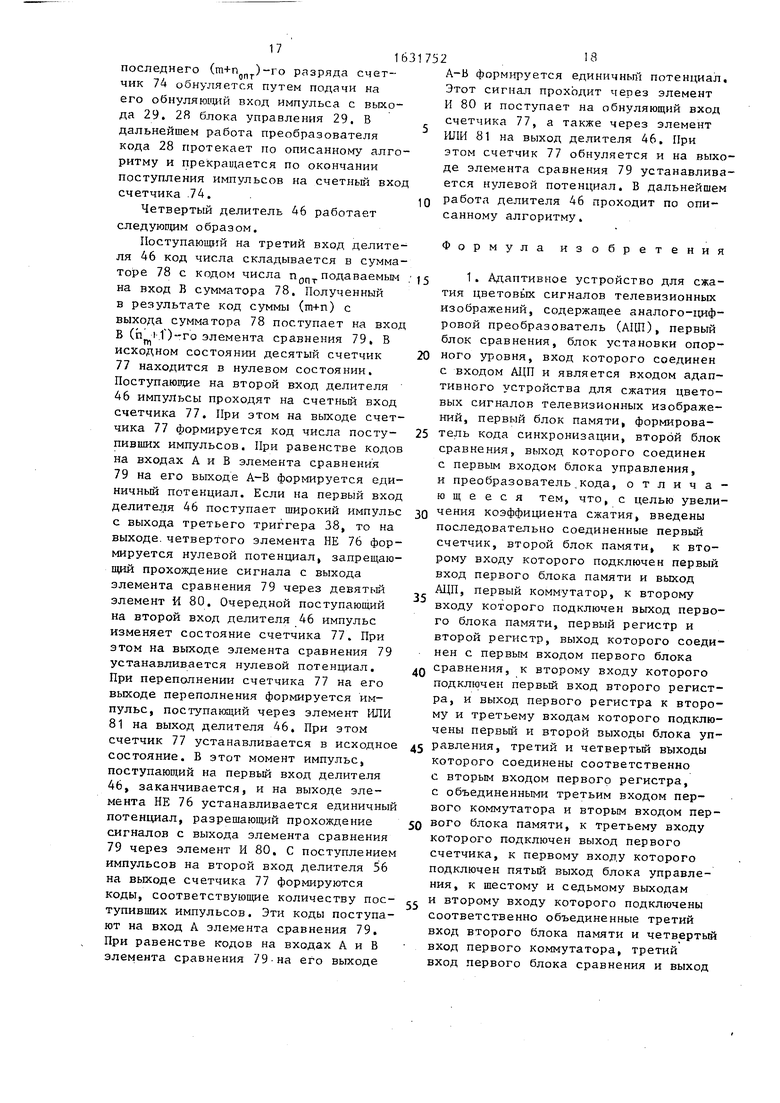

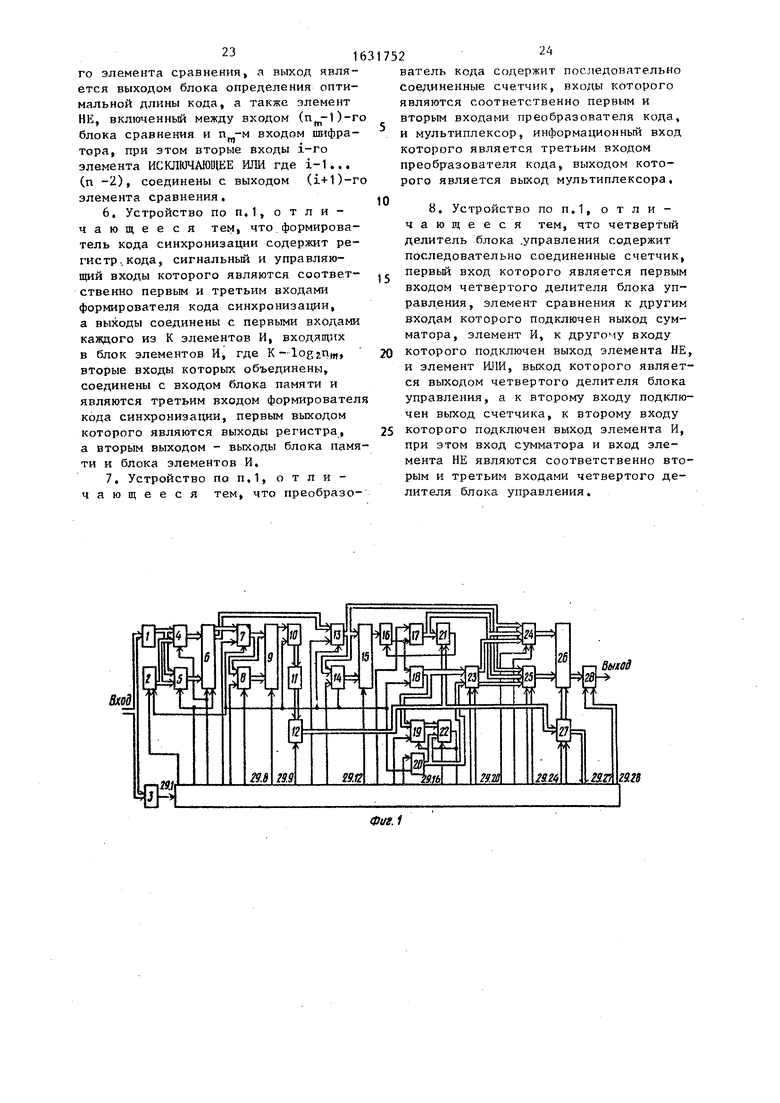

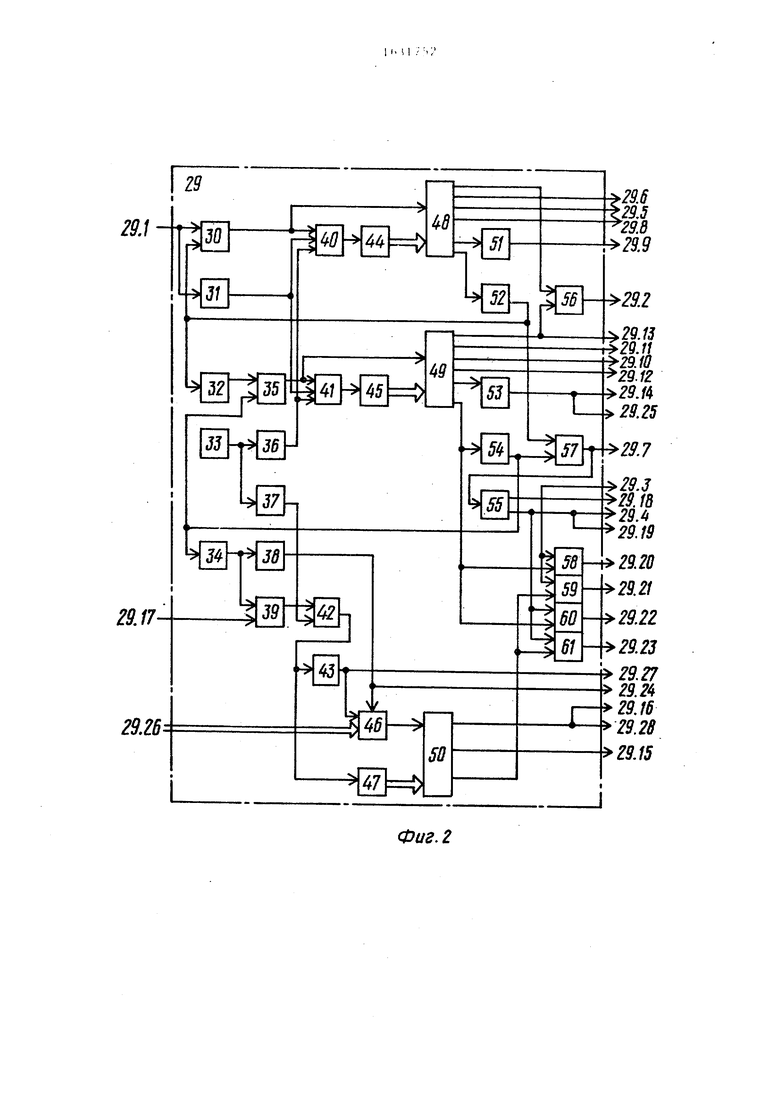

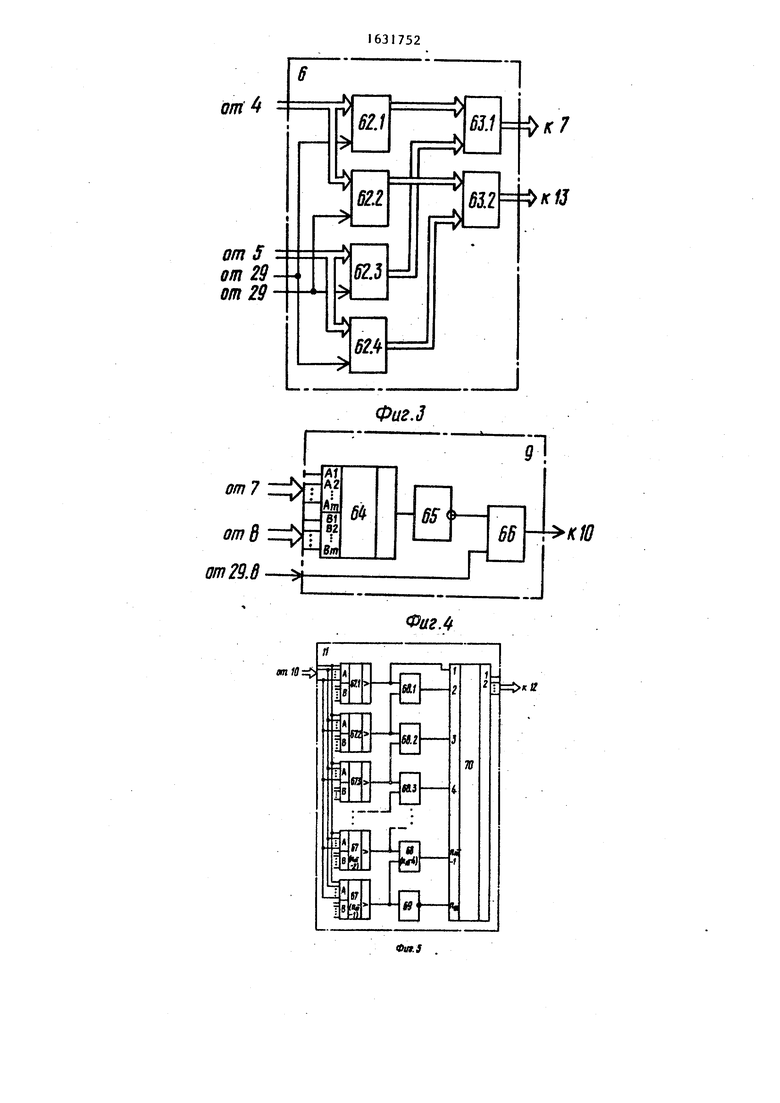

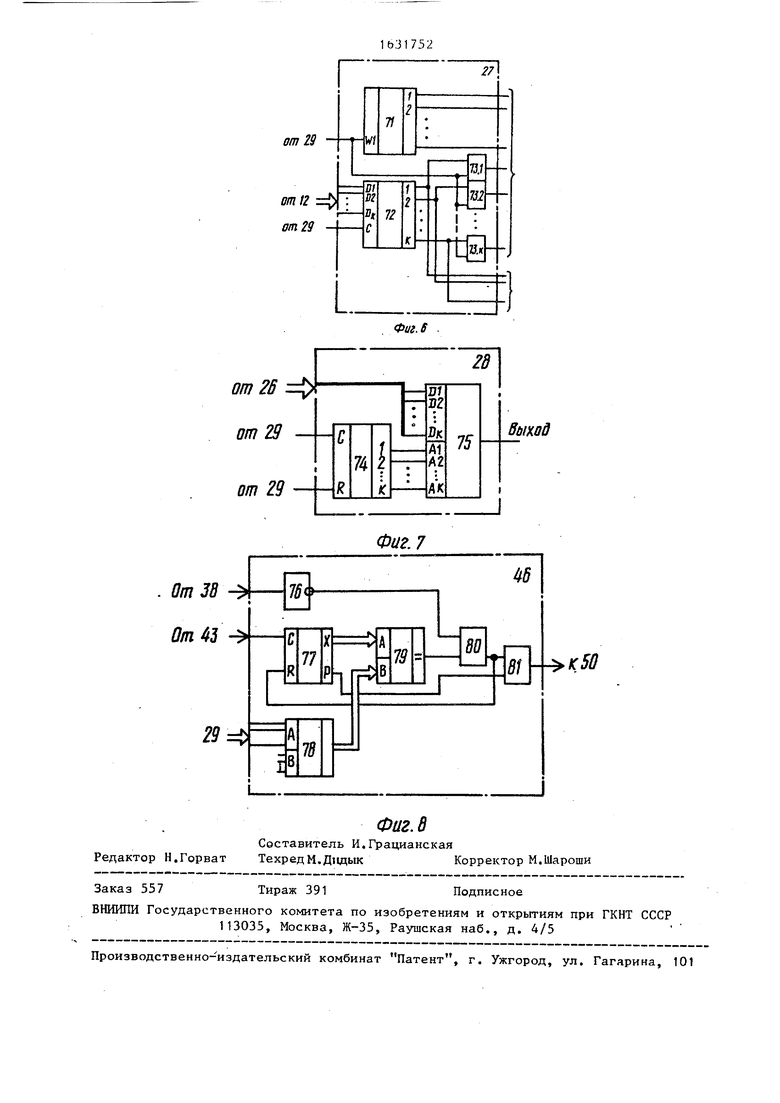

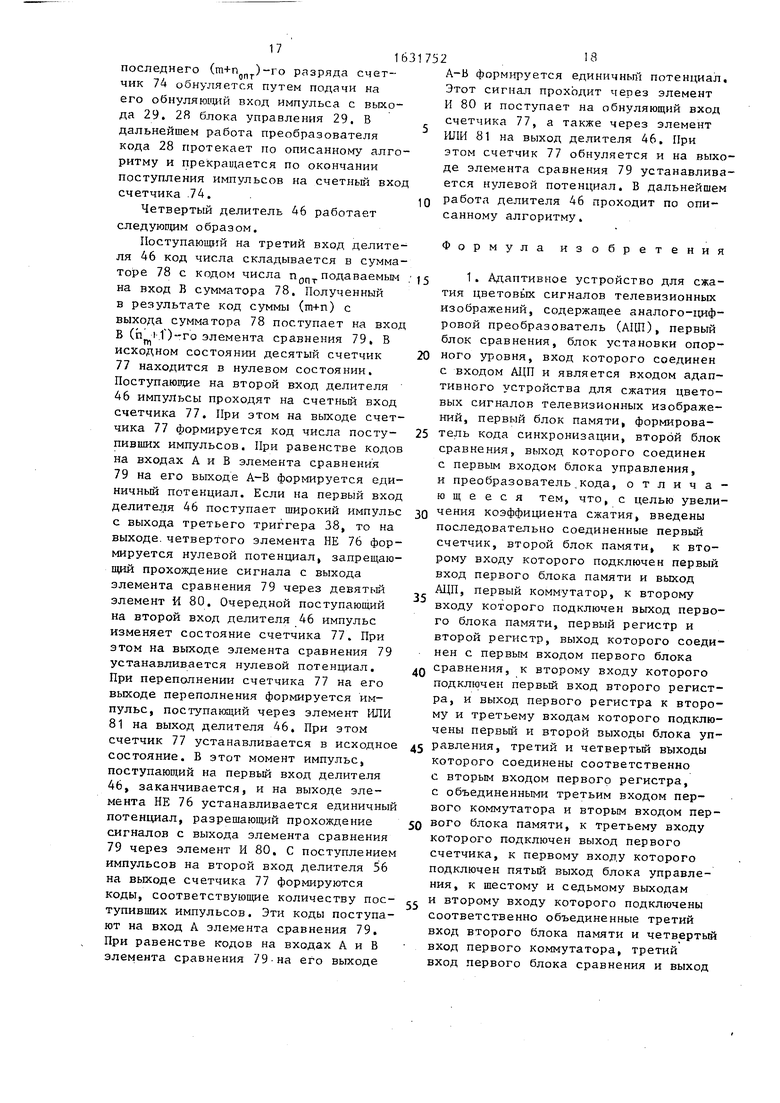

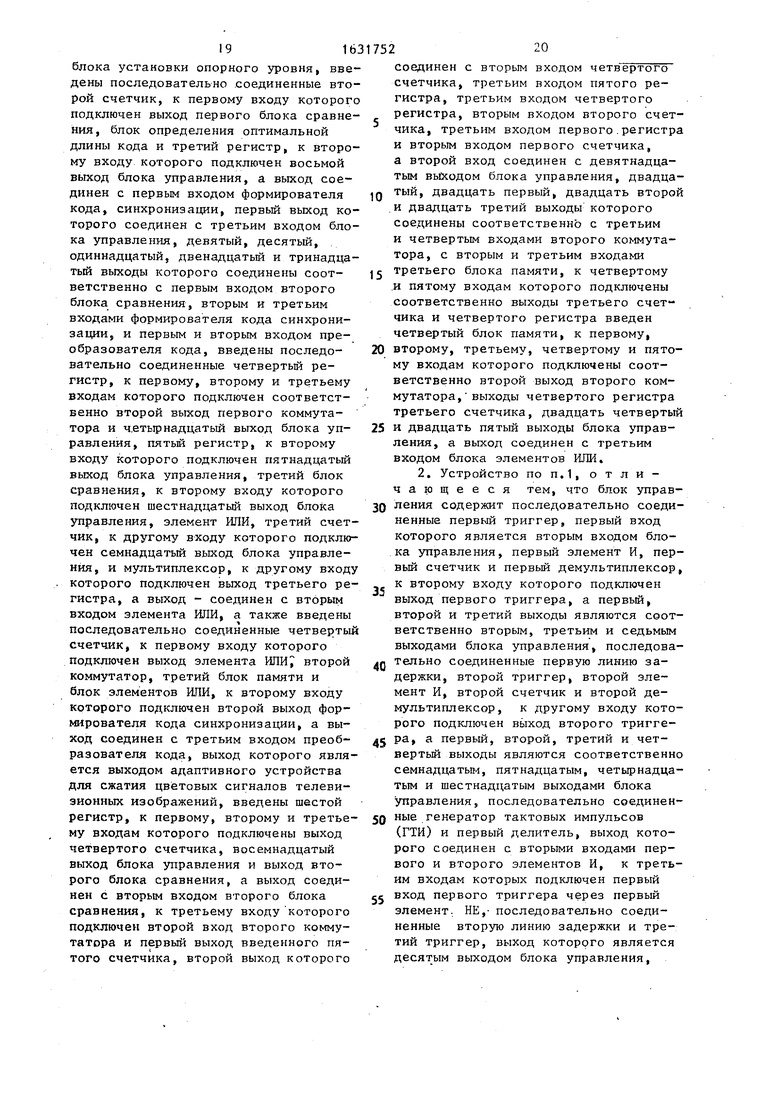

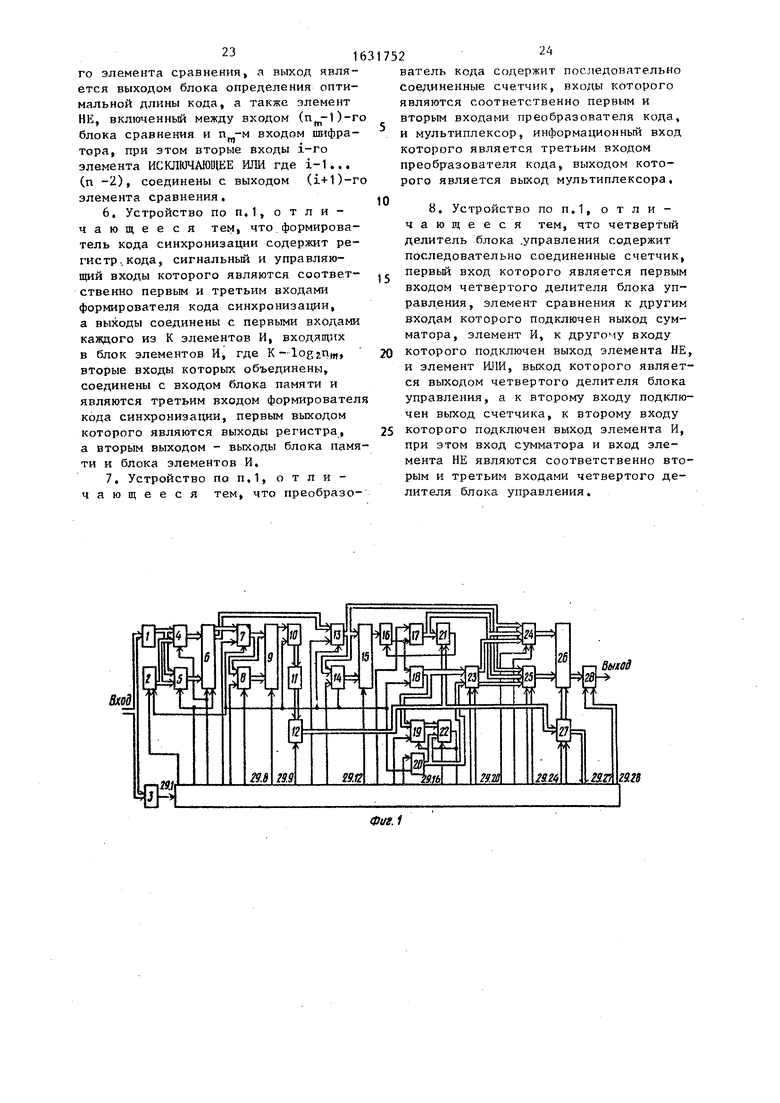

На фиг.1 представлена стру стурная электрическая схема устройства; на фиг.2 - структурная электрическая схема блока управления; на фиг.З - функциональная электрическая схема коммутатора; на фиг.4 - функциональ- . ная электрическая схема блока сравнения; на фиг.5 - функциональная электрическая схема БООДК; на фиг.6 - функциональная электрическая схема формирователя кода синхронизации; на фиг.7 - функциональная электрическая схема преобразователя кода; на фиг.8 - функциональная электрическая схема четвертого делителя.

Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений содержит аналого-цифровой преобразователь (АЦП) 1, первый счетчик 2, блок 3 установки опорного уровня, первый блок 4 памяти, второй блок 5 памяти, первый коммутатор 6, первый регистр 7, второй регистр 8,

О

00

1

ел

Ю

первый блок 9 сравнения, второй счетчик 10, блок определения оптимальной длины кода (БООДК) 11, третий регистр 12, четвертый регистр 13, пятый ре- гистр 14, третий блок 15 сравнения, элемент ИЛИ 16, третий счетчик 17, четвертый счетчик 18, шестой регистр 19, пятый счетчик 20, мультиплексор 21, второй блок 22 сравнения, второй коммутатор 23, третий блок 24 памяти, четвертый блок 25 памяти, блок элементов ИЛИ 26, формирователь 27 кода синхронизации, преобразователь кода 28, блок 29 управления,

Блок управления 29 (фиг.2) содержит первый триггер 30, первый элемент НЕ 31, первую линию задержки 32, генератор тактовых импульсов (ГТИ) 33, вторую линию задержки 34, второй триггер 35, первый делитель 36, второй делитель 37, третий триггер 38, четвертый триггер 39, первый элемент И 40, второй элемент И 41, третий элемент И 42, третий делитель 43, первый счетчик 44, второй счетчик 45, четвертый делитель 46, третий счетчик 47, первый демультиплексор 48, второй демультиплексор 49, третий демультип- лексор 50, пятый делитель 51, шестой делитель 52, седьмой делитель 53,восьмой делитель 54, пятый триггер 55, первый элемент ИЛИ 56, второй элемент ИЛИ 57, четвертый элемент И 58, пятый элемент И 59-,- шестой элемент И 60, седьмой элемент И 61,

Первый коммутатор 6 (фиг.З) содержит первый, второй, третий, четвертый, блоки элементов И 62,1-62.4 первый и второй, -блоки элементов ИЛИ 63.1, 63.2.

Первый блок сравнения 9 (фиг.4) содержит элемент сравнения 64, элемент НЕ 65, элемент И 65.

Блок определения оптимальной длины кода 11 (фиг.З) содержит первый, второй, третий элементы сравнения 67,1, 67.2-67 () первый, второй - (пт-2)-ой элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 68.1, 68.2, 68 (n/()-2) - элемент НЕ 69, шифратор 70,

Формирователь кода синхронизации 27 (фиг.6) содержит блок 71 памяти, регистр 72, блок элементов И 73.

Преобразователь кода 28 (фиг.7) содержит счетчик 74, мультиплексор 75

Четвертый делитель 46 (фиг.8) содержит элемент НЕ 76, счетчик 77,

сумматор 78, элемент сравнения Т9, элемент И 80, элемент ИЛИ 81,

Устройство работает следующим образом.

Аналоговый ТВ-сигнал преобразуется в АЦП 1 в цифровую форму, где каждому элементу отображения соответствует to-разрядный код цветности, а записывается в первый блок 4 памяти. Одновременно осуществляется подсчет числа полос в кадре. По окончании записи на основании подсчитанного числа полос осуществляется выбор оптимальной длины кодового слова, характеризующего длину полосы. Поступающий на вход устройства аналоговый сигнал следующего кадра подвергается аналогичному преобразованию и записывается во второй блок 5 памяти. Одновременно осуществляется считывание кодов цветности из первого блока 4 памяти, их - кодирование с оптимальной длиной кодовых слов и запись кодированных инструкций в третий блок 24 памяти. При поступлении на вход устройства аналогового сигнала очередного кадра кодированные инструкции считываются из третьего блока 34 памяти на вход устройства. Одновременно поступающий на вход устройства сигнал обрабатывается АЦП 1 и записывается в первый блок 4 памяти. Параллельно с этим производится считывание кодов цветности предыдущего кадра из второго блока 5 памяти, их кодирование кодом оптимальной длины и запись полученных кодированных инструкций в четвертый блок 25 памяти. Таким образом, в устройстве одновременно осуществляется обработка трех следующих друг за другом кадров. Это обеспечивает обработку информации без потерь.

Рассмотрим работу устройства по структурной схеме (фиг.1).

В исходном состоянии первый счетчик 2, первый регистр 7, второй регистр 8, второй счетчик 10, четвертый регистр 13, пятый регистр 14, четвертый счетчик 18,шестой регистр 19, пятый счетчик 20 обнулены.

Входной аналоговый сигнал одновременно поступает на вход АЦП 1, вход блока 3 установки опорного уровня. Блок 3 установки опорного уровня формирует и выдает на вход блока 29 управления импульс, соответствующий кадровому гасящему импульсу. Этот импульс .разрешает работу блока 29

управления. Параллельный т-разрядный код цветности с выхода АЦП 1 поступает на первые (информационные) входы первого, второго блоков 4 и 5 памяти Так как на вход Запись блока 4 памяти подается единичный потенциал с выхода блока 29 управления, а на третий вход Запись блока 5 памяти подается нулевой потенциал с выхода блока 29 управления, то поступающий код цветности записывается в блок 4 памяти по адресу, сформированному под воздействием импульса с выхода блока 29 управления на выходе первого счетчика 2. Одновременно из блоков 4 и 5 памяти считывается содержимое ячеек памяти, имеющих этот адрес. Таким образом, информация, записываемая в блок 4 памяти одновременно считывается с его выхода. Коды с выходов первого, второго блока 4, 5 памяти поступает соответственно на два входа первого коммутатора 6, В соответствии с комбинацией сигналов на других входах коммутатора 6 первый вход его подключается к первому выходу, а второй вход - ко второму выходу коммутатора 6. Код с первого выхода коммутатора 6 поступает на первый (информационный) вход первого регистра 7 и записывается в него по приходу импульса с блока 29 управления на второй вход (синхровход) регистра 7. По приходу импульса с выхода блока 29 управления на второй вход (синхровход) второго регистра 8. в него записывается код, поступающий с выхода первого регистра 7, за счет того, что импульс с выхода блока 29 опережает импульс с другого выхода блока 9, во второй регистр 8 записывается код цветности предыдущего элемента отображения (или нулевой комбинации в случае поступления на вход регистра 7 кода цветности первого элемента отображения кадра), а в первый регистр 7 записывается код цветности текущего элемента отображения. Эти коды сравниваются в первом блоке 9 сравнения. В случае различия кодов на выходе блока 9 сравнения по приходу на его третий вход импульса с выхода блока 29 управления формируется единичный импульс. При совпадении кодов на выходе блока 9 сравнения сохраняется нулевой потенциал. Второй счетчик 10 осуществляет подсчет импульсов и выдачу результата на вход

блока определения оптимальной длины кода (БООДК) 11. Под воздействием : этого кода БООДК 11 определяет nonr

и выдает код значения п

5

опт

на информационный вход третьего регистра 12. Однако записываться код пОГ|Т в регистр. 12 не будет, так как запись осуществляется по приходу на синхровход регистра 12 импульса с выхода блока 09 управления 29, который формируется по окончании поступления кадра на вход устройства. При поступлении на вход устройства строчного гасящего импульса на выходе блока 3 установки опорного уровня формируется импульс, блокирующий выдачу импульсов с соответствующих выходов блока 29 управления на время строчного гасяще0 го импульса. По описанному алгоритму осуществляется запись в первый блок 4 памяти кодов цветности всех элементов отображения и определение п.опт для поступившего кадра. По окончании пос5 тупления кадра на вход устройства импульс с выхода блока 29 управления обеспечит запись в регистр 12 кода. По окончании записи на выходе блока 29 управления формируется импульс,

0 обнуляющий первый счетчик 2, первый регистр 7, второй регистр 8, второй счетчик 10, четвертый регистр 13, пятый регистр 14, четвертый счетчик 18, пятый счетчик 20.

Поступающий на вход устройства аналоговый сигнал следующего кадра обрабатывается аналогично описанному, с той разницей, что запись кодов ценности элементов отображения производится во второй блок 5 памяти, выход которого коммутатор 6 подключает к первому (информационному) входу регистра 7. Одновременно с записью из первого блока 4 памяти осуществля5 ется считывание кодов цветности кадра, попт для которого была определена. В соответствии с комбинацией сигналов на входах коммутатора 5, выход блока 4 памяти подключается к инфор0 мационному входу четвертого регистра 13. Но приходу импульса с выхода блока 29 управления на синхровход регистра 13 в него осуществляется запись кода, считываемого из блока 4

5 памяти. По приходу импульса с выхода блока 29 управления на синхровход регистра 14 в него записывается код, поступающий с выхода регистра 14, в него записывается код, поступающий

5

0

с выхода регистра 1.3. За счет того, что импульс с одного выхода блока 29 опережает импульс с другого выхода блока 29, в пятый регистр 14 записывается код цветности предыдущего элемента отображения (или нулевая комбинация в случае считывания кода цветности из первой ячейки памяти блока 4 памяти)j а в четвертый регистр 13 записывается код цветности текущего элемента отображения. Эти коды сравниваются в третьем блоке 15 сравнения. В случае совпадения кодов на выходе блока 15 сравнения сохраняется , нулевой потенциал. При этом состояние счетчика 17 увеличивается на единицу под воздействием импульса с выхода блока 29 управления, а состояние ч счетчика 18 не изменяется. Коммутатор 23 в соответствии с комбинацией сигналов на своих входах подключает выход счетчика 18 к адресному входу третьего блока 24 памяти. С приходом на вход Запись блока 24 памяти Импульса с выхода блока 29 управления в блок 26 памяти по адресу, сформированному на выходе счетчика 18, записывается кодированная инструкция, содержащая информацию о цветности (I) и длине полосы (D). При этом код цветности поступает с выхода четвертого регистра 13 на младших разрядов информационного входа блока 25 памяти, а код длины полосы - с выхода счетчика 17 на nm старших разрядов информационного входа блока 24 памяти. Если длина полосы превышает величину 2 опт элементов, то информация о такой полосе записывается в виде нескольких последовательных инструкций с одинаковым кодом цветности. Происходит это следующим образом. При посТ1утшении на счетный вход счетчика 17 (2ПОПТ-Н )-го импульса на попт-м разряде выхода счетчика 17 устанавливается единичный потенциал. Поступающий на адресный вход мультиплексора 21 код tionT разрешает прохождение этого потенциала на выходе муль- типлексора. Пройдя через элемент ИЛИ 16, этот сигнал обнуляет счетчик

17и увеличивает состояние счетчика

18на единицу. Это приводит к тому, что запись инструкции в блок 26 памяти происходит по новому адресу. Б случае различия кодов цветности текущего и предыдущего члемечтпн отображения на выходе блока 15 срапнр.ння

формируется единичным импулы , обнуляющий счетчик 17 и увеличивающий состояние счетчика 18 на единицу. При этом новая инструкция записывается в блок 24 памяти по новому адресу. Кодированные инструкции одновременно подаются и на информационные входы четвертого блока 25 памяти,

однако на его работу не влияют, так как блок 25 памяти работает в режиме считывания. По окончании кодирования кадра с выхода блока 29 управления на синхровход шестого регистра 19

г поступает импульс, обеспечивающий запись в регистр 19 кода максимального адреса (А , т.е. кода адреса ячейки памяти, в которую записана последняя инструкция закодированного

Q кадра). Одновременно на вход формирователя кода синхронизации 27 с. выхода блока 29 управления поступает импульс, разрешающий запись в регистр формирователя 27 кода попт закодиро5 ванного кадра. По окончании записи этот код выдается со стороны выхода формирователя 27 на вход блока 29 управления. Одновременно с выхода блока 29 управления выдается импульс, обну0 ляющий первый счетчик 2, первый регистр 7, второй регистр 8, второй счетчик 10, четвертый регистр 13, пятый регистр 14, четвертый счетчик 18, пятый счетчик 20,

Поступающий на вход устройства аналоговый сигнал очередного кадра обрабатывается и записывается в первый блок 4 памяти аналогично описанному. Одновременно коды цветности,

л считываемые из второго блока 5 памяти, кодируются аналогично описанному, с той разницей, что запись кодированного инструкцией осуществляется в четвертый блок 25 памяти, Одновременс но с поступлением на вход устройства сигнала очередного кадра начинается считывание кодированных инструкций из блока 24 памяти на выход устройства следующим образом. С выхода блока 29 управления на вход формирователя 27 кода синхронизации поступает импульс, длительность которого равна времени считывания кода синхронизации на выход устройства, причем задний фронт этого импульса совпадает с

5

0

5

задним фронтом кадрового гасящего импульса. С поступлением импульса на второй вход формирователя 27 ня его выходе формируется и выдается

блок элементов ИЛИ 2Ь на вход преобразователя кода 28 (т+пн)-разрядный код синхронизации, состоящий из (m+Пц-Ю-го маркера и k-разрядного кода попт . Одновременно с выхода блока 29 управления на второй вход преобразователя кода 28 начинают поступать импульсы, обеспечивающие преобразование параллельного кода синхронизации в последовательный и выдачу его на выход устройства. По окончании считывания кода синхронизации на выходе блока 29 управления формируется импульс, устанавливающий преобразователь кода 28 в исходное состояние Одновременно завершается поступление импульса с выхода блока 29 управления и на выходе формирователя 27 кода синхронизации устанавливается нулевой потенциал. Одновременно с импульсом на входе преобразователя кода 28 на выходе блока 29 формируется импульс, поступающий на вход второго блока 22 сравнения. Но окончании этого импульса с выхода блока 29 управления счетный вход пятого счетчика 20 поступает единичный импульс. Под воздействием этого импульса на выходе счетчика 20 формируется код адреса ячейки памяти, содержимое которой предстоит считать. Этот код сравнивается во втором блоке 22 сравнения с кодом максимального адреса, хранящимся в регистре 19. При несовпадении кодов нулевой потенциал на выходе блока 22 сравнения сохраняется. Коммутатор 23 в соответствии с комбинацией сигналов на третьем, четвертом своих входах подключает выход счетчика 20 к адресному входу блока 24 памяти. По приходу импульса с выхода блока 20 на вход Считывание блок 24 памяти осуществляет считывание содержимого адресуемой ячейки памяти через блок элементов ИЛИ 26 на вход преобразователя кода 28. На другой вход преобразователя кода 28 поступают импульсы с выхода блока 29, обеспечивая преобразование параллельного кода в последовательный и выдачу его на выход устройства. Но окончании считывания (т+попт)-разрядной инструкции на выход устройства преобразователь кода 28 устанавливается импульсом с выхода блока 29 управления в исходное состояние. После этого счетчик 20 под воздействием импульса с выхода блока 29 управления формирует

5

0

5

0

5

0

5

новый код адреса. В дальнейшем считывание инструкций осуществляется по описанному алгоритму до тех пор, пока коды максимального адреса и адреса, формируемого счетчиком 20, не совпадут. В этом случае по приходу импульса с выхода блока 29 управления на вход блока 22 сравнения на его выходе формируется единичный импульс. Этот импульс обнуляет регистр 19 и, поступая на вход блока 29 управления, блокирует выдачу импульсов с соответствующих выходов блока 29 управления. За счет того, что импульс на входе блока 22 опережает импульс на выходе входа счетчика 20, на выходе блока 22 сравнения формируется сигнал результата сравнения кода максимального адреса ячейки памяти, содержимое из которой уже считано на выход устройства. Таким образом, блокировка выдачи импульсов с соответствующих выходов блока 29 управления произойдет уже после окончания считывания всех инструкций кадра на выход устройства. По окончании обработки поступающего на вход устройства кадра на выходах блока 29 управления одновременно формируются импульсы, которые разрешают запись кода максимального адреса в регистр 19, кода попт в регистр формирователя 27 кода синхронизации. По окончании записи импульс с выхода блока 29 управления разрешает запись кода попт следующего кадра в регистр 12. Но окончании этой записи импульс с выхода блока 29 управления устанавливает первый счетчик 2, первый, второй регистр 7 и 8, второй счетчик 10, четвертый регистр 13, пятый регистр 14, четвертый счетчик 18, пятый счетчик 20 в нулевое состояние.

Блок управления 29 работает следующим образом.

В исходном состоянии первый триггер 30, второй, третий триггер 35 и 38, четвертый триггер 39, шестой счетчик 44, седьмой счетчик 45, восьмой счетчик 47, пятый триггер 55 находятся в нулевом состоянии. ГТИ 33 формирует импульсы с частотой в 21 (т+1) раз выше частоты обработки информации АЦП 1. Эти импульсы поступают одновременно На входы делителей 36 и 37, осуществляющих деление частоты входных импульсов соответственно на Зх(т+1) и 7. Импульсы, формируемые на выходе делителя 36 с частотой

и 7 раз большей частоты обработки информации АЦП 1, поступают одновременно на третьи входы элементов И 40 и 41. Импульсы, формируемые на выходе делителя 37 с частотой в Зх(т+1) раз выше частоты обработки информации АЦП 1, поступают на второй вход элемента И 42.

Поступающий на вход блока 29 управления импульс, соответствующий кадройому гасящему импульсу, подается одновременно на первый вход первого триггера 30, первого элемента НЕ 32, Но заднему фронту этого импульса триггер 30 переключается в единичное состояние. Одновременно на выходе элемента НЕ 31 устанавливается единичный потенциал. Сигналы с выходов . триггера 30 и элемента НЕ 31 разрешают прохождение импульсов с выхода делителя 36 через первый элемент И 40, Эти импульсы поступают на вход счетчика 44, который формирует код адреса выхода демультиплексора 48 на который коммутируется первый вход этого демультиплексора. Так как частота импульсов, поступающих на вход счетчика 44 в 7 раз выше частоты обработки информации АЦП 1, то на всех семи выходах демультиплексора 48 будут появляться импульсы с частотой, равной частоте обработки информации АЦП 1, Импульсы с первого выхода демультиплексора 48 через элемент ИЛИ 56 поступают на выход блока 29 управления. Импульсы со второго, третьего, четвертого выходов демультиплексора 48 поступают на выходы блока 29 управления. Импульсы с шестого, седьмого выходов демультиплексора 48 поступают соответственно на входы пятого шестого делителей 51 и 52, При поступлении на вход блока 29 управления импульса, соответствующего строчному гасящему импульсу, на выходе элемента НЕ 31 устанавливается нулевой потенциал, блокирующий прохождение импульсов через элемент И 40. По окончании импульса, соответствующего строчному .гасящему импульсу, прохождение им- пульсов через элемент И 40 возобновляется. При поступлении на вход пятого делителя 51 И импульсов на его выходе формируется импульс, поступающий на выход блока 29 управления. При поступлении на вход шестого делителя 52 И импульсов на его выходе . формируется импульс, поступающий од-;

5

0

5

0

5

0

5

0

5

повременно на первый вход элемента ИЛИ 57, вход линии задержки 32 и устанавливающий триггер 30 в нулевое состояние. При этом блокируется прохождение импульсов через элемент И 40, Импульс с выхода элемента ИЛИ 57 поступает на выход 29.7.блока 29 управления и одновременно на вход триггера 55. При этом триггер 55 переключается в противоположное состояние, обеспечивая изменения (инвертирование) сигналов на выходах соответствующего блока 29 управления. Импульс, задержанньй линией задержки 32 на время кадрового гасящего импульса, устанавливает триггер 35 в единичное состояние. Единичные потенциалы с выхода триггера 35 и выхода элемента НЕ 31 разрешают прохождение импульсов с выхода делителя 36 через второй элемент И 41 на вход счетчика 45, Счетчик 45 формирует код адреса выхода демультиплексора 49, на который коммутируется первый вход этого демультиплексора. Так как частота импульсов, поступающих на вход счетчика 45, в 7 раз выше частоты обработки информации АЦП 1, то на всех семи выходах демультиплексора 49 будут формироваться импульсы с частотой, равной частоте обработки информации

-АЦП 1. Импульсы на выходах демультиплексора 49 будут появляться синхронно с импульсами на одноименных выходах демультиплексора 48. Импульсы с первого выхода демультиплексора 49 поступают на выход блока 29 управления и одновременно через элемент ИЛИ 55 на соответствующий выход блока 29 управления. Импульсы с выходы демультиплексора 49 поступают на вход седь1 мого делителя 53. При поступлении на вход делителя 52 М импульсов на его выходе формируется импульс, пос- тупеющий одновременно на выходы блока 29 управления. Импульсы с седьмого выхода демультиплексора 49 поступают одновременно на вход делителя 54, вторые входы элементов И 58, 60. В зависимости от состояния триггера 35 эти импульсы проходят через элемент И 58 на выход блока 29 или через элемент И 60 на другой выход блока 29, При поступлении на вход делителя 5 И импульсов на его выходе формируется импульс, устанавливающий второй триггер 35 в нулевое состояние и поступающий на вход второй линии задержки 34, второй вход элемента ИЛИ 57, Нулевой потенциал с выхода триггера 35 блокирует прохождение импульсов через элемент И 41. Импульс с выхода элемента ИЛИ 57 поступает на выход блока 29 и одновременно на вход триггера 55. При этом триггер 55 переключается в противоположное состояние, обеспечивая смену инвертирование управляющих сигналов на соответствующих выходах блока 29 управления. Импульс, задержанный в линии задержки 34 на время, равное Cj,rH - Сск ( длительность кадрового гасящего импульса, о ск время считывания кода синхронизации на выход устройства), поступает одновременно.на вход третьего триггера 38, вход четвертого триггера 39. При этом триггер 38 формирует импульс, длительность которого равна CCK a триггер 39 переключается в единичное состояние, разрешая прохождение импульсов с выхода делителя 37 через элемент И 42, Импульс с триггера 38 поступает на выход блока 19 управления и одновременно - на первый вход четвертого делителя 47. Импульсы с выхода элемента И 42 поступают одновременно на вход делителя 43, вход счетчика 47. Делитель 43 осу осуществляет деление частоты входных импульсов на 3. Импульсы на выходе делителя 43 формируются с частотой, в (т+1) раз большей частоты обработки информации АЦП 1. Эти импульсы поступают на второй вход делителя 46 и одновременно на выход блока 29 управления. Счетчик 47 формирует код адреса выхода демультиплексора 50, к которому подключается его первый вход. Делитель 46 осуществляет деление частоты входных импульсов на (m+n) при считывании кода синхронизации и на ( ) при считывании инструкций

ОмТ

о кадре. При этом код значения попт поступает на третий вход делителя 46, который служит входом блока 29 управления. Импульсы с выхода делителя 46 поступают на первый вход демультиплек сора 50. В соответствии с адресами, формируемыми счетчиком 47, каждый из этих импульсов последовательно появляется на всех трех выходах демультиплексора 50. С первого выхода демультиплексора 50 эти импульсы поступают одновременно на выходы блока 29 управления. Это со второго выхода демультиплексора 50 импульсы поступают

0

5

0

5

0

5

0

5

0

5

на выход блока 29 управления. С третьего выхода демультиплексора 50 импульсы поступают одновременно на входы элементов И 59, 61 и в соответствии с комбинацией сигналов на выходах триггера 55 выдаются на соответствующий выход блока 29 управления. При поступлении импульса на вход блока управления 29 - вход триггера 39 переключается в нулевое состояние, блокируя прохождение импульсов через элемент И 42.

Первый коммутатор 6 работает следующим обра-зом.

Параллельный код, поступающий на первый вход коммутатора 6, поразрядно подается на первые входы элементов И, составляющих первый, второй блоки элементов И 62.1, 62.2. Поступающий на второй вход коммутатора 6 параллельный код поразрядно подается на первые входы элементов И, составляющих третий, четвертый блоки элементов И 62.3. 62.4. Положительный потенции ал, подаваемый на третий вход коммутатора 6, поступает на вторые входы элементов И, составляющих первый - четвертый блоки элементов И 62.1 - 62,4 и разрешает прохождение кодов, поступающих на их первые входы. Коды с выхода первого блока элементов И 62.1 поступают на первые входы элементов ИЛИ, составляющих второй блок элементов И 63.1. Нулевой потенциал, подаваемый на четвертый вход коммутатора 6, запрещает прохождение кодов через второй, третий блоки элементов И 62.2, 62.3. Нулевые потенциалы, поступающие с выхода третьего блока элементов И 62.3 на вторые входы элементов ИЛИ второго блока элементов ИЛИ 63.1, не искажают код, поступающий на первые входы элементов ИЛИ блока 63.1. Точно так же нулевые потенциалы с выхода второго блока элементов И 62.2 не искажают код, поступающий на вторые входы элементов ИЛИ блока 63.2. В результате первый вход коммутатора 6 оказывается подключенным к своему первому выходу, а второй вход - ко второму выходу. При (инвертировании) изменении сигналов на третьем и четвертом входах коммутатора б на противоположные первый вход коммутатора 6 оказывается | I

подключенным к своему второму выходу,

а второй вход - к первому выходу.

Первый блок сравнения 9 работает следующим образом.

Коды, поступающие на первый, второй вход первого блока сравнения 9, поразрядно сравниваются в первом элементе сравнения 64. Сигнал результата сравнения с выхода А-В элемента сравнения 64 инвертируется во втором элементе НЕ 65 и поступает на первый вход восьмого элемента И 66. В случае совпадения поступающих кодов на выходе второго элемента НЕ 65 формируется нулевой потенциал, который блокирует прохождение импульса, поступающего на второй вход восьмого элемента И 66, на выход блока сравнения 9. При несовпадении кодов формируемый на выходе элемента НЕ 65 единичный потенциал разрешает прохождение импульса через элемент И 66 на выход блока сравнения 9.

Блок определения оптимальной длины кода (БООДК) 11 работает следующим образом.

Поступающий на вход БООДК 21 п -разрядный код числа полос (Р) одновременно сравнивается на элементах сравнения 67.1-67.(п-1) с кодами верхних границ интервалов числа полос с неизменным значением п0(1Т, На выходах элементов сравнения, у которых значение кода границы меньше значения поступающих на вход БООДК 11 кода, устанавливается единичный потенциал. На выходах остальных элементов сравнения устанавливается нулевой потенциал При этом значение числа полос оказывается в интервале, ограниченном значениями двух соседних верхних гра- ниц, коды которых подаются на входы В соседних элементов сравнения, сигналы на выходах которых различны. Для определения этого интервала сигналы с выходов соседних элементов сравнения сравниваются на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 68.1-68.(). Единичный потенциал появляется на выходе только того элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, на входы которого подаются различные потенциалы. Если на выходах всех элементов сравнения 67.1-67 () устанавливаются единичные потенциалы, то на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 68„1-68.(nm-2), выходе элемента НЕ 69 установятся нулевые потенциалы. В этом случае единичный потенциал снимается непосредственно с выхода второго элемента сравнения 67.1. Если

5

о -. ,-

5

0

5

на выходах всех элементов сравнения 67.1-b7.() устанавливаются нулевые потенциалы, то на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 68,1 - 68.() устанавливаются также нулевые потенциалы В этом случае единичный потенциал устанавливается на выходе элемента НЕ 69.

Таким образом, при любом поступающем на вход БООДК 11 коде на вход шифратора 70 поступает унитарный код (т.е. код, имеющий только один единичный разряд), причем единичный потенциал подается на вход, номер которого совпадает со значением погп. Под действием этого сигнала на выходе шифратора 70 формируется и выдается на выход БООДК 11 двоичный код значения попг.

Формирователь 27 кода синхронизации работает следующим образом.

На информационные входы седьмого регистра 72 параллельно поступает код попт. По приходу импульса на синх- ровход регистра 72 этот код записывается в него. С выхода регистра 72 код выдается на второй выход формирователя кода синхронизации 27 и одновременно поразрядно подается на первые входы элементов И 73. По приходу импульса с выхода 29, 24 блока управления 29 из пятого блока памяти 71 считывается (m+nm-k)-разрядный синх- рокод. Одновременно этот импульс разрешает прохождение k-разрядного кода поптс выхода седьмого регистра 72 через элементы И блока 73. Выходы блока памяти 71 и блока элементов И 73 образуют первый выход формирователя кода синхронизации 27, По окончании импульса с выхода 29. 24 блока управления 29 на выходах блока памяти 71 и блока элементов И 73 устанавливаются нулевые потенциалы.

Преобразователь кода 28 работает следующим образом.

На счетный вход счетчика 74 поступают тактовые импульсы с частотой в (ш+1) раз выше частоты обработки информации АЦП 1. Счетчик 74 формирует и выдает на адресные входы мультиплексора 75 адрес информационного входа мультиплексора 75, подключаемого на выход мультиплексора преобразователя кода 28. На информационные входы мультиплексора 75 поразрядно поступают коды с выхода блока элементов ИЛИ 26. По окончании считывания

последнего (m+nonr)-io разряда счетчик 74 обнуляется путем подачи на его обнуляющий вход импульса с выхода 29. 28 бпока управления 29. В дальнейшем работа преобразователя кода 28 протекает по описанному алгоритму и прекращается по окончании поступления импульсов на счетный вход счетчика 74.

Четвертый делитель 46 работает следующим образом.

Поступающий на третий вход делителя 46 код числа складывается в сумматоре 78 с кодом числа поптподаваемым на вход В сумматора 78. Полученный в результате код суммы (m+n) с выхода сумматора 78 поступает на вход В (hi 1)-го элемента сравнения 79, В исходном состоянии десятый счетчик 77 находится в нулевом состоянии. Поступающие на второй вход делителя 46 импульсы проходят на счетный вход счетчика 77. При этом на выходе счетчика 77 формируется код числа поступивших импульсов. При равенстве кодов на входах А и В элемента сравнения 79 на его выходе А-В формируется единичный потенциал. Если на первый вход делителя 46 поступает широкий импульс с выхода третьего триггера 38, то на выходе четвертого элемента НЕ 76 формируется нулевой потенциал, запрещающий прохождение сигнала с выхода элемента сравнения 79 через девятый элемент И 80. Очередной поступающий на второй вход делителя 46 импульс изменяет состояние счетчика 77. При этом на выходе элемента сравнения 79 устанавливается нулевой потенциал. При переполнении счетчика 77 на его выходе переполнения формируется импульс, поступающий через элемент ИЛИ 81 на выход делителя 46. При этом счетчик 77 устанавливается в исходное состояние. В этот момент импульс, поступающий на первый вход делителя 4b, заканчивается, и на выходе элемента НЕ 76 устанавливается единичный потенциал, разрешающий прохождение сигналов с выхода элемента сравнения 79 через элемент И 80. С поступлением импульсов на второй вход делителя 56 на выходе счетчика 77 формируются коды, соответствующие количеству поступивших импульсов. Эти коды поступают на вход А элемента сравнения 79. При равенстве кодов на входах А и В элемента сравнения 79 на его выходе

5

0

А-В формируется единичный потенциал. Этот сигнал проходит через элемент И 80 и поступает на обнуляющий вход счетчика 77, а также через элемент ИЛИ 81 на выход делителя 46. При этом счетчик 77 обнуляется и на выходе элемента сравнения 79 устанавливается нулевой потенциал. В дальнейшем работа делителя 46 проходит по описанному алгоритму.

Формула изобретения

1. Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений, содержащее аналого-цифровой преобразователь (АЦП), первый блок сравнения, блок установки опорного уровня, вход которого соединен с входом АЦП и является входом адаптивного устройства для сжатия цветовых сигналов телевизионных изображений, первый блок памяти, формирова5 тель кода синхронизации, второй блок сравнения, выход которого соединен с первым входом блока управления, и преобразователь кода, отличающееся тем, что, с целью увеличения коэффициента сжатия, введены последовательно соединенные первый счетчик, второй блок памяти, к второму входу которого подключен первый вход первого блока памяти и выход АЦП, первый коммутатор, к второму входу которого подключен выход первого блока памяти, первый регистр и второй регистр, выход которого соединен с первым входом первого блока

Q сравнения, к второму входу которого подключен первый вход второго регистра, и выход первого регистра к второму и третьему входам которого подключены первый и второй выходы блока уп5 рявления, третий и четвертый выходы которого соединены соответственно с вторым входом первого регистра, с объединенными третьим входом первого коммутатора и вторым входом первого блока памяти, к третьему входу которого подключен выход первого счетчика, к первому входу которого подключен пятый выход блока управления, к шестому и седьмому выходам и второму входу которого подключены соответственно объединенные третий вход второго блока памяти и четвертый вход первого коммутатора, третий вход первого блока сравнения и выход

0

5

0

5

блока установки опорного уровня, введены последовательно соединенные второй счетчик, к первому входу которого подключен выход первого блока сравнения, блок определения оптимальной длины кода и третий регистр, к второму входу которого подключен восьмой выход блока управления, а выход соединен с первым входом формирователя кода, синхронизации, первый выход которого соединен с третьим входом блока управления, девятый, десятый, одиннадцатый, двенадцатый и тринадцатый выходы которого соединены соответственно с первым входом второго блока сравнения, вторым и третьим входами формирователя кода синхронизации, и первым и вторым входом преобразователя кода, введены последовательно соединенные четвертый регистр, к первому, второму и третьему входам которого подключен соответственно второй выход первого коммутатора и четырнадцатый выход блока управления, пятый регистр, к второму входу которого подключен пятнадцатый выход блока управления, третий блок сравнения, к второму входу которого подключен шестнадцатый выход блока управления, элемент ИЛИ, третий счетчик, к другому входу которого подключен семнадцатый выход блока управления, и мультиплексор, к другому входу которого подключен выход третьего регистра, а выход - соединен с вторым входом элемента ИЛИ, а также введены последовательно соединенные четвертый счетчик, к первому входу которого подключен выход элемента ИЛИ второй коммутатор, третий блок памяти и блок элементов ИЛИ, к второму входу которого подключен второй выход формирователя кода синхронизации, а выход соединен с третьим входом преобразователя кода, выход которого является выходом адаптивного устройства для сжатия цветовых сигналов телевизионных изображений, введены шестой регистр, к первому, второму и третьему входам которого подключены выход четвертого счетчика, восемнадцатый выход блока управления и выход второго блока сравнения( а выход соединен с вторым входом второго блока сравнения, к третьему входу которого подключен второй вход второго коммутатора и первый выход введенного пятого счетчика, второй выход которого

соединен с вторым входом четвертого счетчика, третьим входом пятого регистра, третьим входом четвертого регистра, вторым входом второго счетчика, третьим входом первого регистра и вторым входом первого счетчика, а второй вход соединен с девятнадцатым выходом блока управления, двадца- тый, двадцать первый, двадцать второй и двадцать третий выходы которого соединены соответственно с третьим и четвертым входами второго коммутатора, с вторым и третьим входами 5 третьего блока памяти, к четвертому и пятому входам которого подключены соответственно выходы третьего счетчика и четвертого регистра введен четвертый блок памяти, к первому, 0 второму, третьему, четвертому и пятому входам которого подключены соответственно второй выход второго коммутатора, выходы четвертого регистра третьего счетчика, двадцать четвертый 5 и двадцать пятый выходы блока управления, а выход соединен с третьим входом блока элементов ИЛИ.

2. Устройство по п.1, отличающееся тем, что блок управ- 0 ления содержит последовательно соединенные первый триггер, первый вход которого является вторым входом блока управления, первый элемент И, первый счетчик и первый демультиплексор, к второму входу которого подключен выход первого триггера, а первый, второй и третий выходы являются соответственно вторым, третьим и седьмым выходами блока управления, последовательно соединенные первую линию задержки, второй триггер, второй элемент И, второй счетчик и второй демультиплексор , к другому входу которого подключен выход второго тригге- 5 pa, а первый, второй, третий и четвертый выходы являются соответственно семнадцатым, пятнадцатым, четырнадцатым и шестнадцатым выходами блока управления, последовательно соединенные генератор тактовых импульсов (ГТИ) и первый делитель, выход которого соединен с вторыми входами первого и второго элементов И, к третьим входам которых подключен первый вход первого триггера через первый элемент НЕ, последовательно соединенные вторую линию задержки и третий триггер, выход которого является десятым выходом блока управления,

5

0

0

5

последовательно соединенные четвертый триггер, первый вход которого является первым входом блока управления, а второй вход соединен с вхо- дом третьего триггера, третий элемент И, к другому входу которого подключен выход ГТИ через второй делитель, третий делитель, четвертый делитель,

ВТОрОЙ И Третий ВХОДЫ КОТОРОГО ЯВЛЯ-

ются соответственно третьим входом и десятым выходом блока управления, и третий демультиплексор, к другому входу которого подключен выход третьего элемента И через третий счетчик, а первый и второй выходы являются соответственно девятнадцатым и объединенными девятым и тринадцатым выходами блока управления, пятый делитель, вход которого соединен с чет- вертым выходом первого демультиплек- сора, а выход является восьмым выходом блока управления, первый элемент ИЛИ, к первому.,и второму входам которого подключены соответственно пятый выход первого демультиплексора и первый выход второго демультиплексора, а выход является пятым выходом блока управления, последовательно соединенные шестой делитель, к входу которого подключен шестой выход демультиплексора, и второй элемент ИЛИ, выход которого является первым выходом блока управления, седьмой , делитель, к входу которого подключен пятый выход второго демультиплексора, а выход является восемнадцатым и одиннадцатым выходами блока управления, восьмой, делитель, к входу которого подключен шестой выход второго де- мультиплексора, а выход соединён с вторым входом второго элемента ИЛИ, .входом второй линии задержки и вторым входом второго триггера, пятый триггер, к входу которого подключен выход второго элемента ИЛИ, а первый и второй выходы являются объединенными шестым и двадцатым выходами блока управления и объединенными четвертым и двадцать вторым выходами блока управления-, а также четвертый пятый, шестой и седьмой элементы И, выходы которых являются соответственно двадцать вторым, двадцать третьим, двадцать четвертым и двадцать пятым выхо- дами блока управления, к первому и .. , второму входам четвертого элемента И подключены соответственно первый вход пятого триггера и объединенные первый

вход шестого элемента И и шестой вы- ход второго демультиплексора, к второму входу пятого элемента И,подклю- чен первый вход седьмого элемента И и третий выход третьего демультиплексора, к второму входу шестого элемента И подключен второй вход седьмого элемента И и второй выход пятого триггера, при этом выход третьего делителя является двенадцатым выходом блока управления, а выход шестого делителя соединен с входом первой линии задержки и вторым входом первого триггера.

3.Устройство по п.1, отличающееся тем, что коммутатор содержит первый и второй блоки элементов И, объединенные первые входы которых являются вторым входом коммутатора, а выходы соединены с первыми входами соответственно первого и второго блоков элементов ИЛИ, к вторым входам которых подключены выходы третьего и четвертого блоков элементов И, объединенные первые входы которых являются первым входом коммутатора, при этом объединенные вторые входы первого и четвертого блоков элементов И являются третьим входом коммутатора, четвертым входом которого являются объединенные вторые входы второго и третьего блоков элементов И, выходами коммутатора являются выходы блока элементов ИЛИ.

4.Устройство по п.1, о т л и - чающе еся тем, что блок сравнения содержит последовательно соединенные элемент сравнения, первый и второй входы которого являются соответствующими входами блока сравнения, элемент НЕ и элемент И, другой вход которого является третьим входом блока сравнения, выход которого является выходом элемента И.

5.Устройство по п.1, отличающееся тем, что блок определения оптимальной длины кода содержит nm-1 элементов сравнения, пт loguM (где М - количество элементов отображения в кадре), объединенные входы которых являются первым входом - блока определения оптимальной длины кода п -2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,

к первым входам которых подключены выходы соответствующих элементов г сравнения, а выходы соединены с соответствующими входами шифратора, к входу которого подключен выход первого элемента сравнения, а выход является выходом блока определения оптимальной длины кода, а также элемент НЕ, включенный между входом (п -О-го блока сравнения и входом шифратора, при этом вторые входы 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ где i-1... (п -2), соединены с выходом (i+1)-ro элемента сравнения.

6.Устройство по п. 1, о т л и - чающее ся тем, что формирователь кода синхронизации содержит регистр, кода, сигнальный и управляющий входы которого являются соответ- ственно первым и третьим входами формирователя кода синхронизации,

а выходы соединены с первыми входами каждого из К элементов И, входящих в блок элементов И, где K-log nm, вторые входы которых объединены, соединены с входом блока памяти и являются третьим входом формирователя кода синхронизации, первым выходом которого являются выходы регистра, а вторым выходом - выходы блока памяти и блока элементов И.

7.Устройство по п,1, отличающееся тем, что преобразователь кода содержит последовательно соединенные счетчик, входы которого являются соответственно первым и вторым входами преобразователя кода, и мультиплексор, информационный вход которого является третьим входом преобразователя кода, выходом которого является выход мультиплексора.

8. Устройство по п.1, о т л и - чающееся тем, что четвертый делитель блока .управления содержит последовательно соединенные счетчик, первый вход которого является первым входом четвертого делителя блока управления, элемент сравнения к другим входам которого подключен выход сумматора, элемент И, к другому входу которого подключен выход элемента НЕ и элемент ИЛИ, выход которого является выходом четвертого делителя блока управления, а к второму входу подключен выход счетчика, к второму входу которого подключен выход элемента И, при этом вход сумматора и вход элемента НЕ являются соответственно вторым и третьим входами четвертого делителя блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия телевизионных сигналов цветного изображения | 1989 |

|

SU1633523A1 |

| Устройство для сжатия цифровых телевизионных сигналов цветного изображения | 1988 |

|

SU1529471A1 |

| Устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1607080A1 |

| Устройство для отображения информации | 1988 |

|

SU1501135A1 |

| Устройство для сжатия цветовых сигналов телевизионных изображений | 1987 |

|

SU1515400A1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1984 |

|

SU1257635A1 |

| Телевизионная система с компрессией цифровых сигналов цветных изображений | 1989 |

|

SU1672589A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1494778A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1423982A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

Изобретение относится к технике передачи и хранения цветовых изображений в системах с применением телевизионных дисплеев и видеотерминалов, может быть использовано в автоматизированных системах отображения, обработки данных и управления. Цель изобретения - увеличение коэффициента сжатия. Устройство содержит АЦП 1, счетчики 2, Ю, 17, 18 и 20, блок установки 3 опорного уровня, блоки памяти 4, 5, 24 и 25, коммутаторы 6 и 23, регистры 7, 8, 12, 13, 14 и 19, блоки сравнения 9, 15 и 22, блок 11 определения оптимальной длины кода, элемент ИЛИ 1Ь, мультиплексор 21, блок элементов ИЛИ 26, формирователь 27 кода синхронизации, преобразова- . тель 28 кода и блок управления 29. Цель достигается за счет использования адаптивного построчно- весового кодирования в устройстве для сжатия цветовых сигналов телевизионных изображений. Устройство по пп.2-8 ф-лы отличается выполнением входящих в него блоков. Даны их ил. 7 з.п. ф-лы, 8 ил. & (Л

Вход

Выход

Ш8

art 4

от 5 от 29 от 29

hW

Фиг.д

Фиг л

t Cxt«r

amis

от 12 ф от 29

от 26 $ от 29

от 29

-I-I I

Фаг. В .

Фаг, 7

| Устройство для сжатия цифровых телевизионных сигналов | 1982 |

|

SU1136325A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-02-28—Публикация

1988-08-09—Подача