/X

fe

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения частоты сигналов | 1981 |

|

SU966617A1 |

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 2002 |

|

RU2231077C2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| Цифровой частотомер непрерывного действия | 1989 |

|

SU1698817A1 |

| Устройство для измерения сдвига фаз | 1986 |

|

SU1381406A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Способ измерения частоты следования импульсов | 1988 |

|

SU1594483A1 |

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| Цифровой фазометр-частотомер | 1985 |

|

SU1265644A1 |

Изобретение может быть использовано в измерителях частоты импульсных последовательностей. Цель изобретения - повышение точности преобразования частоты в код. Поставленная цель достигается тем, что в преобразователь частоты вход введен накапливающий сумматор 7, преобразователь также содержит формирователь 1 интервала измерений, генератор 2 опорной .частоты, первый формирователь 3. импульсов, счетчик 4 импульсов, второй формирователь 5 импульсов, регистр 7. Сущность изобретения заключается в возможности уменьшения погрешности измерения, обусловленной отличием номинальной и реальной функций преобразования. Это достигается путем представления результирующего кода в накапливающем сумматоре как суммы членов арифметической прогрессии. 2 ил.

Фиг.1

3L

ш

w

1

w

Q2

SP

чэ о о

ЦП

Изобретение относится к цифровой измерительной технике и может быть использовано в измерителях частоты импульсных последовательностей,

Цель изобретения - повышение точности преобразования частоты в код.

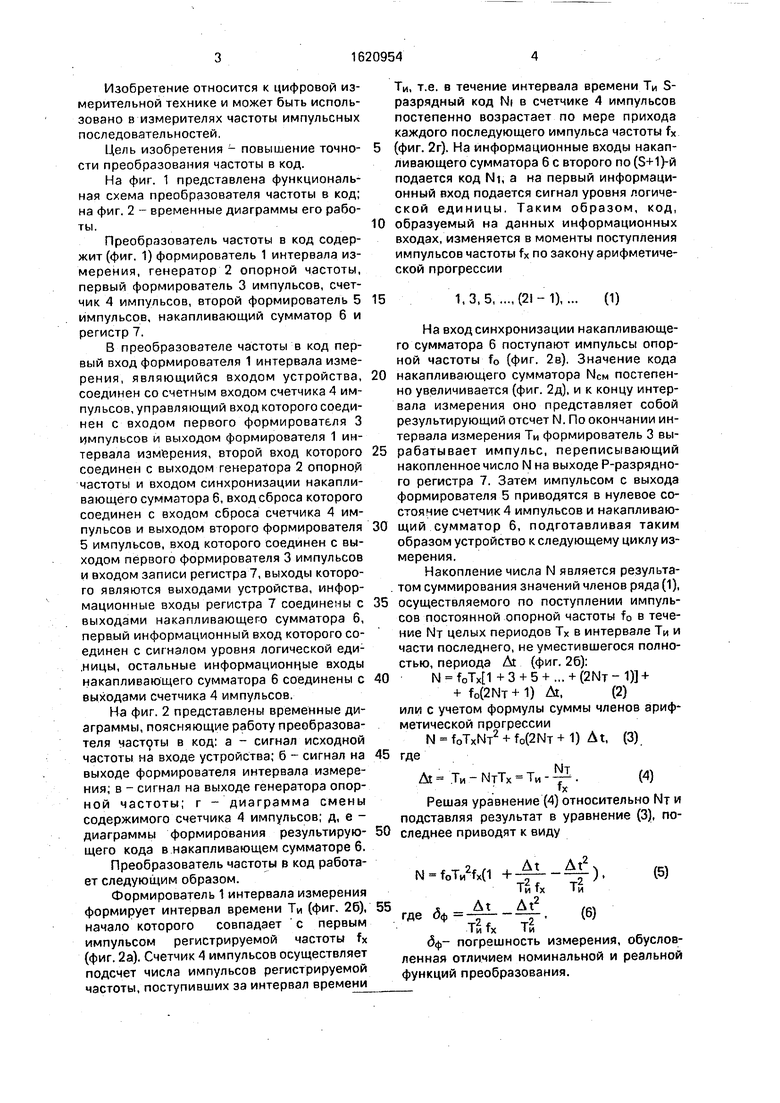

На фиг. 1 представлена функциональная схема преобразователя частоты в код; на фиг. 2 - временные диаграммы его работы.

Преобразователь частоты в код содержит (фиг. 1) формирователь 1 интервала измерения, генератор 2 опорной частоты, первый формирователь 3 импульсов, счетчик 4 импульсов, второй формирователь 5 импульсов, накапливающий сумматор 6 и регистр 7.

В преобразователе частоты в код первый вход формирователя 1 интервала измерения, являющийся входом устройства, соединен со счетным входом счетчика 4 импульсов, управляющий вход которого соединен с входом первого формирователя 3 импульсов и выходом формирователя 1 интервала измерения, второй вход которого соединен с выходом генератора 2 опорной частоты и входом синхронизации накапливающего сумматора 6, вход сброса которого соединен с входом сброса счетчика 4 импульсов и выходом второго формирователя 5 импульсов, вход которого соединен с выходом первого формирователя 3 импульсов и входом записи регистра 7, выходы которого являются выходами устройства, информационные входы регистра 7 соединены с выходами накапливающего сумматора б, первый информационный вход которого соединен с сигналом уровня логической еди- .ницы, остальные информационные входы накапливающего сумматора 6 соединены с выходами счетчика 4 импульсов.

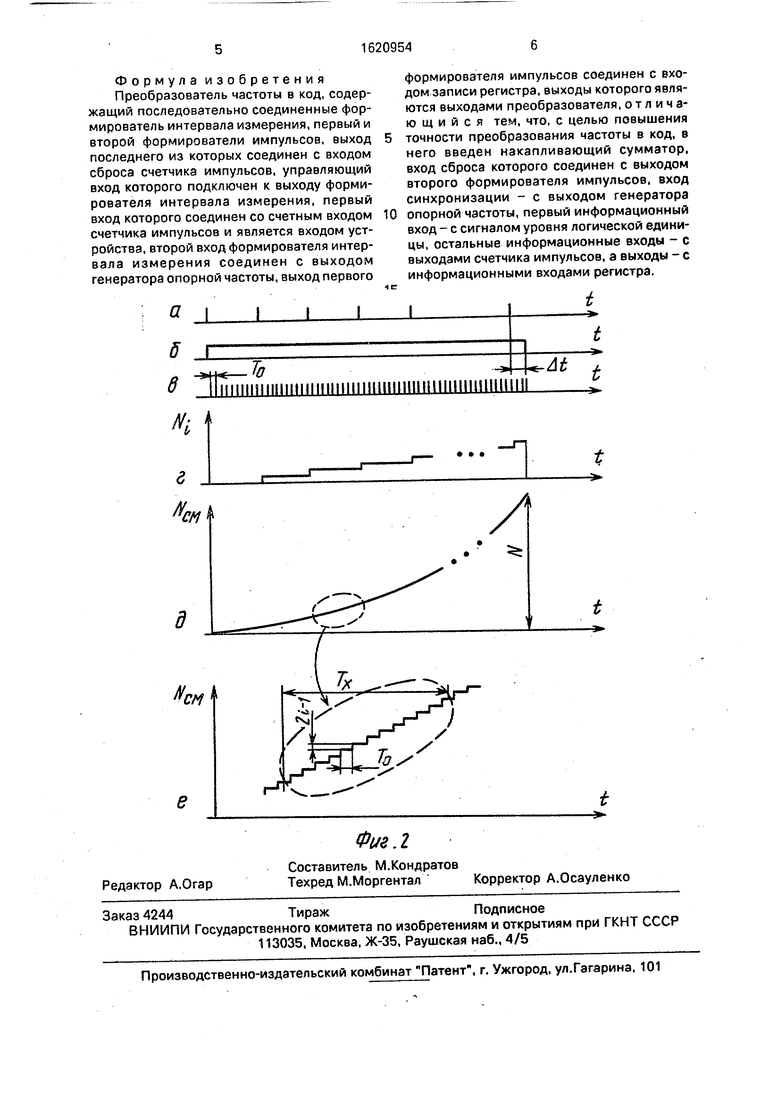

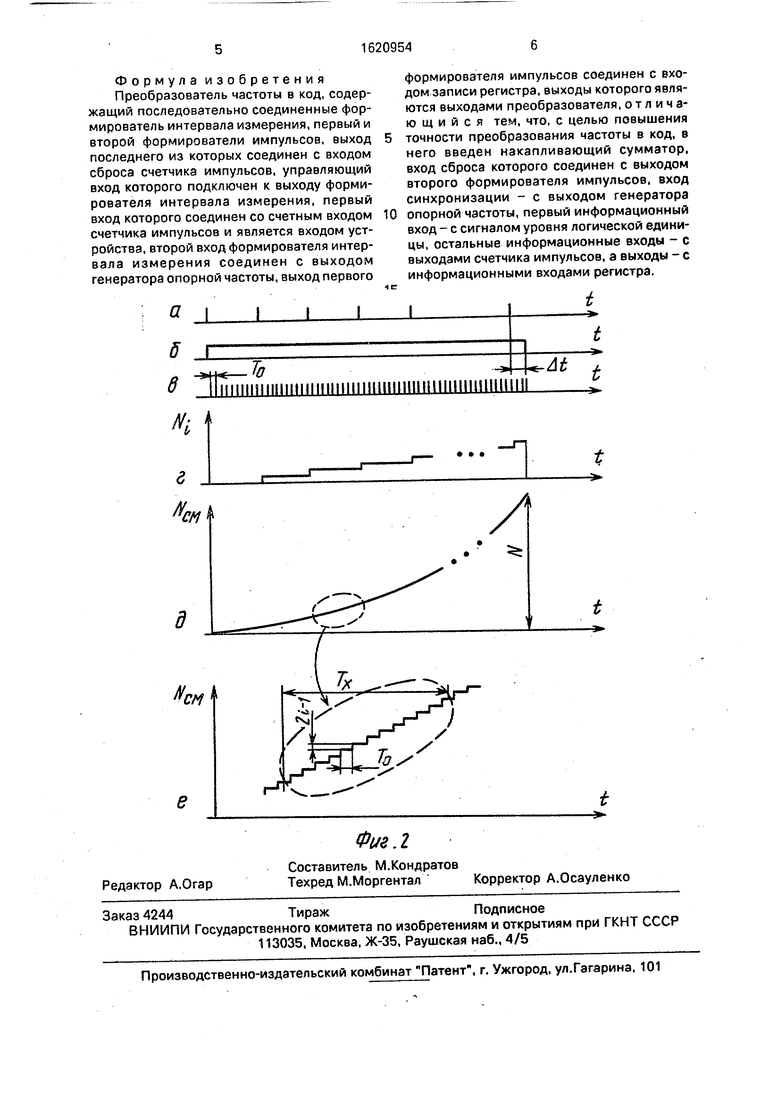

На фиг. 2 представлены временные диаграммы, поясняющие работу преобразователя частоты в код: а - сигнал исходной частоты на входе устройства; б - сигнал на выходе формирователя интервала измерения; в - сигнал на выходе генератора опорной частоты; г - диаграмма смены содержимого счетчика 4 импульсов; д, е - диаграммы формирования результирующего кода в накапливающем сумматоре 6.

Преобразователь частоты в код работает следующим образом.

Формирователь 1 интервала измерения формирует интервал времени Ти (фиг. 26), начало которого совпадает с первым импульсом регистрируемой частоты fx (фиг. 2а). Счетчик 4 импульсов осуществляет подсчет числа импульсов регистрируемой частоты, поступивших за интервал времени

Ти, т.е. в течение интервала времени Ти S- разрядный код NI в счетчике 4 импульсов постепенно возрастает по мере прихода каждого последующего импульса частоты fx

(фиг. 2г). На информационные входы накапливающего сумматора 6 с второго по (5+1)-й подается код NI, а на первый информационный вход подается сигнал уровня логической единицы. Таким образом, код,

образуемый на данных информационных входах, изменяется в моменты поступления импульсов частоты fx по закону арифметической прогрессии

15

1,3,5(21-1),... (1)

На вход синхронизации накапливающего сумматора б поступают импульсы опорной частоты f0 (фиг. 2в), Значение кода

накапливающего сумматора NCM постепенно увеличивается (фиг. 2д), и к концу интервала измерения оно представляет собой результирующий отсчет N. По окончании интервала измерения Ти формирователь 3 вырабатывает импульс, переписывающий накопленное число N на выходе Р-разрядно- го регистра 7. Затем импульсом с выхода формирователя 5 приводятся в нулевое состояние счетчик 4 импульсов и нэкапливающий сумматор 6, подготавливая таким образом устройство к следующему циклу измерения.

Накопление числа N является результатом суммирования значений членов ряда (1),

осуществляемого по поступлении импульсов постоянной опорной частоты fo в течение NT целых периодов Тх в интервале Ти и части последнего, не уместившегося полностью, периода At (фиг. 26):

N +3 + 5 + ... + (2Мт-1) +

+ fo(2NT + 1) At,(2)

или с учетом формулы суммы членов арифметической прогрессии

N fоТхМт2 + f 0(2 NT + 1) A t, (3)

где

At Ти-МтТх Ти--71. TX

(4)

Решая уравнение (4) относительно NT и подставляя результат в уравнение (3), по- следнее приводят к виду

TSfx

AT

Т2и

).

(5)

где TSfx

Аг т2.

(6)

5ф- погрешность измерения, обусловленная отличием номинальной и реальной функций преобразования.

Формула изобретения Преобразователь частоты в код, содержащий последовательно соединенные формирователь интервала измерения, первый и второй формирователи импульсов, выход последнего из которых соединен с входом сброса счетчика импульсов, управляющий вход которого подключен к выходу формирователя интервала измерения, первый вход которого соединен со счетным входом счетчика импульсов и является входом устройства, второй вход формирователя интер- вала измерения соединен с выходом генератора опорной частоты, выход первого

формирователя импульсов соединен с входом записи регистра, выходы которого являются выходами преобразователя, отличающийся тем, что, с целью повышения точности преобразования частоты в код, в него введен накапливающий сумматор, вход сброса которого соединен с выходом второго формирователя импульсов, вход синхронизации - с выходом генератора опорной частоты, первый информационный вход - с сигналом уровня логической единицы, остальные информационные входы - с выходами счетчика импульсов, а выходы - с информационными входами регистра.

| Цифровой частотомер | 1985 |

|

SU1302208A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-01-15—Публикация

1989-01-27—Подача