Изобретение относится к автоматике и вычислительной технике и .может быть использовано при построении устройств программного управления и контроля в специализированных многофункциональных управляющих и вычислительных системах, а также микро-

контроллерных системах для АСУ ТП и группами взаимодействующих объектов. Цель изобретения - расширение области применения устройства за счет обеспечения выполнения функций контроля состояния взаимодействующих модулей в заданные основным алгоритмом моменты времени и соответствующего переключения режима работы системы модулей в случае отклонения значения контролируемых параметров от программных

Введение дополнительных аппаратно-программных средств обеспечивает запрос одним из управляющих модулей значений логических условий из любого другого модуля системы; модификацию адреса перехода, указанного в микрокоманде запрашивающего модуля, и передачу управления по этому адресу; выполнение указанных микроопераций параллельно с основными микрооперациями алгоритма за счет управления содержимым полей микрокоманды с использованием введенной метки - признака режима работы модуля и самого содержимого полей микрокоманды.

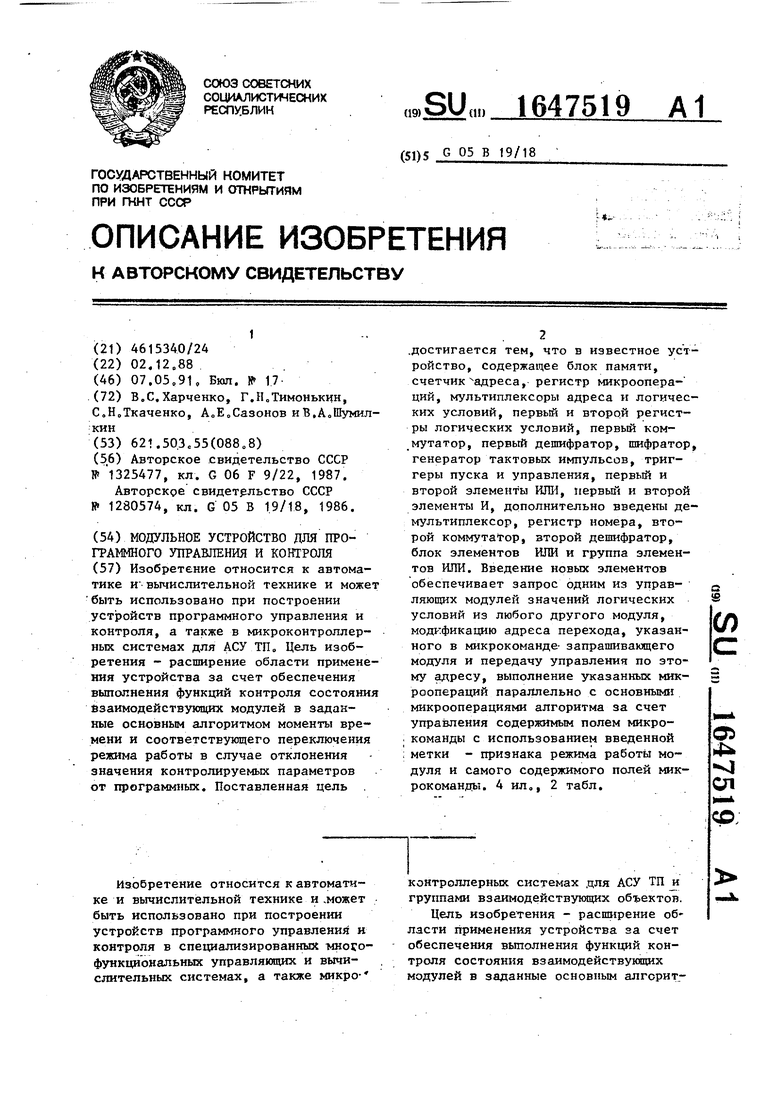

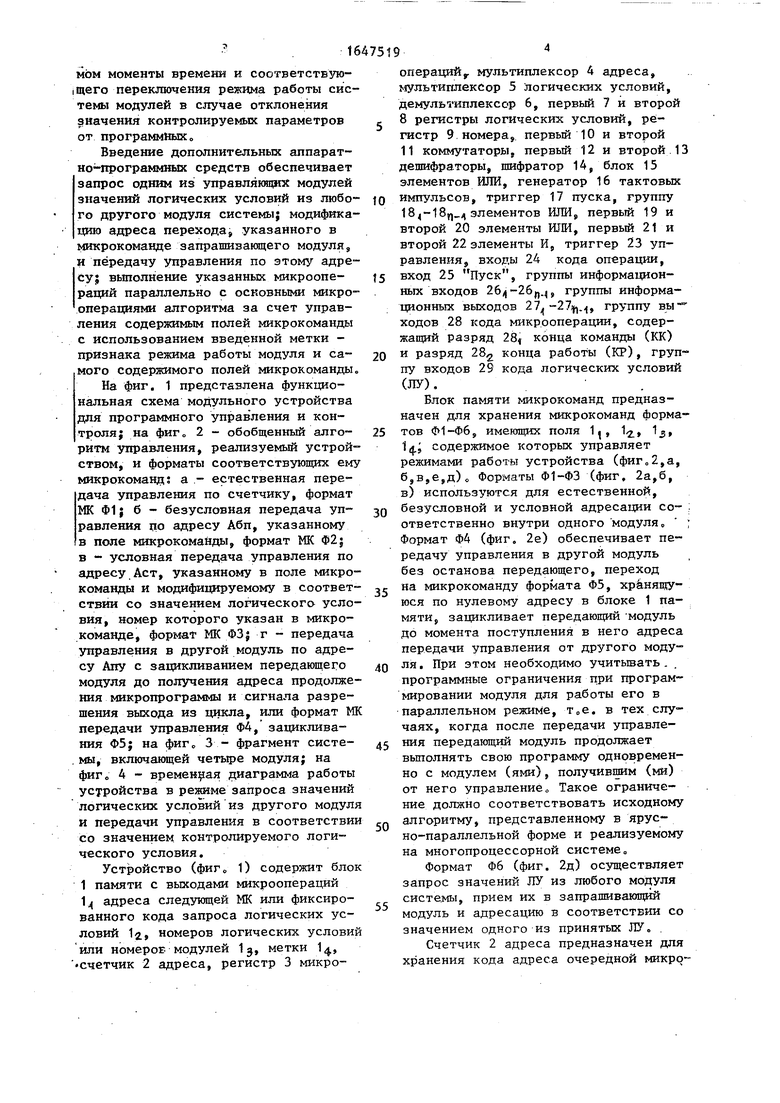

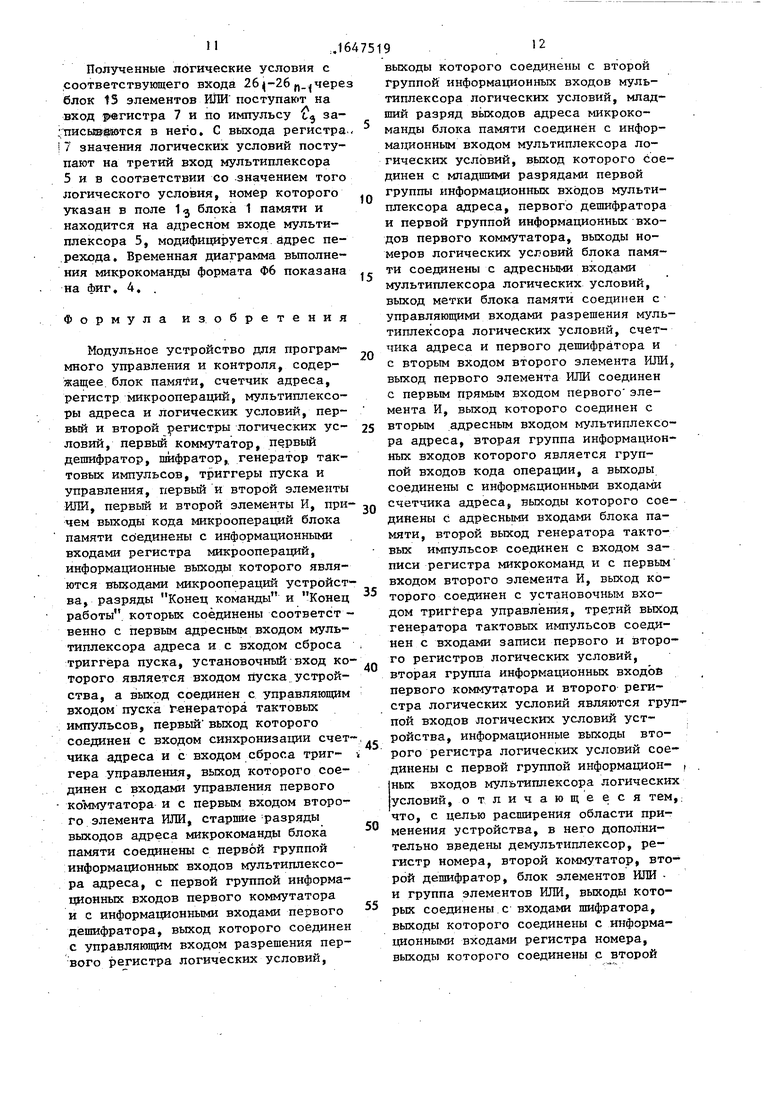

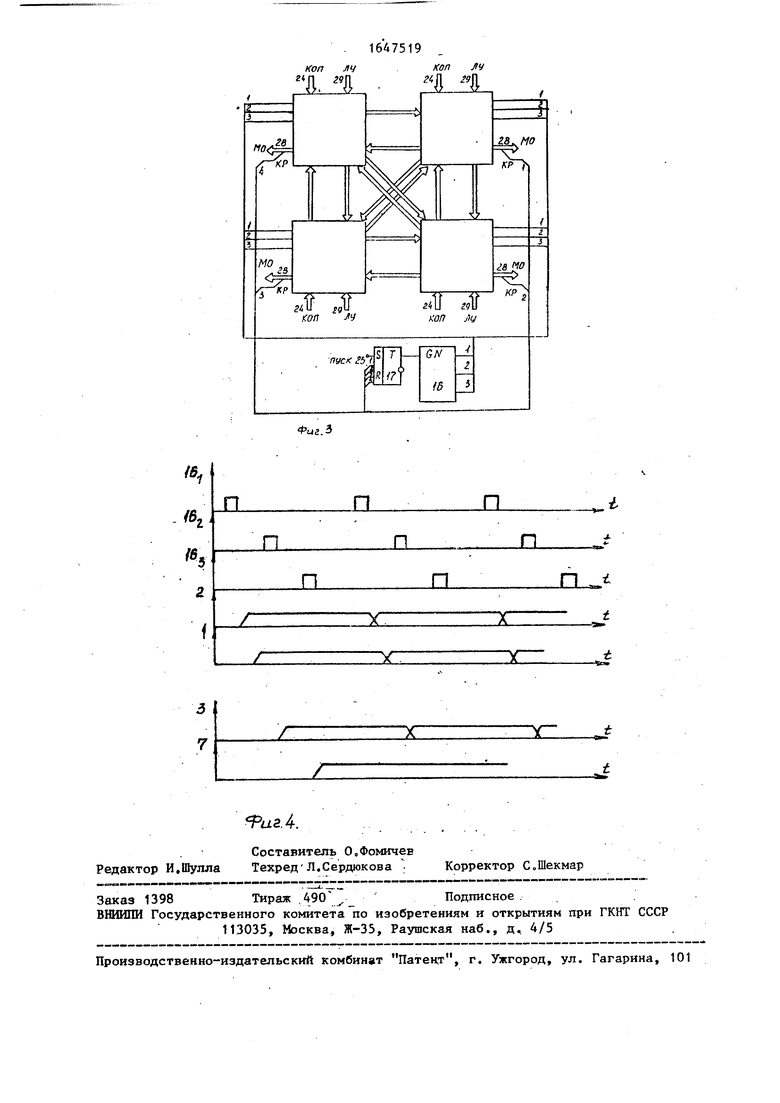

На фиг. 1 представлена функциональная схема модульного устройства для программного управления и контроля; на фиг0 2 - обобщенный алгоритм управления, реализуемый устройством, и форматы соответствующих ему микрокоманд: а - естественная передача управления по счетчику, формат Ж Ф1; б - безусловная передача управления по адресу Абп, указанному в поле микрокоманды, формат Ж Ф2| в - условная передача управления по адресу ACT, указанному в поле микрокоманды и модифицируемому в соответствии со значением логического услокоманде, формат Ж ФЗ; г - передача управления в другой модуль по адресу Any с зацикливанием передающего модуля до получения адреса продолжения микропрограммы и сигнала разрешения выхода из цикла, или формат Ж передачи управления Ф4, зацикливания Ф5; на фиг„ 3 - фрагмент системы, включающей четыре модуля; на фиго 4 - временная диаграмма работы устройства в режиме запроса значений логических условий из другого модуля и передачи управления в соответствии со значением контролируемого логического условия.

Устройство (фиг о 1) содержит блок 1 памяти с выходами микроопераций 1 адреса следующей Ж или фиксированного кода запроса логических условий 1, номеров логических условий или номерог модулей 1, метки 1 счетчик 2 адреса, регистр 3 микро

10

15

20

25

75194

операций,, мультиплексор 4 адреса, мультиплексор 5 логических условий, демультиплексор 6, первый 7 и второй 8 регистры логических условий, регистр 9 номера, первый 10 и второй 11 коммутаторы, первый 12 и второй 13 дешифраторы, шифратор 14, блок 15 элементов ИЛИ, генератор 16 тактовых импульсов, триггер 17 пуска, группу 184-18fl 4элементов ИЛИ, первый 19 и второй 20 элементы ИЛИ, первый 21 и второй 22 элементы И, триггер 23 управления, входы 24 кода операции, вход 25 Пуск, группы информационных входов 26,|-26п.( группы информационных выходов 27 -27.,,, группу вы ходов 28 кода микрооперации, содержащий разряд 284 конца команды (КК) и разряд 282 конца работы (КР), группу входов 29 кода логических условий (ЛУ).

Блок памяти микрокоманд предназначен для хранения микрокоманд Форматов Ф1-Фб, имеющих поля 1, 1, 1, 1ф5 содержимое которых управляет режимами работы устройства (фиг„2,а, б,в,е,д)0 Форматы Ф1-ФЗ (фиг, 2а,б, в) используются для естественной, безусловной и условной адресации соответственно внутри одного модуля Формат Ф4 (фиг. 2е) обеспечивает передачу управления в другой модуль без останова передающего, переход ,г на микрокоманду формата Ф5, хранящуюся по нулевому адресу в блоке 1 памяти, зацикливает передающий модуль до момента поступления в него адреса передачи управления от другого модуля. При этом необходимо учитывать . программные ограничения при программировании модуля для работы его в параллельном режиме, т„е. в тех случаях, когда после передачи управления передающий модуль продолжает выполнять свою программу одновременно с модулем (ями), получившим (ми) от него управление Такое ограничение должно соответствовать исходному алгоритму, представленному в ярус- но-параллельной форме и реализуемому на многопроцессорной системе

Формат Фб (фиг. 2д) осуществляет запрос значений ЛУ из любого модуля системы, прием их в запрашивающий модуль и адресацию в соответствии со значением одного из принятых ЛУ

Счетчик 2 адреса предназначен для хранения кода адреса очередной микро30

40

45

50

55

516

команды, который поступает на его информационный вход с выхода мультиплексора 4 адреса. Запись кода в счетчик 2 адреса осуществляется по заднему фронту тактового импульса С., поступающего на его вход синхронизации с первого выхода генератора 1б„

Регистр 3 микроопераций предназначен для хранения управляющих кодов, поступающих на его вход с выхода 1 блока 1 памяти. Запись кода в регистр 3 микроопераций осуществляется по заднему фронту тактового импульса С2, поступающего на его вход синхрониза- ции с второго выхода генератора 16. Мультиплексор 4 адреса предназначен для выбора направления приема кода адреса следующей микрокоманды.

Состояния входов управления и ин- формационных входов мультиплексора 4 адреса показаны в табл. 1.

Мультиплексор 5 логических условий предназначен для модификации адреса следующей микрокоманды с учетом значения условия, поступающего из блока 1 памяти. При этом состояние управляющего входа мультиплексора 5 обеспечивает его работу в двух режимах (табл. 2).

Таблица 1

Мультиплексор 4 адреса

О 1 О 1

Открыт Закрыт Закрыт Закрыт Закрыт Открыт Закрыт Открыт Закрыт

Входы мультиплексора 5

Таблица2

50

., б„

в, JQ тр 2, - 15

- 20 4

ий 25 а30

35

40

45

50

55

19

Из табл. 2 следует, что при значении метки К- 1 1 устанавливается единичный сигнал на управляющем входе мультиплексора 5. В этом режиме открыт первый вход De мультиплексора 5, а младший разряд кода адреса, не изменяя своего значения, поступает на первый информационный вход первого коммутатора 10. Этим обеспе- чивается передача управления в другой модуль по адресу А пц без модификации младшего разряда. При значении метки %. 1 ф нулевой сигнал на управляющем входе мультиплексора 5 закрывает вход De и открывает второй D и третий DЈ входы мультиплексора 5„ В этом случае младший разряд адреса перехода принимает значение в соответствии со зна- . чением проверяемого ЛУ,

Демультиплексор 6 предназначен для передачи кодов адресов передачи управления фиксированного кода запроса логических условий или значений логических условий из данного модуля в модуль, номер которого указан в микрокоманде, и поступает на адресный вход демультиплексора 6. Во всех этих случаях демультиплексор 6 находится в открытом состоянии за счет единичного сигнала на его управляющем входе, который формируется за счет метки -К- 1 1 при передаче управления или запроса логических условий, а при передаче значений логических условий в запросивший модуль - за счет единичного состояния триггера 23 управления.

Первый регистр 7 логических уело-/ вий принимает значения логических условий из запрошенного модуля с выхода блока 15 элементов ИЛИ.Запись в регистр 7 логических условий осуществляется по заднему фронту сигнала , поступающего с третьего выхода генератора 16 на вход синхронизации. Разрешение записи дает единичный сигнал на управляющем входе регистра 7, поступающий с выхода первого дешифратора 12.

Второй 8 регистр логических условий принимает значения логических условий, формируемые в блоке 1 памяти для данного модуля, и записывает их по заднему фронту сигнала Ј, аналогично первому регистру 7 логичес ких условий.

Регистр 9 номера предназначен для записи по .заднему фронту тактового

импульса v KOfla номера модуля, запросившего значения логических условий с тем, чтобы эти значения передать в соответствующий модуль0.

Первый коммутатор 10 предназначен для передачи адреса управления или фиксированного кода - признака запроса логических условий, или значений логических условий. Управление JQ выбором канала в коммутаторе 10 осуществляется сигналом с выхода триг- / гера 23 управления

Второй коммутатор 11 предназначен для передачи кода номера модуля, по- 15 ступающего из одного из двух направлений: из поля 1д номера модуля выхода блока 1 памяти микрокоманд или из регистра 9 номера. Код номера модуля поступает с выхода второго 20 коммутатора 11 на адресный вход де- мультиплексора 6.

Первый дешифратор 12 предназначен для формирования единичного сигнала

го модуля; прием управления в начальный момент по коду операции, получаемому через второй вход мультиплексора 4 адреса или в ходе работы системы по коду полученного адреса передачи управления Ацу через соответствующие входы 26.-26,ц.уст- ройства на третий вход мультиплексора 4 адреса; выдача запроса на значение логических условий от любого модуля системы и адресация в соответствии со значением; проверяемого логического условия, полученного по запросу; прием запроса на выдачу значений логических условий в запрашиваемый модуль и выдача логических условий

В исходном состоянии все элементы ндмяти обнулены, разряд 28.1 КК имеет единичное состояние. На входе 24 устройства устанавливается код опе- рации, являющийся адресом начала программы,, По тактовому импульсу С. код

адреса в счет- 2 адреса и через время С

За$

в случае поступления на его информа- 7-5& операции записывается через второй ционный вход фиксированного кода - признака запроса логических условий с выхода 1л блока 1 памяти. При этом значение сигнала на управляющем входе первого дешифратора 12 равно логической единице за счет метки -К-1 1.

Второй дешифратор 13 предназначен для формирования единичного сигнала в случае поступления на его вход фиксированного кода признака запроса логических условий при значении сигнала на его управляющем входе, равном логическому нулю,,

Шифратор 14 формирует код номера модуля, запросившего логические условия в соответствии с номером входа шифратора 14, получившего единичный сигнал.

вход мультиплексора 4

чик

(фиг„ 4) на выходе блока 1 памяти

появляется код выбранной микрокоман30 ды. Если она имеет формат Ф1 (фиг.2а) то значение метки устанавливает счетчик 2 адреса в режим счета и по следующему тактовому импульсу ч, текущий адрес увеличивается на

35 единицу

По тактовому импульсу Ј2 код микрооперации записывается в регистр 3 и начинается выполнение микрооперации в операционном блоке. Если выб-

40 ранная микрокоманда имеет формат Ф2, то значение метки #1 ф устанавливает счетчик 2 адреса в режим записи параллельным кодом. Код микрооперации по импульсу Јg записывается Модульное устройство для програм- 45 B регистр 3 и начинается выполнение

микрооперации в операционном блоке. Код адреса безусловной передачи At50

много управления и контроля работает в следующих режимах: выполнение сабственных микропрограмм с контролем собственных логических условий. При этом возможны три вида адресации: естественная передача, безусловный переход, условный переход; передача управления другим модулям системы. При этом возможна передача управления с продолжением собственной микро- 5ь программы (в момент передачи адрес следующей МК формируется по счетчику) или с зацикливанием передающего модуля до получения управления от другопоступает через первый вход мультиплексора 4 адреса на вход счетчика 2 адреса и по очередному импульсу Vg. записывается в этот счетчик,

Если выбранная микрокоманда имеет формат ФЗ, то за счет метки обеспечивается прием адреса в счетчик 2 адреса параллельным кодом. По импульсу $2 К°Д микрооперации записывается в регистр 3 и начинается выполнение микрооперации в операционном блоке К у.менту импульса &$

го модуля; прием управления в начальный момент по коду операции, получаемому через второй вход мультиплексора 4 адреса или в ходе работы системы по коду полученного адреса передачи управления Ацу через соответствующие входы 26.-26,ц.уст- ройства на третий вход мультиплексора 4 адреса; выдача запроса на значение логических условий от любого модуля системы и адресация в соответствии со значением; проверяемого логического условия, полученного по запросу; прием запроса на выдачу значений логических условий в запрашиваемый модуль и выдача логических условий

В исходном состоянии все элементы ндмяти обнулены, разряд 28.1 КК имеет единичное состояние. На входе 24 устройства устанавливается код опе- рации, являющийся адресом начала программы,, По тактовому импульсу С. код

адреса в счет- 2 адреса и через время С

За$

операции записывается через второй

вход мультиплексора 4

чик

(фиг„ 4) на выходе блока 1 памяти

появляется код выбранной микрокоманды. Если она имеет формат Ф1 (фиг.2а) то значение метки устанавливает счетчик 2 адреса в режим счета и по следующему тактовому импульсу ч, текущий адрес увеличивается на

единицу

По тактовому импульсу Ј2 код микрооперации записывается в регистр 3 и начинается выполнение микрооперации в операционном блоке. Если выб-

ранная микрокоманда имеет формат Ф2, то значение метки #1 ф устанавливает счетчик 2 адреса в режим запи

поступает через первый вход мультиплексора 4 адреса на вход счетчика 2 адреса и по очередному импульсу Vg. записывается в этот счетчик,

Если выбранная микрокоманда имеет формат ФЗ, то за счет метки обеспечивается прием адреса в счетчик 2 адреса параллельным кодом. По импульсу $2 К°Д микрооперации записывается в регистр 3 и начинается выполнение микрооперации в операционном блоке К у.менту импульса &$

91

формируются логические условия, которые поступают на вход 29 устройств По импульсу Og логические условия записываются во второй регистр 8 логических условий и поступают на второй вход мультиплексора 5, который открыт за счет метки 1 (j) 0 На входе адреса мультиплексора 5 находится код номера проверяемого логического условия, значение соответствующего логического условия поступает на выход мультиплексора 5 и этим модифицирует младший разряд кода адреса перехода. По очередному импульсу $ адрес перехода записывается через первый вход мультиплексора 4 адреса в счетчик 2 адреса,

Если выбранная микрокоманда имеет формат Ф4, то запись микрооперации и ее выполнение осуществляются аналогично При этом номер модуля, куда должно быть передано управление, поступает через открытый первый вход второго коммутатора 11 на адресный вход демультиплексора 6, выбирая соответствующее направление передачи адреса перехода Адрес перехода пступает через открытый первый вход первого коммутатора 10 на информационный вход демультиплексора бив соответствующую шину,

В принимающем модуле код адреса перехода поступает с одного из входо ( перез блок 15 элементов ИЛИ на третий вход мультиплексора 4 адреса и вход первого элемента ИЛИ 19, с выхода которого единичный сигнал через первый элемент И 21 поступает на второй управляющий вход мультиплексора 4 адреса (табл. 1), открывается третий вход мультиплексора 4 адреса Таким образом, принимающий модуль начнет выполнение программы с указанного адреса.

В передающем модуле при этом возможно продолжение собственной программы, так как в момент передачи управления обеспечивается естественная адресация. Возможно также зацикливание передающего модуля до получения управления от другого модуля Для этого после микрокоманды формата Ф4 в блок 1 памяти записывается микрокоманда формата Ф2, имеющая в поле адреса нулевое содержимое. Переход на нулевой адрес обеспечивает зацикливание модуля, так как в нем записана микрокоманда формата Ф5, от

19

10

to

15

0

25

30

35

40

45

0

5

личающаяся от микрокоманды формата Ф2 тем, что в поле микроопераций записано нулевое состояние, не вызывающее никаких действий в операционном блоке.

Если выбранная микрокоманда имеет формат Фб, инициирующий запрос значений логических условий из другого модуля системы, то в поле 1 адреса микрокоманды находится фиксированный код - признак запроса логических условий, а в поле 1 ,, блока 1 памяти находится код номера модуля, из которого запрашиваются логические условия. Этот код поступает через первый вход второго коммутатора 11 на адресньй вход демультиплексора 6 и подготавливает соответствующее направление передачи кода - запроса.

Фиксированный код поступает через первый вход первого коммутатора 10 на информгционный вход демультиплексора 6 и по соответствующей шине на запрашиваемый модуль. Кроме того, фиксированный код поступает на первый дешифратор 12, единичный сигнал на выходе которого открывает регистр 7, подготавливая его к приему запрошенных логических усповий. Модуль, принявший фиксированный код - запрос, через один из входов 26|-26Г).и блок 15 элементов ИЛИ, принимает его на вход второго дешифратора 13, единичный сигнал на выходе которого по импульсу ч; через второй элемент И 22 устанавливает в единичное состояние триггер 23 управления, чем обеспечивается открытие вторых входов первого 10 и второго 11 коммутаторов в запрошенном модуле.

Одновременно с этим единичный сигнал на выходе соответствующего элемента ИЛИ группы 18ц-18п- элементов ИЛИ, поступая на вход пифратора 14, формирует на его выходе код номера модуля, запросившего значение логических условий, этот код по импульсу записывается в регистр 9 номера и поступает через второй вход второго коммутатора 11 на вход адреса демультиплексора 6, открывая этим выход в модуль, запросивший логические условия. Логические усговия из запрошенного модуля через второй вход первого коммутатора 10 поступают на информационный вход демультиплексора и по соответствующей шине в модуль, выставивший запрос.

11.1647519

Полученные логические условия с ответствующего входа п,через ок 15 элементов ИЛИ поступают на од регистра 7 и по импульсу засываются в него. С выхода регистра . значения логических условий постуют на третий вход мультиплексора и в соответствии со значением того гического условия, номер которого азан в поле 1 блока 1 памяти и ходится на адресном входе мультиексора 5, модифицируется адрес пехода. Временная диаграмма выполнея микрокоманды формата Ф6 показана фиг, 4.

10

15

в г т г д г пл и д м ти вы у ти ч с вы с м в р ны п с с ди вы пи вх т д г н г в п с п р р д н у ч м т ги р и ры вы ци вы

Формула изобретения

Модульное устройство для программного управления и контроля, содержащее блок памяти, счетчик адреса, регистр микроопераций, мультиплексоры адреса и логических условий, первый и второй регистры логических условий, первый коммутатор, первый дешифратор, шифратор, генератор тактовых импульсов, триггеры пуска и управления, первый и второй элементы ИЛИ, первый и второй элементы И, при- чем выходы кода микроопераций блока памяти соединены с информационными входами регистра микроопераций, информационные выходы которого являются выходами микроопераций устройства, разряды Конец команды и Конец работы которых соединены соответст - венно с первым адресным входом мультиплексора адреса и с входом сброса триггера пуска, установочный вход которого является входом пуска устрой

входом пуска генератора тактовых импульсов, первый выход которого соединен с входом синхронизации счетчика адреса и с входом сброса триг- гера управления, выход которого соединен с входами управления первого коммутатора и с первым входом второго элемента ИЛИ, старшие разряды выходов адреса микрокоманды блока памяти соединены с первой группой информационных входов мультиплексора адреса, с первой группой информационных входов первого коммутатора и с информационными входами первого дешифратора, выход которого соединен с управляющим входом разрешения первого регистра логических условий,

12

0

5

0

5

Q

5

0

5

0

5

выходы которого соединены с второй группой информационных входов мультиплексора логических условий, младший разряд выходов адреса микрокоманды блока памяти соединен с информационным входом мультиплексора логических условий, выход которого соединен с младшими разрядами первой группы информационных входов мультиплексора адреса, первого дешифратора и первой группой информационных входов первого коммутатора, выходы номеров логических условий блока памяти соединены с адресными входами мультиплексора логических условий, выход метки блока памяти соединен с управляющими входами разрешения мультиплексора логических условий, счетчика адреса и первого дешифратора и с вторым входом второго элемента ИЛИ выход первого элемента ИЛИ соединен с первым прямым входом первого элемента И, выход которого соединен с вторым адресным входом мультиплексора адреса, вторая группа информационных входов которого является группой входов кода операции, а выходы соединены с информационными входами счетчика адреса, выходы которого соединены с адресными входами блока памяти, второй выход генератора тактовых импульсор соединен с входом записи регистра микрокоманд и с первым входом второго элемента И, выход которого соединен с установочным входом триггера управления, третий выход генератора тактовых импульсов соединен с входами записи первого и второго регистров логических условий, вторая группа информационных входов первого коммутатора и второго регистра логических условий являются группой входов логических условий устройства, информационные выходы второго регистра логических условий соединены с первой группой информацион- t ных входов мультиплексора логических условий, отличающееся тем, что, с целью расширения области применения устройства, в него дополнительно введены демультиштексор, регистр номера, второй коммутатор, второй дешифратор, блок элементов ИЛИ и группа элементов ИЛИ, выходы которых соединены с входами шифратора, выходы которого соединены с информационными входами регистра номера, выходы которого соединены с второй

группой информационных вхрдов второго коммутатора, выходы которого соединены с адресными входами демульти- плексора, выходы которого являются группами информационных выходов устройства, группы входов логических условий устройства соединены с входами соответствующих элементов ИЛИ группы и с соответствующими группами входов блока элементов ИЛИ, выходы которого соединены с третьей группой информационных входов мультиплексора адреса, с входами первого элемента ИЛИ, с информационными входами первого регистра логических условий и информационными входами второго дешифратора, выход которого соединен с вторым сходом второго элемента

И и с вторым инверсным входом первого элемента И, выход второго элемента И соединен с входом записи регистра номера, выход первого дешифратора соединен с инверсным управляющим входом разрешения второго дешифратора, выход второго элемента ИЛИ соединен с управляющим входом демуль- типлексора, информационные входы которого соединены с выходами первого коммутатора, прямой выход триггера управления соединен с прямым и инверсным управляющими входами разрешения второго коммутатора, первая группа информационных входов которого соединена с выходами номеров логических условий блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств программного управления и контроля, а также в микроконтроллерных системах для АСУ ТП„ Цель изобретения - расширение области применения устройства за счет обеспечения выполнения функций контроля состояния взаимодействующих модулей в заданные основным алгоритмом моменты времени и соответствующего переключения режима работы в случае отклонения значения контролируемых параметров от программных. Поставленная цель достигается тем, что в известное устройство, содержащее блок памяти, счетчикхадреса, регистр микроопераций, мультиплексоры адреса и логических условий, первый и второй регистры логических условий, первый коммутатор, первый дешифратор, шифратор, генератор тактовых импульсов, триггеры пуска и управления, первый и второй элементы ИЛИ, первый и второй элементы И, дополнительно введены де- мультиплексор, регистр номера, второй коммутатор, второй дешифратор, блок элементов ИЛИ и группа элементов ИЛИ. Введение новых элементов обеспечивает запрос одним из управляющих модулей значений логических условий из любого другого модуля, модификацию адреса перехода, указанного в микрокоманде запрашивающего модуля и передачу управления по этому адресу, выполнение указанных микроопераций параллельно с основными микрооперациями алгоритма за счет управления содержимым полем микрокоманды с использованием введенной метки - признака режима работы модуля и самого содержимого полей микрокоманды. 4 ил„, 2 табл. ма 8 (Л с& 4 3 СП со,

Фиг.1

о

ш r-.

r

vO

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-05-07—Публикация

1988-12-02—Подача