Изобретение относится к вычислительной технике и может использоваться в системах функционального диагностирования.

Цель изобретения - повышение достоверности контроля.

Сущность изобретения состоит в повышении достоверности контроля программ за счет обеспечения трех типов контроля. Первый - контроль правильности начала программы с первой микрокоманды реализуется благодаря наличию кодовой комбинации (заполнения 1 поля кода логического условия) в первой микрокоманде. При начале программы с любой другой микрокоманды отсутствие кодовой комбинации будет являться источником сигнала ошибки. Второй - контроль на четность - реализуется с помощью специального контрольного разряда, содержащегося в микрокоманде и дополняющего количество 1 в

микрокоманде до четного. Нечетное число 1 является источником сигнала ошибки. Третий - контроль методом сравнения с эталоном. Этот контроль является поразрядным. Сущность его заключается в поочередной коммутации выходов проверяемых разрядов с группой элементов, формирующих, в зависимости от значений этих разрядов, специальную контрольную кодовую комбинацию - сигнатуру и сравнении ее с эталонной, содержащейся в одной, заранее определенной микрокоманде.

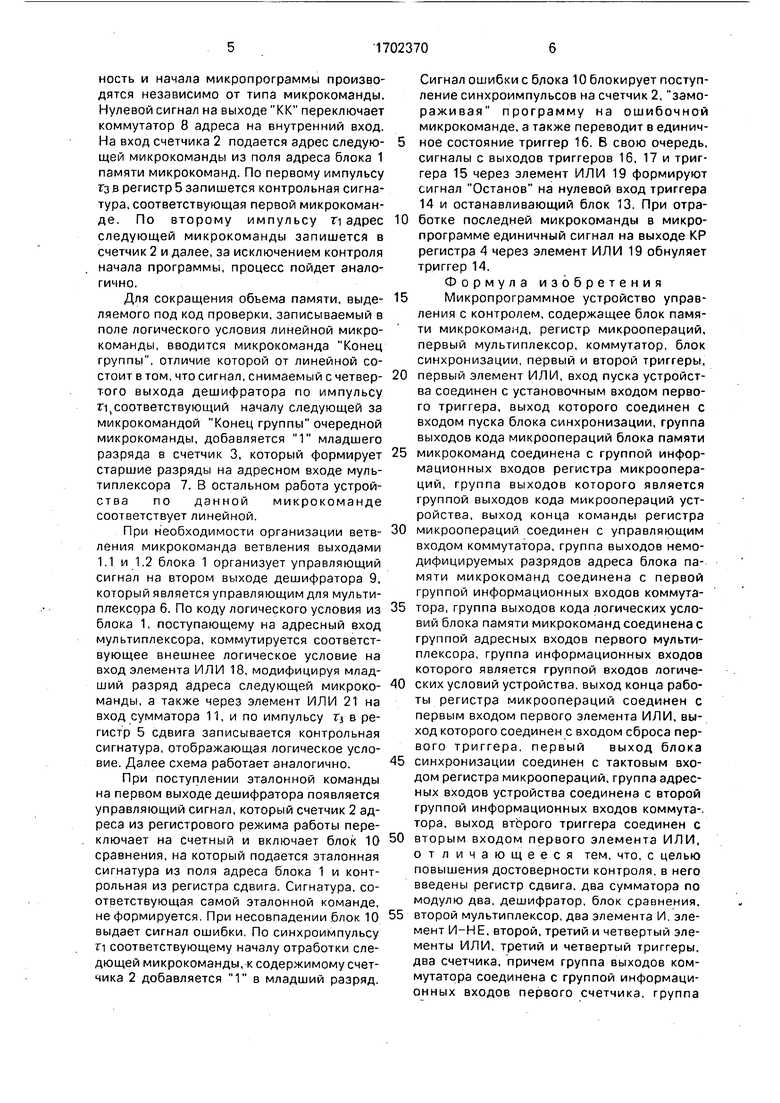

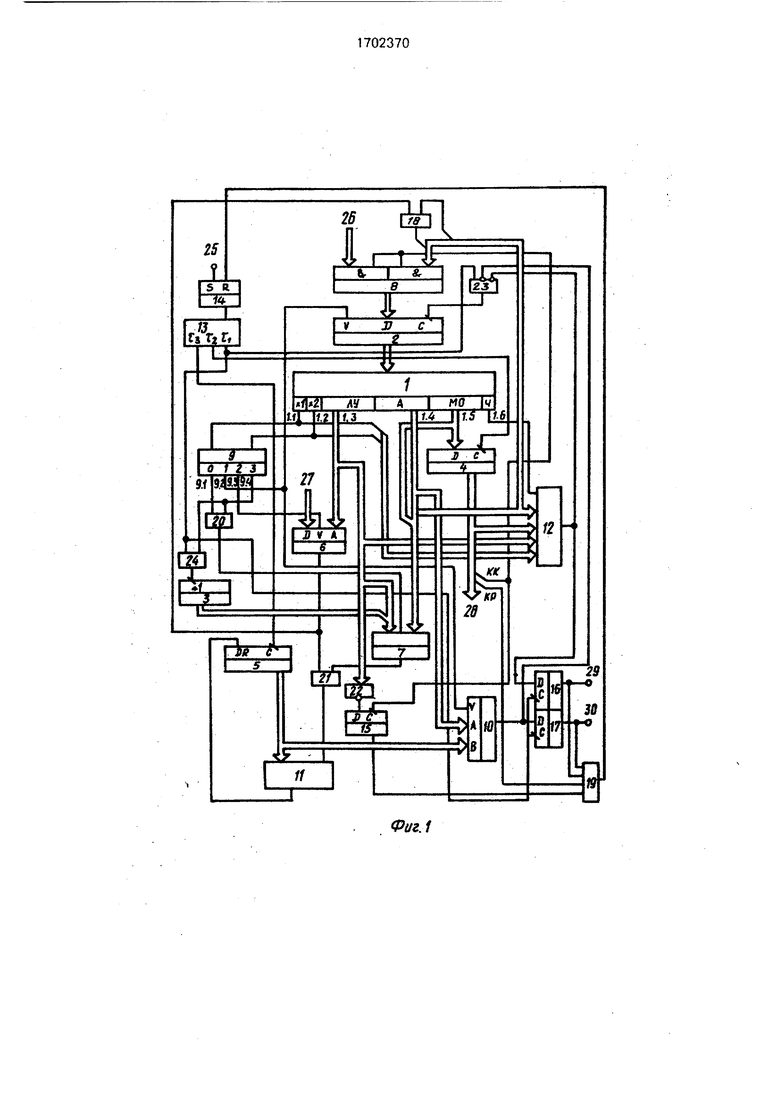

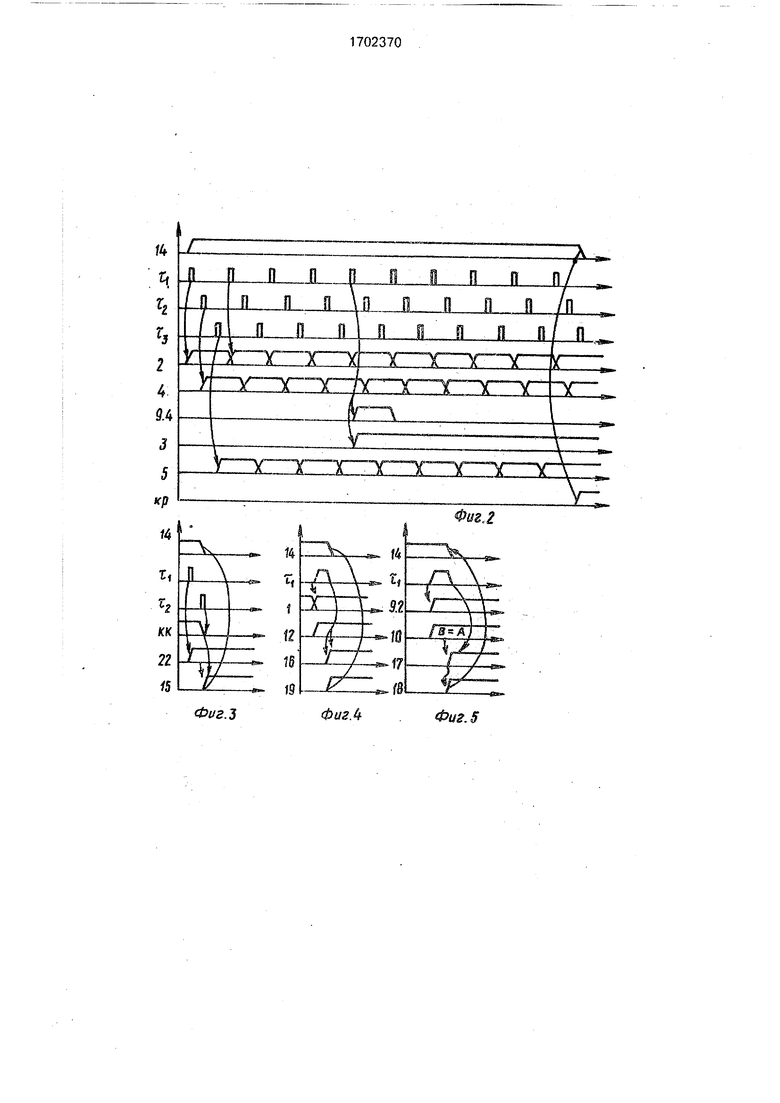

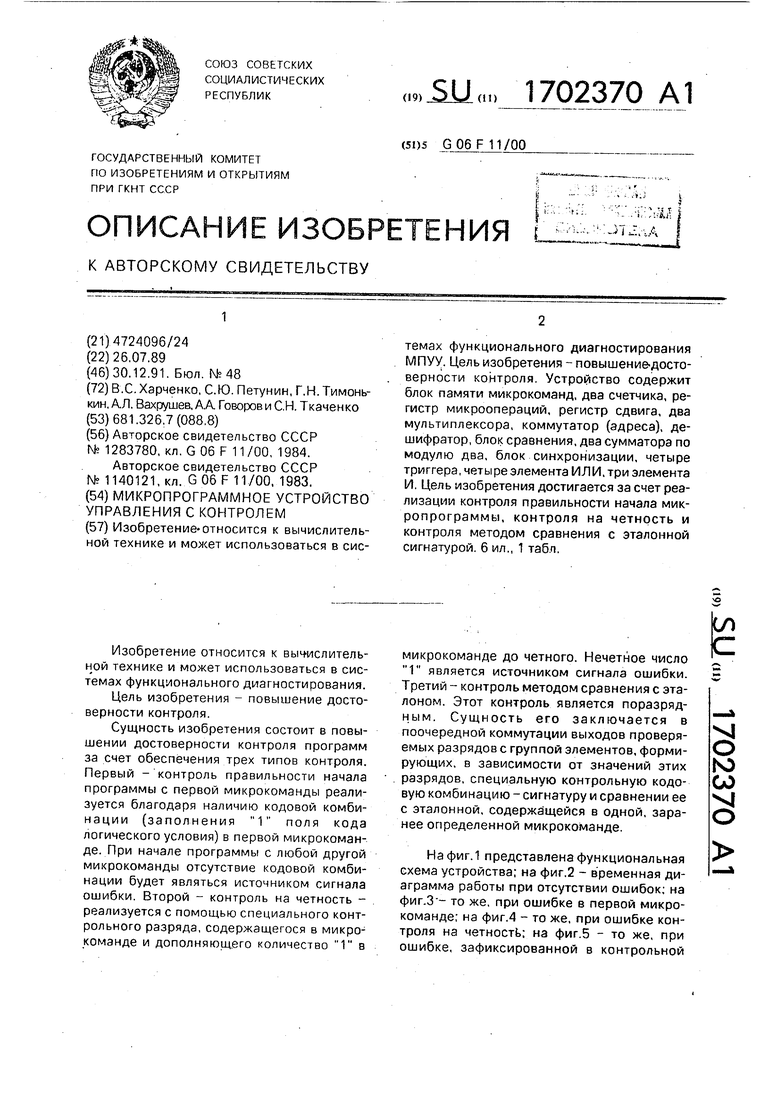

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - временная диаграмма работы при отсутствии ошибок; на фиг. то же, при ошибке в первой микрокоманде; на фиг.4 - то же, при ошибке контроля на четность; на фиг.5 - то же, при ошибке, зафиксированной в контрольной

сл

с

ч|

о

го со

3

сигнатуре; на фиг.6 - вариант формирования контрольной сигнатуры.

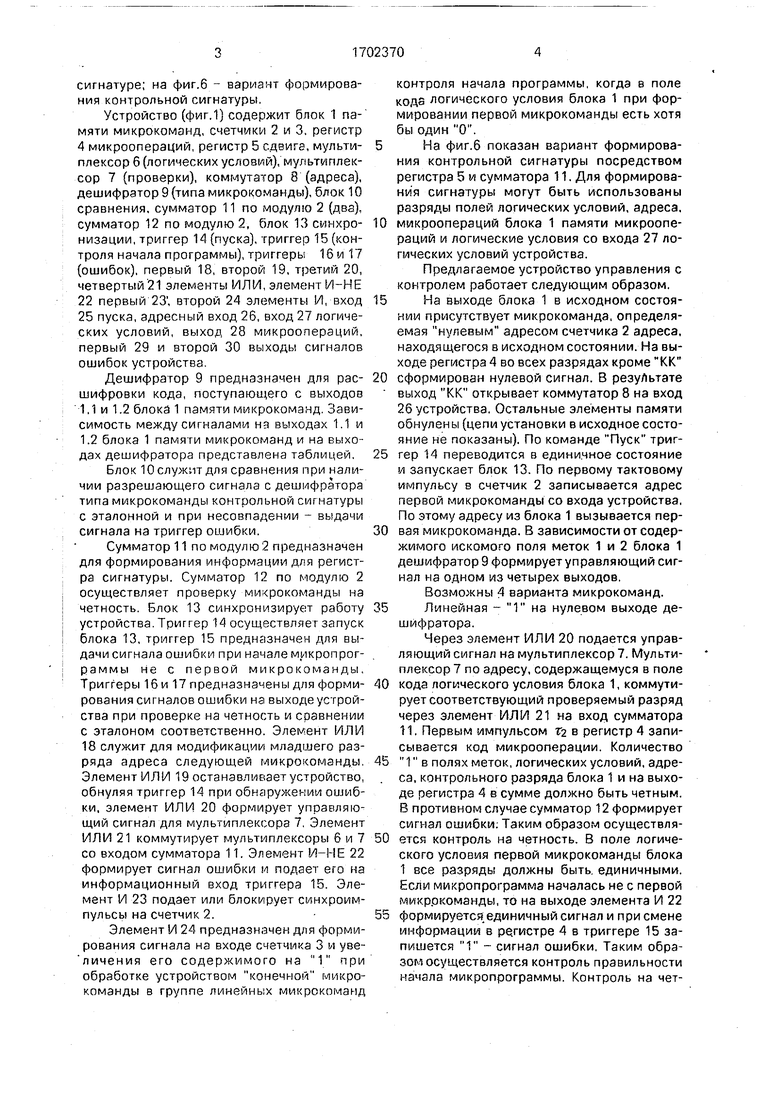

Устройство (фиг.1) содержит блок 1 па- мяти микрокоманд, счетчики 2 и 3, регистр 4 микроопераций, регистр 5 сдвиге, мультиплексор б (логических условий), мультиплексор 7 (проверки), коммутатор 8 (адреса), дешифратор 9 (типа микрокоманды), блок 10 сравнения, сумматор 11 по модулю 2 (два). сумматор 12 по модулю 2, блок 13 синхронизации, триггер 14 (пуска), триггер 15 (контроля начала программы), триггеры 16 и 17 (ошибок), первый 18, второй 19, третий 20, четвертый 21 элементы ИЛИ, элемент И-НЕ 22 первый 23, второй 24 элементы И, вход 25 пуска, адресный вход 26, вход 27 логических условий, выход 28 микроопераций, первый 29 и второй 30 выходы сигналов ошибок устройства.

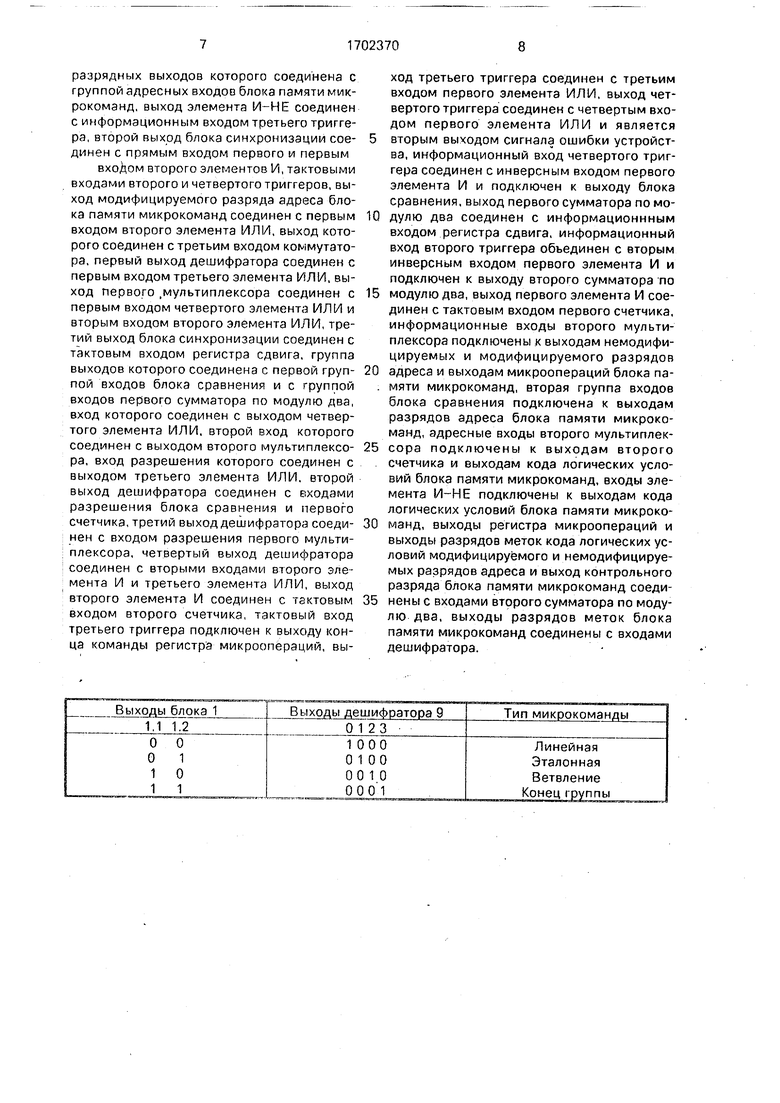

Дешифратор 9 предназначен для расшифровки кода, поступающего с выходов

1.1и 1.2 блоки 1 памяти микрокоманд. Зависимость между сигналами на выходах 1.1 и

1.2блока 1 памяти микрокоманд и на выходах дешифратора представлена таблицей.

Блок 10 служит для сравнения при наличии разрешающего сигнала с дешифратора типа микрокоманды контрольной сигнатуры с эталонной и при несовпадении - выдачи сигнала на триггер ошибки.

Сумматор 11 по модулю 2 предназначен для формирования информации для регистра сигнатуры. Сумматор 12 по модулю 2 осуществляет проверку микрокоманды на четность. Блок 13 синхронизирует работу устройства. Триггер 14 осуществляет запуск блока 13, триггер 15 предназначен для выдачи сигнала ошибки при начале микропрог- раммы не с первой микрокоманды. Триггеры 16 и 17 предназначены для формирования сигналов ошибки на выходе устройства при проверке на четность и сравнении с эталоном соответственно. Элемент ИЛИ 18 служит для модификации младшего разряда адреса следующей микрокоманды. Элемент ИЛИ 19 останавливает устройство, обнуляя триггер 14 при обнаружении ошибки, элемент ИЛИ 20 формирует управляющий сигнал для мультиплексора 7. Элемент ИЛИ 21 коммутирует мультиплексоры 6 и 7 со входом сумматора 11. Элемент И-НЕ 22 формирует сигнал ошибки и подает его на информационный вход триггера 15. Элемент И 23 подает или блокирует синхроимпульсы на счетчик 2.

Элемент И 24 предназначен для формирования сигнала на входе счетчика 3 и уве- личения его содержимого на 1 при обработке устройством конечной микрокоманды в группе линейных микрокоманд

контроля начала программы, когда в поле коде логического условия блока 1 при формировании первой микрокоманды есть хотя бы один О.

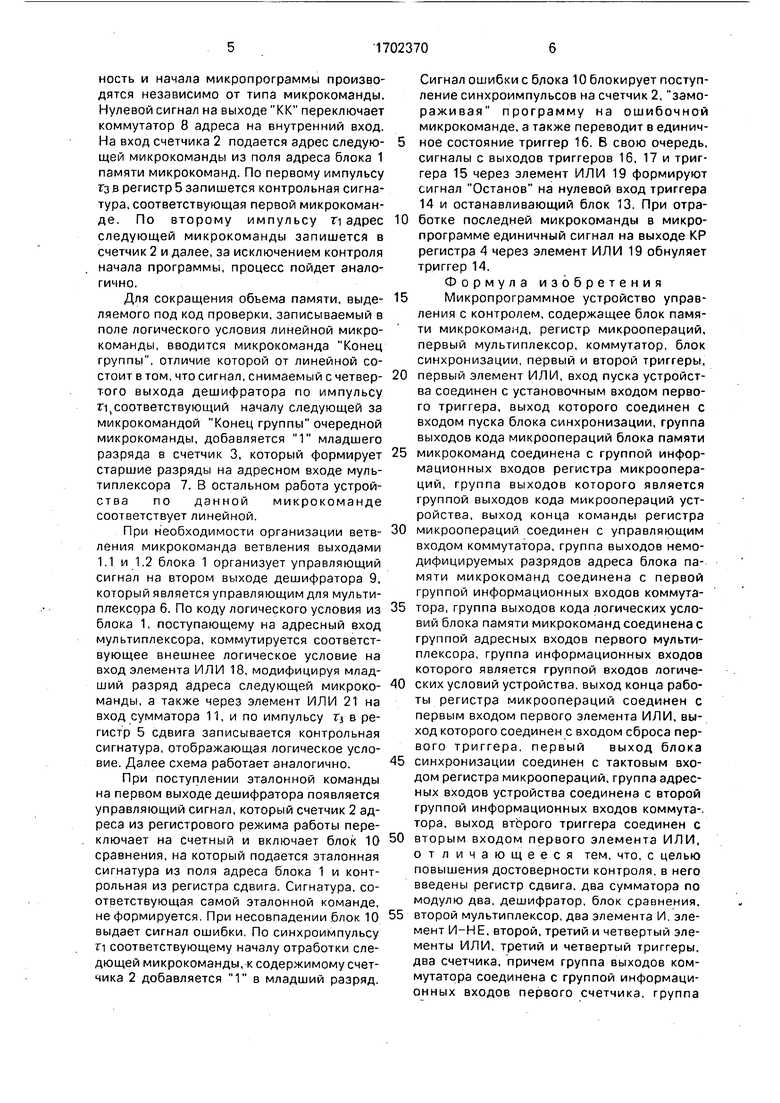

На фиг.6 показан вариант формирования контрольной сигнатуры посредством регистра 5 и сумматора 11. Для формирования сигнатуры могут быть использованы разряды полей логических условий, адреса,

микроопераций блока 1 памяти микроопераций и логические условия со входа 27 логических условий устройства.

Предлагаемое устройство управления с контролем работает следующим образом.

На выходе блока 1 в исходном состоянии присутствует микрокоманда, определяемая нулевым адресом счетчика 2 адреса, находящегося в исходном состоянии. На выходе регистра 4 во всех разрядах кроме КК

сформирован нулевой сигнал. В результате выход КК открывает коммутатор 8 на вход 26 устройства. Остальные элементы памяти обнулен ы (цепи установки в исходное состояние не показаны). По команде Пуск триггер 14 переводится в единичное состояние и запускает блок 13. По первому тактовому импульсу в счетчик 2 записывается адрес первой микрокоманды со входа устройства, По этому адресу из блока 1 вызывается первая микрокоманда. В зависимости от содержимого искомого поля меток 1 и 2 блока 1 дешифратор 9 формирует управляющий сигнал на одном из четырех выходов.

Возможны 4 варианта микрокоманд.

Линейная - 1 на нулевом выходе дешифратора.

Через элемент ИЛИ 20 подается управляющий сигнал на мультиплексор 7. Мультиплексор 7 по адресу, содержащемуся в поле

кода логического условия блока 1, коммутирует соответствующий проверяемый разряд через элемент ИЛИ 21 на вход сумматора 11, Первым импульсом Тг в регистр 4 записывается код микрооперации. Количество

1 в полях меток, логических условий, адре- са, контрольного разряда блока 1 и на выходе регистра 4 в сумме должно быть четным. В противном случае сумматор Сформирует сигнал ошибки; Таким образом осуществляется контроль на четность. В поле логического условия первой микрокоманды блока 1 все разряды должны быть, единичными. Если микропрограмма началась не с первой микрркоманды, то на выходе элемента И 22

формируется единичный сигнал и при смене информации в регистре 4 в триггере 15 запишется 1 - сигнал ошибки. Таким образом осуществляется контроль правильности начала микропрограммы. Контроль на четность и начала микропрограммы производятся независимо от типа микрокоманды. Нулевой сигнал на выходе КК переключает коммутатор 8 адреса на внутренний вход. На вход счетчика 2 подается адрес следующей микрокоманды из поля адреса блока 1 памяти микрокоманд. По первому импульсу Гз в регистр 5 запишется контрольная сигнатура, соответствующая первой микрокоманде. По второму импульсу п адрес следующей микрокоманды запишется в счетчик 2 и далее, за исключением контроля начала программы, процесс пойдет аналогично.

Для сокращения объема памяти, выделяемого под код проверки, записываемый в поле логического условия линейной микрокоманды, вводится микрокоманда Конец группы, отличие которой от линейной состоит в том, что сигнал, снимаемый с четвертого выхода дешифратора по импульсу П(соответствующий началу следующей за микрокомандой Конец группы очередной микрокоманды, добавляется 1 младшего разряда в счетчик 3, который формирует старшие разряды на адресном входе мультиплексора 7. В остальном работа устройства по данной микрокоманде соответствует линейной.

При необходимости организации ветвления микрокоманда ветвления выходами 1.1 и 1.2 блока 1 организует управляющий сигнал на втором выходе дешифратора 9. который является управляющим для мультиплексора 6. По коду логического условия из блока 1, поступающему на адресный вход мультиплексора, коммутируется соответствующее внешнее логическое условие на вход элемента ИЛИ 18, модифицируя младший разряд адреса следующей микрокоманды, а также через элемент ИЛИ 21 на вход сумматора 11, и по импульсу г в регистр 5 сдвига записывается контрольная сигнатура, отображающая логическое условие. Далее схема работает аналогично.

При поступлении эталонной команды на первом выходе дешифратора появляется управляющий сигнал, который счетчик 2 адреса из регистрового режима работы переключает на счетный и включает блок 10 сравнения, на который подается эталонная сигнатура из поля адреса блока 1 и контрольная из регистра сдвига. Сигнатура, соответствующая самой эталонной команде, не формируется. При несовпадении блок 10 выдает сигнал ошибки. По синхроимпульсу ri соответствующему началу отработки сле- дющей микрокоманды, к содержимому счетчика 2 добавляется 1 в младший разряд.

Сигнал ошибки с блока 10 блокирует поступление синхроимпульсов на счетчик 2, замо- раживая программу на ошибочной микрокоманде, а также переводит в единич- ное состояние триггер 16. В свою очередь, сигналы с выходов триггеров 16, 17 и триггера 15 через элемент ИЛИ 19 формируют сигнал Останов на нулевой вход триггера 14 и останавливающий блок 13. При отра0 ботке последней микрокоманды в микропрограмме единичный сигнал на выходе КР регистра 4 через элемент ИЛИ 19 обнуляет триггер 14.

Формула изобретения

5 Микропрограммное устройство управления с контролем, содержащее блок памяти микрокоманд, регистр микроопераций, первый мультиплексор, коммутатор, блок синхронизации, первый и второй триггеры,

0 первый элемент ИЛИ. вход пуска устройства соединен с установочным входом первого триггера, выход которого соединен с входом пуска блока синхронизации, группа выходов кода микроопераций блока памяти

5 микрокоманд соединена с группой информационных входов регистра микроопераций, группа выходов которого является группой выходов кода микроопераций устройства, выход конца команды регистра

0 микроопераций соединен с управляющим входом коммутатора, группа выходов немодифицируемых разрядов адреса блока памяти микрокоманд соединена с первой группой информационных входов коммута5 тора, группа выходов кода логических условий блока памяти микрокоманд соединена с группой адресных входов первого мультиплексора, группа информационных входов которого является группой входов логиче0 ских условий устройства, выход конца работы регистра микроопераций соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом сброса первого триггера, первый выход блока

5 синхронизации соединен с тактовым входом регистра микроопераций, группа адресных входов устройства соединена с второй группой информационных входов коммута-. тора, выход второго триггера соединен с

0 вторым входом первого элемента ИЛИ. отличающееся тем, что, с целью повышения достоверности контроля, в него введены регистр сдвига, два сумматора по модулю два, дешифратор, блок сравнения,

5 второй мультиплексор, два элемента И. элемент И-НЕ. второй, третий и четвертый элементы ИЛИ, третий и четвертый триггеры, два счетчика, причем группа выходов коммутатора соединена с группой информационных входов первого счетчика, группа

разрядных выходов которого соединена с группой адресных входов блока памяти микрокоманд, выход элемента И-НЕ соединен с информационным входом третьего триггера, второй выход блока синхронизации сое- динен с прямым входом первого и первым входом второго элементов И, тактовыми входами второго и четвертого триггеров, выход модифицируемого разряда адреса блока памяти микрокоманд соединен с первым входом второго элемента ИЛИ, выход которого соединен с третьим входом коммутатора, первый выход дешифратора соединен с первым входом третьего элемента ИЛИ, выход первого.мультиплексора соединен с первым входом четвертого элемента ИЛИ и вторым входом второго элемента ИЛИ, третий выход блока синхронизации соединен с тактовым входом регистра сдвига, группа выходов которого соединена с первой труп- пой входов блока сравнения и с группой входов первого сумматора по модулю два, вход которого соединен с выходом четвертого элемента ИЛИ, второй вход которого соединен с выходом второго мультиплексо- ра, вход разрешения которого соединен с выходом третьего элемента ИЛИ. второй выход дешифратора соединен с входами разрешения блока сравнения и первого счетчика, третий выход дешифратора соеди- нен с входом разрешения первого мультиплексора, четвертый выход дешифратора соединен с вторыми входами второго элемента И и третьего элемента ИЛИ, выход второго элемента И соединен с тактовым входом второго счетчика, тактовый вход третьего триггера подключен к выходу конца команды регистра микроопераций, выход третьего триггера соединен с третьим входом первого элемента ИЛИ, выход четвертого триггера соединен с четвертым входом первого элемента ИЛИ и является вторым выходом сигнала ошибки устройства, информационный вход четвертого триггера соединен с инверсным входом первого элемента И и подключен к выходу блока сравнения, выход первого сумматора по модулю два соединен с информационнным входом регистра сдвига, информационный вход второго триггера объединен с вторым инверсным входом первого элемента И и подключен к выходу второго сумматора по модулю два, выход первого элемента И соединен с тактовым входом первого счетчика, информационные входы второго мультиплексора подключены к выходам немодифицируемых и модифицируемого разрядов адреса и выходам микроопераций блока памяти микрокоманд, вторая группа входов блока сравнения подключена к выходам разрядов адреса блока памяти микрокоманд, адресные входы второго мультиплексора подключены к выходам второго счетчика и выходам кода логических условий блока памяти микрокоманд, входы элемента И-НЕ подключены к выходам кода логических условий блока памяти микрокоманд, выходы регистра микроопераций и выходы разрядов меток кода логических условий модифицируемого и немодифицируемых разрядов адреса и выход контрольного разряда блока памяти микрокоманд соединены с входами второго сумматора по модулю два, выходы разрядов меток блока памяти микрокоманд соединены с входами дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

Изобретение-относится к вычислительной технике и может использоваться в системах функционального диагностирования МПУУ. Цель изобретения - повышение-достоверности контроля. Устройство содержит блок памяти микрокоманд, два счетчика, регистр микроопераций, регистр сдвига, два мультиплексора, коммутатор (адреса), дешифратор, блок сравнения, два сумматора по модулю два, блок синхронизации, четыре триггера, четыре элемента ИЛИ. три элемента И. Цель изобретения достигается за счет реализации контроля правильности начала микропрограммы, контроля на четность и контроля методом сравнения с эталонной сигнатурой. 6 ил., 1 табп.

олегои

Фиг.З

Фиг Л

Фиг. 5

4S

3 ft

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-30—Публикация

1989-07-26—Подача