Изобретение относится к вычислительной технике и может быть использовано при построении арифметических узлов.

Целью изобретения является повышение достоверности работы устройства.

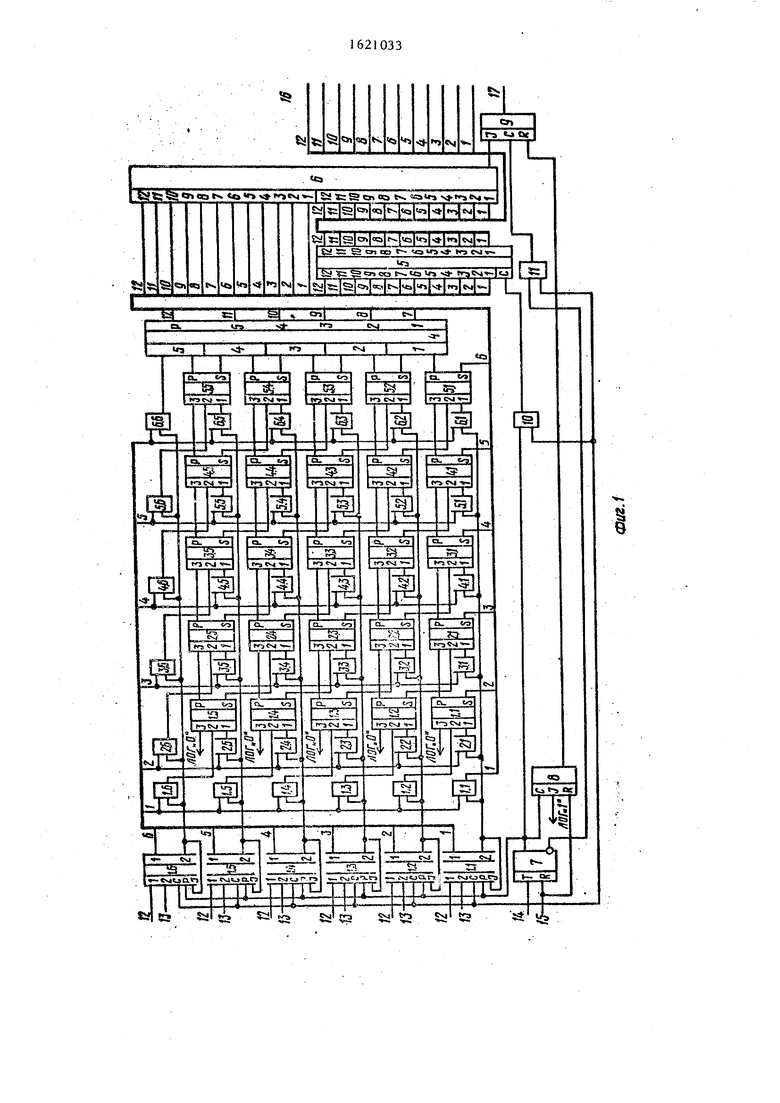

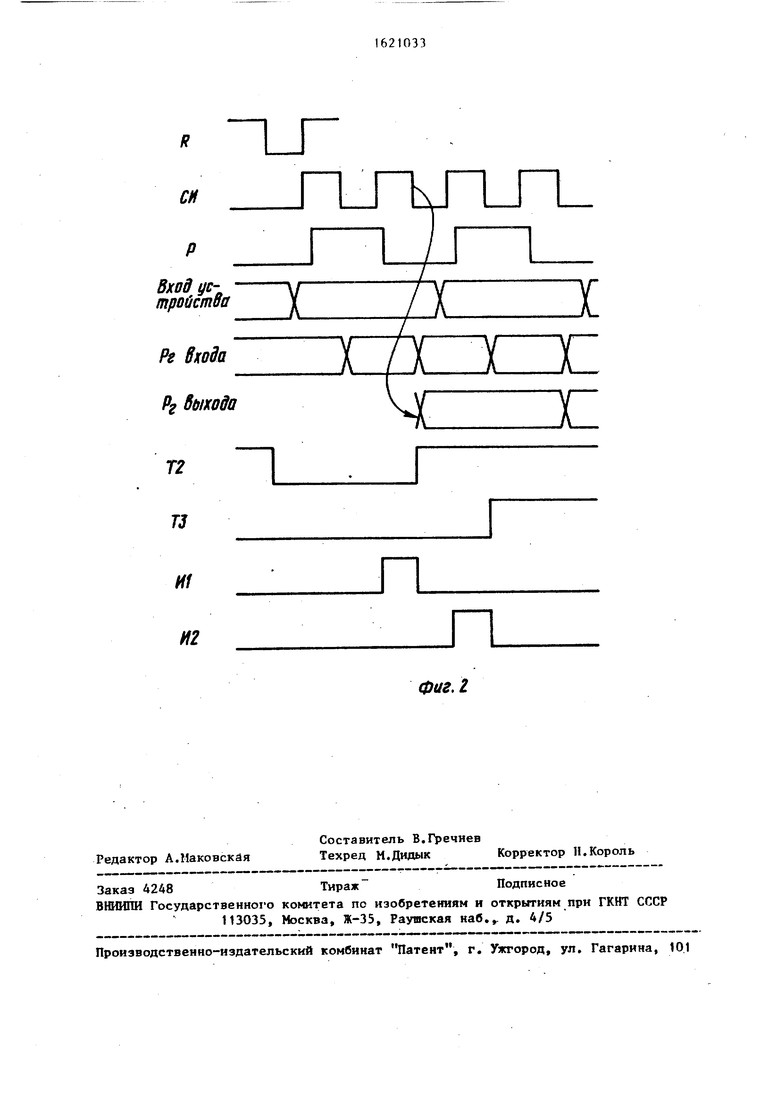

На фиг.1 приведена функциональная схема устройства для шестиразрядных сомножителей; на фиг.2 - временная диаграмма его работы.

Устройство (фиг.1) содержит группу 1 регистров, матрицу 2 элементов И, матрицу 3 сумматоров, сумматор 4, выходной регистр 5, узел 6 сравнения, триггеры 7-9, элементы И 10, 11j входы 12, 13 множимого и множителя устройства соответственно, тактовый 14

и установочный 15 входы устройства, информационный выход 16 устройства, контрольный выход 17 устройства.

Устройство работает следующим образом.

На входы 12 и 13 устройства поступают множимое и множитель соответственно. Па тактовый вход 14 устройства подаются синхроимпульсы типа меандр. Импульс, поступающий на установочный вход 15 устройства в начале работы, устанавливает в нулевое состояние первый 7 и второй 8 триггеры.

В момент времени Т1 по заднему фронту синхроимпульса происходит приО

ьэ

ОЭ

со

ем разрядов множимого и множителя в регистры группы 1.

Режим приема обеспечивается нулевым значением сигнала Р на входах задания режима работы регистров группы 1, поступающего с прямого выхода первого триггера 7. С выходов регистров группы 1 разряды множимого и множителя поступают соответственно на первые и вторые входы элементов И матрицы 2, которые определяют конъюнкции разрядов множимого и множителя. Конъюнкция с выходов элементов II каждой j-й строки (j + 1)-ro столбца матрицы 2 поступает на первый информационный вход сумматора j-й строки j-ro столбца матрицы 3 (1 : j иг (п-1),где п - разрядность множимого и множителя).

Конъюнкция с выходов элементов И (j + 1)-fi строки первого столбца матрицы 2 поступает на вторые входы сумматоров j-й строки первого столбца матрицы 3.

На вторые входы сумматоров k-й строки каждого столбца матрицы 3, начиная с второго, поступают сигналы с выхода суммы сумматора (k + 1)-й строки предыдущего столбца матрицы 3 (1 6 ).

На вторые входы сумматоров (п-1)строки каждого столбца матрицы 3, начиная с второго,поступают конъюнкции с выходов элементов И n-й строки предыдущего столбца матрицы 2.

Третьи входы сумматоров первого столбца матрицы 3 подключены к шине нулевого потенциала устройства. Третьи входы сумматоров всех столбцов матрицы 3 соединены с выходами переноса соответствующих сумматоров предыдущего столбца матрицы 3.

На сумматоре 4 суммируются сигналы с выходов суммы и переноса сумматоров (п-1)-го столбца матрицы 3 и выходов элемента И n-й строки п-го столбца матрицы 2, причем в k-м раз- ряде сумматора А складываются выход переноса сумматора k-й строки и выхо суммы сумматора (k+1)-u строки (п - - 1)-го столбца матрицы 3.

С выхода сумматора 4 снимаются старшие разряды (с седьмого по двенадцатый) произведения, а младшие разряды произведения (с первого по шестой) снимаются с выхода элемента И первой строки первого столбца мат

6210334

рицы 2 и выходов суммы сумматоров первой строки матрицы 3.

Все 12 разрядов произведения пос ступают на информационный вход выходного регистра 5 и записываются в него по сигналу с выхода элемента И 10 в момент 12 по заднему фронту синхроимпульса.

Ю По этому фронту синхросигнала

происходит циклический сдвиг содержимого регистров группы 1. Режим сдвига определяется единичным сигналом на прямом выходе триггера 7.

15 Таким образом,меняются местами множимое и множитель. Вычисление повторяется, но результат произведения в регистр 5 не записывается, а поступает на первый информационный

20 вход узла 6 сравнения, где сравнивается с предыдущим результатом, записанным в регистре 5. При несравнении устанавливается в единичное состояние триггер 9 и на контрольном выхо25 де 16 устройства формируется единичный сигнал, говорящий о неисправности устройства.

0

5

0

5

0

5

Формула изобретения

Устройство для умножения чисел с контролем, содержащее матрицу элементов И размерности пхп (п - разрядность сомножителей), матрицу сумматоров размерности (п-1)х(п-1) и сумматор, причем выход каждого элемента И j-й строки (j+1)-ro столбца матрицы соединен с первым информационным входом сумматора j-й строки j-ro столбца матрицы (1 -Sj п-1), второй информационный вход сумматора (п-1)-й строки j-ro столбца соединен с выходом элемента И n-й строки j-ro столбца матрицы, выход суммы сумматора р-й строки k-ro столбца матрицы соединен с вторым информационным входом сумматора (р-1)-й строки (k-H)-ro столбца матрицы (2 $ р (п-1); 1 $ k n-2), выход переноса каждого сумматора j-й строки k-ro столбца матрицы соединен с третьим информационным входом сумматора j-й строки (k+1)-ro столбца матрицы, второй ин- формапионный вход сумматора j-rt строки первого столбца матрицы соединен с выходом элемента И (j-H)-ft строки первого столбца матрицы, третий информационный вход сумматора первой строки матрицы подключен к шине ну5

левого потенциала устройства, выход переноса сумматора j-й строки (п - - 1)-го столбца матрицы соединен с j-м разрядом входа первого слагаемого сумматора, k-й разряд входа второго слагаемого сумматора соединен с выходом суммы сумматора (k+1)-ft строки (п-1)-го столбца матрицы, выход элемента II n-й ст.роки п-го столбца матрицы соединен с последним разрядом входа второго слагаемого сумматора, отличающееся тем что, с целью повышения достоверности работы устройства, в него введены группа регистров ,выходной регистр, узел сравнения, два элемента И и три триггера, причем первые и вторые разряды информационных входов регистров группы подключены к соответствующим разрядам входа множимого и входа множителя устройства соответственно, выход первого разряда 1-го регистра группы (1 jЈ i n) соединен с первыми входами всех элементов И 1-го столбца матрицы, выход второго разряда 1-го регистра группы соединен с вторыми входами всех элементов И i-й строки матрицы, тактовые входы регистров группы, счетный вход первого триггера и первые входы первого и второго элементов И подключен к тактовому входу устройства, выход второго разряда 1-го регистра группы соединен с последовательным вхо

10

101136

дом i-ro регистра группы, установочные входы первого и второго триггеров подключены к установочному входу устройства, прямой выход первого триг- триггера соединен с вторым входом первого элемента И, тактовым входом второго триггера и входами задания рекима работы регистров группы, нн- весний выход первого триггера соединен с вторым входом второго элемента И, выход первого элемента И соединен с тактовым входом выходного регистра, выход элемента И первой строjr ки первого столбца матрицы, выходы суммы сумматоров первой строки матрицы и выходы суммы и выходы переноса сумматора соединены с соответствующими информационными входами выход-.

20 ного регистра и соответствующими разрядами первого информационного входа узла сравнения, выход несрав- непил которого соединен с информационным входом третьего триггера,

25 выход которого является контрольным выходом устройства, выход второго элемента И и прямой выход второго триггера соединены с тактовым и установочным входами третьего триггера соответственно, выход выходного регистра соединен с вторым информационным входом узла сравнения и является информационным выходом устройства, информационный вход второго триггера подключен к шине единично3$ го потенциала устройства.

30

Ре входа

i

Рг Ьыкодо

пг г

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство для контроля умножения двоичных чисел по модулю три | 1988 |

|

SU1774337A1 |

| Устройство для умножения | 1982 |

|

SU1137463A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1608653A1 |

| Устройство умножения булевых матриц | 1980 |

|

SU959063A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Устройство для умножения | 1988 |

|

SU1571574A1 |

| Устройство для контроля по модулю @ =2 @ -1 умножения матриц чисел | 1985 |

|

SU1339565A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических узлов. Цель изобретения - повышение достоверности работы устройства. Устройство содержит группу регистров, матрицу элементов И, матрицу сумматоров, сумматор, выходной регистр, узел сравнения, триггеры, элементы И. Сомножители поступают на входы множимого и множителя устройства и записываются в регистр группы (по одному разряду каждого сомножителя в регистр) по синхроимпульсу с тактвого входа устропстиа. Результат вычислений записывается в выходной регистр. Затем происходит циклический сдвиг информации врегистрах группы,в результате чего меняются местами сомножители.Новый результат вычислений сравнивается узлом сравнения с содержимым выходного регистра. При неравенстве двух результатов триггер устанавливается в одиночное состояние, что говорит об ошибке в работе устройства. 2 ил. /) с

фае. 2

| Устройство для умножения | 1984 |

|

SU1203512A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Самофалов К.Г | |||

| и др | |||

| Прикладная теория цифровых автоматов | |||

| Киев: школа, 1987, с.95. | |||

Авторы

Даты

1991-01-15—Публикация

1988-05-17—Подача