Изобретение относится к вычислительной технике и может быть использовано при построении аппаратуры контроля и диагностики арифметических устройств.

Цель изобретения - расширение диагностических возможностей устройства.

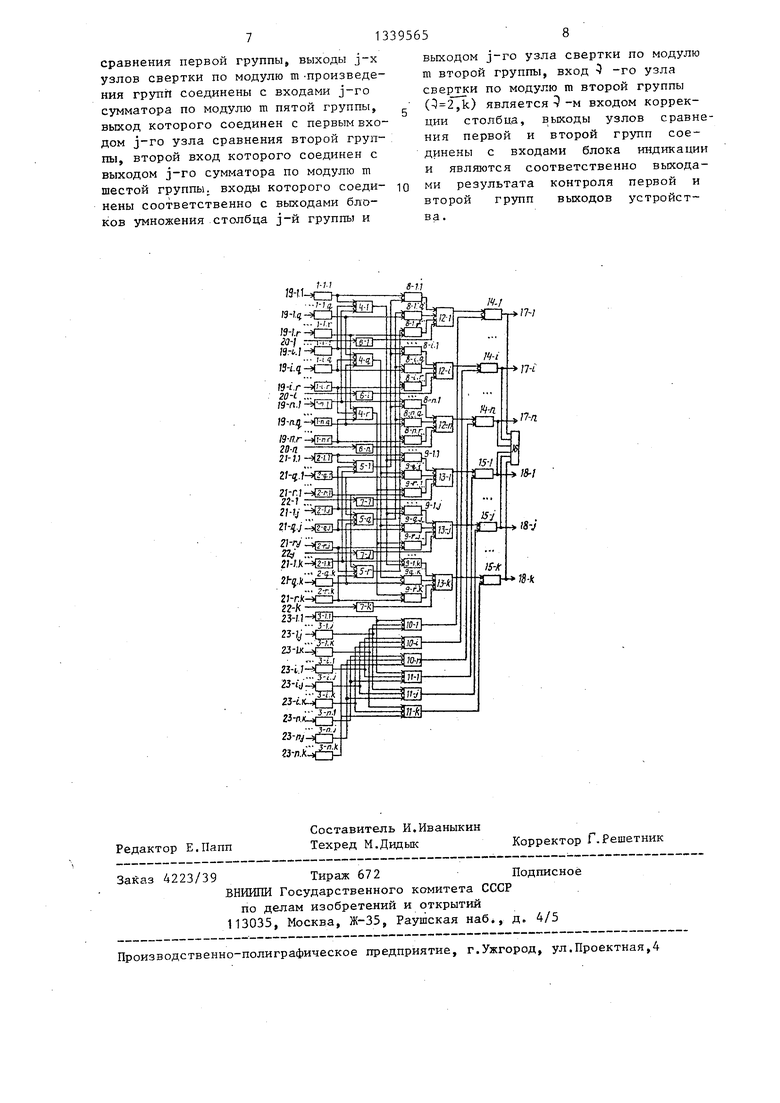

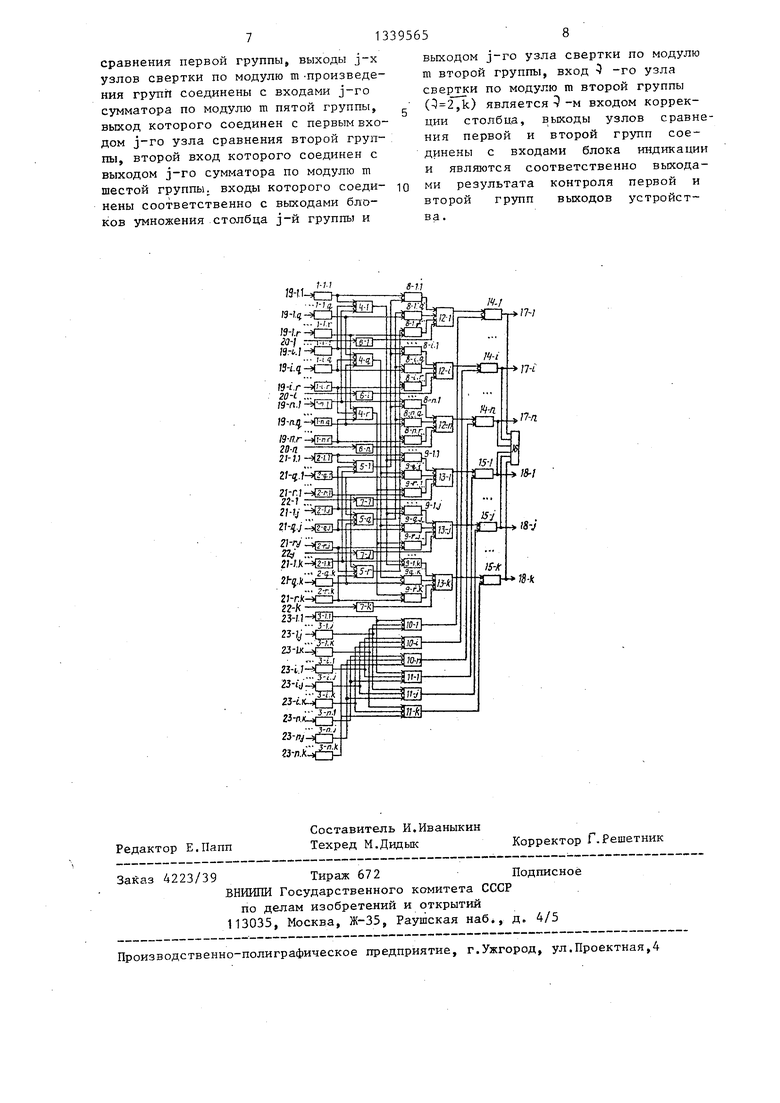

На чертеже изображено предлагае- мое устройство.

Устройство содержит п групп уз- JIOB по модулю m множимого 1-1.1,..,, .q, ..., 1-n.r, k групп узлов свертки по модулю m множителя 2-1.1, ..., 2-q.j2-r.k. n групп узлов свертки по модулю m произведения 3-1. 1,..., 3-i., ..., 3-n.k, четвертую и вторую группы сумматоров по модулю m 4-1, ..., 4-q, ..., 4-r и 5-1, ..., 5-q, ..., 5-r, первую и вторую группы узлов свертки по модулю m 6-1, ..., 6-i, ..., 6-n и 7-lj, ..., 7-j, ..., 7-k, n групп блоков

8-1.18-i.q, ..., 8-n.r умно-

жения строки, k групп блоков 9-1.1,, ..., 9-q.j, ..., 9-r.k умножения столбца, первую, пятую, третью и шестую группы сумматоров по модулю m 10-1, ..., 10-i, ..., 10-n, 11-1, ..., 11-j, ...., 11-k, 12-1, -...,12..., 12-П и 13-1, ..., 13-j, ..., 13-k, первую и вторую группы узлов

сравнения 14-1,...., 14-i14-п

и 15-115-J, ..., 15-k, блок

16 индикации, первую и вторую группы выходов 17-1, ..., 17-i, .,., 17-п и 18-1, ..., 18-J, ..., 18-k устройства, входы 19-1.1, ..., 19-i.q, ... 19-n.r элементов строк множимого уст ройства, группу входов коррекции стрки 20-1, ..., 20-i, ..., 20-п устройства, входы 21-1.1, ..., 21-q.j,... 21-r.k элементов столбцов множителя устройства, группу входов коррекции столбца 22-1, ..., 22-, ..., 22-k устройства, входы 23-1.1, ...,23-i.

. .., 23-n.k.

..

Устройство работает следующим образом.

На входы 19-1.1, ..., 19-i.q, ... 19-n.r элементов строк множимого устройства, являющиеся входами соответствующих узлов свертки по модулю m множимого, поступают коды элементов

а„а;-, ..., а; n-г матрицы

множимого. На выходах узлов свертки по модулю m множимого 1-1.1, ..., 1-i.q, ..., 1-n.r формируются кон

трольные коды соответствуюидах элементов ka,, , ... 5 ka , . . . , ка .

На входы 21-1.1, ..., 21-q.j,..., 21-r.k элементов столбцов множителя устройства, являющиеся входами соответствующих узлов свертки по модулю m множителя, поступают коды элеменr k матритов b

Ci 1

, b.

цы множителя. На выходах узлов свертки по модулю m множителя 2-1.1, . .. , ..., 2-r.k формируются контрольные коды соответствующих элементов kb „ , . . ., kb j , . . . , kb гк .

На входы 23-1.1, ..., 23-i.j

23-n.k элементов строк матрицы произведения устройства, являющиеся входами соответствующих узлов свертки по модулю m произведения, поступают коды

элементов с , ..., с; с,;,

U k матрицы произведения. На выходах узлов свертки по модулю m произведения 3-1.1, ..., 3-i.j, ..., 3-n.k формируются контрольные коды, соответствующих элементов kc, , ..., kc

M

kr Mk

Контрольные коды ka;. элементов каждого столбца q матрицы множимого поступают с выходов узлов свертки по модулю m множимого на входы соответствующего q-ro сумматора по модулю m четвертой группы, ,г. При этом на выходах сумматоров по модулю m группы 4-1, ..., 4-q4-r формируются контрольные коды столбцов мноkA,

kA,

сожимого kA,, ., ответственно.

Контрольные коды kb элементов строки q матрицы множителя поступаю с выходов узлов свертки по модулю m множителя на входы соответствующего q-ro сумматора по модулю m второй группы, ,r. При этом на выходах сумматоров по модулю m второй группы 5-1

5-q,

5-r формируются контрольные коды строк матрицы

, kB,

kB,, сомножителя kB ,, ответственно.

Контрольные коды kc; элементов каждой строки i и каждого столбца j матрицы произведения поступают с выходов узлов свертки по модулю m произведения на входы соответственно i-ro сумматора по модулю m первой группы и j-ro сумматора по модулю m пятой группы, 1 1,п, j 1,k. При этом на выходах сумматоров по модулю m

первой группы 10-110-i, ...,

10-n и пятой группы 11-1, ..., (

11-k формируются контрольные коды

kC

(

kCn и констолбцов kT, ,

матрицы произведения.

Контрольные коды ka,-,, элементов матрицы множимого поступают с выходов узлов свертки по модулю m множимого также на первые входы q-x блоков умножения строки i-x групп, q 1,г, ,п. На вторые входы q-x блоков умножения строки всех групп поступают контрольные коды kBo с выходов сумматоров по модулю m второй группы. При этом на выходах блоков умножения строки. 8-1. 1 j ч. . ., 8-1 .q, ,.., С-1.Г, , Б-i-.q, .., 8-1.г, .. ., 8-и. 1 , . , 8-п, q, ) 8-п. г определяются произведения ka,, kB,, ..., ka,-kB, ...,. ka,,. kB ka;,. kB,, ,.., ka;q,.kB(, .xkBf,, . . ., kB ,, ..., , ..., ka. kBj, соответственно.

Контрольные коды kbqj элементов матрицы множителя поступают с вьпсо- дов узлов свертки по модулю ш множителя также на первые входы q-x бло- Ков умножения столбца j-x групп, ,r, j 1,k. На вторые входы q-x блоков умножения столбца всех групп поступают контрольные коды kAq с выходов сумматоров по модулю m четвертой группы. При этом на выходах блоков умножения столбца 9-1.1, ...., У-q 1, J 9 IT. 1 , . . ., У- 1.J, ...,

9-q.j, ..., 9-r.j, ..., 9-1.k,

9-qAk, ..., 9-r.k определяются произведениями kb (, kA,, ...,

2, ..

I у iC3.1 f«

ka.,a -kBa

kb kA

kb «, kA

P( j-kA(,

r .. . ,

kb

kb, kAa, kA

1

... , kb j

cCD К.П , . . ,

f,| kA соответственно.

kbn k

ч1 2.

На группу входов коррекции строки

устройства 20-1, ..., 20-i, ..., 20-п, являющиеся входами узлов свертки по модулю m первой группы соответственно 6-1, ..., 6-i, ..., 6-п, поступают отбрасываемые части произведений элементов строк 1, ..., i, ... п матрицы произведения.. При этом на выходах узлов свертки по модулю m первой группы формируются контрольные коды коррекции i-й строки результата S; .

Контрольные коды произведений, снимаемые с выходов блоков умножения строки i-группы, и контрольный код коррекции i-й строки результата S-, ,11, поступают на входы i-ro сумматора по модулю m третьей«группы.

При этом на вькодах сумматоров по модулю m третьей группы 12-1, t.., 12-i, ..,, 12-n определяются контрольные коды строк матрицы произведения соответственно kC , .. ., kC, , ..., kC.

1

kCi( XlClta; kB)+S )modra. 0 , t I

Ha группы входов коррекции столбца устройства 22-1, ..., 22-j, .,., 22-k, являющиеся входами узлов свертки по модулю m второй группы 7-1,

5 .j J 7-k, поступают отбрасываемые части произведений элементов столбцов 1, ..., J, k матрицы произведения. При этом на выходах узлов свертки по модулю m второй

0 группы формируются контрольные коды .коррекции j-ro столбца результата RJ.

Контрольные коды произведений, снимаемые с выходов блоков умножения

5 столбца j-й группы, и контрольньй код коррекции j-ro столбца результата R. , ,k, поступают на входы j-ro сумматора по модулю m шестой группы. При этом на выходах суммато0 ров по модулю т-шестой группы 13-1, ..., 13-J, ..., l3-k определяются контрольные коды столбцов матрицы произведения соответственно kT, ,..,,

kTj,

IcT , KJ.|.

35

Ц ( il(kb kAj+R )modm.

Контрольные коды строк матрицы произведения kCj и kC, снимаемые с

40 выходов сумматоров по модулю третьей и первой групп, поступают на входы узлов сравнения первой группы. При этом на выходах узлов сравнения первой группы 14-1, ..., 14-1, ...,

45 14-п формируются сигналы контроля, указывающие на правильность вычислений матрицы произведения с точностью до ее строки.

Контрольные коды столбца матрицы

gQ произведения kT и kT:, снимаемые с выходов сумматоров по модулю га пятой и шестой групп, поступают на входы узлов сравнения второй группы. При этом на выходах узлов сравнения втоgg рой группы 15-1, ..., 13-1, ...,15-п формируются сигналы контроля, указывающие на правильность вычислений матрицы произведения с точностью до ее столбца.

5

Сигналы контроля, снимаемые с выходов узлов сравнения первой и второй групп, поступают соответственно на выходы 17-1, ..., 17-i, ..., 17-п и 18-1, ..., 18-J, , 18-k устройства, а также на входы блока 16 индикации.

При правльном вычислении матрицы произведения сигналы контроля принимают значения Исправно, Вычислени элемента матрицы произведения с ошикой приводит к несоответствию срав ниваемьк контрольных кодов и фиксации ошибки сигналами контроля строк и столбца, содержащих этот элемент. Блок индикации высвечивает номера строки и столбца образующие код локализации ошибки.

Формула изо

р е т е н и я

Устройство для контроля по модулю -1 умножения матриц чисел,

30

содержащее первый, второй и третий сумматоры по модулю m , первую группу сумматоров по модулю т, первый и второй узлы свертки по модулю т, пер вьш узел сравнения, п групп узлов свертки по модулю m произведения, первую группу блоков умножения строки, причем входы узлов свертки по модулю m произведения каждой группы являются входами элементов соответствующей строки п и-матрии з1 произве- 35 дения устройства, а выходы узлов свертки по модулю m произведения каждой группы соединены с входами соответствующего сумматора по модулю m первой группы, выходы блоков умножения строки первой группы и выход первого узла свертки по модулю m сое динены с соответствующими входами третьего сумматора по модулю т, вы25 ки п г-матрииД)1 множимого, входы узлов свертки по модулю m множителя каждой группы являются входами элементов соответствующего столбца r-k- матрицы множителя, выход q-ro узла свертки подмодулю т множимого i-й группы ( ,г., ,п) соединен с i-м входом сумматора по модулю m четвертой группы и первым входом q-ro блока умножения строки i-й группы, второй вход которого объединен с вторыми входами q-x блоков умножения строки остальных групп и подключен к выходу q-ro сумматора по модулю m второй группы,, j-й вход которого соединен с выходом q-ro узла свертки подмодулю m множителя j-й группы (j 1,k) и первым входом q-ro блока умножения столбца j-й группы, второй вход которого объединен с вторыми

40

ХОД-которого соединен с первым входом 45 ходами q-x блоков умножения столбца

первого узла сравнения, входы первого и второго узлов свертки по модулю m являются первыми входами коррекции строки и столбца матрицы соответственно, отлич ающее с я тем, что, с целью расширения диагностических возможностей устройства, в него введены п групп узлов свертки по модулю m множимого, k групп узлов свертки по модулю m множителя, г-1 сумматоров по модулю т, образуюш,их с вторым сумматором по модулю m вторую группу сумматоров по модулю т, п-1 узлов свертки по модулю т, образующих с первым узлом свертки по модулю m первую группу узлов свертки по модулю гп, k-1 узлов свертки по модулю т, образующих с вторым узлом свер

тки по модулю m вторую группу узлов свертки по модулю т, п-1 групп блоков умножения строки, k групп блоков умножения столбца, п-1 сумматоров по

модулю т, об 1азующих с третьим сумматором по модулю m третью группу сумматоров по модулю т, г-1 суммато- ров по модулю т, образующих с первым сумматором по модулю m четвертую группу сумматоров по модулю т, k сумматоров по модулю-т пятой группы, k сумматоров по модулю m шестой группы, п-1 узлов сравнения, образующих с первым узлом сравнения первую группу

узлов сравнения, k узлов сравнения второй группы и блок индикации, причем входы узлов свертки по модулю m множимого каждой группы являются входами элементов соответствующей строки п г-матрииД)1 множимого, входы узлов свертки по модулю m множителя каждой группы являются входами элементов соответствующего столбца r-k- матрицы множителя, выход q-ro узла свертки подмодулю т множимого i-й группы ( ,г., ,п) соединен с i-м входом сумматора по модулю m четвертой группы и первым входом q-ro блока умножения строки i-й группы, второй вход которого объединен с вто рыми входами q-x блоков умножения строки остальных групп и подключен к выходу q-ro сумматора по модулю m второй группы,, j-й вход которого соединен с выходом q-ro узла свертки подмодулю m множителя j-й группы (j 1,k) и первым входом q-ro блока умножения столбца j-й группы, второй вход которого объединен с вторыми

0

5

остальных групп и подключен к выходу q-ro сумматора по модулю m четвертой группыJ выходы блоков умножения строки и -и группы и выход со -го узла свертки по модулю m первой группы.соединены: с входами со -го сумматора по модулю m третьей группы, выход которого соединен с первым входом 03 -го узла сравнения первой группы, вход W-го узла свертки по модулю m первой группы является со -м входом коррекции строки (,п), выход i-ro cyT/iMaTopa по модулю m первой группы соединен с вторым входом i-ro узла

сравнения первой группы, выходы j-x узлов свертки по модулю m -произведения групп соединены с входами j-ro сумматора по модулю m пятой группы, выход которого соединен с первым входом j-ro узла сравнения второй группы, второй вход которого соединен с выходом j-ro сумматора по модулю m шестой группы, входы которого соединены соответственно с выходами блоков умножения столбца j-й группы и

выходом j-ro узла свертки по модулю m второй группы, вход -го узла свертки по модулю m второй группы (2,k) являетсяР-м входом коррекции столбца, выходы узлов сравнения первой и второй групп соединены с входами блока индикации и являются соответственно выходами результата контроля первой и второй групп выходов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля по модулю @ умножения матриц чисел | 1984 |

|

SU1297053A1 |

| Устройство для контроля умножения чисел по модулю | 1985 |

|

SU1259269A1 |

| Устройство для контроля умножения двоичных чисел по модулю три | 1988 |

|

SU1774337A1 |

| Устройство для умножения с контролем | 1989 |

|

SU1741128A1 |

| Преобразователь позиционного кода в код с большим основанием | 1987 |

|

SU1444959A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Матричный умножитель по модулю чисел Ферма | 1990 |

|

SU1783513A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении, аппаратуры контроля и диагностики арифметических устройств.. Цель изобретения - расширение диагностических возможностей устройства. Устройство содержит п групп узлов свертки.п& модулю m множимого, k групп узлов свертки по модуЛю m цножителя, п групп узлов свертки по модулю m произведения, шесть групп сумматоров по модулю га, две группы узлов свертки по модулю га, п групп блоков умножения строки, kгрупп блоков умножения столбца, две группы узлов сравнения и блок индикации. Сигналы контроля, снимаемые с выходов узлов сравнения, поступают на выходы устройства и на входы блока индикации, При правильном вычисления- матрицы произведения скгиал1л контроля принимают значения Исправно ; Вычисление элемента матрицы произведения с ошибкой приводит к несоответствию сравниваемых контрольных кодов и фиксации ошибки. Блок индикации высвечивает номера строки и столбца, образующие код локализации ошибки. Расширение диагностических возможностей достигается Sa счет введения групп узлов свертки по модулю ш, блоков умножения и сумматоров по модулю т. 1 ил. i (Л С 00 00 со ел 05 СП

гз-пх:

«-.;

ПCDT 7-/

/7-i

Редактор Е.Папп

Составитель И.Иваныкин Техред М.Дидык

Заказ 4223/39Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор Г. Решетник

| Устройство для контроля умножения по модулю | 1975 |

|

SU595737A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля по модулю @ умножения матриц чисел | 1984 |

|

SU1297053A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1985-11-14—Подача