Изобретение относится к автоматике и приборостроению и может быть использовано в цифровых системах управления и измерения.

Целью изобретения является расширение функциональных возможностей устройства за счет измерения угла поворота вала.

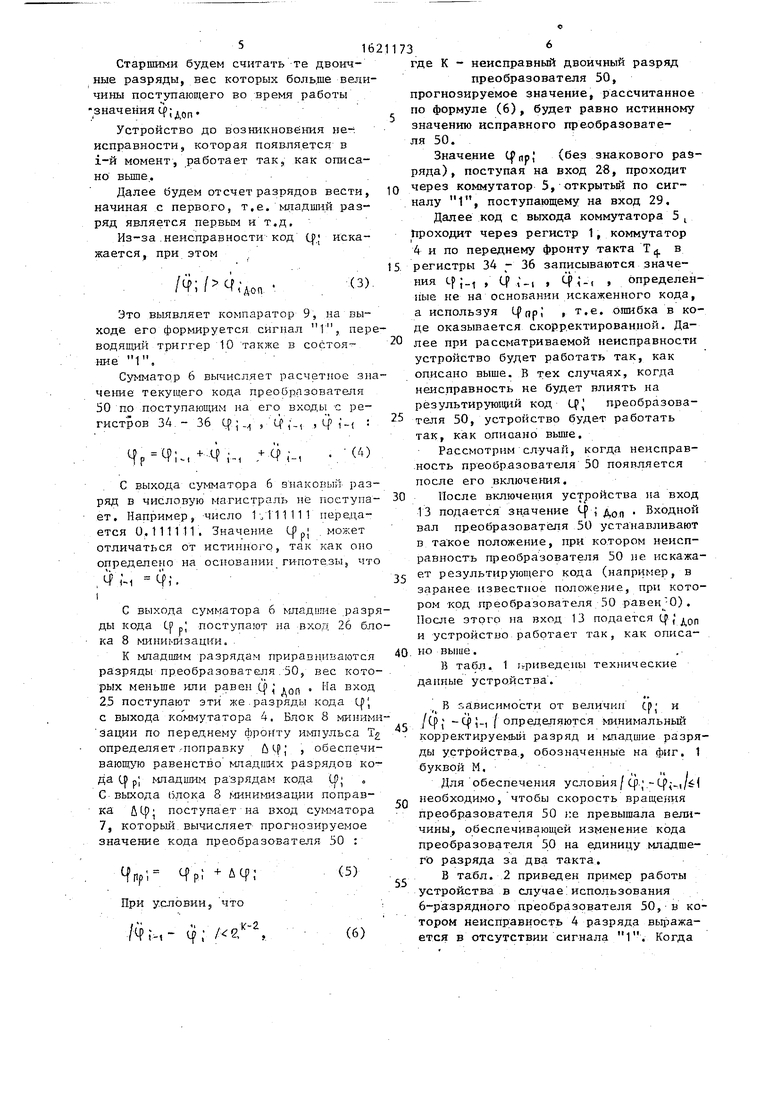

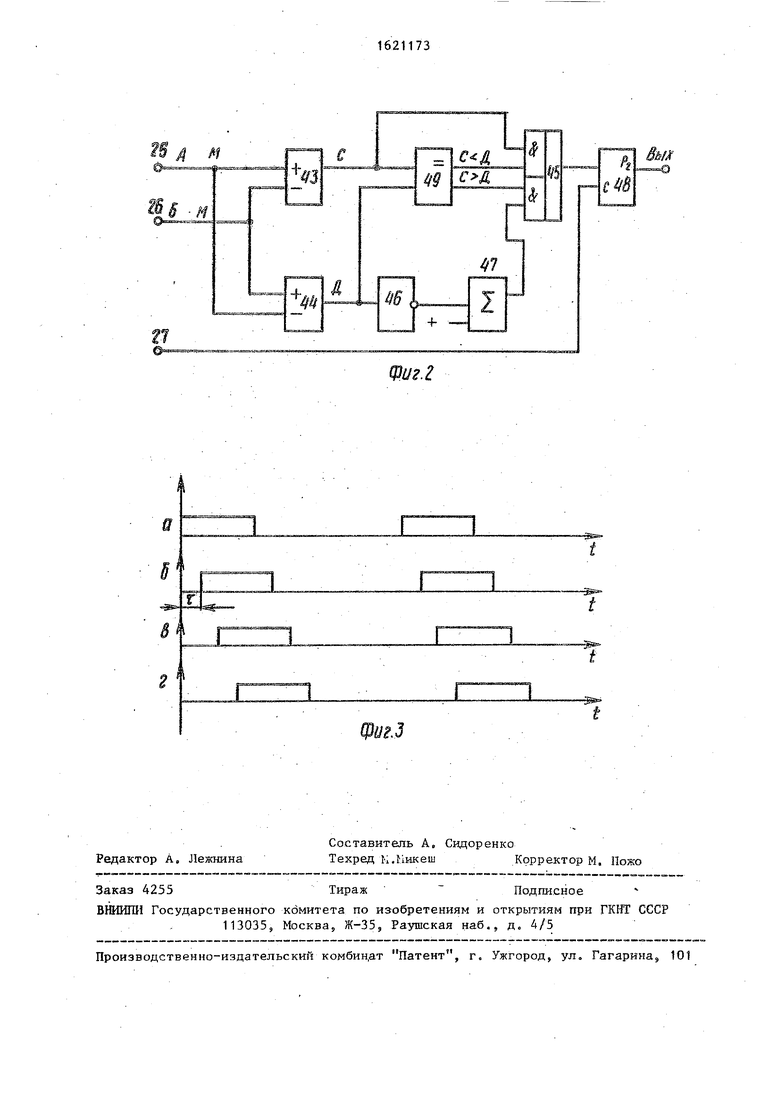

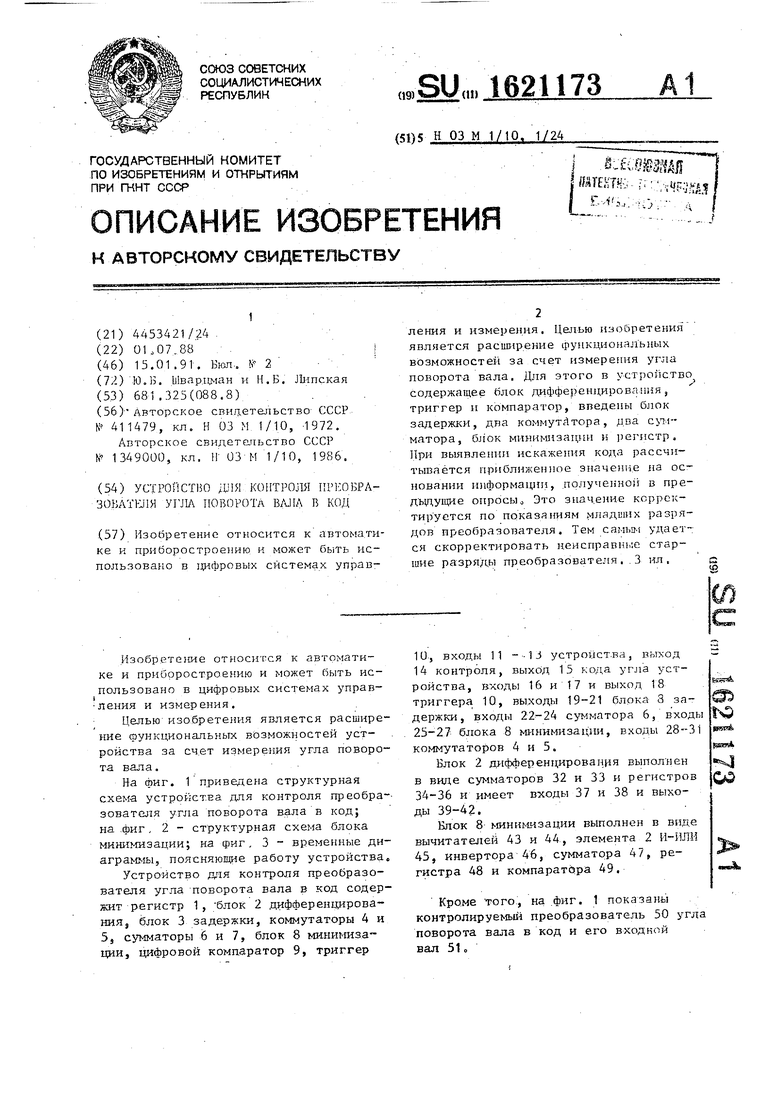

На шиг. 1 приведена структурная схема устройства для контроля преобразователя угла поворота вала в код; на фиг, 2 - структурная схема блока минимизации; на фиг. 3 - временные диаграммы, поясняющие работу устройства.

Устройство для контроля преобразователя угла поворота вала в код содержит регистр 1, блок 2 дифференцирования, блок 3 задержки, коммутаторы 4 и 5, сумматоры 6 и 7, блок 8 минимизации, цифровой компаратор 9, триггер

10, входы 11 - 1J устройства, выход 14 контроля, выход 15 кода угла устройства, входы 16 и 17 и выход 18 триггера 10, выходы 19-21 блока 3 задержки, входы 22-24 сумматора 6, входы 25-27 блока 8 минимизации, входы 28-31 коммутаторов 4 и 5.

Блок 2 дифференцирования выполнен в виде сумматоров 32 и 33 и регистров 34-36 и имеет входы 37 и 38 и выходы 39-42.

Блок 8 минимизации выполнен в виде вычитателеи 43 и 44, элемента 2 И-НЛП 45, инвертора 46, сумматора 47, регистра 48 и компаратора 49.

Кроме того, на фиг. 1 показаны контролируемый преобразователь 50 угла поворота вала в код и его входной вал 51,

&S7&

ю

РДО5&

(аяя4

4

ОЗ

«&,

Устройство работает следующим образом.

На вход 12 поступают тактовые импульсы Tj, по которым производится опрос преобразователя 50 угла поворота вала в код. На выходе преобразователя 50 формируется код I s где i 1,2.а, - порядковые номера сигналов опроса преобразователя 50 (так- тов)„ Тактовые импульсы Т} (фиг. 3, а) с входа 12 поступают на блок 3 задержки, на выходах 19-21 которого формируются импульсы Т, Т и Т4 (фиг. 3, б, в, г), сдвинутые один от- носительно другого на величину t (фиг,2 На выходе преобразователя 50 код формируется через время, существенно меньшее t . Этот код запоминается и может измениться только после очеред- ного опроса преобразователя 50,

Рассмотрим работу устройства в том случае, если преобразователь 50 исправен.

Случай, когда i 3.

При этом в регистре 34 хранится Ц, н i -в регистре 35 - Ср ,, - первая производная угла на момент , рассчитанная как изменение угла за время, равное такту; в регистре 36 - П)д , вторая производная угла на момент i-1, рассчитанная как изменени скорости за время, равное одному такту.

Код преобразователя 50 поступает через вход 30 открытого коммутатора 4 на вход 37 блока 2 дифференцирования. Сумматор 32 рассчитывает первую производную

-Ц, -, ,

(1)

причем Ч1 i-i регистра 34.

поступает с выхода

Сумматор 33 по значениям ф{ и , поступающим на его входы, рассчитывает вторую производную:

w

(2)

С выхода сумматора 33 это значение поступает на компаратор 9, который сравнивает его абсолютную величину с поступающим на вход 13 устройства Cf J доп - текущим максимально возмож- ным ускорением вращения преобразователя 50. На выходе компаратора 9 формируется сигнал О, так как /СР;

g s 0

5

о

5

0

5

0

Ч Aon Этот сигнал поступает на вход 16 триггера 10 и по переднему фронту такта 1 (фиг. 3, б), поступающего на его синхронизирующий вход 17, устанавливается в состояние О.

Сигнал О с выхода 18 триггера 10, поступая на вход 31, открывает коммутатор 5 для прохождения кода , поступающего на вход 300 С выхода коммутатора 5 код Cfj поступает на вход регистра 1 и запоминается в нем в момент поступления переднего фронта такта ТЈ (фиг. 3, в) на его синхронизирующий вход.

Таким образом, в течение такта Ту, поступающего на вход .29, коммутатор 4 открыт для прохождения кода Cf; , поступающего с регистра 1 на вход 28. По переднему фронту такта Тф (фиг. 3, г) регистры 34-36 запоминают поступающие в этот момент времени на их входы соответственно Ц , Ц); , q и хранят эти значения до поступления следующего такта 1 af.

На выход 15 устройства поступает код преобразователя 50 с выхода регистра 34 с задержкой приблизительно 3Ј относительно момента опроса преобразователя 50, эта задержка пренебрежимо мала по сравнению с периодом опроса преобразователя 50.

Случай когда i 3,

В течение этого времени устройство не выполняет своих функций, а происходит запоминание информации в регистрах 34 - 36. Так как после включения информация в них не предсказуема, то на вход 13 поступает максимально возможный код, т.е.Cf, доп ($ Mo(VC « При этом устройство работает так, как описано выше, так как компаратор 9 и триггер 10 устанавливаются в состояние О.

Рассмотрим работу устройства в случае неисправности одного или нескольких разрядов преобразователя 50. Преобразователь 50 является преобразователем позиционного кодирования, причем неисправность ставших разрядов преобразователя 50 не влияет на показание младших разрядов результирующего двоичного кода„

Случай, когда неисправен один или несколько старших разрядов, причем неисправность возникает не сразу же после включения преобразователя 50, а во время его работы.

Старшими будем считать те двоичные разряды, вес которых больше величины поступающего во время работы значенияц ;доп.

Устройство до возникновения неисправности, которая появляется в i-й момент, работает так, как описано выше.

Далее будем отсчет разрядов вести, начиная с первого, т.е. младший разряд является первым и т.д.

Из-за неисправности код Cj)j искажается, при этом

,

ДСП

Это выявляет компаратор

9, п.

на

выходе его формируется сигнал 1, переводящий триггер 10 также в состояние 1,

Сумматор 6 вычисляет расчетное значение текущего кода преобразователя 50 по поступающим на его входы с регистров 34-36 , (jf,, , q , -( :

(3)

, 4i-,

С выхода сумматора 6 знаковый разряд в числовую магистраль не поступает. Например, число 1,111111 передается 0.111111. Значение (р „| может отличаться от истинного, так как оно определено на основании гипотсзы5 что

, .

(4)

С выхода сумматора 6 младшие разряды кода Ср „; поступают на вхол 26 блока 8 минимизации.

К младшим разрядам приравниваются разряды преобразователя 50, вес которых меньше или равен И) ,оп , а вход

ч;

25 поступают эти же разряды кода

с выхода коммутатора 4. Блок 8 минимизации по переднему фронту импульса Т/г определяет поправку , обеспечивающую равенство младших разрядов кода ср р; младшим разрядам кода (5; С выхода блока 8 минимизации поправка йф| поступает на вход сумматора 7, который вычисляет прогнозируемое значение кода преобразователя 50 :

V-e р; +

При условии 5 что

/ipj,- tf; ,

где К - неисправный двоичный разряд

преобразователя 50,

прогнозируемое значение, рассчитанное по формуле (б), будет равно истинному значению исправного преобразователя 50.

Значение (без знакового разряда), поступая на вход 28, проходит 0 через коммутатор 5, открытый по сигналу 1, поступающему на вход 29.

Далее код с выхода коммутатора 5 t проходит через регистр 1, коммутатор 4 и по переднему фронту такта Т в 15 регистры 34 - 36 записываются значения , , q ,, , , , определенные не на основании искаженного кода, а используя т«е« ошибка в коде оказывается скорректированной. Да20 лее при рассматриваемой неисправности устройство будет работать так, как описано выше. В тех случаях, когда неисправность не будет влиять на результирующий код Ц преобразова25 теля 50, устройство будет работать так, как описано выше.

Рассмотрим случай, когда неисправность преобразователя 50 появляется после его включения.

30 После включения устройства на вход 13 подается значение Ц ; доп . Входной вал преобразователя 50 устанавливают в такое положение, при котором неисправность преобразователя 50 не искажает результирующего кода (например, в заранее известное положение, при котором код преобразователя 50 равен 0). После этого на вход 13 подается (, доп и устройство работает так, как описа40 но выше.

В табл. 1 приведены технические данные устройства.

35

5

0

В зависимости от величин (р и

/ I

/Cpj ., | определяются минимальный корректируемый разряд и младшие разряды устройства, обозначенные на фиг. 1 буквой М.

Для обеспечения условия/ |;-LJ)-, необходимо, чтобы скорость вращения преобразователя 50 не превышала величины, обеспечивающей изменение кода преобразователя 50 на единицу младшего разряда за два такта,

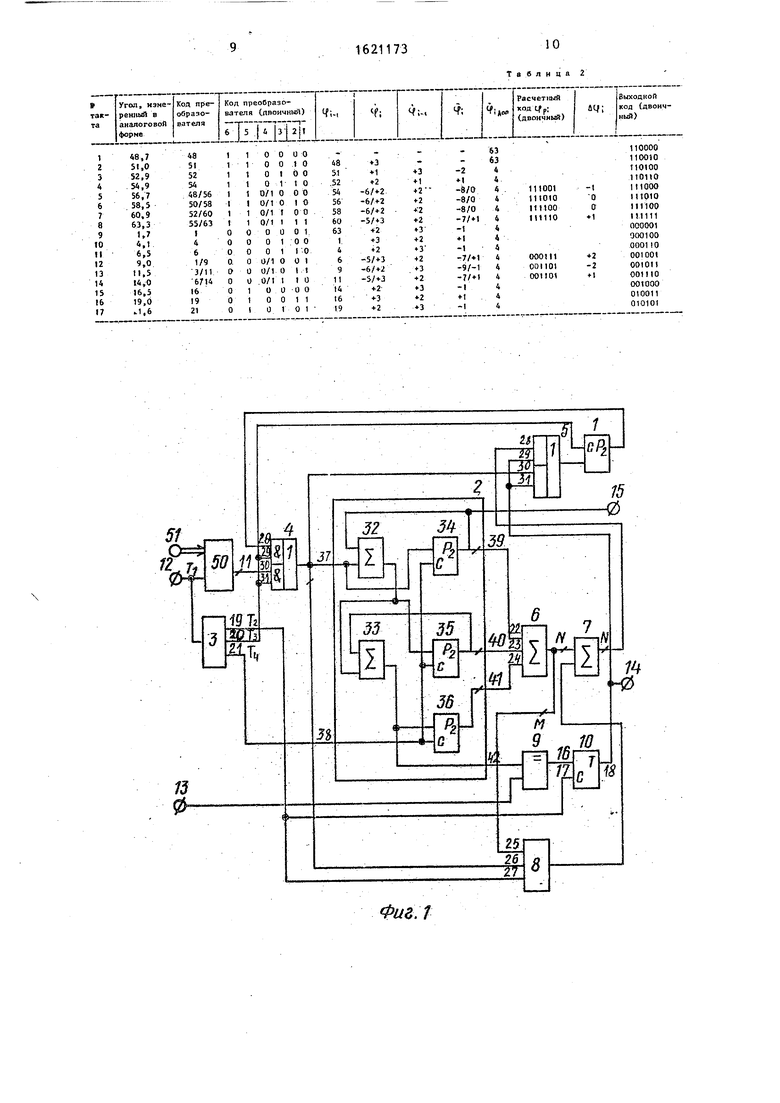

В табл. 2 приведен пример работы устройства в случае использования 6-разрядного преобразователя 50, в котором неисправность 4 разряда выражается в отсутствии сигнала 1. Когда

неисправность преобразователя 50 ис- ражает указанные в табл, 2 величины, эти величины представляются дробью, в числителе которой находится искаженная неисправностью величина, в знаменателе - неискаженная величина При i 182 непредсказуемые значения величин отмечены прочерке. Значение (|р; (в дополнительном коде) представ-, лено без знакового разряда, т,е„ таким, как оно передается по числовой магистрали, это обеспечивает правильное формирование кода при переходе его значения через О,.

Формула изобретения

Устройство для контроля преобразователя угла поворота вала в код, содержащее блок дифференцирования, триг-., гер и цифровой компаратор, первая группа входов которого является задающим входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет измерения угла поворота валаэ в него введены блок задержки, два коммутатора, два сумматора, блок минимизации и регистр 5 первая группа информационных входов первого коммутатора является группой информационных входов устройства, выходы первого коммутатора соединены с группой информационных входов блока дифференцирования, , первой группой информационных входов бттока минимизации и первой группой информационных входов второго коммутатора, выходы которого соединены с информационными входами регистра, выходы которого соединены с второй группой ин- формационных входов первого коммутатора, вход блока задержки является такто.вым входом устройства, первый вы- ход которого т.соединен с тактовым входом регистра и управляющим входом коммутатора, второй выход соединен с тактовым входом блока дифференцирования, а третий выход соединен с тактовыми входами блока минимизации и триггера, первая группа выходов блока дифференцирования является выходом кода угла устройства и соединена с первой группой входов первого сумматора, вторая и третья группы выходов блока дифференцирования соединены с второй и третьей группами входов первого сумма-v тора, выходы которого соединены с первой группой входов второго сумматора и второй группой информационных входов блока минимизации, выходы которого соединены с второй группой входов второго сумматора, выходы которого соединены с-второй группой информационных входов второго коммутатора, четвертая группа выходов блока дифференцирования соединена с второй группой входов цифрового компаратора, выход которого соединен с информационным входом триггера, выход которого соединен с управляющим входом второго коммутатора и является выходом контроля устройства.

Таблица 1

1621173

10

Таблиц

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля преобразователя угол-код | 1986 |

|

SU1349000A1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1522408A1 |

| Преобразователь угла поворота вала в код с самоконтролем | 1987 |

|

SU1462484A1 |

| Многоканальное тензометрическое устройство | 1987 |

|

SU1439387A1 |

| Устройство для ввода информации | 1987 |

|

SU1462287A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Устройство для автоматического управления (его варианты) | 1984 |

|

SU1249481A1 |

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Устройство для автоматизированного управления технологическим процессом водоснабжения города | 1986 |

|

SU1381431A1 |

Изобретение относится к автоматике к приборостроению и может быть использовано в цифровых системах управления и измерения. Целью изо&ретения является расширение функциональных возможностей за счет измерения угла поворота вала. Для этого в устройство содержащее блок дифференцирования, триггер и компаратор, введены блок задержки, дна коммутатора, ива сумматора, блок минимизации и регистр. При выявлении искажения кода рассчитывается приближенное значение на основании информации, полученной в предыдущие опросы о Это значение корректируется по показаниям .младших разрядов преобразователя. Тем самым удается скорректировать неисправьые старшие разряды преобразователя. 3 ил. s (О

«8,7

51,0

54,9

56,7

58,5

60,9

63,3

1,7

4,1

6,5

9,0

11,5

14,0

16,5

19,0

.1,6

110000 110010 П0100 110110 111000 111010 111100

111111

000001 000100

oooi ю ООЮ01

001011 001110 001000 010011 010101

Фиг. 1

г

Фиг.

t

Т

| Авторское свидетельство СССР № 411479, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля преобразователя угол-код | 1986 |

|

SU1349000A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-15—Публикация

1988-07-01—Подача