3 . 15

Изобретение относится к вычислительной технике и может быть использовано для цифровой обработки случайных процессов, например, при цифро- вой фильтрации и спектральном анализе.

Цель изобретения - повышение быстродействия и упрощение фильтра.

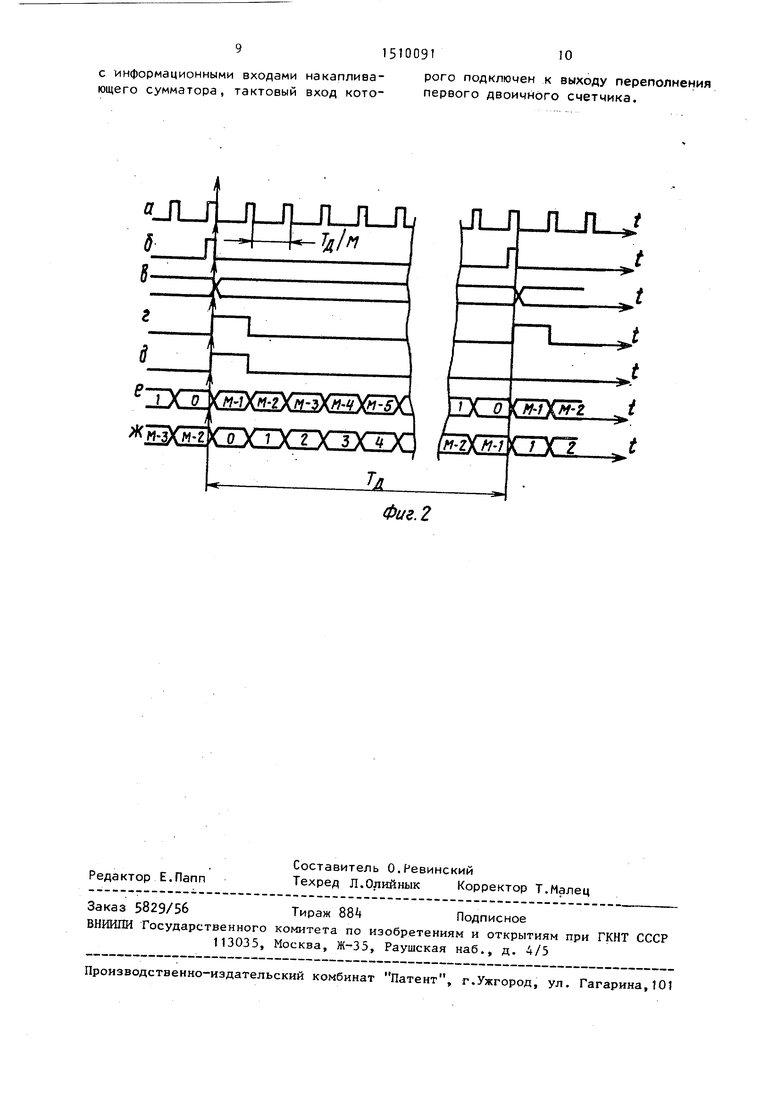

На фиг. 1 приведена функциональная схема фильтра; на фиг. 2 - временные диаграммы его работы.

Цифровой фильтр содержит линейный дельта-модулятор 1, первый и второй двоичные счетчики 2 и 3, тактовый генератор , блок 5 оперативной памяти, элемент И 6, буферный регист 7, элемент ИЛИ-НЕ 8, блок 9 постоянной памяти, мультиплексор 10, элемент 11 эквивалентности, реверсивный счетчик 12, накапливающий сумматор 13 и цифроаналоговый преобразователь И. На фиг. 1 обозначены вход 15, первые и второй выходы 1б и 17- На фиг. 2 показаны следующие сигналы: а - тактовые импульсы с генератора 4; 6 - импульсы на выходе переполнения счетчика 2j в - смена шагов квантования на выходе дельта-модулятора 1 ; г - импульсы на выходе элемента И 6; д - импульсы на выходе элемента ИЛИ-НЕ 8.; е - смена сигналов на выходе, мультиплексора 10; ж - смена сигналов на выходе блока 9 постоянной памяти.

В сигналах (фиг. 2е,ж) условно показаны адреса блоков 5 и 9 памяти.

В основе работы цифрового фильтра с линейной дельта-модуляцией лежит следующее.

Выходной сигнал цифрового фильтра с линейной дельта-модуляцией в обычном формате импульсно-кодовой модуляции представляется в следующем виде:

П 1 М-А

Yn ГГГ

,ix)

k- m

JH1 -w ,

(1)

где е

h)

1 - 1,

0,

L ; , i 0,M-1 - весовая последовательность в формате линейной дельта-модуляции (шаги квантования импульсной характеристики цифрового фильтра); , входная последовательность (шаги квантования входного сигнала). ч ,,

Последовательности L ; | и ь j представляют собой кодированные последовательности шагов квантования

соответствующих величин и представлены в формате линейной дельта-модуляции.

Для получения алгоритма функционирования устройства разделим (1) на два последовательных этапа, представляемых двумя последовательно включенными накапливающими сумматорами, осуществляющими непрерывное накопление сигналов: п

Y.

VY

1

мм

VY; Z 21

(к)

(Ь)

(2)

) т

Отметим, что значение i,Y; также можно представить двумя накапливающими сумматорами:

5

0

5

0

5

0

(3)

однако прямая реализация (З) приводит к увеличению аппаратурных затрат (избыточный накапливающий сумматор) и увеличению времени вычисления свертки (1) из-за затрат времени в указанном сумматоре.

Цифровой фильтр с линейной дельта-модуляцией работает следующим образом.

Перед началом фильтрации необходимо провести обнуление реверсивного счетчика 12 и накапливающего сумматора 13. При этом на цифровых и аналоговом выходах 1б и 17 устанавливаются нулевые значения выходных сигналов. Такое обнуление необходимо также проводить пр.и случайных сбоях, например, питания, чтобы предотвратить накопление ошибок в выходном

сигнале фильтра. В блок Ь памяти заносится при этом нулевое значение сигнала, т.е. последовательность (0,1). .

В блоке 9 постоянной памяти записана одноразрядная последовательность

(hV

k 0,М-1 весовых коэффициенK i

тов фильтра. Запись производится подряд, начиная с нулевого адреса блока 9 по возрастающим адресам в том порядке, как они записаны в последова

тельности

bt i

ПО нулевому адресу

,(и)

записывается значение L , по первому - и т.д., по (м-1)-му адресу записывается значение Ьц,.

51

Тактовый генератор k генерирует непрерывную последовательность импульсов (фиг. 2а) с частотой f

М --, где Т. - период частоты дискТА

ретизации входного сигнала, М - длина импульсной характеристики цифрового фильтра. Примем, что переходом, вызывающим изменение счетчиков 2, 3 и 12, является переход на их счетном входе из единичного состояния в нулевое, т.е. изменение состояния счетчиков происходит по заднему фронту сигналов на их счетных входах. Примем также что запись значения сигнала по информационным входам регистра 7 производится по заднему фронту сигнала на его тактовом входе, а запись значения сигнала по информационным входам реверсивного счетчика 12 производится по переднему фронту сигнала на его входе размещения предустановки. Первый двоичный счетчик 2 работает в режиме вычитания, поэтому после поступления М импульсов частоты f на его счетный вход на его выходе переполнения (за- ема)- в конце периода дискретизации Тд формируется импульс (фиг. 26), поступающий на тактовый вход линейного дельта-модулятора 1. На выходе послЪднего при этом фиксируется значение шага квантования L входного сигнала (фиг. 2в) в п-м периоде дискретизации, которое сохраняется на выходе блока 1 до поступления следующего импульса (фиг. 26) с выхода зае ма счетчика 2, Сигналы с разрядных выходов счетчика 2 подаются на входы элемента И 6, поэтому при состоянии счетчика 2, равном М-1, на выходе элемента И 6 формируется импульс (фиг. 2г) длительностью , который поступает на тактовый вход регистра 7 и вход разрешения предустановки второго двоичного счетчика 3. По заднему фронту этого импульса в регистре 7 фиксируется состояние счетчика 3 во втором такте teLt,: а в следующем периоде дискретизации

входного сигнала, по переднему фронту этого импульса, в счетчик 3 записывается состояние регистра 7. Поэтому в первом такте текущего периода дискретизации состояние счетчика 3 равно состоянию этого счетчика во втором такте t ,tj предыдущего периода дискретизации, чем обеспечи0916

вается рециркуляция адресов ячеек блока 9 постоянной памяти.

Счетчик 3, имеющий коэффициент g пересчета М, работает в режиме сложения. Разрядные выходы счетчика 3 соединены с входами элемента ИЛИ-НЕ 8, в результате чего, при нулевом состоянии счетчика 3 на выходе эле10 мента ИЛИ-НЕ 8 формируется импульс (фиг. 2д) длительностью Тд/М, поступающий на управляющие входы блока 5 памяти и мультиплексора ТО. При наличии этого импульса блок 5 памяти

15 находится в режиме записи (фиг. 2е), а мультиплексор 10 передает сигнал с выхода линейного дельта-модулятора 1 на первый вход элемента 11 эквивалентности. В отсутствии этого

0 импульса блок 5 памяти переводится в режим чтения, а мультиплексор 10 передает сигнал с выхода блока 5 на первый вход элемента 11. За счет изменения начального состояния счет25 чика 3 на единицу в каждом новом периоде дискретизации осуществляется рециркуляция адресов ячеек блоков S и 9 памяти - в каждом следующем периоде Тд адреса ячеек блока 9 па0 мяти смещаются на единицу в сторону опережения от адресов ячеек блока 5 памяти. Таким образом, шаги квантования входного сигнала , , запись которых производится в блок 5

g памяти всегда при нулевом состоянии счетчика 3, записываются в п-м периоде дискретизации по р-му адресу, где р (M-n)modM.

Поэтому в п-м периоде дискретиза0 ции по сигналам с выходов разрядов счетчиков 2 и 3, поступающих на адресные входы блоков 5 и 9 памяти соответственно, считываются с выхода мультиплексора 10 последовательность

n-(n+M-1-S)modM, S М-1,0 .(фиг. 2е) и с выхода блока 9 после- довательность m (n+r)mociM, г О,М-1 (фиг. 2ж), которые поступают синхронно на входы элемента 11

0 эквивалентности. Отметим, что nmodM- начальное состояние счетчика 3 в п-м периоде дискретизации. На выходе элемента 11 эквивалентности (элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ) формируется произведение I L © Г |. Последовательность таких произведений поступает на вход, управляющий направлением счета реверсивного счетчика 12, который изменяет свое состояние на единицу после поступления на его счетный вход очередного заднего фронта тактового импульса (фиг. 2а). В результате через М тактов на выходах реверсивного счетчика 12 формируется значение свертки (3) в п-м периоде дискретизации (k+m n-(n+M-1-a)modM +(n+r)moaM, а так как г М-1-s и, учитывая начальное состояние счетчика 3 в п-м периоде дискретизации, равное nmodM, получаем k+m nmoaM). Указанное соотношения между индексами последовательностей и ъ по соответствующим адресам блоков 5 и 9 памяти проиллюстрированы на фиг. 2 для случая nmodM 0.

В конце текущего периода дискретизации по импульсу с выхода заема счетчика 2 (фиг. 26) накопленное в реверсивном счетчике 12 значение записывается в накапливающий сумматор 13, где суммируется с его предыдущим значением. В следующем, (п+1)-м периоде дискретизации значение сигнала на выходах реверсивного счетчика 12 изменится на величину.,, поэтому после п периодов дискретизации, учитывая нулевое начальное значение, сигнал на выходах реверсивного счетчика 12 равен Y.

Таким образом, отсутствие обнуления реверсивного счетчика 12 позволило исключить непроизводительные затраты времени на эту операцию, а также объединить в нем выполнение двух последовательных суммирований (2). Накопление значений выходного сигнала реверсивного счетчика 12 в накапливающем сумматоре 13 дает, сог ласно (2), отсчет выходного сигнала цифрового фильтра в формате им- пульсно-кодовой модуляции, который преобразуется цифроаналоговым преобразователем 1 в аналоговую форму Y(t).

При фильтрации периодических сигналов выходной сигнал фильтра, а также первая разность (З) являются периодическими функциями времени, поэтому отсутствие переполнения счетчика 12 обеспечивается выбором его разрядности из условия максимального значения амплитуды первой разности.

Таким образом, в цифровом фильтре с линейной дельта-модуляцией полностью исключена задержка времени фоо

0

5

0

5

0

5

0

5

мирования адресов блоков постоянной и оперативной памяти, исключены также непроизводительные затраты времени на обнуление реверсивного счетчика и выполнение дополнительного суммирования .

Формула изобретения

Цифровой фильтр с линейной дельта- модуляцией, содержащий линейный дельта-модулятор, информационный вход которого является входом фильтра, а выход соединен с первым информационным входом мультиплексора и информационным входом блока оперативной памяти, выход которого подключен к второму информационному входу мультиплексора, выход которого соединен с первым входом элемента эквивалентности, выход которого подключен к управляющему входу реверсивного счетчика, тактовый генератор, выход которого соединен со счетными входами реверсивного счетчика и первого двоичного счетчика, выходы разрядов которого подключены к адресным входам блока оперативной памяти и входам элемента И, второй двоичный счетчик, выходы которого соединены с входами элемента ИЛИ-НЕ и блока постоянной памяти, выход которого подключен к второму входу элемента эквивалентности, накапливающий сумматор, выходы которого соединены с входами цифро- аналогового преобразователя и являются первыми выходами фильтра, выход переполнения первого двоичного счетчика подключен к тактовому входу линейного дельта-модулятора , выход элемента ИЛИ-НЕ соединен с управляющими входами блока оперативной памяти и мультиплексора, выход цифро- аналогового преобразователя является вторым выходом фильтра, отличающийся тем, что, с целью повышения быстродействия и упрощения фильтра, в него введен буферный регистр, информационные входы и выходы которого подключены соответственно к выходам и установочным входам второго двоичного счетчика, счетный вход которого подключен к выходу тактового генератора, выход элемента И соединен с тактовым входом буферного регистра и входом разрешения предустановки второго двоичного счетчика, вы- ходь1 реверсивного счетчика соединены

с информационными входами накапливающего сумматора, тактовый вход которого подключен к выходу переполнения первого двоичного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1425841A1 |

| Коррелятор | 1986 |

|

SU1425711A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Цифровой фильтр с дельта-модуляцией | 1987 |

|

SU1418908A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Анализатор активности непрерывных сигналов | 1989 |

|

SU1658386A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

Изобретение относится к вычислительной технике. Его использование для цифровой обработки случайных процессов (цифровая фильтрация, спектральный анализ) позволяет повысить быстродействие и упростить фильтр. В его состав входят линейный дельта-модулятор 1, двоичные счетчики 2, 3, тактовый генератор 4, блок 5 оперативной памяти, элемент И 6, элемент ИЛИ-НЕ 8, блок 9 постоянной памяти, мультиплексор 10, элемент 11 эквивалентности, реверсивный счетчик 12, накапливающий сумматор 13 и цифроаналоговый преобразователь 14. Благодаря введению буферного регистра 7 и соответствующим соединениям исключается обнуление реверсивного счетчика, который работает с накоплением, что позволяет исключить один накапливающий сумматор. 2 ил.

гг 5

JLJ JLJl fLJ-Jb

f J „ Тя /М

Фиг. 2

| Известия ВУЗов, электроника | |||

| - , т | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Ведущий наконечник для обсадной трубы, употребляемой при изготовлении бетонных свай в грунте | 1916 |

|

SU258A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-23—Публикация

1988-03-17—Подача