Изобретение относится к испытательной технике, а именно к устройствам для испытаний изделий на воздействие широкополосной случайной вибрации с заданным энергетическим спектром.

Цель изобретения - повышение точности измерения амплитудно-частотной характеристики (АЧХ) формирователя без увеличения времени измерения путем сравнения АЧХ, измеренной ранее, с текущей АЧХ формирователя и получения разностной АЧХ.

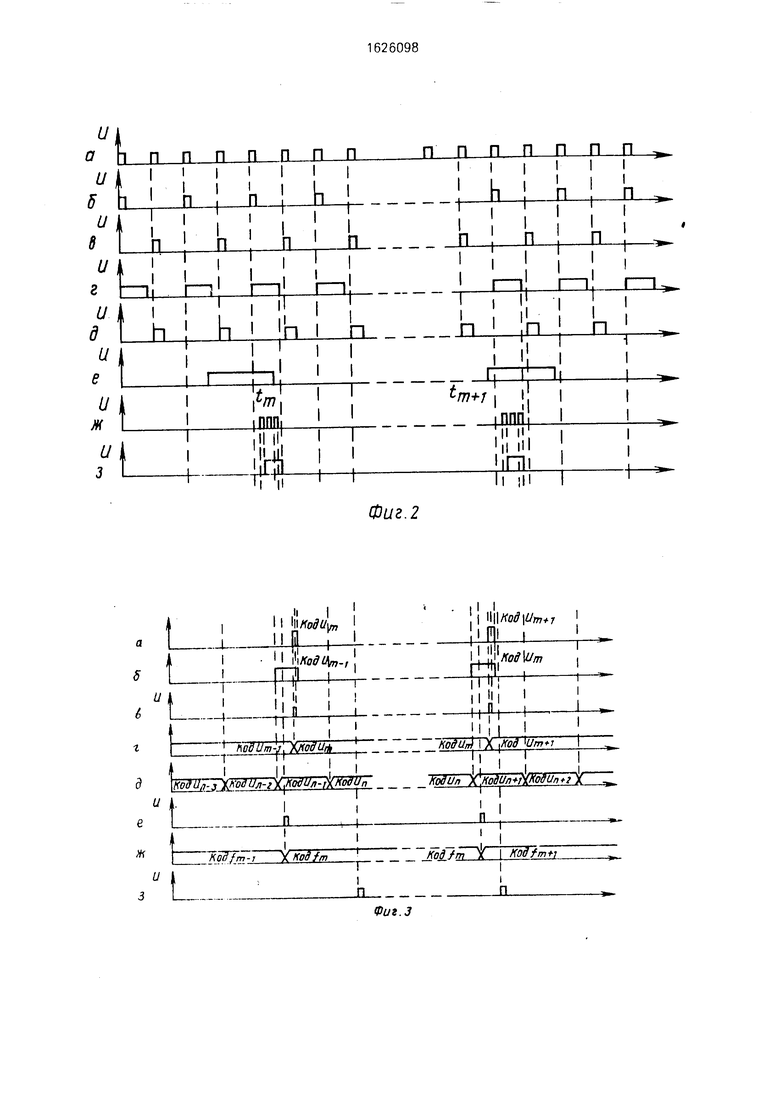

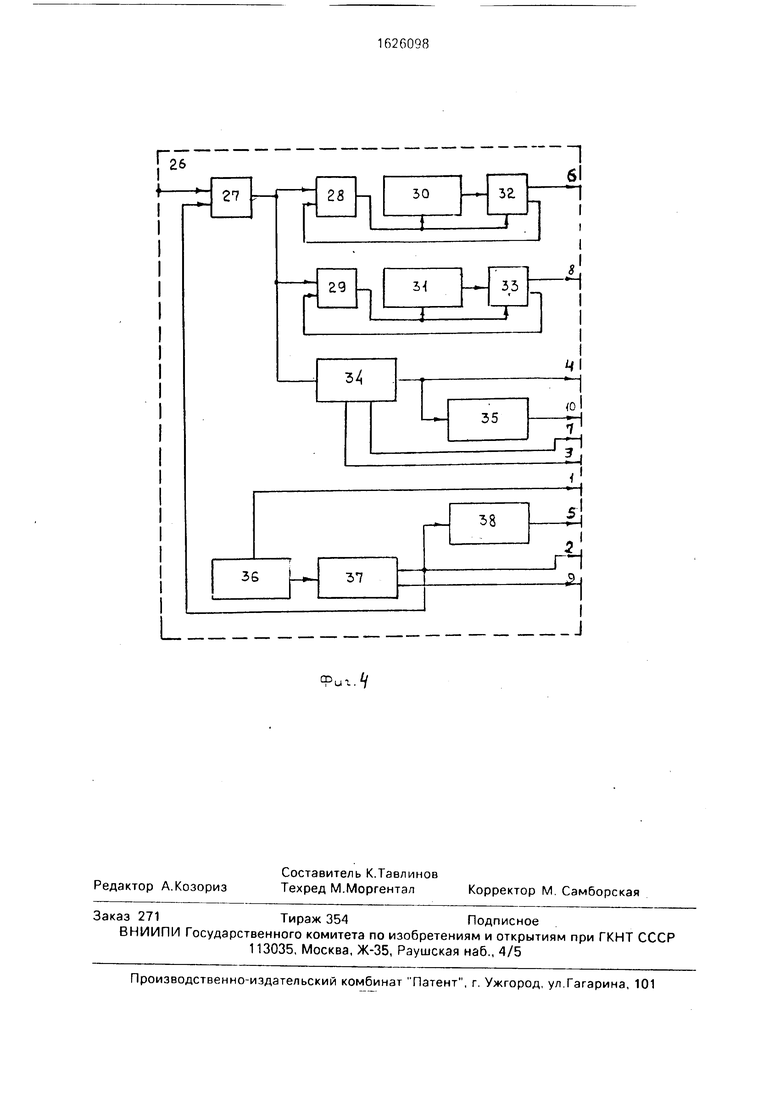

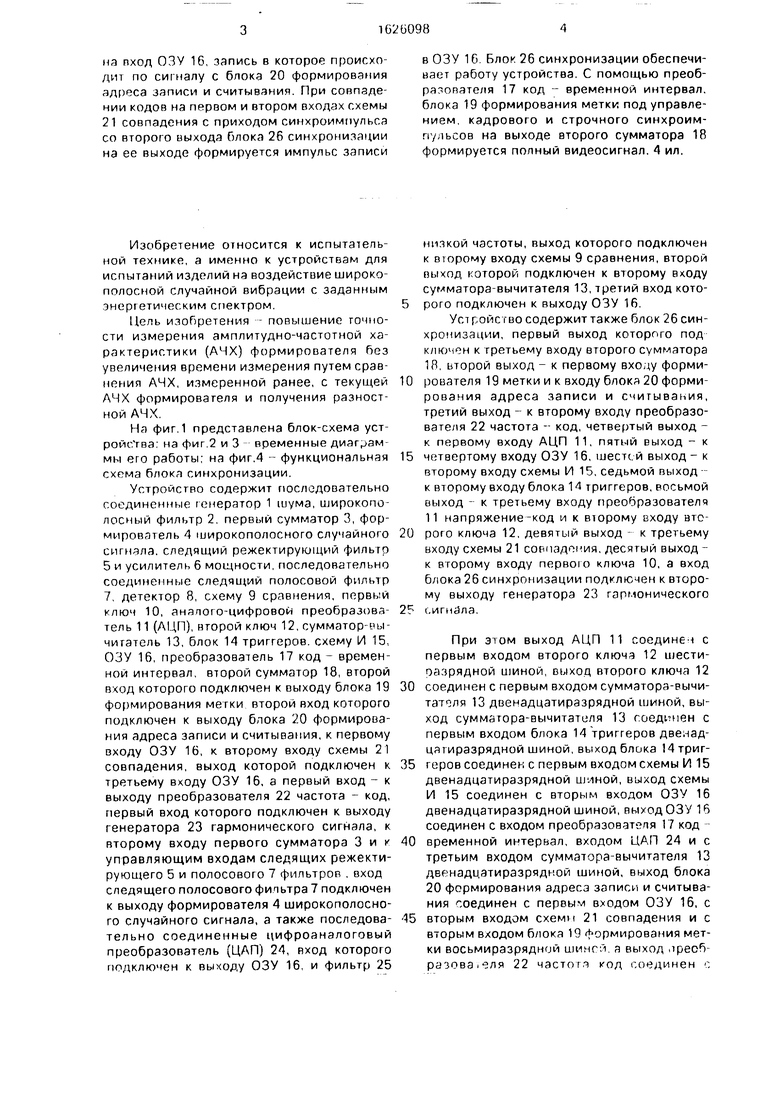

На фиг.1 представлена блок-схема уст- ройс тва: на фиг.2 и 3 временные диаграммы его работы; на фиг.4 - функциональная схема блока синхронизации.

Устройство содержит последовательно соединенные генератор 1 шума, широкополосный фильтр 2. первый сумматор 3, формирователь 4 широкополосного случайного сигнала, следящий режектирующий фильтр 5 и усилитель 6 мощности, последовательно соединенные следящий полосовой фильтр 7, детектор 8, схему 9 сравнения, первый ключ 10, анапого-цифровой преобразователь 11 (АЦП), второй ключ 12, сумматор-ш 1- читатель 13, блок 14 триггеров, схему И 15, ОЗУ 16, преобразователь 17 код- временной интервал, второй сумматор 18, второй вход которого подключен к выходу блока 19 формирования метки второй вход которого подключен к выходу блока 20 формирования адреса записи и считывания, к первому входу ОЗУ 16, к второму входу схемы 21 совпадения, выход которой подключен к третьему входу ОЗУ 16, а первый вход - к выходу преобразователя 22 частота - код, первый вход которого подключен к выходу генератора 23 гармонического сигнала, к второму входу первого сумматора 3 и к управляющим входам следящих режекти- рующего 5 и полосового 7 фильтров . вход следящего полосового фипьтра 7 подключен к выходу формирователя 4 широкополосного случайного сигнала, а также последовательно соединенные цифроаналоговый преобразователь (ЦАП) 24, вход которого подключен к выходу ОЗУ 16, и фильтр 25

низкой частоты, выход которого подключен к второму входу схемы 9 сравнения, второй выход которой подключен к второму входу сумматора-вычитателя 13, третий вход которого подключен к выходу ОЗУ 16.

Уст гюйс гво содержит также блок 26 синхронизации, первый выход которого под ключей к третьему входу второго сумматора 18, второй выход - к первому входу формирователя 19 метки и к входу блока 20 формирования адреса записи и считывания, третий выход - к второму входу преобразователя 22 частота -- код, четвертый выход - к первому входу АЦП 11, пятый выход - к

четвертому входу ОЗУ 16, шесте.и выход - к второму входу схемы И 15, седьмой выход - к второму входу блока 14 триггеров, восьмой выход - к третьему входу преобразователя 11 напряжение-код и к второму входу второго ключа 12, девятый выход - к третьему входу схемы 21 совпадения, десятый выход- к второму входу первою ключа 10, а вход блока 26 синхронизации подключен к второму выходу генератора 23 гармонического

(.игндла.

При этом выход АЦП 11 соединен с первым входом второго ключа 12 шести- оазрядной шиной, выход второго ключа 12

соединен с первым входом сумматора-вычитателя 13 двенадцатиразрядной шиной, выход сумматора-вычитателя 13 соединен с первым входом блока 14 триггеров двенадцатиразрядной шиной, выход блока 14 триггеров соединен с первым входом схемы И 15 двенадцатиразрядной шиной, выход схемы И 15 соединен с вторым входом ОЗУ 16 двенадцатиразрядной шиной, выход ОЗУ 16 соединен с входом преобразователя 17 код

временной интервал, входом ЦАП 24 и с третьим входом сумматора-вычитателя 13 двенадцатиразрядной шиной, выход блока 20 формирования адреса записи и считывания соединен с первым входом ОЗУ 16, с

вторым входом схемм 21 совпадения и с вторым входом блока 19 формирования метки восьмиразрядной шингй а выход ,треог - разова ля 22 частота код соединен с

первым входом схемы 21 совпадения вось миразрядной шиной

Блок 26 синхронизации состоит из первой 27, второй 28 и третьей 29 схем И, пер вого 30 и второго 31 счетчиков, первого 32 и второго 33 триггеров, импульсного распре делителя 34, делителя 35 на три частоты импульсного сигнала, генератора 36 строчного и кадрового синхроимпульсов делителя 37 на две частот ы строчного синхроимпульса и ждущего мультивибратора 38

Устройство работает следующим образом

Случайный сигнал с выхода генератора 1 шума поступает на вход широкополосного фильтра 2, который формирует случайный сигнал в требуемом диапазоне частот С выхода широкополосно о фильтра 2 сигнал поступает на первый вход первого сумматора 3, на второй вход которого одновременно поступает сигнал с выхода генератора 23 гармонического сигнала Далее суммарный гармонический и случайный сигнал поступает на вход формирователя 4 сигнала возбуждения с регулируемой АЧХ С выхода формирователя 4 широкополосного случайного сигнала суммарный сигнал поступает одновременно на входы следящих режекти рующего 5 и полосового 7 фильтров

Центральная частота этих фильгрор перестраивается с помощью сигнала, снг маемого с выхода генератора 2Т гармонии ского сигнала, и равна мгновенной час г г гармонического сигнала С выхода с еддщ го режектирующего фильтра 5 широкого лосный случайный сигнал без гармонично ои составляющей поступает на вход усилителя 6 мощности. С выхода следящего полосовс го фильтра 7 выделенная гармоническая го ставляющая поступает на вход детекторе 8 с выхода которого сигнал в виде постоям ного напряжения,пропорционального амплитуде гармонической составляющей поступает на вход схемы 9 сравнения, л втором входе которой при первом цикле измерения АЧХ формирователя отсутствует, так как на вход ЦАП 24 поступает код нуле вого уровня

При этом на выходе схемы 9 сравнения присутствует постоянное напряжение, равное постоянному напряжению на ее первом входе, которое через первый ключ 10 поступает на второй вход АЦП 11, который преобразует постоянное напряжение в параллельный шестиразрядный цифровой код Преобразование происходит с приходом трех последовательных тактовых импульсов на первый вход АЦП 11 (фиг.2ж)

При этом по первому тактовому импульсу происходит запоминание на внутренних

компараторах АЦП 11 пходной вепичины напряжения по второму тактовому импульсу фиксируется выходной код преобразованного входного напряжения на выходах преобразователя напряжение код (через 50 с) а по третьему сброс данного выходного кода (также через 50 с) Одновременно с задним фронтом первого тактового импульса на второй вход первого ключа 10 посту0 паег импульс запрета (фиг 2з). который закрывает первый ключ 10 до момента совпадающего с задним фронтом третьего тактового импульса

С выхода АЦП 11 параллельный шести5 разрядный цифровой код поступает на первый вход второго ключа 12 (фиг За), на второй вход которого поступает напряжение логического О при котором на выходе второго ключа 12 шесть младших разрядов

0 имеют значение логического О а шесть старших разрядов соответствуют параллельному шестиразрядному цифровому коду, который поступает на первый вход второго ключа 12 С выхода второго ключа

5 12 параллельный дьенадцатиразрядный цифровой код поступает на первый вход сумматора-вычитателя 13, на третий вход коюоого поступает параллельный двенад- цагирачояднни код с ьькода ОЗУ 16 (фиг 36)

i,n|)H ,(1,клс измерен и i ХЧХ фор мировлтеля loeHci/.L s ь ИМРЮ значение ло HMICKOIG 0 ) На в of зход

OVf1MclTO,J( ВЫЧИ1 ,J I «МЧ . } nnriyn,i(3T СИГНсЭЛ

второго (Л .хемы Э cpd (ля Если

L постоянное ч прчч- ми г ропсрцио,)пь- НОР амптит дс г я, ri ИЧР ,кой оставляю щей на первом 0л, емы 9 сравнения, богьше |1остсчнною ня(,рлжения на ыором р j/ie схемы 1 и1- то с второго выхо0 да схемы 9 сравнения напряжение логического О nocrvnaeT на вчерти вход сумматора-вычитателя 13 Напряжение логического 0 на втором входе суммато- ра-вычига Г ля 13 означает операцию сли при котооои значение кода на первом входе складывается со значением кода на трет ем входе сумматора-вычитателя 13

При этом происходит операция сложения

0 значения кода на первом вхэд из значения чода на третьем входе сумматора-вычитателя 13. С выхода сумма гора-вычитателя 13 просуммированный (в соответствии со знаком) параллельный двенадцатиразрядный

5 цифровой код поступает на первый вход блока 14 триггеров на второй вход которого гост/поеттактовый импульс (фиг Зв), который совпадает с третьим тактовым импульсом, поступающим на третий вход преобразователя 11 напряжение-код (фиг 2ж) По фронту

этого тактового импульса происходит запоминание параллельного двенадцатиразрядного цифрового кода, значение которого устанавливаются на прямых выходах блока 14 триггеров (фиг.Зг) и поступает на первый вход схемы 15, на второй вход которой поступает напряжение логической 1,

Значение параллельного двенадцатиразрядного цифрового кода устанавливается на выходе схемы И 15 без изменения и поступает на второй вход ОЗУ 1 С. По адресу, выставляемому на выходе блока 20 формирования адреса записи и считывания (фиг.Зд), который поступает на первый вход ОЗУ 16 и импульса записи с выхода схемы 21 совпадения (фиг Зз), который поступает на третий вход ОЗУ 16, происходит запись информации, которая подается на второй вход ОЗУ 16. На первый вход схемы 21 совпадения с выхода преобразователя 22 час тота-код поступает код частоты (фиг Зж). Н- второй вход схемы 21 совпадения с выхода блока 20 формирования адреса записи и считывания поступает код адреса записи который увеличивает свое значение на единицу с приходом на его вход последующего нечетного строчного синхроимпульса (фиг.26). На третий вход схемы 21 совпадения поступают четные строчные синхроимпульсы (фиг 2в). При совпадении кодов на первом и втором входах с приходом четного строчного синхроимпульса на третий вход схемы 21 совпадения на ее выходе форми руется импульс записи (фиг.Зз), который по ступает на третий вход ОЗУ 16.

Частота получаемых отсчетов Ри ЛЧХ формирователя определяется верхней частотой огибающей частотной характеристики fB и скоростью изменения частоты Я генератора гармонического сигнала, а именно F0 2A/fB.

С частотой FQ происходит запуск преобразователя 22 частота-код, запуск преобра зователя 11 напряжение-код и коммутация первого ключа 10. Таким образом сканируется весь частотный диапазон от fH до fB с частотой отсчетов F0 и происходит запись в ОЗУ 16 АЧХ устройства. Тактовые импульсы с частотой FO с второго выхода генератора 23 гармонического сигнала поступают нэ вход блока 26 синхронизации (фиг.2е). В момент совпадения тактового импульса F0 с первым нечетным строчным синхроимпульсом образуются импульсы запуска на третьем, четвертом, пятом, седьмом и восьмом выходах блока 26 синхронизации(фиг.2г,ж,з и Зв,е). При последующих циклах измерения, начиная с второго, сигнал в виде постоянного напряжения, пропорционального

амплитуде гармонической составляющей, поступает на первый вход схемы 9 сравнения, на второй вход которой поступает постоянное напряжение, пропорциональное

амплитуде этой же гармонической составляющей предыдущего цикла измерения. С первого выхода схемы 9 сравнения разностное напряжение через первый ключ 10 поступает на первый вход преобразователя 11

напряжения-код. Так. как амплитуда разностного напряжения во много раз меньше амплитуд постоянных напряжений, пропорциональных амплитуде гармснич- ,ко составляющей при текущем и предиествующем циклах измерений, диапазоны входных напряжений АЦП 11 при последующих циклах измерения, начиная с второго, следует уменьшить до величины соответ гл чующего возможному максимальному

разностному напряжению Этот диапазон входных напряжений выбирается равным шагу АЦП 11 при первом цикле измерения Для этого на его третий вход поступает напряжение логической 1.

С выхода АЦП 11 параллельный шестиразрядный цифровой код поступает на первый вход второго ключа 12, нп второй вход которого поступает напряжение логической 1, при котором на выходе второго ключа

12 шесть старших разрядов имеют значение , о; ; ЧРСКОГО О, а шесть младших разрядов соответствуют шестирэзрядному цифровому коду, который постуг.л-. т на первый вход второго ключа 12. С выхода второго ключа

12 параллельный д«енадця иразряднь й цифровой код поступает на первый вход сумматора-вычитателя 13 на третий вход которого поступает параллельный две.од- цатиразрядный цифровой коде выхода ОЗУ

16 (при последующих циклах измерения /ЛЧХ формирователя двенадцатиразррдный цифровой код имеет значение, пропорциональное амплитуде гармонической составляющей предшествующего цикла

измерения). В остальном работа при втором и последующих циклах измерения совпадает с работой при первом цикле измерения. Перед началом работы происходит запись логического О во все разряды ОЗУ 16 пу

тем подачи логического О на второй вход схемы И 15, на выходе которой псе двенадцать разрядов имеют значение логического О и поступают на второй вход ОЗУ 16. Считывание на индикатор АЧХ формирователя происходит следующим образом. Блок 20 формирования адреса записи и считывания вырабатывает код адреса считывании (фиг.Зд), который поступает на первый вход ОЗУ 16, и с приходом на четвертуй

вход ОЗУ 16 импульса считывания (фиг 2г) с частотой, соответствующей нечетному синхроимпульсу, происходит сквозное считывание информации из ОЗУ 16.

С выхода ОЗУ 16 информация в виде параллельного двенадцатиразрядного циф рового кода через преобразователь 17 код - временной интервал поступает на первый вход второго сумматора 18. Одновременно код адреса считывания поступает на второй вход блока 19 формирования метки.

Блок 19 формирования метки с приходом на его первый вход нечетного строчного синхроимпульса вырабатывает сигнал-метку, поступающий на второй вход второго сумматора 18. Этот сигнал необходим для индикации текущего положения на частотной оси.

Блок 26 синхронизации вырабатывает строчный и кадровый синхроимпульсы, поступающие с первого выхода блока 26 синхронизации на третий вход второго сумматора 18. Таким образом, на выходе вто рого сумматора 18 получается полный видеосигнал, который можно подать ча видеоусилитель любого видеоконтрольного устройства, На экране индикатора видеоканального устройства АЧХ форг ироьчге я индицируется в виде вертикальных линии огибающая которых описывает функцию .т меренной АЧХ.

Формула изобретения

Устройство для испытания изделий на случайную вибрацию, содержащее последовательно соединенные генератор шума, широкополосный фильтр, первый сумматор формирователь широкополосного случайного сигнала, следящий режектирующий фильтр и усилитель мощности, последовательно соединенные оперативно-запоминающее устройство (ОЗУ), преобразователь код временной интервал и второй сумматор, блок синхронизации, блок формирования метки, блок формирования адреса записи и считывания, преобразователь частота-код, следящий полосовой фильтр, первый вход которого подключен к выходу формирователя широкополосного сигнала, генератор гармонического сигнала, к первому выходу которого подключены второй

вход первого сумматора, управляющие входы следящих режектирующего и полосового фильтров и первый вход преобразователя частота-код, и аналого-цифровой преобразователь (АЦП), второй вход второго сумматора подключен к выходу блока формирования метки, третий вход второго сумматора подключен к первому выходу блока синхронизации, второй выход которого подключей к входу блока формирования адреса записи и считывания и к первому входу блока формирования метки, второй вход которого подключен к выходу блока формирования адреса записи и считывания и к

первому входу ОЗУ, третий выход блока синхронизации подключен к второму входу преобразователя частота-код,четвертый выход блока синхронизации подключен к первому входу АЦП, отличающееся тем, что с

целью повышения точности измерения амплитудно-частотной характеристики, в него введены последовательно соединенные детектор, вход которого подключен к выходу следящего полосового фильтра, схема

сравнения, первый ключ, выход которого подключен к второму входу АЦП, последовательно соединенные второй ключ, первый вход которого подключен к выходу АЦП суммлтор-вычитэтель, блок триггеров схг

ма И ьыход которой подключен к второму входу ОЗУ, последовательно с: диненные ци(1 роаналоговый преобразовалель, .ход которого подключен к e 1ходу ОЗУ, и филчтр низкой частоты, выхоц котгчюго подключен

к второму входу с ,. пы сравнения, вгорор ,п оторой подключен к второму входу сумматора-вычитате я, третий вход которого подключен к выходу ОЗУ, и схема .совпадения, первый вход которой подключен к

выходу преобразователя частота-код, второй вход - к выходу блока формирования адреса записи и считывания, а выход - к третьему входу ОЗУ, пятый выход блока синхронизации подключен к четвертому входу

ОЗУ, шестой выход - к второму входу схемы И, седьмой выход - к второму входу блока триггеров, восьмой выход - к третьему входу АЦП и к втором/ входу второго ключа, девятый выход - к третьему входу схемы совпадения, десятый выход - к второму входу первого ключа, а вход бпока синхронизации подключен к второму выходу генератора гармонического сигнала

е ж

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1989 |

|

SU1600000A1 |

| Устройство формирования заданного спектра вибрации | 1988 |

|

SU1649342A1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

| Измеритель частотных характеристик четырехполюсника | 1988 |

|

SU1661679A1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК ЧЕТЫРЕХПОЛЮСНИКА | 1992 |

|

RU2065667C1 |

| Устройство для испытания изделий на случайную вибрацию | 1986 |

|

SU1322107A1 |

| ИМИТАТОР ПАССИВНОГО РАДИОЛОКАТОРА | 1988 |

|

SU1841093A2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| Способ компенсации фазовых искажений в многоканальных системах аналого-цифрового преобразования сигналов и устройство для его реализации | 2019 |

|

RU2723566C1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

Изобретение относится к испытательной технике. Цель изобретения - повышение точности измерения, которое достигается путем получения разностной АЧХ формирователя посредством сравнения АЧХ, измеренной ранее, с текущей АЧХ формирователя. Сигнал с генератора 1 шума поступает на вход широкополосного фильтра 2 и далее на первый сумматор 3, на второй вход которого поступает сигнал с генератора 23 гармонического сигнала. С выхода формирователя 4 широкополосного случайного сигнала суммарный сигнал поступает на входы следящих режектирующего 5 и полосового 7 фильтров. Выделенная гармоническая составляющая поступает на вход детектора 8, с выхода которого постоянное напряжение, пропорциональное амплитуде гармонической составляющей, поступает на вход схемы 9 сравнения, где сраесивается с сигналом ЦАП 24 С выхода схемы 9 сравнения через первый ключ 10 напряжение поступает на вход АЦП 11, где оно преобразуется ч шестиразрядный код, поступающий через второй ключ 12 на вход сумматора-вычитателя 13, функция которого реализуется в зависимости от сигнала с второго выхода схемы 9 сравнения. Результат запоминается в блоке 14 триггеров и через схему И 15 поступает (Л С

Л.

п

|J

Put.ty

CD

| Автоматическое устройство для регистрации частотных характеристик | 1980 |

|

SU1002849A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для испытания изделий на случайную вибрацию | 1986 |

|

SU1322107A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-02-07—Публикация

1989-01-16—Подача