Изобретение относится к виброиспытательной технике и может быть использовано для формирования заданного спектра вибрации в процессе виброиспытаний .

Цель изобретения - повышение производительности виброиспытаний за счет уменьшения времени определения параметров формирующих фильтров.

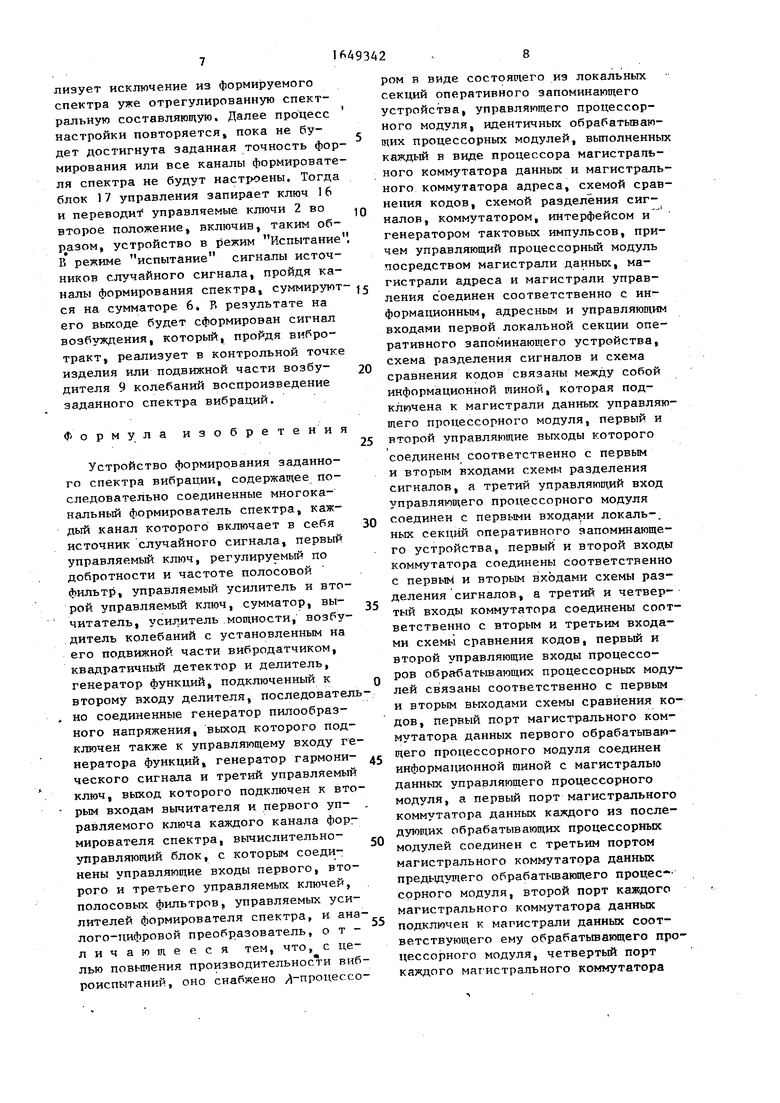

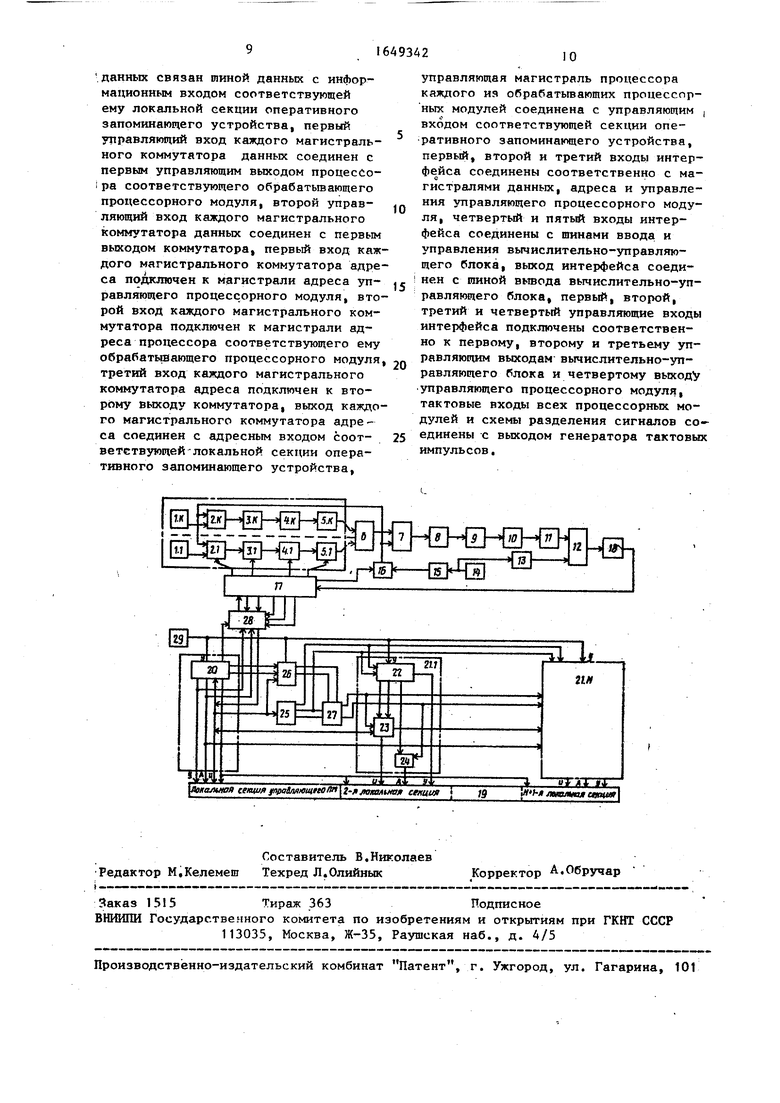

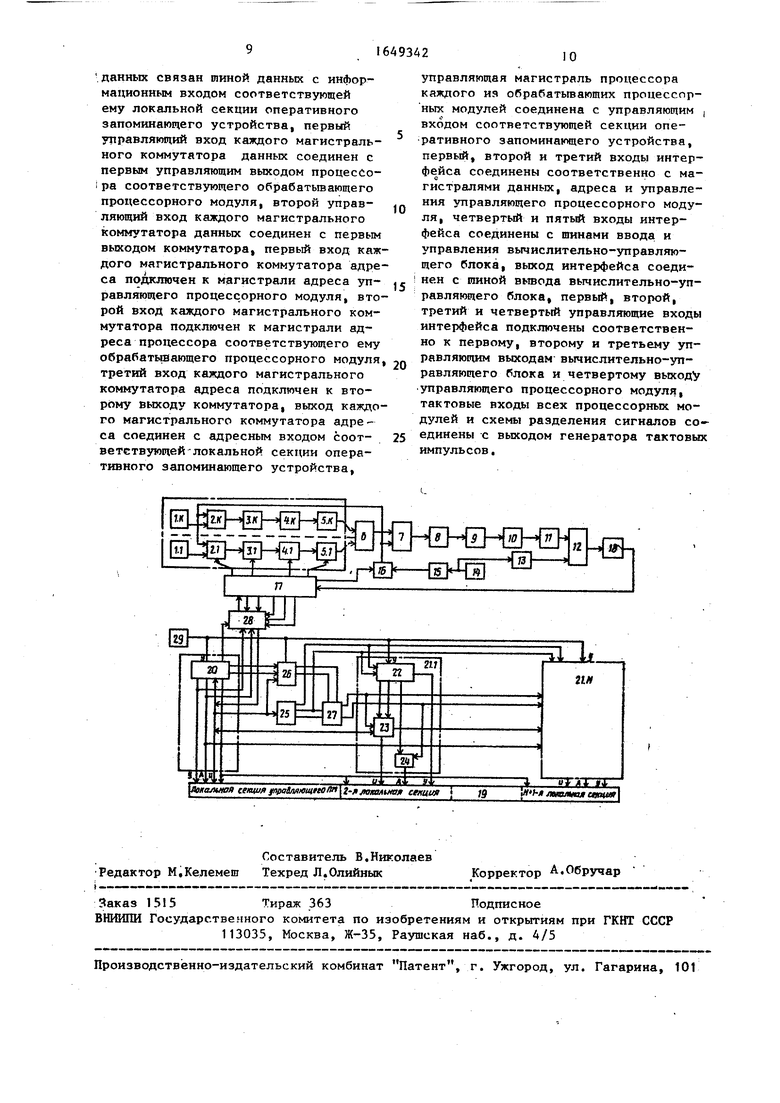

На чертеже приведена блок-схема устройства формирования заданного спектра вибрации.

Устройство содержит последовательно соединенные многоканальный формирователь спектра, каждый канал которого включает в себя источник 1 случайного сигнала, первый управляемый ключ 2, регулируемый по добротности и час тоте полосовой фильтр 3, управляемый усилитель 4 и второй управляемый ключ 5, сумматор 6, вычитатель 7, усилитель Я мощности, возбудитель 9

колебаний с установленным на его подвижной части вибродатчиком 10, квадратичный детектор II и делитель 12, к второму входу которого подключен генератор 13 функций, последовательно соединенные генератор 14 пилообразного напряжения, выход которого подключен также к управляющему входу генератора 13 функций, генератор 15 гармонического сигнала и третий уп- 1 авляемый ключ 16, выход которого

г подключен к вторым входам вычитате- ля 7 и первого управляемого ключа 2 каждого канала формирователя спектра, вычислительно-управляющий блок (ВУБ) 17, с которым соединены управляющие входы первых 2 и вторых 5 управляемых ключей, полосовых фильтров

13, управляемых усилителей 4 формирователя спектра и третьего управляемого ключа 16, аналого-цифровой преобразователь (АЦП) 18, вход которо$

СО

Ј

кэ

го соединен с выходом делителя 12, а выход - с входом ВУБ 17, А-процессор, содержащий разделенное на N локальных секций оперативное запоминающее устройство (ОЗУ) 9, управляющий процессорный модуль (ПМ) 20, который посредством магистрали данных, магистрали адреса и магистрали управления соединен соответственно с ин- формационным (И), адресным (А) и управляющим (У) входами первой локальной секции ОЗУ 19, идентичные обрабатывающие процессорные модули (ПМ) 21.1-21.N, выполненные каждый в виде процессора 22, магистрального коммутатора 23 данных (МКД) и магистрального коммутатора 24 адреса, схему 25 сравнения кодов (ССК), схему 26 разделения сигналов (СРС), коммутатор 27, интеррейс 28 и генератор 29 тактовых импульсов.

Устройство работает следующим образом.

Осуществляется загрузка управляю- щей программы и программы параллельного выполнения алгоритма прямого и обратного дискретного преобразования Фурье (ДПФ) в первую локальную секцию ОЗУ 19 из ВУБ 17 через интер- рейс 28.

В режиме Настройка все ключи, кроме 16, по команде ВУБ 17 замкнуты. Гармонический сигнал генератора 15 сканируется в рабочем диапазо- не частот с помощью генератора 14 пилообразного напряжения и поступает через ключ 16, вычитатель 7, усилител 8 мощности на вход возбудителя 9 колебаний. Механические колебания возбудителя 9 колебаний преобразуют «- ся в электрический сигнал установлен- 1 ным на изделии вибродатчиком 10. На выходе квадратичного детектора 11 будет периодический сигнал с периодом т, равным периоду генератора 14 пилообразного напряжения. Генератор 13 функций формирует сигнал с тем же периодом Т, по форме эквивалентный заданному спектру. Сигнал на выходе усилителя 8 после операции деления по форме соответствует форме спектра, который необходимо сформировать с помощью фильтров 3 для того, чтобы воспроизвести заданный спектр в контролируемой точке изделия. Далее этот сигнал поступает на АЦП 18, где он преобразуется в цифровую форму с частотой выборки, определяемой частотой генератора 29. ВУБ 17 в определенные моменты времени осуществляет подключение АЦП 18 к управляющему ПМ 20. В результате выборка в виде цифрового кода, полученная с выхода АЩ 18, поступает на управляющий ПМ 20 и далее в соответствии с управляющей программой рассылается в соответствующие локальные секции ОЗУ 19, организуя память данных (ПД) обрабатывающих ПК 21 по закону, заданному программно. По окончанию приема выборки управляющий ПМ 20, обращаясь к ОЗУ 1, начинает выполнять SIMD-программу вычисления дискретного преобразования Фурье. Одновременно ССК 25 вырабатывается с выхода 1 сигнал, осуществляющий начальный запуск обрабатывающих ПМ 21 ,

В соответствии с упомянутым- алгоритмом команды из памяти команд (ПК) ОЗУ 19 последовательно поступают на все ПМ 21, и все активные в данный момент времени ПМ 21 выполняют каждую из этих команд с данными, расположенными в локальных секциях ОЗУ 19

Подробно это происходит следующим образом, В системе использована СРС 26 связана с управляющим ПМ 20. Когд ПМ 20 приступает к выполнению SIMD- программы, он выставляет адрес памяти команд и формирует сигнал Чтение памяти, который проходит через СРС 26, разделяясь на два взаимоисключающих сигнала Чтение команды (выход 1) и чтение данных (выход 2) которые, проходя через коммутатор 27 управляют МКД 23 и МКА 24 обрабатывающих ПМ 21, обеспечивая необходимое прохождение данных из ПК или из локальных секций ОЗУ 19. В результат по сигналу Чтение команды происходит переключение МКД 23 на режим чтения команды из ПК, а так как все ПМ 21 работают от одних и тех же фаз ГТИ 29 и подключены посредством МКД 23 к ПК ОЗУ 19, происходит, синхронный прием команды в них. По сигналу Чтение данных МКД 23 и МКА 24 ПМ2Ч переключаются на Чтение данных из соответствующих локальных секций ОЗУ 19, а сигналы с управляющего выхода ПМ 21 управляют направлением передачи этих данных, т.е. из ПМ 21 в ОЗУ 19 или наоборот. Таким образом, SIMD-программа из ПК- ОЗУ 19 выполняется всеми процессоXP,(1)-XP A(1-1)

к

л|ЯГ(р7-Ъа) (р1-)

Хр1(1)-Хр11(1-2).

К

К

ficp -tf) ф7()

ехр

К

7()

, ехр

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| МНОГОПРОЦЕССОРНЫЙ МОДУЛЬ | 2008 |

|

RU2397538C1 |

| МУЛЬТИПРОЦЕССОРНАЯ СИСТЕМА ВВОДА И ПРЕДВАРИТЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2006930C1 |

| УСТРОЙСТВО КОНТРОЛЯ ОДНОКРИСТАЛЬНОГО МИКРОКОНТРОЛЛЕРА | 2003 |

|

RU2248606C1 |

| УСТРОЙСТВО АУТЕНТИФИКАЦИИ ПРОГРАММНЫХ МОДУЛЕЙ | 1998 |

|

RU2146834C1 |

| Многоканальная система обмена для управления электропитанием вычислительного комплекса | 1988 |

|

SU1654830A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

Изобретение относится к виброиспытательной технике и может быть использовано для формирования заданного спектра вибрации в процессе внб- роиспытаний. Цель изобретения - повышение производительности виброиспытаний - достигается за счет автоматизации настройки коэффициента усиления, добротности и частоты формирующих фильтров путем реализации итерационного процесса настройки формирующих фильтров при помощи многопроцессорной системы в виде fl-процессора, выполняющей прямое и обратное дискретные преобразования урье в процесса настройки фильтров. 1 ил.

где Хп(1) - значение сигнала при (j)0 J Х- (1-1) - значение сигнала при

расстройке ±ДСО|; X (1-2) - значение сигнала при

расстройке± iCOg.

Таким образом, управляющий ПМ 20 в этот момент имеет информацию о средней частоте С00 , полосе пропускания (i и коэффициенте передачи К первого канала Формирователя спектра. Эта информация, в соответствии с управляющей программой, через интеррейс

28 поступает в ВУР 17. Он преобразует ее в. форму, необходимую для управления, и устанавливают на Формирующем фильтре 3 и управляемом усилителе 4 первого канала формирователя эти параметры, устанавливает первый управляемый ключ 2 в первое положение и замыкает второй управляемый ключ 5 этого канала, что обеспечивает прохождение сигнала генератора 15 через канал и поступление его на второй вход вычитателя 7, Вычитатель 7 pea™

лизует исключение из формируемого спектра уже отрегулированную спектральную составляющую. Далее процесс настройки повторяется пока не будет достигнута заданная точность формирования или все каналы формирователя спектра не будут настроены. Тогда блок 17 управления запирает ключ 16 и переводи управляемые ключи 2 во второе положение, включив, таким образом, устройство в режим Испытание. В режиме испытание сигналы источников случайного сигнала, пройдя каналы формирования спектра, суммируют- ся на сумматоре 6, Р результате на его выходе будет сформирован сигнал возбуждения, который, пройдя вибротракт, реализует в контрольной точке изделия или подвижной части возбу- дителя 9 колебаний воспроизведение заданного спектра вибраций.

Формула изобретения

Устройство формирования заданного спектра вибрации, содержащее последовательно соединенные многоканальный формирователь спектра, каждый канал которого включает в себя источник случайного сигнала, первый управляемый ключ, регулируемый по добротности и частоте полосовой Фильтр, управляемый усилитель и второй управляемый ключ, сумматор, вы- читатель, усилитель мощности, возбудитель колебаний с установленным на его подвижной части вибродатчиком, квадратичный детектор и делитель, генератор функций, подключенный к второму входу делителя, последовательно соединенные генератор пилообразного напряжения, выход которого подключен также к управляющему входу генератора функций, генератор гармони- ческого сигнала и третий управляемый ключ, выход которого подключен к вторым входам вычитателя и первого управляемого ключа каждого канала формирователя спектра, вычислительно- управляющий блок, с которым соединены управляющие входы первого, второго и третьего управляемых ключей, полосовых фильтров, управляемых усилителей формирователя спектра, и аналого-цифровой преобразователь, отличающееся тем, что, с целью повышения производительное ™ виброиспытаний, оно снабжено -процессоQ5 0

5

0 с Q Q

ром в виде состоящего из локальных секций оперативного запоминающего устройства, управляющего процессорного модуля, идентичных обрабатывающих процессорных модулей, выполненных каждый в виде процессора магистрапь- ного коммутатора данных и магистрального коммутатора адреса, схемой сравнения кодов, схемой разделения сигналов, коммутатором, интерфейсом и генератором тактовых импульсов, причем управляющий процессорный модуль посредством магистрали данных, магистрали адреса и магистрали управления соединен соответственно с информационным, адресным и управляющим входами первой локальной секции оперативного запоминающего устройства, схема разделения сигналов и схема сравнения кодов связаны между собой информационной тиной, которая подключена к магистрали данных управляющего процессорного модуля, первый и второй управляющие выходы которого соединены соответственно с первым и вторым входами схемы разделения сигналов, а третий управляющий вход управлятацего процессорного модуля соединен с первыми входами локаль-. ных секций оперативного запоминающего устройства, первый и второй входы коммутатора соединены соответственно с первым и вторым входами схемы разделения сигналов, а третий и четвертый входы коммутатора соединены соответственно с вторым и третьим входами схемы сравнения кодов, первый и второй управляющие входы процессоров обрабатывающих процессорных модулей связаны соответственно с первым и вторым выходами схемы сравнения кодов, первый порт магистрального коммутатора данных первого обрабатывающего процессорного модуля соединен информационной шиной с магистралью данных управляющего процессорного модуля, а первый порт магистрального коммутатора данных каждого из последующих обрабатывающих процессорных модулей соединен с третьим портом магистрального коммутатора данных предыдущего обрабатывающего процессорного модуля, второй порт каяадого магистрального коммутатора данных подключен к. магистрали данных соответствующего ему обрабатывающего процессорного модуля, четвертый порт каждого магистрального коммутатора

данных связан тиной данных с индюр- мационным входом соответствующей ему локальной секции оперативного запоминающего устройства, первый управляющий вход каждого магистрального коммутатора данных соединен с первым управляющим выходом процесео- ра соответствующего обрабатывающего процессорного модуля, второй управляющий вход каждого магистрального коммутатора данных соединен с первым выходом коммутатора, первый вход каждого магистрального коммутатора адреса подключен к магистрали адреса уп- равляющего процессорного модуля, второй вход каждого магистрального коммутатора подключен к магистрали адреса процессора соответствующего ему обрабатывающего процессорного модуля, третий вход каждого магистрального коммутатора адреса подключен к второму выходу коммутатора, выход каждого магистрального коммутатора адре- са соединен с адресным входом соответствующей -локальной секции оперативного запоминающего устройства,

алыюя секция рчю&ля вщю11я г- лаю1лиюя секция } }Ц N t-t лыалюяиктя

п

5

управляющая магистраль процессора каждого из обрабатывающих процессорных модулей соединена с управляющим , входом соответствующей секции оперативного запоминающего устройства, первый, второй и третий входы интерфейса соединены соответственно с магистралями данных, адреса и управления управляющего процессорного модуля, четвертый и пятый входы интерфейса соединены с шинами ввода и управления вычислительно-управляющего блока, выход интерфейса соединен с шиной вывода вычислительно-управляющего блока, первый, второй, третий и четвертый управляющие входы интерфейса подключены соответственно к первому, второму и третьему управляющим выходам вычислительно-управляющего блока и четвертому выходу управляющего процессорного модуля, тактовые входы всех процессорных модулей и схемы разделения сигналов соединены с выходом генератора тактовых импульсов.

| Устройство для испытания на случайные вибрации | 1982 |

|

SU1073592A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Система формирования заданного спектра вибрации | 1984 |

|

SU1201708A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-05-15—Публикация

1988-05-30—Подача