Изобретение относится к радиотехнике и может быть использовано в приемниках навигационной аппаратуры и в системах синхронизации.

Целью изобретения является расшире- ние диапазона выходных частот.

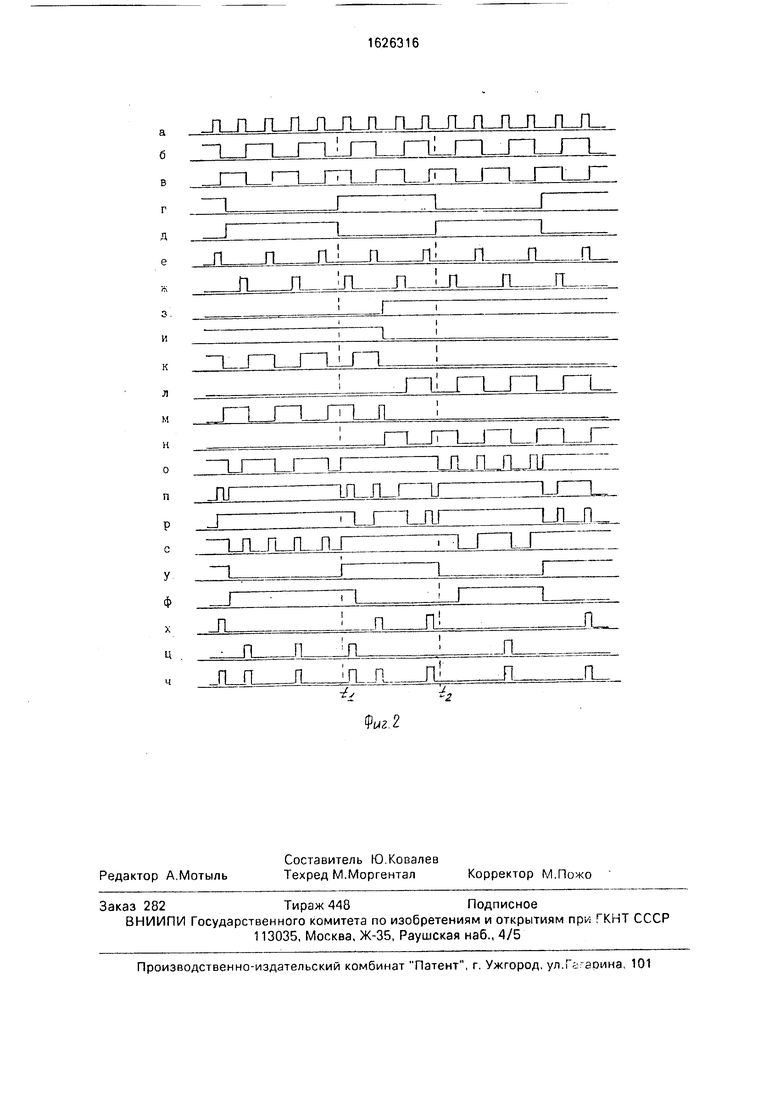

На фиг. 1 представлена структурная электрическая схема цифрового синтезатора частоты; на фиг. 2 - временные диаграммы работы синтезатора.

Цифровой синтезатор частоты содержит накапливающий сумматор (НС) 1. первый счетный триггер 2, инвертор 3. второй счетный триггер 4, демультиплексор 5, блок 6 управления мультиплексором (БУМ), муль- типлексор 7, делитель 8 частоты. При этом демультиплексор 5 состоит из первого 9 и второго 10 элементов И. БУМ 6 содержит инвертор 11, элемент 12 задержки, с первого по четвертый элементы И 13-16, с перво- го по четвертый элементы ИЛИ 17-20, первый 21 и второй 22 R-S-триггеры. Мультиплексор 7 состоит из первого 23,второго 24 элементов И и элемента ИЛИ 25.

Цифровой синтезатор частоты работает следующим образом.

На тактовый вход НС 1 поступает импульсная последовательность с частотой fTi, на кодовый вход НС 1 поступает код Zy. Частота следования импульсов на выходе переполнения НС 1 прямо пропорциональна коду Zy. Под действием неравномерной последовательности импульсов с выхода НС 1 первый счетный триггер 2 меняет свое состояние (по переднему фронту входных импульсов). Смена состояний первого счетного триггера 2 иллюстрируется его выходными сигналами (фиг. 2г, д).

На выход инвертора 3 поступает последовательность с частотой fT2 (фиг. 2а), та же последовательность поступает на информационный вход демультиплексора 5. Второй счетный триггер 4 меняет свое состояние по переднему фронту импульсов с выхода инвертора 3. Под влиянием сигналов с выхода второго счетного триггера 4 (фиг. 26, в) демультиплексор 5 разделяет входную последовательность импульсов (фиг 2а) на две последовательности с вдвое меньшей частотой (фиг. 2е, ж). Демультиплексор 5 легко реализовать на двух элементах И 9, 10, работающих как ключи, стробируемые выходными сигналами второго счетного триггера 4.

Мультиплексор 7 пропускает на выход одну из двух последовательностей (фиг. 2е, ж), формируемых демультиплексором 5. Мультиплексор 7 реализуется на первом и втором элементах И 23, 24 и на элементе ИЛИ 25. Первый и второй элементы И 23, 24

работают как ключи, стробируемые выходными сигналами БУМ 6. Выходные сигналы первого и второго элементов И 23, 24 суммируются с помощью элемента ИЛИ 25.

Синтезатор работает следующим образом.

Сигналы на выходе БУМ 6 изменяются при изменении состояния первого счетного триггера 2. При этом происходит переключение мультиплексора 7, т.е. один из ключей, выполненных на первом и втором элементах И 23. 24, закрывается логическим нулем, а другой открывается логической единицей, При каждом переключении мультиплексора 7 происходит дискретное изменение частоты следования импульсов на его выходе Рели сигнал на втором управляющем входе Г - ) он лсиимескому нулю, то переключение мультиплексора 7 происходит так, что на его выхода интервал между двумя соседними импульсами уменьшается на половину периода (ФРГ. 2ч, точка и). Последовательность импульсов как бы сжимается, средняя частота их следования растет. Если на втором управляющем входе логическая единица, то при переключении мультиплексора 7 интервал между двумя соседними импульсами на его выходе увеличивается на полпериода (фиг. 2 ч, момент тз), последовательность растягивается, частота снижается.

Управление работой мультиплексора 7 производит БУМ G.

Установка и сброс первого и второго RS-триггеров 21 и 22 производится низким уровнем CHI налов с выходов первого, второго, третьего и четвертого элементов ИЛИ 17-20. Выходы первого счетного триггера 2 подключены на первые входы первого, второго, третьего и четвертого элементов ИЛИ 17-20 таким образом, чтобы при смене состояния первого счетного триггера 2 на противоположное первый и второй RS-грнггеры 21 и 22 также поменяли свое состояние на противоположное при соответствующих сигналах на остальных сходах первого, второго, третьего и четвертого элементов ИЛИ 17-20, которые стробируются импульсами с второго тактового входа. Это делается для запрета переключений первого и второго RS-триггеров 21 и 22 в моменты времени, когда на второй тактовый вход устройства и на входы ключей мупьтиплексора 7 поступают импульсы. В противном случае форма импульсов на выходе мультиплексора 7 может быть искажена. Первый, второй, третий и четвертый элементы ИЛИ 17-20 стробируются также сигналами с выходов первого, второго, третьего и четвертого элементов И 13-16.

Если имеет место режим увеличения частоты (фиг. 2 з, и), то ключи на логических элементах И 13, 15 открыты и пропускают на выход сигналы второго счетного триггера 4 (фиг. 2к, м). Благодаря этому сигналы вы- 5 сокого уровня на входах R первого и второго RS-триггеров 21,22 (фиг. 2о, р) затягиваются на время длительности импульса на выходах второго счетного триггера 4 (фиг. 26, в). Следовательно сброс первого и второго RS- 10 триггеров 21, 22 затягивается на это же время (фиг. 2у, ф). Поэтому если произошла смена состояния первого счетнш о триггера 2 и сразу же за этим моментом (фиг. 2. момент ti), следует импульс с второго тактоьо- 15 го входа, то запирание соответствующего ключа будет задержано (в данном примере ключа на втором элементе И 24 мультиплексора 7). Импульс с второго тактового входа пройдет на выход мультиплексора 7, про- 20 изойдет сжатие последовательности (фиг 2р. ч).

Аналогично при режиме уменьшения частоты будут затягиваться моменты появления низких уровней на входах S первого 25 и второго RS-триггеров 21, 22 (фиг. 2л, н, п, с) и соответственно моменты отпирания ключей на первом и втором элементах И 23, 24 мультиплексора 7 (фиг. 2у, ф). Лишние импульсы не будут проходить на выход 30 мультиплексора 7 (фиг. 2 ц, ч, момент t2) произойдет растяжение1 последовательности.

Стробирующие импульсы с второго тактового входа цифрового синтезатора часто- 35 ты проходят через элемент 12 задержки для уравнивания времени распространения логических сигналов, поступающих на вторые и третьи входы первого, второго, третьего и четвертого элементов ИЛИ 17-20. В против- 40 ном случае возможны ложные срабатывания первого и второго RS-триггеров 21, 22 и сбои в работе цифрового синтезатора частоты.

Частота сжатий (растяжений) после- 45 довательности на выходе мультиплексора 7 и, следовательно, величина перестройки частоты следования импульсов на выходе мультиплексора 7 определяются частотой смены состояний первого счетного триггера 2. По- 50 следняя в свою очередь пропорциональна управляющему коду Zy.

Знак перестройки определяется логическим сигналом на втором входе БУМ 7. Под несущей здесь подразумевается сигнал с 55 астотой fr2 /2 на выходе мультиплексора 7. Неравномерная последовательность с выхода мультиплексора 7 поступает на делитель 8 для сглаживания фазовых флуктуации.

Средняя частота следования импульсов на входе первого счетного триггера 2 равна

NC

где тТ1 - тактовая частота накопительного сумматора 1;

Nc - его емкость:

Zy - управляющий код НС 1.

Несущая частота, т.е. частота следования импульсов на первом и втором сигнальных входах мультиплексора 7. равна

f -fr2

н-Т,

где fr2 - тактонля частота на втором тактовом входе цифрового синтезатора частоты. При одном изменении состояния первого счетного триггера 2 положение импульсов в последовательности на выходе мультиплексора 7 изменится на величину

At1 тт2 2fH

При двух изменениях состояния первого счетного триггера 2 положение импульсов изменится на величину

At2 2 Ди j-.

IH

т.е. на один период несущей частоты. Это значит, что по приходу двух импульсов на вход первого счетного триггера 2 на некотором интервале Т число импульсов в выходной последовательности мультиплексор;) 7 измените на единицу (на этом же интервале Т). Полому частота на выходе мультиплексора 7 равна

Ъ

.„4Если обозначить коэффициент деления делителя 8 через лд, то выражение для выходной частоты устройства следующее.

1

Пд

fo

пд - NC / 2 Мд Дискрет перестройки частоты и диапазон ее изменения равны соответственно

Ju.

Af

2 nANc

5f 2Nc -Af

III пд

В цифровом синтезаторе частоты можно обеспечить любую несущую частоту, ограниченную сверху только быстродействием инвертора 3, второго счетного триггера 4, де- мультиплексора 5, БУМ 6 и мультиплексора 7. Емкость НС 1 определяется только диапазоном перестройки частоты.

Неравномерность расстановки импульсов выходного сигнала во времени определяется значением тактовой частоты ftz. При изменении выходной частоты от нуля до максимума величина фазовых скачков в выходном сигнале будет изменяться СООТПРТ- ственно от 0 дг йО°

Ф о р му па изобретения

1.Цифровой сип гозэтор час™ i ы, содир- жащий пгипстощпй сумматор и делитель Ч,- 1 1П 1 ЗГОЙ КОДОВЫЙ И Г.1 СТОПЫ И

входы или п ливш-ощего сумматора являются СООТЬ , Oi -. , но i ОДОВЫМ И ПЕРВЫМ грмо

вым входами и.фрового синтезатора чэстогы, о г л и (а ю ид и г. с я тем, что, с целью рлштп |,,1ч диапазона выходных частот, введены последовательно соединенные гноями триггер блок ynpiBTi -M ri i1 три-- к г ром и г //цтиплекСОр, HJCi I ч ПНООП TOP, is i i М С С. Т 11 М к 1 р и г р р 11

Демул-лпг , . , . 1Р 11 ВТОРОМ ВЫХОДЫ

которо i , i i ел огвенпо

ВОМу И В Г Г1 риМ . I L l i я 1 ИМ P OjJlM Мул ТИплексорч . к. рой упп-1пг.1пн вход ко срогг i1 .u i -i соотвск с входом /югп г м с вторым пьио дом блонп /правле 1ч мультиплексором второй и третий которого подключены соотс гственно f инверсному выходу первого счетного триггера и к прчмому вы ходу вторг/о тчого триггера, таергый вход бло) упрпсрпгння мультип юксором объод ч - тот, Ti входом демутыиплок- сора м ror.i i ч н с инверсным выходом второго счетною триггера, тактовые инпергора, ц мх льтиплексора ii блока управления мулшиплсч сором оГэ -единены и являют-) i.ioru.M rai юпым входом цифрового синтез.иор-з мае готы, пятый вход блока управления глулг .иплеисором яьляется управляющим РХОДОМ цифрового синтезатора частоты, а выход переполнения накапливающего сумматора соединен со счетным входом первого сметною триггера.

2.Сише- чтпр по п. 1, о т л и м л ю щ й- с я тем, ч го домупыпппексор содержит первый и втором элементы И, перпый вход и выход первого элемента И являются соответственно первым входом и первым выходом демультиплексора, первый вход и выход второго элемента И является соответственно вторым t ходом и вторым выходом демультиплексора, второй вход первого элемента И соединен г вторым входом второго элемента И и является тактовом входом демультиплексора.

3.Синтезатор по п. 1, о т л и ч а го щ и й- с я тегл что блек управления мулыиплексо.- ром содержит последовательно соединенные инвертор, первый элемент И первый элемент ИЛИ и первый RS-триггер, последовательно соединенные второй элемент И и второй элемент ИЛИ, последовательно соединенныетретий элемент И, третий элемент ПЛИ и второй RS-триггер, последовательно соединенные четвертый элемент И и четвертый элемент ИЛИ, второй вход которого объединен с вторым входом первого элемента

ИЛИ, вторым входом второго элемента ИЛИ и вторым входом третьего элемента ИЛИ и подключен к ьыходу элемента задержки, вход которого является тактовым входом блока управления мультиплексором выход

второго прмента ИЛИ соединен с S-BXO- дом перье о RS-тритгера, выход которого является первым выходом блока управления мультиплексором выход четвертого элемента ИЛИ подключен к S-входу второго

RS-Tpnirepa, выход которого является вторым выходом блока управления мультиплексором, третий вход первого элемента ИЛИ соединен с третьим входом четвертого элемента ИЛИ и является первым входом блока

управления мультиплексором, третий вход второго элемента ИЛИ подключен к третьему входу третьего элемента ИЛИ и является вторым входом блока управления мультиплексором, второй вход первого элемента И

соединен с первым входом второго элемен- тя 1/1 и является третьим входом блока управления мультиплексором, первый вход третьего элемента И подключен к первому входу четвертого элемента И и является четвертым входом блока управления мультиплексором, второй вход третьего элемента И соединен с выходом инвертора, вход которого подключен к второму входу второго элемента И, к второму входу четвертого элемента И и является плтым входом блока управления мультиплексором.

4. Синтезатор по п. 1,отличающий- с я тем, что мупьтиплексор содержит последовательно соединенные первый элемент И

и элемент ИЛИ и второй элемент И, выход которого подключен к второму входу элемента ИЛИ, выход которого является выходом мультиплексора, первый пход первого элемента И и первый вход второго элемента

И являются соответственно первым и вторым управляющими входами мультиплексора, второй вход первого элемента И и второй вход сторого элемента И являются соответственно первым и вторым сигнальными входами мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221755A1 |

| Цифровой компенсатор выпадений телевизионного сигнала яркости | 1985 |

|

SU1269274A1 |

| Синтезатор частот | 1988 |

|

SU1566455A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1396277A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Цифровой синтезатор частот | 1988 |

|

SU1518865A2 |

Изобретение относится к радиотехнике. Цель изобретения - расширение диапазона выходных частот. Цифровой синтезатор частоты содержит накапливающий сумматор (НС) 1. первый счетный триггер 2, инвертор 3, второй счетный триггер 4, демультиплек- сор 5, блок управления мультиплексором У, п (БУМ) 6, мультиплексор 7, делитель 8 частоты. При этом демультиплексор 5 содержит первый и второй элементы И 9, 10. БУМ 6 состоит из инвертора 11, элемента 12 задержки, с первого по четвертый элементы ИЛИ 17-20, первого и второго RS-триггеров 21, 22. Мультиплексор 7 содержит первый и второй элементы И 23, 24 и элемент ИЛИ 25. НС 1 и первый счетный триггер 2 образуют низкочастотный тракт и формируют сетку точной подстройки частоты с малым дискретом. В высокочастотном канале (инвертор 3, второй счетный триггер 4, демультиплексор 5, БУМ 6) формируется импульсная последовательность несущей частоты. С помощью сигнала с выхода первого счетного триггера 2 производится управление частотой несущего колебания. Один из сигналов на управляющем входе мультиплексора 7 определяет направление перестройки частоты. 3 з.п. ф- лы, 2 ил. (Л о ю ON CJ Фцг.1

| Гнатек Ю.Р | |||

| Справочник по цифро-аналоговым и аналогоцифровым преобразователям | |||

| - М.: Радио и связь, 1982, с | |||

| Гудок | 1921 |

|

SU255A1 |

| Алешин В.Г | |||

| и др | |||

| Радиопередающие устройства, синтезаторы частоты | |||

| М., 1978, с | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

Авторы

Даты

1991-02-07—Публикация

1989-02-27—Подача