ется пороговый уровень, а следовательно, и тот момент, когда можно прекратить наблюдения (так как заданная точность идентификации уже достигнута) и сформировать на выходе предлагаемого устройства искомый результат, специальным образом пронормировав при этом последнее наблюдение идентифицируемого случайного процесса.

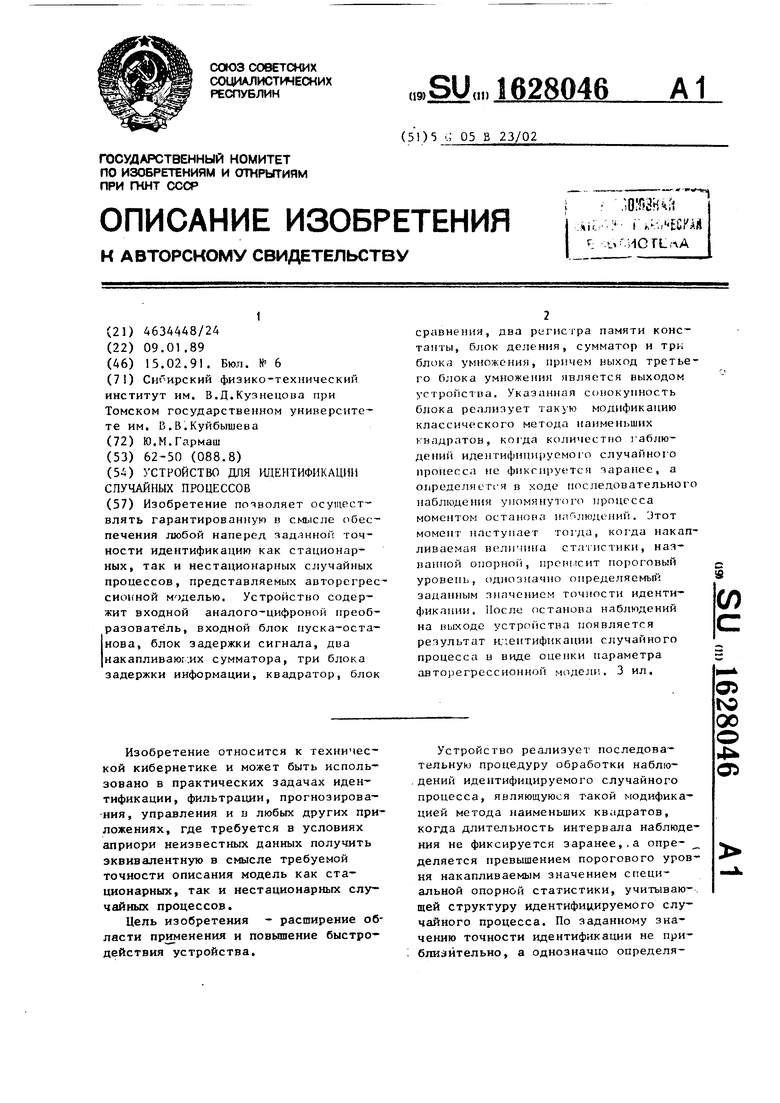

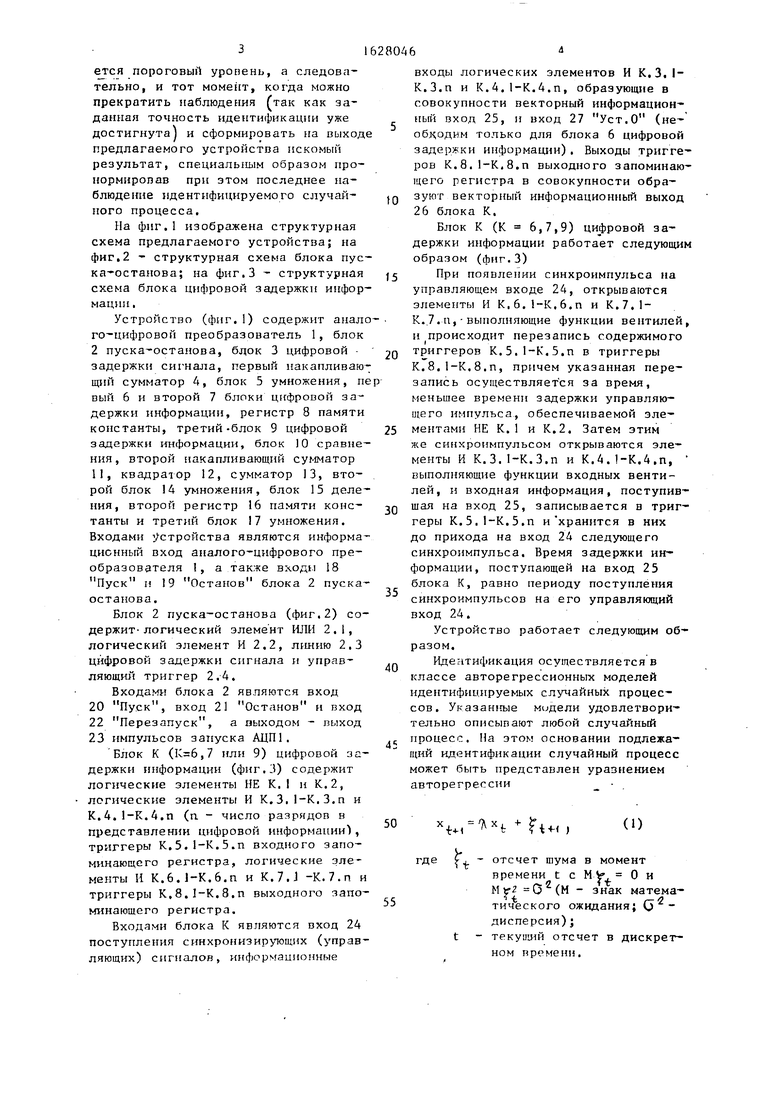

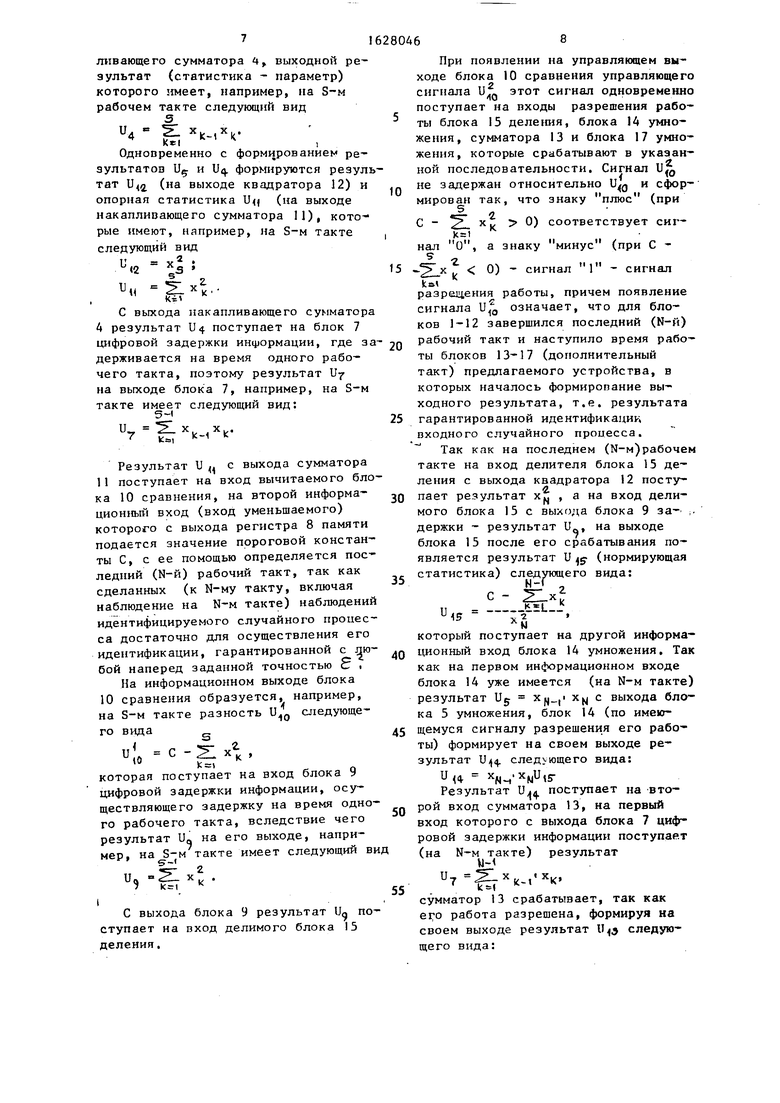

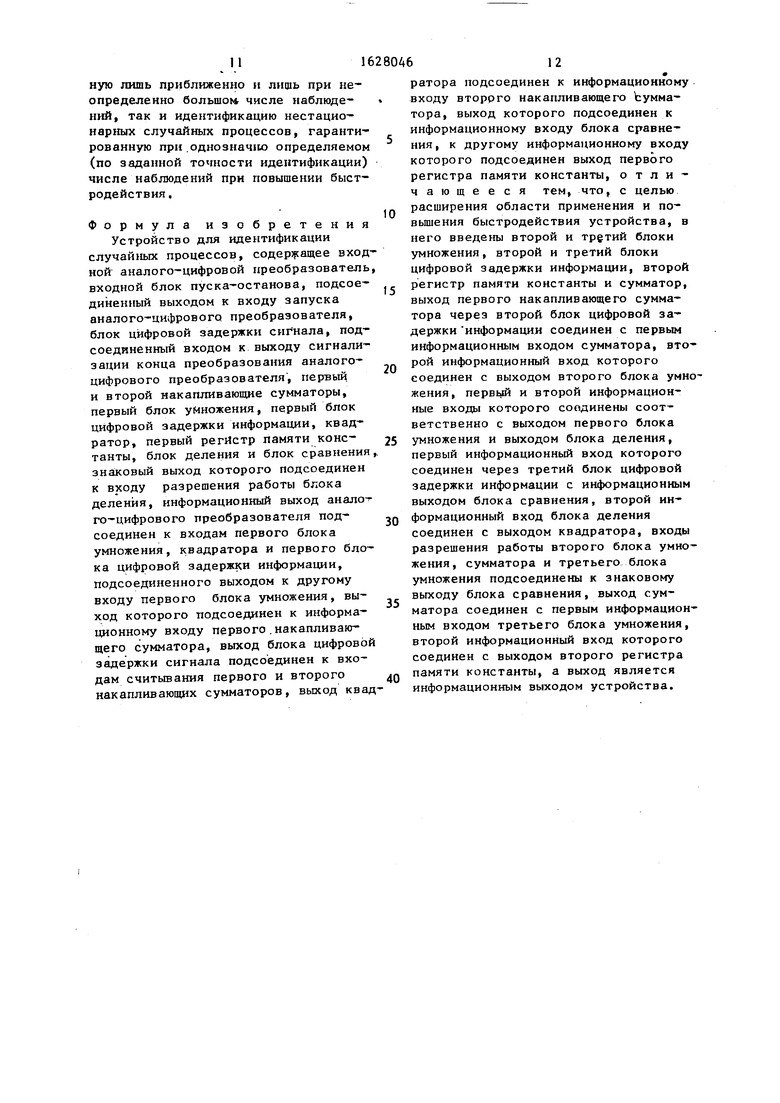

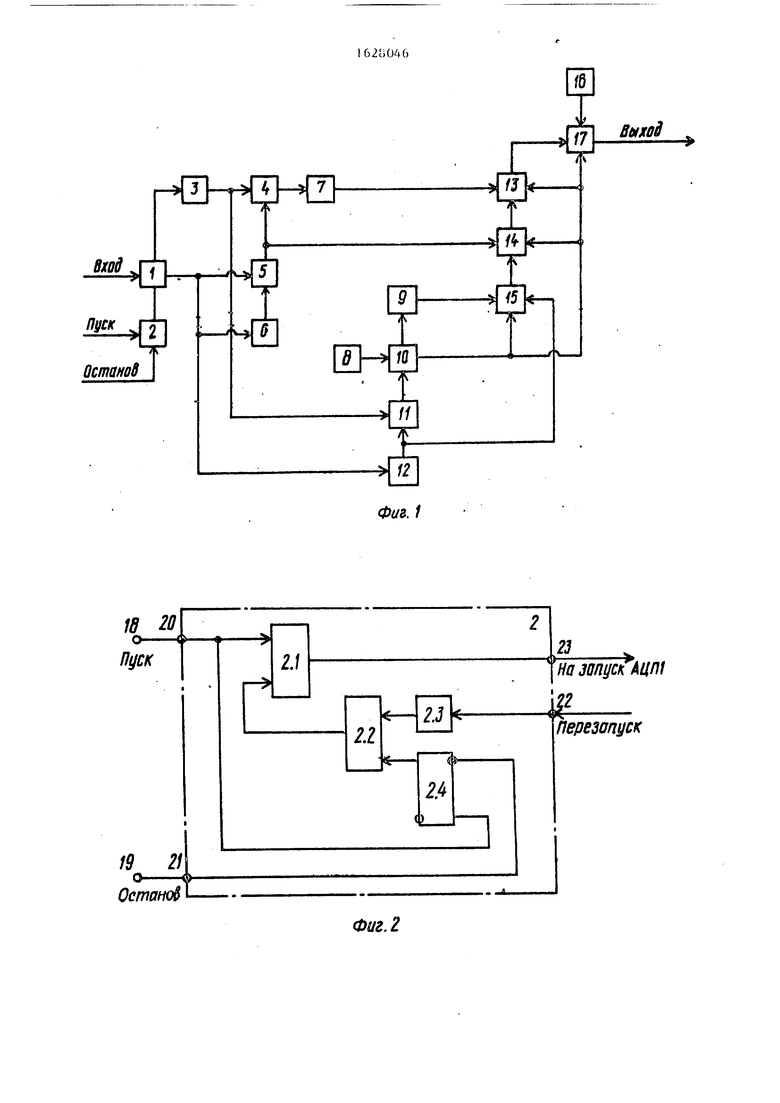

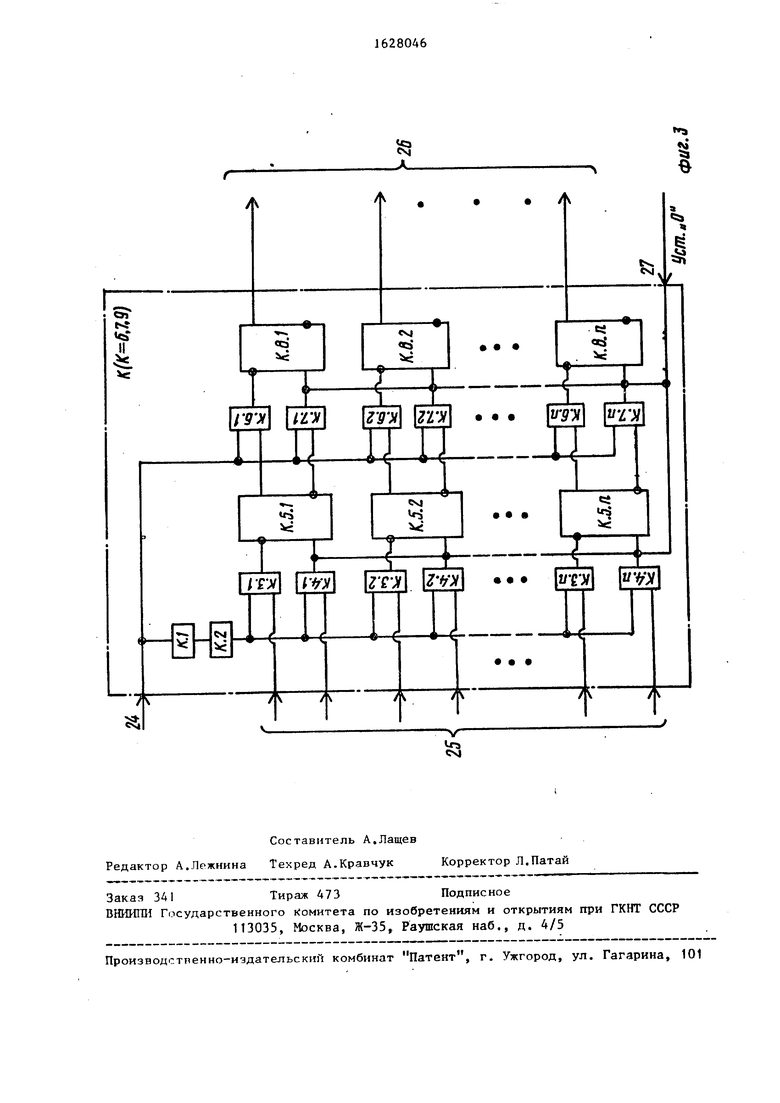

На фиг.1 изображена структурная схема предлагаемого устройства; на фиг,2 - структурная схема блока пуска-останова; на фиг.З - структурная схема блока цифровой задержки информации.

Устройство (фиг.1) содержит аналого-цифровой преобразователь 1, блок 2 пуска-останова, бдок 3 цифровой - задержки сигнала, первый накапливающий сумматор 4, блок 5 умножения, пе вый 6 и второй 7 блоки цифровой задержки информации, регистр 8 памяти константы, третий-блок 9 цифровой задержки информации, блок 10 сравнения, второй накапливающий сумматор 11, квадратор 12, сумматор 13, второй блок 14 умножения, блок 15 деления, второй регистр 16 памяти константы и третий блок 17 умножения. Входами устройства являются информационный вход аналого-цифрового преобразователя 1, а также входи 18 Пуск и 19 Останов блока 2 пуска- останова.

Блок 2 пуска-останова (фиг.2) содержит- логический элемент ИЛИ 2.1, логический элемент И 2.2, линию 2.3 цифровой задержки сигнала и управляющий триггер 2,4.

Входами блока 2 являются вход 20 Пуск, вход 21 Останов и гзход

22 Перезапуск, а выходом - выход

23импульсов запуска АЦП1.

Блок К (,7 или 9) цифровой задержки информации (фиг.З) содержит логические элементы НЕ К.I и К.2, логические элементы И К.3.1-К.З.П и К.4.1-К.4.П (а - число разрядов в представлении цифровой информации), триггеры К.5.1-К.5.П входного запоминающего регистра, логические элементы II К.6.1-К.6.П и K.7.J -К.7.п и триггеры К.8.1-К.8.П выходного запоминающего регистра.

Входами блока К являются вход 24 поступления синхронизирующих (управляющих) сигналов, информационные

5

0

5

0

5

0

5

входы логических элементов И К.З.I- К.З.п и К.4.1-К.4.П, образующие в совокупности векторный информационный вход 25, и вход 27 Уст.О (необходим только для блока 6 цифровой задержки информации). Выходы триггеров К.8.1-К.8,п выходного запоминающего регистра в совокупности образуют векторный информационный выход 26 блока К.

Блок К (К 6,7,9) цифровой задержки информации работает следующим образом (фнг.З)

При появлении синхроимпульса на управляющем входе 24, открываются элементы И К.6.1-К.6.П и К.7.1- К.7.п,выполняющие функции вентилей, и происходит перезапись содержимого триггеров К.5.1-К.5.П в триггеры К.8.1-К.8.П, причем указанная перезапись осуществляется за время, меньшее времени задержки управляющего импульса, обеспечиваемой элементами НЕ К.1 и К.2. Затем этим же синхроимпульсом открываются элементы И К.З.ЬК.З.п и К.4.1-К.4.П, выполняющие функции входных вентилей, и входная информация, поступившая на вход 25, записывается в триггеры К.5.1-К.5.П и хранится в них до прихода на вход 24 следующего синхроимпульса. Время задержки информации, поступающей на вход 25 блока К, равно периоду поступления синхроимпульсов на его управляющий вход 24.

Устройство работает следующим образом.

Идентификация осуществляется в классе авторегрессионных моделей идентифицируемых случайных процессов. Указанные мидели удовлетворительно описывают любой случайный процесс. На этом основании подлежащий идентификации случайный процесс может быть представлен уравнением авторегрессии

0

5

где

Г,

t+ )

(О

t отсчет шума в момент времени t с М у 0 и Мк-2 0 (М - знак математического ожидания; (J - дисперсия);

текущий отсчет в дискретном времени.

16

Требуется идентифицировать случайный процесс, что эквивалентно нахождению оценки истинного значения параметра из (1), если задано, что допустимое среднеквадрати-. ческое отклонение найденной оценки $ от не должно превышать б2, т.е. для осуществления идентификации случайного процесса, гарантированной в смысле выполнения условия

)2 б е (2)

предлагаемое устройство формирует (после завершения последнего, N-ro, шага наблюдения) нормированную ста- тистику - параметр д...

Перед пуском устройства в регистры 8 и 16 памяти константы вводятся соответственно константы Си 1/С, определяемые на основе заданной точное 52 из соотношения

c-G /eV.

если дисперсия U известна, и из соотношения

С %Р/е

если О неизвестна, но известно, что она не превышает известной константы р (т.е.).

Сигнал Пуск, пройдя через блок 2 пуска-останова, приводит в исходное состояние блоки предлагаемого устройства (на фиг.1 не показаны связи, обеспечивающие сброс в О соответствующих блоков устройства) и запускает АЦП1, преобразующий поступающую на его информационный вход непрерывную реализацию x(t) идентифицируемого случайного процесса в представленные в цифровом коде дискретные отсчеты

V

которые с информационного выхода АЦП1 одновременно поступают на входы блока 5 умножения, блока 6 цифровой задержки информации и квадратора 12. Импульсы с выхода сигнализации конца преобразования АЦП 1 поступают на блок 3 цифровой задержки сигнала, где задерживаются на время выполнения операций перемножения в блоке 5 умножения и суммирования в сумматоре 4, после чего одновременно подаются на управляющие входа накапливающих сумматоров 4 и 11 для одновременного считывания (на каждом рабочем такте) накопленной в них информации.

Поступающая с информационного выхода АЦП1 информация об отсчетах xs, S 1,2,... (указанная информация в виде готового результата преобразо1628046

Q

5

0

вания считывается с информационного выхода АЦП) , импульсами с выхода сиг нализации конца преобразования, подаваемыми на вход считывания этого же АЦП), на фиг.) эта связь не показана, после задержки на один рабочий такт предлагаемого устройства в блоке 6 цифровой задержки информации приоб ретает на другом входе блока 5 умножения вид х, , S 1,2 (XQ -О,

так как после включения предлагаемого устройства на выходе АЦТП появляется х., т.е. результат первого преобразования, потом х и т.д.), вследствие этого результат U. на выходе блока 5 умножения имеет, например, на S-M рабочем такте вид

U Х5-Г XS S 1 2, ...

Работа блоков 1-12 предлагаемого устройства (фнг.1) периодически повторяется, причем период повторения - рабочий такт устройства - складывается из времени выполнения операции

5 преобразования в АЦН1, времени выполнения операции перемножения в блоке 5 умножения (или в квадраторе 12), времени выполнения операции сложения в сумматоре 4 (или в сумматоре

0 ||) и времени выполнения операции сравнения в блоке 10 сравнения ( входящие в состав рабочего такта время считывания информации из блоков 1-12 и время задержки, осуществляемой ли5 нией 2.3 и составе блока 2 пуска- останова, исключены из рассмотрения из-ча их малости по сравнению с временем выполнения операций в блоках, при необходимости учет указанных вре-

0 мен легко осуществим). Блоки 13-17 предлагаемого устройства включаются в работу лишь после появления на управляющем выходе блока 10 сравнения сигнала разрешения работы указанных

5 блоков. Появление этого сигнала означает завершение последнего, N-ro, рабочего такта (блоки 1-12 прекращают работу) и начало дополнительного такта (блоки 13-17 включаются на

0 время, необходимое для формирования на выходе устройства результата гарантированной идентификации случайного процесса, поступившего на его вход).

С выхода блока 5 умножения результат Us одновременно поступает на информационный вход блока 14 умножения и на информационный вход накапливающего сумматора 4 выходной результат (статистика - параметр) которого имеет, например, на S-м рабочем такте следующий вид

U,

ХК-1ХЮ

kel,

Однопременно с формированием результатов U и Uq. формируются резултат (на выходе квадратора 12) и опорная статистика (на выходе накапливающего сумматора 11), которые имеют, например, на S-м такте следующий вид

«2 «

Kit

С выхода накапливающего сумматора 4 результат 1)4 поступает на блок 7 цифровой задержки информации, где за- держивается на время одного рабочего такта, поэтому результат U на выходе блока 7, например, на S-м

такте имеет следующий вид: 5-1

ХК-1ХГ

Результат U и с выхода сумматора 11 поступает на вход вычитаемого блока 10 сравнения, на второй информационный вход (вход уменьшаемого) которого с выхода регистра 8 памяти подается значение пороговой константы С, с ее помощью определяется последний (N-й) рабочий такт, так как сделанных (к N-му такту, включая наблюдение на N-м такте) наблюдений идентифицируемого случайного процесса достаточно для осуществления его идентификации, гарантированной с JJKJ- бой наперед заданной точностью С ,

На информационном выходе блока 10 сравнения образуется, например, на S-м такте разность следующего вида g

, п г хг

и,

с Ю к которая поступает на вход блока 9 цифровой задержки информации, осуществляющего задержку на время одного рабочего такта, вследствие чего результат и на его выходе, например, на S-м такте имеет следующий ви

0

0

5

5

0

5

При появлении на управляющем выходе блока 10 сравнения управляющего сигнала этот сигнал одновременно поступает на входы разрешения работы блока 15 деления, блока 14 умножения, сумматора 13 и блока 17 умножения, которые срабатывают в указанной последовательности. Сигнал U, не задержан относительно и сформирован так, что знаку плюс (при

5 г

С нал

s

О,

г

0) соответствует сига знаку

минус

(при С 5 0) - сигнал 1 - сигнал

ka разрешения работы, причем появление

сигнала U, означает, что для блоков 1-12 завершился последний (N-й) рабочий такт и наступило время работы блоков 13-17 (дополнительный такт) предлагаемого устройства, в которых началось формирование выходного результата, т.е. результата гарантированной идентификации входного случайного процесса. Так как на последнем (М-м)рабочем такте на вход делителя блока 15 деления с выхода квадратора 12 посту- 1

0 пает результат х

N

а на вход делимого блока 15 с выхода блока 9 за- , держки - результат Uq, на выходе блока 15 после его срабатывания появляется результат U (нормирующая статистика) следующего вида:

х2

-Л |у

Р -

и

15

..

М

который поступает на другой информационный вход блока 14 умножения. Так как на первом информационном входе блока 14 уже имеется (на N-м такте) результат U х,| хм с выхода блока 5 умножения, блок 14 (по имеющемуся сигналу разрешения его работы) формирует на своем выходе результат U следующего вида:

U

xNM xNU,sРезультат U поступает на второй вход сумматора 13, на первый вход которого с выхода блока 7 цифровой задержки информации поступает (на N-м такте) результат

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения моментов изменения свойств случайного процесса | 1985 |

|

SU1282159A1 |

| Устройство для определения момента изменения свойств случайного процесса | 1983 |

|

SU1166149A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| Устройство для адаптивной обработки информации | 1981 |

|

SU976450A1 |

| Цифровой панорамный измеритель частоты | 1980 |

|

SU928243A1 |

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

| Устройство для определения весовых функций | 1982 |

|

SU1140131A1 |

| Устройство для определения изменения свойств случайных процессов | 1983 |

|

SU1205154A1 |

| Устройство для распознавания случайных последовательностей | 1988 |

|

SU1764067A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

Изобретение позволяет осуществлять гарантированную в смысле обеспечения любой наперед заданной точности идентификацию как стационарных, так и нестационарных случайных процессов, представляемых авторегрес- сионной моделью. Устройство содержит входной аналого-цифровой преобразователь, входной блок пуска-останова, блок задержки сигнала, два накапливаю: их сумматора, три блока задержки информации, квадратор, блок Изобретение относится к технической кибернетике и может быть использовано в практических задачах идентификации, фильтрации, прогнозирования, управления и и любых других приложениях, где требуется в условиях априори неизвестных данных получить эквивалентную в смысле требуемой точности описания модель как стационарных, так и нестационарных случайных процессов. Цель изобретения - расширение области применения и повышение быстродействия устройства. сравнении, два pvirncipa памяти константы, блок деления, сумматор и трь блока умножения, причем выход третьего блока умножения является выходом тройства. Указанная совокупность блока реалнч ет таь,}ю модификацию классического метода наименьших шадратов, количество i аблю- дении идентифицируемою случайною пронегса не фиксируется заранее, а оьределяьп я в оде последовательно о наблюдения VHOMHHVTOIO процесса моментом останова наблюдении. Зтот момент наступает , когда накапливаемая вели шна сташстики, названной опорной, ирсипснт пороговый уровень, однозначно определяемый заданным значением точности идентификации. После останова наблюдений на выходе устройства появляется результат и. ентификации случайного процесса в виде оценки параметра авторегрессионной модели. 3 ил. Устройство реализует последовательную процедуру обработки наблюдений идентифицируемого случайного процесса, являющуюся такой модификацией метода наименьших квадратов, когда длительность интервала наблюдения не фиксируется заранее, а опре- деляется превышением порогового уровня накапливаемым значением специальной опорной статистики, учитывающей структуру идентифицируемого случайного процесса. По заданному значению точности идентификации не приблизительно, а однозначио определи(Л о N5 00 О 4 О

Uc

I

U0

С выхода блока 9 результат UQ ступает на вход делимого блока 15 деления.

55

U7 Txfc-t xK

сумматор 13 срабатывает, так как erto работа разрешена, формируя на своем выходе результат 11 следующего вида:

U

«3

N-«

к «

х к-, х ic +

Результат поступает на первый вход блока 17 умножения, на второй вход которого с выхода регистра 16 памяти подается значение константы 1/С, а так как работа блока 17 разрешена, он срабатывает, формируя на своем выходе результат (нормированная статистика - параметр) вида:

следующего А

- N

Ч-i х +

VNM

к-н

i/c(2L

S«i

Результат U,7 /Лн являясь оценкой параметра /Д авторегрессионной модели (1) идентифицируемого случайного процесса, поступившего на вход предлагаемого устройства, представляет собой результат его идентификации (по N наблюдениям), гарантированной в смысле обязательного выполнения условия (2).

Синхронизация работы устройства в целом осуществляется следующим образом (фиг.1).

Сигналом Пуск осуществляется сброс в О накапливающих сумматоров 4 и 11, входного и выходного запоминающих регистров в блоке 6 (фиг.З) и триггера знака в блоке 10 (на фиг.1 указанные связи не показаны), приводится в единичное состояние триггер 2.4 (в блоке 2) и запускается (на первое преобразование).ЛЦП1. Работа АЦП1 и блоков 5, 4 и 7, а также АЦП1 и блоков 12, И, 10 и 9 осуществляется последовательно во времени, причем в качестве сигнала синхронизации для всех перечисленных блоков (кроме АЦП1) используется сигнал окончания операции предыдущего блока (на фиг.1 указанные цепи синхрнизации не показаны). Сигналом синхронизации для АЦП1 (на второе, третье и т.д. преобразования) является сигнал окончания операции сравнения в блоке 10, который поступает с отдельного выхода блока 10 на вход 22 Перезапуск (фиг.2) блока 2 (на фиг.1 указанная связь не показана).

Как и для блоков 5 и 12, синхронизирующим сигналом для блока 6, поступающим на его управляющий вход 24 (фиг.З) являются импульсы с выхода сигнализации конца преобразования АЦП Г (на фиг.1 указанная связь ие показана). Считывание готовой ин10

15

формации из сумматоров 4 и 11 осуществляется одновременно путем одновременной подачи на их входы считывания (после задержки в блоке 3 на время i) обработки выходной информации АЦП1 в блоке 5 умножения и сумматоре 4, которое равно времени 6 обработки той же информации с выхода АЦП1 в квадраторе 12 и сумматоре И), импульсов сигнализации конца преобразования с отдельного выхода АЦП1. Работа блоков 1-12 повторяется с периодом, равным длительности рабочего такта, вплоть до последнего (N-ro) рабочего такта, когда в блоке

0

5

10 выполняется условие С после чего триггер знака в

блока 10 устанавливается в

сигнал 1 одновременно подается на

вход 21 Останов блока 2 (на фиг.1

К 2 21 0,

У- составе

состояние

указанная связь не показана) и па входы разрешения работы блоков 15, 14, 13 и 17. Сигнал на входе Останов блока 2 (фиг.2) прекращает работу блоков 1-12, для чего устанав0 ливает управляющий 2.4 в состояние О, запирая тем самым элемент И 2.2 для прохождения поступающего па вход 22 Перезапуск блока 2 сигнала окончания операции срав5 нения (сигнала перезапуска АЦП1) с отдельного выхода блока 10, более позднее появление сигнала перезапуска на входе 22 блока 2 (относительно момента появления сигнала I на

0 входе 21 блока 2) осуществляется его небольшой задержкой, обеспечиваемой линией 2.3 блока 2.

Сигнал 1 со знакового выхода блока 10 разрешает работу (точнее,

5 дает общее разрешение на работу) блоков 15, 14, 13 и 17 во время дополнительного такта (или сверхтакта), которые срабатывают друг за другом в указанной последовательности,

0 причем в качестве сигналя синхронизации (сигнала начала операции) для каждого из этих блоков используется сигнал окончания операции предыдущего блока (на фиг,1 указан5 ные цепи синхронизации не показаны). Предлагаемое устройство обеспечивает как идентификацию стационарных случайных процессов, гарантированную лишь приближенно и лишь при неопределенно большом, числе наблюдений, так и идентификацию нестационарных случайных процессов, гарантированную при однозначно определяемом (по заданной точности идентификации) числе наблюдений при повышении быстродействия.

Формула изобретения

Устройство для идентификации случайных процессов, содержащее входной аналого-цифровой преобразователь входной блок пуска-останова, подсоединенный выходом к входу запуска аналого-цифрового преобразователя, блок цифровой задержки сигнала, подсоединенный входом к выходу сигнализации конца преобразования аналого- цифрового преобразователя, первый и второй накапливающие сумматоры, первый блок умножения, первый блок цифровой задержки информации, квадратор, первый регистр памяти константы, блок деления и блок сравнения знаковый выход которого подсоединен к входу разрешения работы блока деления, информационный выход аналого-цифрового преобразователя подсоединен к входам первого блока умножения, квадратора и первого блока цифровой задержки информации, подсоединенного выходом к другому входу первого блока умножения, выход которого подсоединен к информационному входу первого накапливающего сумматора, выход блока цифровой задержки сигнала подсоединен к входам считывания первого и второго накапливающих сумматоров, выход квад0

5

5

0

5

0

ратора подсоединен к информационному входу второго накапливающего Ъумма- тора, выход которого подсоединен к информационному входу блока сравнения , к другому информационному входу которого подсоединен выход первого регистра памяти константы, отличающееся тем, что, с целью расширения области применения и повышения быстродействия устройства, в него введены второй и третий блоки умножения, второй и третий блоки цифровой задержки информации, второй регистр памяти константы и сумматор, выход первого накапливающего сумматора через второй блок цифровой задержки информации соединен с первым информационным входом сумматора, второй информационный вход которого соединен с выходом второго блока умножения, первый и второй информационные входы которого соединены соответственно с выходом первого блока умножения и выходом блока деления, первый информационный вход которого соединен через третий блок цифровой задержки информации с информационным выходом блока сравнения, второй информационный вход блока деления соединен с выходом квадратора, входы разрешения работы второго блока умножения, сумматора и третьего блока умножения подсоединены к знаковому выходу блока сравнения, выход сумматора соединен с первым информационным входом третьего блока умножения, второй информационный вход которого соединен с выходом второго регистра памяти константы, а выход является информационным выходом устройства.

Фаг. 1

Фиг. 2

л

«o V:

I

§ Ji

t

I

/tv

Ca

ч

«5

fltf

Vf

Авторы

Даты

1991-02-15—Публикация

1989-01-09—Подача