Изобретение относится к области радиотехники и может быть использовано в качестве малошумящего устройства усиления аналоговых сигналов, в структуре аналоговых интерфейсов различного функционального назначения, в том числе работающих в широком диапазоне температур и воздействия радиации.

Известны схемы классических операционных усилителей (ОУ), содержащих в промежуточном каскаде однотактный «перегнутый» каскод, который реализуется на полевых с p и n каналами транзисторах [1-28] или биполярных [29-39] транзисторах. Это одна из наиболее популярных схем в аналоговой микроэлектронике. При этом входные каскады ОУ [1-39]. выполняются в рамках десятков различных схемотехнических решений.

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, представленный в патенте EP № 0632581, fig. 1 - fig. 3, 1995 г. Он содержит входной дифференциальный каскад 1 на полевых транзисторах с первым 2 и вторым 3 входами устройства, с первым 4 и вторым 5 токовыми выходами устройства, а также общей истоковой цепью 6, согласованной с первой 7 шиной источника питания, первый 8 выходной полевой транзистор, исток которого соединен со вторым 5 токовым выходом входного дифференциального каскада 1, второй 9 выходной полевой транзистор, исток которого связан с первым 4 токовым выходом входного дифференциального каскада 1, первый 10 токостабилизирующий двухполюсник на полевом транзисторе, который включен между первым 4 токовым выходом входного дифференциального каскада 1 и второй 11 шиной источника питания, второй 12 токостабилизирующий двухполюсник на полевом транзисторе, включенный между вторым 5 токовым выходом входного дифференциального каскада 1 и второй 11 шиной источника питания, цепь динамической нагрузки 13, включенная между стоком первого 8 выходного полевого транзистора, связанного с токовым выходом устройства 14 и первой 7 шиной источника питания.

Существенный недостаток известного ОУ фиг. 1, обусловленный свойствами его архитектуры, состоит в том, что в нем не обеспечиваются малые значения систематической составляющей напряжения смещения нуля (Uсм).

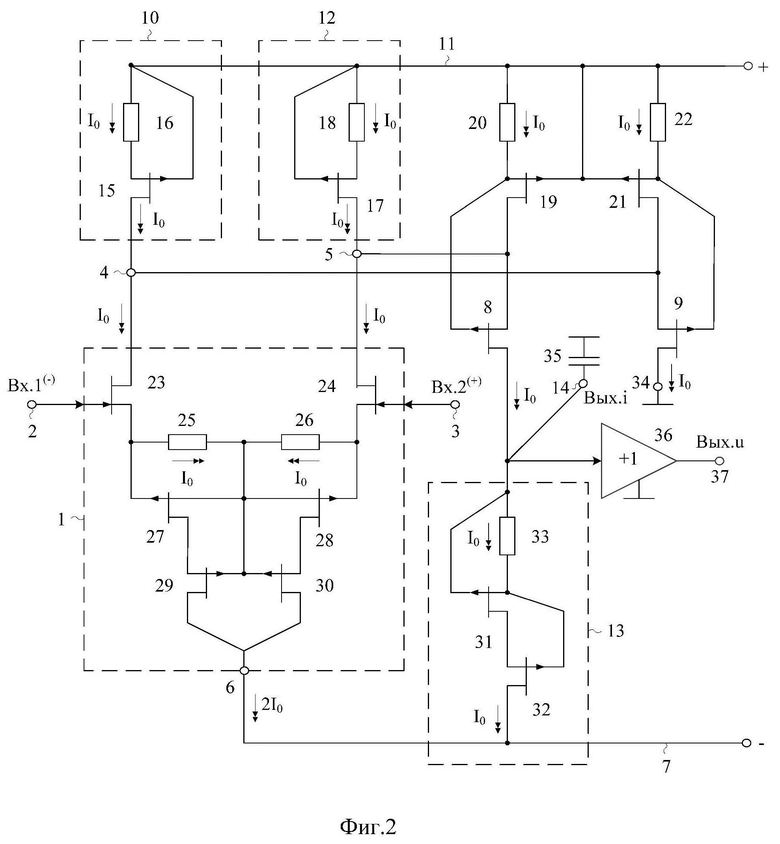

Основная задача предполагаемого изобретения состоит в создании условий, при которых в ОУ реализуются малые значения систематической составляющей напряжения смещения нуля. При этом положительный эффект в схеме фиг. 2 обеспечивается за счет специального построения входного дифференциального каскада ОУ и «перегнутого» каскода.

Поставленная задача решается тем, что в ОУ фиг. 1, содержащем входной дифференциальный каскад 1 на полевых транзисторах с первым 2 и вторым 3 входами устройства, с первым 4 и вторым 5 токовыми выходами устройства, а также общей истоковой цепью 6, согласованной с первой 7 шиной источника питания, первый 8 выходной полевой транзистор, исток которого соединен со вторым 5 токовым выходом входного дифференциального каскада 1, второй 9 выходной полевой транзистор, исток которого связан с первым 4 токовым выходом входного дифференциального каскада 1, первый 10 токостабилизирующий двухполюсник на полевом транзисторе, который включен между первым 4 токовым выходом входного дифференциального каскада 1 и второй 11 шиной источника питания, второй 12 токостабилизирующий двухполюсник на полевом транзисторе, включенный между вторым 5 токовым выходом входного дифференциального каскада 1 и второй 11 шиной источника питания, цепь динамической нагрузки 13, включенная между стоком первого 8 выходного полевого транзистора, связанного с токовым выходом устройства 14 и первой 7 шиной источника питания, предусмотрены новые элементы и связи – первый 10 токостабилизирующий двухполюсник выполнен на полевом транзисторе 15, затвор которого соединен со второй 11 шиной источника питания, а исток подключен ко второй 11 шине источника питания через первый 16 дополнительный резистор, второй 12 токостабилизирующий двухполюсник выполнен на полевом транзисторе 17, затвор которого соединен со второй 11 шиной источника питания, а исток подключен ко второй 11 шине источника питания через второй 18 дополнительный резистор, исток первого 8 выходного транзистора соединен со стоком первого 19 вспомогательного полевого транзистора, затвор которого подключен ко второй 11 шине источника питания, а исток соединен с затвором первого 8 выходного полевого транзистора и связан со второй 11 шиной источника питания через третий 20 дополнительный резистор, исток второго 9 выходного транзистора соединен со стоком второго 21 вспомогательного полевого транзистора, затвор которого подключен ко второй 11 шине источника питания, а исток соединен с затвором второго 9 выходного полевого транзистора и связан со второй 11 шиной источника питания через четвертый 22 дополнительный резистор, причем входной дифференциальный каскад 1 содержит первый 23 и второй 24 входные полевые транзисторы, между истоками которых включены последовательно соединенные пятый 25 и шестой 26 дополнительные резисторы, а также первый 27, второй 28, третий 29 и четвертый 30 выходные полевые транзисторы, затвор первого 23 входного полевого транзистора подключён к первому 2 входу устройства, его сток соединен с первым 4 токовым выходом входного дифференциального каскада 1, а исток соединен с затвором первого 27 выходного полевого транзистора, затвор второго 24 входного полевого транзистора соединен со вторым 3 входом устройства, его сток соединен со вторым 5 токовым выходом входного дифференциального каскада 1, а исток соединен с затвором второго 28 выходного полевого транзистора, истоки первого 27 и второго 28 выходных полевых транзисторов объединены, а также соединены с затворами третьего 29, четвертого 30 выходных полевых транзисторов и общим узлом последовательно соединенных пятого 25 и шестого 26 дополнительных резисторов, сток первого 27 выходного полевого транзистора подключен к истоку третьего 29 выходного полевого транзистора, сток второго 28 выходного полевого транзистора подключен к истоку четвертого 30 выходного полевого транзистора, стоки третьего 29 и четвертого 30 выходных полевых транзисторов связаны с общей истоковой цепью 6, цепь динамической нагрузки 13 содержит первый 31 и второй 32 транзисторы, затвор первого 31 транзистора соединен с токовым выходом устройства 14, а его исток связан с затвором второго 32 транзистора и подключен к токовому выходу устройства 14 через резистор 33, сток первого 31 транзистора связан с истоком второго 32 транзистора , а сток второго 32 транзистора подключен к первой 7 шине источника питания, а сток второго 9 выходного полевого транзистора связан с источником напряжения смещения 34.

На чертеже фиг. 1 приведена схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п.1, п.2 и п.3 формулы изобретения.

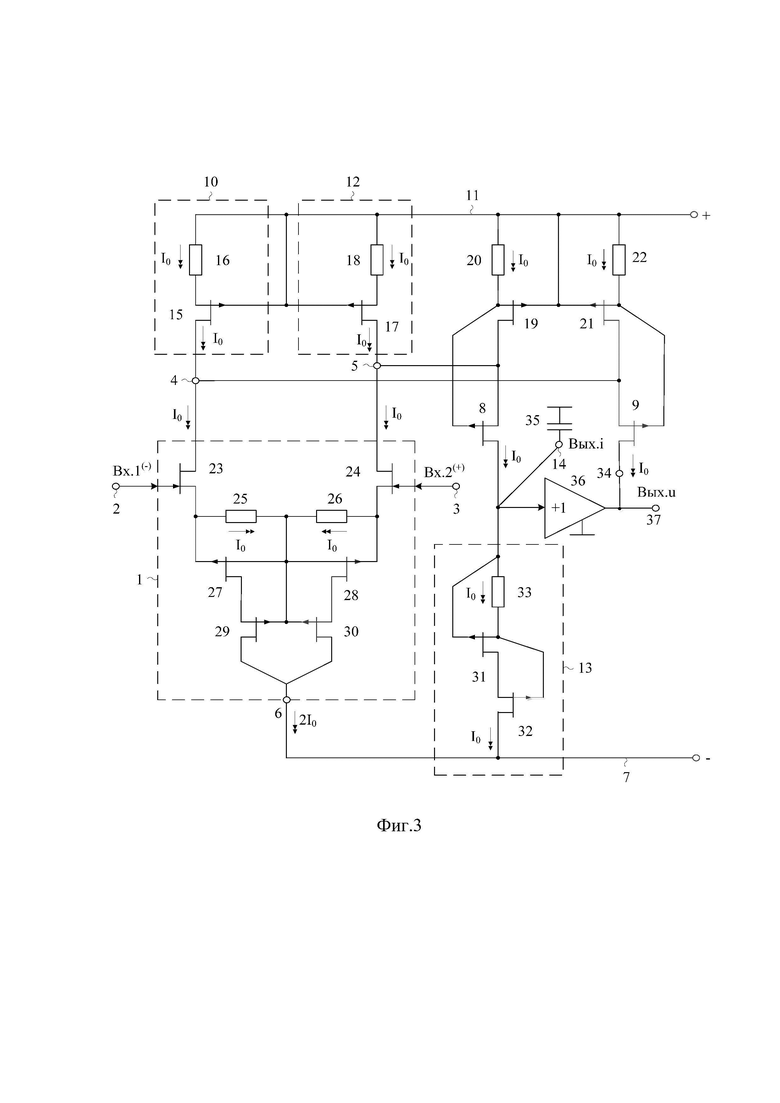

На чертеже фиг. 3 приведена схема заявляемого ОУ в соответствии с п. 4 формулы изобретения.

На чертеже фиг. 4 показана схема операционного усилителя фиг. 2 в среде LTspice на моделях Si CJFET ОАО «Интеграл» (г. Минск) при комнатной температуре (t = 27°C), R1÷R7=20кОм, C1 = 3 пФ, Vcc=Vee=±10 В.

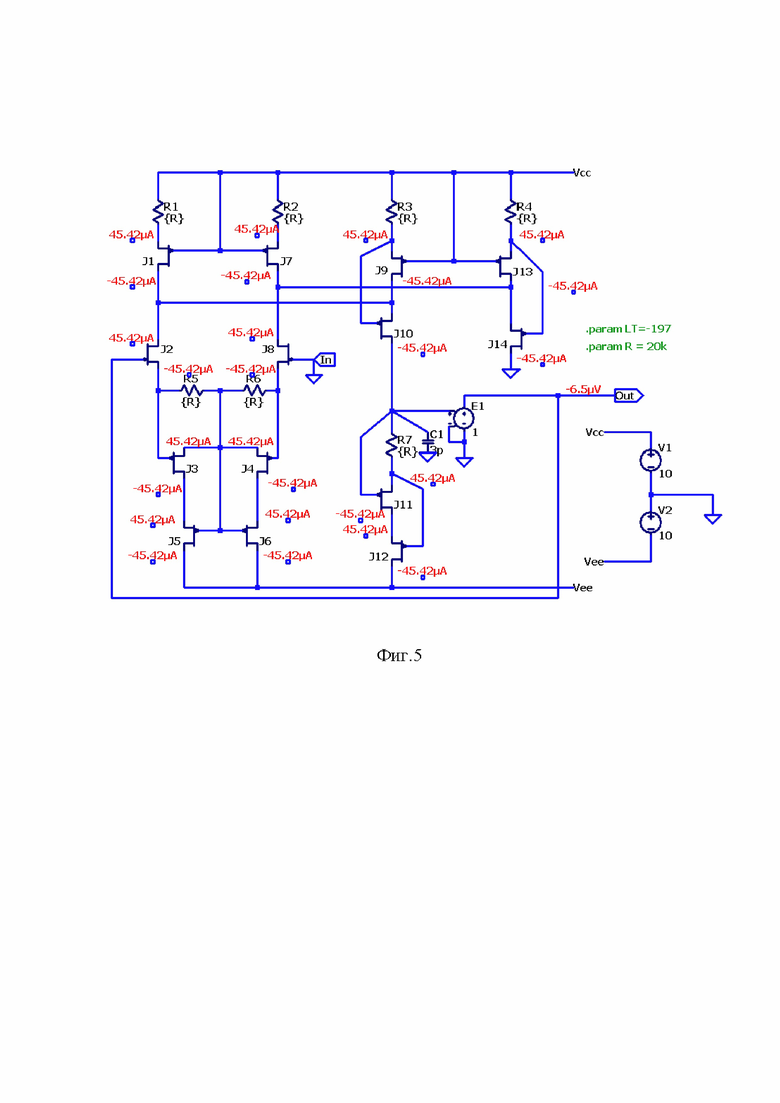

На чертеже фиг. 5 показана схема операционного усилителя фиг. 2 в среде LTspice на моделях Si CJFET ОАО «Интеграл» (г. Минск) при криогенной температуре (t = -197°C), R1÷R7=20кОм, C1 = 3 пФ, Vcc=Vee=±10 В.

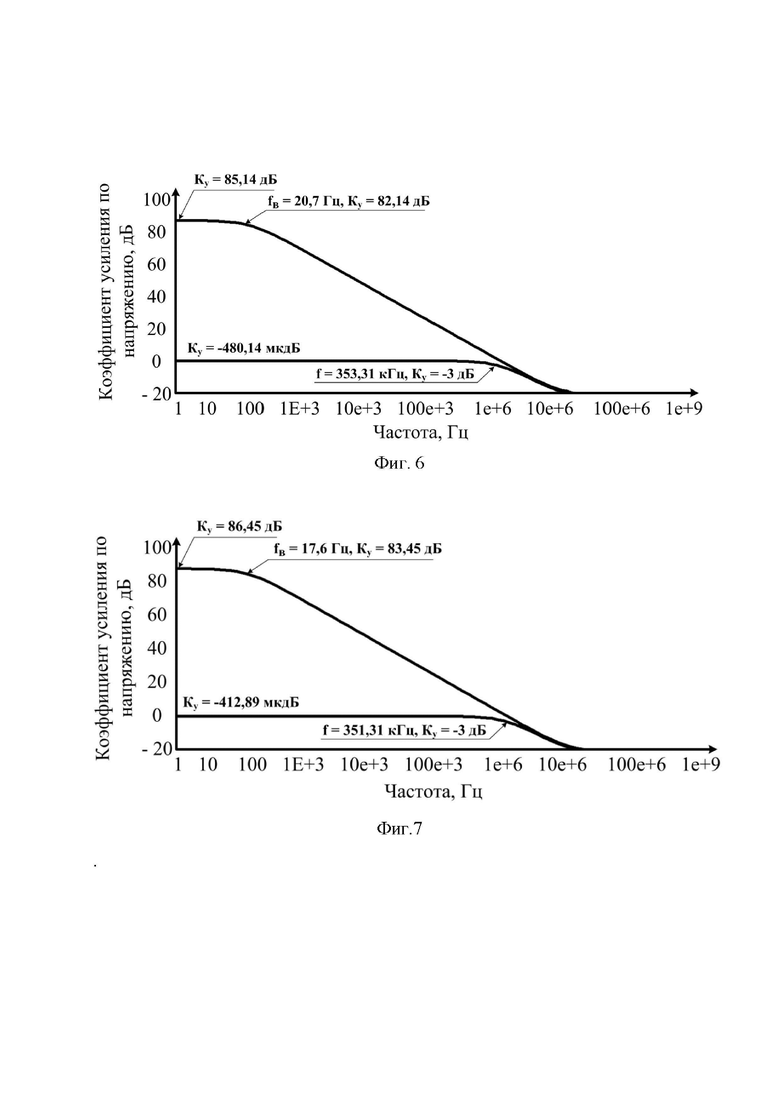

На чертеже фиг. 6 приведена амплитудно-частотная характеристика (АЧХ) ОУ фиг. 5 при комнатной температуре (t = 27°C), R1÷R7 = 20 кОм, C1 = 3 пФ, Vcc=Vee=±10.

На чертеже фиг. 7 представлена АЧХ ОУ фиг. 5 при криогенной температуре (t=-197°C) R1÷R7 = 20 кОм, C1 = 3 пФ, Vcc=Vee=±10.

На чертеже фиг. 8 приведена зависимость систематической соствляющей напряжения смещения нуля (Uсм) ОУ фиг.2 в широком температурном диапазоне при R1÷R7 = 20 кОм, C1 = 3 пФ, Vcc=Vee=±10.

На чертеже фиг. 9 показана схема для моделирования операционного усилителя фиг.3 при комнатной температуре (t = 270C), R1÷R7 = 20 кОм, C1 = 3 пФ, Vcc=Vee=±10 В в среде LTspice на моделях Si полевых транзисторов ОАО «Интеграл» (г. Минск).

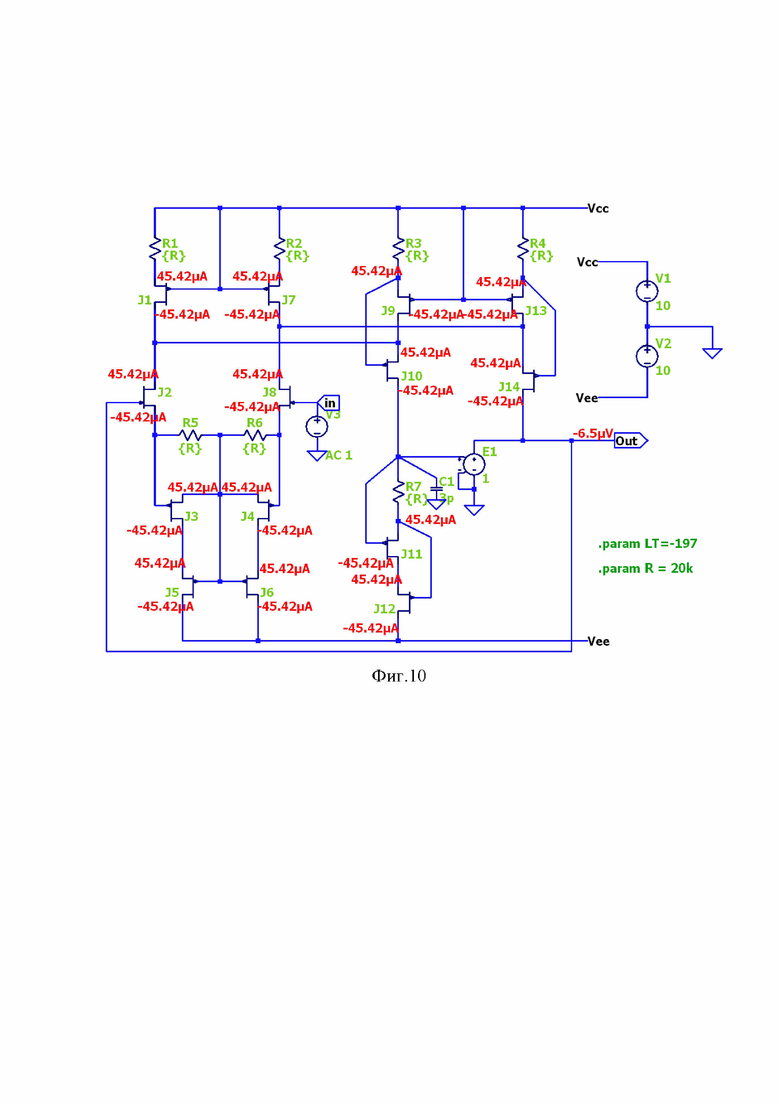

На чертеже фиг. 10 показана схема для моделирования операционного усилителя фиг.3 при криогенной температуре (t = -1970C), R1÷R7 = 20 кОм, C1 = 3 пФ, Vcc=Vee=±10 В в среде LTspice на моделях Si полевых транзисторов ОАО «Интеграл» (г. Минск).

На чертеже фиг.11 приведена амплитудно-частотная характеристика (АЧХ) ОУ фиг.9 при комнатной температуре (t = 270C), R1÷R7 = 20 кОм, C1 = 3 пФ, Vcc=Vee=±10.

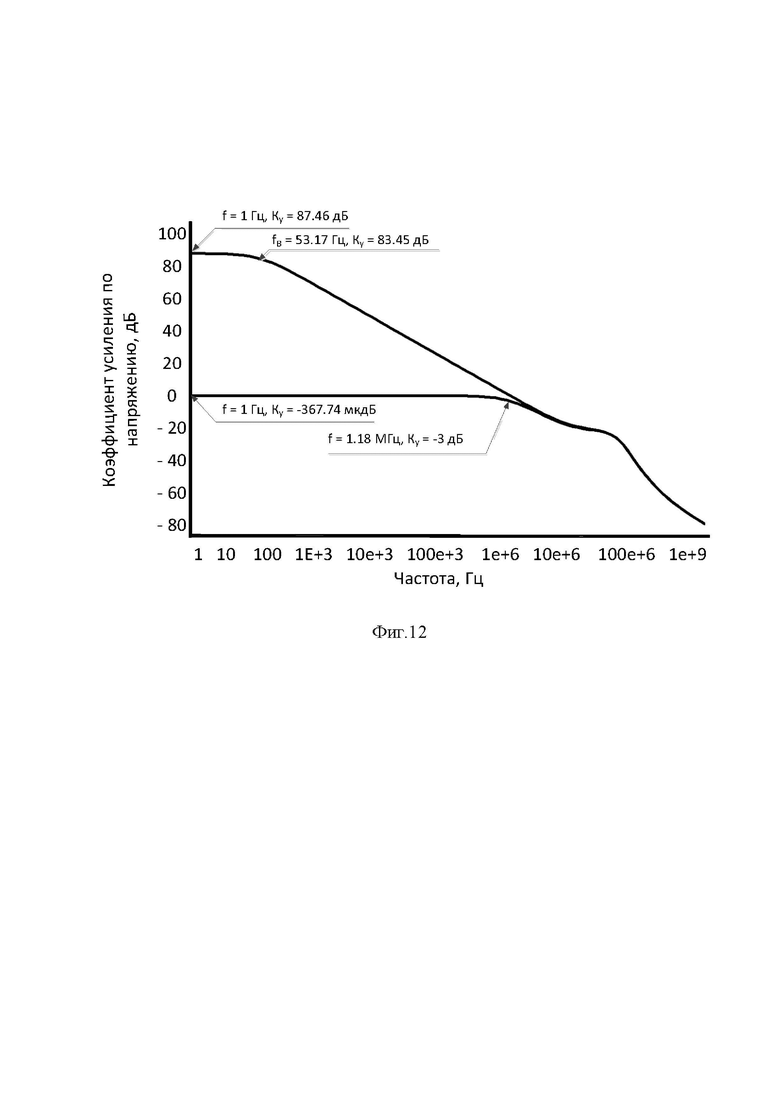

На чертеже фиг. 12 приведена амплитудно-частотная характеристика (АЧХ) ОУ фиг.10 при криогенной температуре (t = -1970C), R1÷R7 = 20 кОм, C1 = 3 пФ, Vcc=Vee=±10.

Операционный усилитель на основе «перегнутого» каскода и комплементарных полевых транзисторов фиг. 2 содержит входной дифференциальный каскад 1 на полевых транзисторах с первым 2 и вторым 3 входами устройства, с первым 4 и вторым 5 токовыми выходами устройства, а также общей истоковой цепью 6, согласованной с первой 7 шиной источника питания, первый 8 выходной полевой транзистор, исток которого соединен со вторым 5 токовым выходом входного дифференциального каскада 1, второй 9 выходной полевой транзистор, исток которого связан с первым 4 токовым выходом входного дифференциального каскада 1, первый 10 токостабилизирующий двухполюсник на полевом транзисторе, который включен между первым 4 токовым выходом входного дифференциального каскада 1 и второй 11 шиной источника питания, второй 12 токостабилизирующий двухполюсник на полевом транзисторе, включенный между вторым 5 токовым выходом входного дифференциального каскада 1 и второй 11 шиной источника питания, цепь динамической нагрузки 13, включенная между стоком первого 8 выходного полевого транзистора, связанного с токовым выходом устройства 14 и первой 7 шиной источника питания. Первый 10 токостабилизирующий двухполюсник выполнен на полевом транзисторе 15, затвор которого соединен со второй 11 шиной источника питания, а исток подключен ко второй 11 шине источника питания через первый 16 дополнительный резистор, второй 12 токостабилизирующий двухполюсник выполнен на полевом транзисторе 17, затвор которого соединен со второй 11 шиной источника питания, а исток подключен ко второй 11 шине источника питания через второй 18 дополнительный резистор, исток первого 8 выходного транзистора соединен со стоком первого 19 вспомогательного полевого транзистора, затвор которого подключен ко второй 11 шине источника питания, а исток соединен с затвором первого 8 выходного полевого транзистора и связан со второй 11 шиной источника питания через третий 20 дополнительный резистор, исток второго 9 выходного транзистора соединен со стоком второго 21 вспомогательного полевого транзистора, затвор которого подключен ко второй 11 шине источника питания, а исток соединен с затвором второго 9 выходного полевого транзистора и связан со второй 11 шиной источника питания через четвертый 22 дополнительный резистор, причем входной дифференциальный каскад 1 содержит первый 23 и второй 24 входные полевые транзисторы, между истоками которых включены последовательно соединенные пятый 25 и шестой 26 дополнительные резисторы, а также первый 27, второй 28, третий 29 и четвертый 30 выходные полевые транзисторы, затвор первого 23 входного полевого транзистора подключён к первому 2 входу устройства, его сток соединен с первым 4 токовым выходом входного дифференциального каскада 1, а исток соединен с затвором первого 27 выходного полевого транзистора, затвор второго 24 входного полевого транзистора соединен со вторым 3 входом устройства, его сток соединен со вторым 5 токовым выходом входного дифференциального каскада 1, а исток соединен с затвором второго 28 выходного полевого транзистора, истоки первого 27 и второго 28 выходных полевых транзисторов объединены, а также соединены с затворами третьего 29, четвертого 30 выходных полевых транзисторов и общим узлом последовательно соединенных пятого 25 и шестого 26 дополнительных резисторов, сток первого 27 выходного полевого транзистора подключен к истоку третьего 29 выходного полевого транзистора, сток второго 28 выходного полевого транзистора подключен к истоку четвертого 30 выходного полевого транзистора, стоки третьего 29 и четвертого 30 выходных полевых транзисторов связаны с общей истоковой цепью 6, цепь динамической нагрузки 13 содержит первый 31 и второй 32 транзисторы, затвор первого 31 транзистора соединен с токовым выходом устройства 14, а его исток связан с затвором второго 32 транзистора и подключен к токовому выходу устройства 14 через резистор 33, сток первого 31 транзистора связан с истоком второго 32 транзистора , а сток второго 32 транзистора подключен к первой 7 шине источника питания, а сток второго 9 выходного полевого транзистора связан с источником напряжения смещения 34.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, токовый выход устройства 14 соединен со входом буферного усилителя 36, выход которого 37 является потенциальным выходом устройства.

На чертеже фиг. 2, в соответствии с п. 3 формулы изобретения, в качестве источника напряжения смещения 34 используется общая шина источников питания. Корректирующий конденсатор 35 обеспечивает устойчивость ОУ при введении общей отрицательной обратной связи.

На чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, в качестве источника напряжения смещения 34 используется потенциальный выход устройства 37.

Рассмотрим работу ОУ фиг. 2.

В статическом режиме, например, при подключении первого 2 и второго 3 входов ОУ фиг. 2 к общей шине источников питания, статические токи истоков всех полевых транзисторов схемы (8, 9, 15, 17, 19, 21, 23, 24, 27, 28, 29, 30, 31, 32) определяются численными значениями идентичных сопротивлений применяемых резисторов 16, 18, 20, 22, 25, 26, 33:

где Iиi – ток истока i-го полевого транзистора;

Uзи.i – напряжение затвор-исток соответствующих полевых транзисторов в рабочей точке при токе истока, равном I0;

Ri – сопротивления соответствующих резисторов (16, 18, 20, 22, 25, 26, 33).

В схеме ОУ фиг. 2 за счет выбора идентичными сопротивлений применяемых резисторов при идентичных стокозатворных характеристиках применяемых JFET обеспечивается идентичный статический режим по току стока всех полевых транзисторов. Это является необходимым условием минимизации систематической составляющей напряжения смещения нуля ОУ, т.к. в цепи токового выхода 14 обеспечивается взаимная компенсация втекающих в данных узел и вытекающих из данного узла статических токов. Данный вывод подтверждается результатами компьютерного моделирования, представленными на чертежах фиг.5, фиг.8, фиг.9, фиг.10 из которых следует, что Uсм заявляемого ОУ изменяется в пределах 6-12 мкВ в широком температурном диапазоне (от -197°С до +27°С). При этом обеспечивается работа входного и промежуточного каскадов в режиме микротоков при разомкнутом коэффициенте усиления ОУ более 85 дБ (фиг.6, фиг.7, фиг.11, фиг.12).

Реализация операционного усилителя в соответствии с фиг.3 позволяет выполнять буферный усилитель 36 на одиночном полевом транзисторе (например, истоковом повторителе), статический режим по току которого устанавливается вторым 9 выходным транзистором.

В предлагаемой схеме ОУ, в частном случае, могут использоваться полевые транзисторы с управляющим p-n переходом или КМОП транзисторы со встроенным каналом, которые имеют похожие вольт-амперные характеристики в сравнении с JFET.

Таким образом, заявляемое устройство имеет существенные преимущества по Ucм в сравнении с ОУ-прототипом, что позволяет рекомендовать его для практического использования в аналоговых интерфейсах различного назначения, в том числе, работающих в криогенном диапазоне температур и при воздействии проникающей радиации.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № 5.376.899, fig. 4, 1994 г.

2. Заявка на патент США № US 2008/0129383, 2008 г., fig. 2

3. Заявка на патент США № US 2005/0258901, 2005 г., fig. 14

4. Патент США № 6.750.715, fig. 4, 2004 г.

5. Патент США № 6.714.076, fig. 3, 2004 г.

6. Патент США № 6.628.168, fig. 2, 2003 г.

7. Патент США № 8.604.878, fig. 1B, 2013 г.

8. Патент EP № 0632581, fig. 1 - fig. 3, 1995 г.

9. Патент США № 7.453.319, fig. 1, 2008 г.

10. Патент US 7.915.848, 2011 г., fig. 9

11. Zurla R. et al. Enhanced Compensation for Voltage Regulators Based on Three-Stage CMOS Operational Amplifiers for Large Capacitive Loads //2020 IEEE International Symposium on Circuits and Systems (ISCAS). – IEEE, 2020. – P. 1-5, fig. 5

12. AL-Qaysi H. K., Jasim M. M., Hameed S. M. Design of very low-voltages and high-performance CMOS gate-driven operational amplifier //Indonesian Journal of Electrical Engineering and Computer Science. – 2020. – Т. 20. – №. 2. – P. 670-679, fig. 1

13. Aminzadeh H., Lotfi R., Mafinezhad K. Design of low-power single-stage operational amplifiers based on an optimized settling model //Analog Integrated Circuits and Signal Processing. – 2009. – Т. 58. – №. 2. – P. 153-160, fig. 3

14. Esfahani Z. K. et al. Monolithically Integrated Light Feedback Control Circuit for Blue/UV LED Smart Package //IEEE Photonics Journal. – 2017. – Т. 9. – №. 2. – P. 1-13., fig. 3

15. Johansson J. Power-Efficient Settling Time Reduction Techniques for a Folded-Cascode Amplifier in 1.8 V, 0.18 um CMOS // Master of Science Thesis in Electrical Engineering, Department of Electrical Engineering, Linköping University, 2017, 92 p., fig. 3.6

16. Патент США № 6.788.143, fig. 1, fig. 4, 2004 г.

17. Патент США № 7.894.727, fig. 2, fig. 3, 2011 г.

18. Патент США № 7.570.113, 2009 г., fig. 1a

19. Патент США № 6.717.474, 2004 г., fig. 4

20. Патент США № 6 5.424.681, 1995 г., fig. 7

21. Патент США № 5.475.339, 1995 г., fig. 5

22. Патент США № 5.808.513, fig. 3, 1998 г.

23. Патент США № 4.284.959, fig. 3, 1981 г.

24. Soni P., Singh B. P., Bhardwaj M. Design of Enhanced Performance Folded Cascoded Operational Transconductance Amplifier //AIP Conference Proceedings. – American Institute of Physics, 2010. – Т. 1324. – №. 1. – P. 360-364., fig. 1, fig. 2

25. Noormohammadi M., Lazarjan V. K., HajSadeghi K. New operational transconductance amplifiers using current boosting //2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS). – IEEE, 2012. – P. 109-112., fig. 1

26. Kalkote M. T., Durai S. A. Enhancement of Transconductance Using Multi-Recycle Folded Cascode Amplifier //Nanoelectronic Materials and Devices. – Springer, Singapore, 2018. – P. 111-122., fig. 1

27. Assaad R., Silva-Martinez J. Recent advances on the design of high-gain wideband operational transconductance amplifiers //VLSI Design. – 2009. – Т. 2009., fig. 5

28. Wang W. et al. Micropower two-stage amplifier employing recycling current-buffer Miller compensation //2014 IEEE International Symposium on Circuits and Systems (ISCAS). – IEEE, 2014. – P. 1889-1892., fig. 2

29. Патент RU 2319291, 2008г., fig. 1

30. Патент US 4.837.523, 1989 г., fig. 1

31. Патент US 4.600.893, 1986 г., fig. 4

32. Патент US 6.236.273, 2001 г., fig. 1С

33. Патент US 6.529.076, 2003 г., fig. 1,2

34. Патент RU 2193273, 2002 г., fig. 1

35. Патент US 5.327.100, 1994 г., fig. 1

36. Патент US 4.406.990, 1983 г., fig. 6

37. Патент US 6.144.234, 2000 г., fig. 9

38. Патент US 6.924.701, 2005 г., fig. 3

39.Патент РФ № 2319291, 2008 г., fig. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах | 2024 |

|

RU2837569C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770913C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

Изобретение относится к области радиотехники и может быть использовано в качестве малошумящего устройства усиления аналоговых сигналов в структуре аналоговых интерфейсов различного функционального назначения, в том числе работающих в широком диапазоне температур и воздействия радиации. Технический результат: создание условий, при которых в ОУ реализуются малые значения систематической составляющей напряжения смещения нуля. При этом положительный эффект обеспечивается за счет специального построения входного дифференциального каскада ОУ и «перегнутого» каскода. Операционный усилитель на основе «перегнутого» каскода и комплементарных полевых транзисторов содержит входной дифференциальный каскад (1) на полевых транзисторах, первый (8) выходной полевой транзистор, второй (9) выходной полевой транзистор, первый (10) токостабилизирующий двухполюсник на полевом транзисторе, второй (12) токостабилизирующий двухполюсник на полевом транзисторе, цепь динамической нагрузки (13), первую и вторую шины источника питания. 3 з.п. ф-лы, 12 ил.

1. Операционный усилитель на основе «перегнутого» каскода и комплементарных полевых транзисторов, содержащий входной дифференциальный каскад (1) на полевых транзисторах с первым (2) и вторым (3) входами, а также с первым (4) и вторым (5) токовыми выходами устройства, общая истоковая цепь (6) которого согласована с первой (7) шиной источника питания, первый (8) выходной полевой транзистор, исток которого соединен со вторым (5) токовым выходом входного дифференциального каскада (1), второй (9) выходной полевой транзистор, исток которого связан с первым (4) токовым выходом входного дифференциального каскада (1), первый (10) токостабилизирующий двухполюсник на полевом транзисторе, который включен между первым (4) токовым выходом входного дифференциального каскада (1) и второй (11) шиной источника питания, второй (12) токостабилизирующий двухполюсник на полевом транзисторе, включенный между вторым (5) токовым выходом входного дифференциального каскада (1) и второй (11) шиной источника питания, цепь динамической нагрузки (13), включенная между стоком первого (8) выходного полевого транзистора, связанного с токовым выходом устройства (14) и первой (7) шиной источника питания, отличающийся тем, что первый (10) токостабилизирующий двухполюсник выполнен на полевом транзисторе (15), затвор которого соединен со второй (11) шиной источника питания, а исток подключен ко второй (11) шине источника питания через первый (16) дополнительный резистор, второй (12) токостабилизирующий двухполюсник выполнен на полевом транзисторе (17), затвор которого соединен со второй (11) шиной источника питания, а исток подключен ко второй (11) шине источника питания через второй (18) дополнительный резистор, исток первого (8) выходного транзистора соединен со стоком первого (19) вспомогательного полевого транзистора, затвор которого подключен ко второй (11) шине источника питания, а исток соединен с затвором первого (8) выходного полевого транзистора и связан со второй (11) шиной источника питания через третий (20) дополнительный резистор, исток второго (9) выходного транзистора соединен со стоком второго (21) вспомогательного полевого транзистора, затвор которого подключен ко второй (11) шине источника питания, а исток соединен с затвором второго (9) выходного полевого транзистора и связан со второй (11) шиной источника питания через четвертый (22) дополнительный резистор, причем входной дифференциальный каскад (1) содержит первый (23) и второй (24) входные полевые транзисторы, между истоками которых включены последовательно соединенные пятый (25) и шестой (26) дополнительные резисторы, а также первый (27), второй (28), третий (29) и четвертый (30) согласующие полевые транзисторы, затвор первого (23) входного полевого транзистора подключён к первому (2) входу устройства, его сток соединен с первым (4) токовым выходом входного дифференциального каскада (1), а исток соединен с затвором первого (27) согласующего полевого транзистора, затвор второго (24) входного полевого транзистора соединен со вторым (3) входом устройства, его сток связан со вторым (5) токовым выходом входного дифференциального каскада (1), а исток соединен с затвором второго (28) согласующего полевого транзистора, истоки первого (27) и второго (28) согласующих полевых транзисторов объединены, а также соединены с затворами третьего (29) и четвертого (30) согласующих полевых транзисторов и общим узлом последовательно соединенных пятого (25) и шестого (26) дополнительных резисторов, сток первого (27) согласующего полевого транзистора подключен к истоку третьего (29) согласующего полевого транзистора, сток второго (28) согласующего полевого транзистора подключен к истоку четвертого (30) согласующего полевого транзистора, стоки третьего (29) и четвертого (30) согласующих полевых транзисторов связаны с общей истоковой цепью (6) входного дифференциального каскада (1), цепь динамической нагрузки (13) включает первый (31) и второй (32) дополнительные полевые транзисторы, затвор первого (31) дополнительного полевого транзистора соединен с токовым выходом устройства (14), а его исток связан с затвором второго (32) дополнительного полевого транзистора и подключен к токовому выходу устройства (14) через согласующий резистор (33), сток первого (31) дополнительного полевого транзистора связан с истоком второго (32) дополнительного полевого транзистора, сток второго (32) дополнительного полевого транзистора подключен к первой (7) шине источника питания, а сток второго (9) выходного полевого транзистора связан с источником напряжения смещения (34).

2. Операционный усилитель на основе «перегнутого» каскода и комплементарных полевых транзисторов по п.1, отличающийся тем, что токовый выход устройства (14) соединен с входом буферного усилителя (36), выход которого (37) является потенциальным выходом устройства.

3. Операционный усилитель на основе «перегнутого» каскода и комплементарных полевых транзисторов по п.1, отличающийся тем, что в качестве источника напряжения смещения (34) используется общая шина источников питания.

4. Операционный усилитель на основе «перегнутого» каскода и комплементарных полевых транзисторов по п.1, отличающийся тем, что в качестве источника напряжения смещения (34) используется потенциальный выход (37).

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

| Дифференциальный усилитель | 1978 |

|

SU674199A1 |

| Устройство для передачи браслета | 1977 |

|

SU632581A1 |

| US 8604878 B2, 10.12.2013 | |||

| US 7894727 B2, 22.02.2011 | |||

| US 6714076 B1, 30.03.2004. | |||

Авторы

Даты

2022-06-14—Публикация

2022-02-07—Подача