Изобретение относится к области радиотехники и может быть использовано в качестве малошумящего устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения на полевых транзистора, например, в операционных усилителях (ОУ), компараторах и т.п., в том числе работающих в широком диапазоне температур и воздействия радиации.

Известны схемы классических дифференциальных усилителей (ДУ) на полевых транзисторах [1-15], которые стали основой многих аналоговых микросхем.

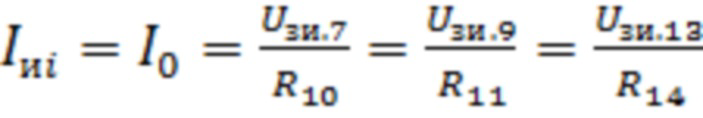

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный усилитель на полевых транзисторах с управляющим p-n переходом (JFET), представленный в патенте RU 2741056, который содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первым 4 и вторым 5 токовыми выходами, истоковую цепь стабилизации статического режима, которая включает первый 6, второй 7, третий 8 и четвертый 9 вспомогательные полевые транзисторы, а также первый 10 и второй 11 вспомогательные резисторы, пятый 12 и шестой 13 вспомогательные полевые транзисторы и третий 14 вспомогательный резистор, образующие цепь динамической нагрузки входного дифференциального каскада 1, первую 15 и вторую 16 шины источников питания.

Существенный недостаток известного ДУ фиг. 1 состоит в том, что для его построения необходимо иметь полевые транзисторы как с n-, так и с p-каналами, что требует специальных дорогостоящих технологических процессов.

Основная задача предполагаемого изобретения состоит в создании условий, при которых в ДУ фиг. 1, реализуемом на однотипных полевых транзисторах, существенно повышается крутизна преобразования входного напряжения в выходной ток устройства, что важно при работе ДУ с малыми статическими токами транзисторов. В конечном итоге, это повышает коэффициент усиления по напряжению практических схем включения ДУ, например, в операционных усилителях или компараторах напряжения.

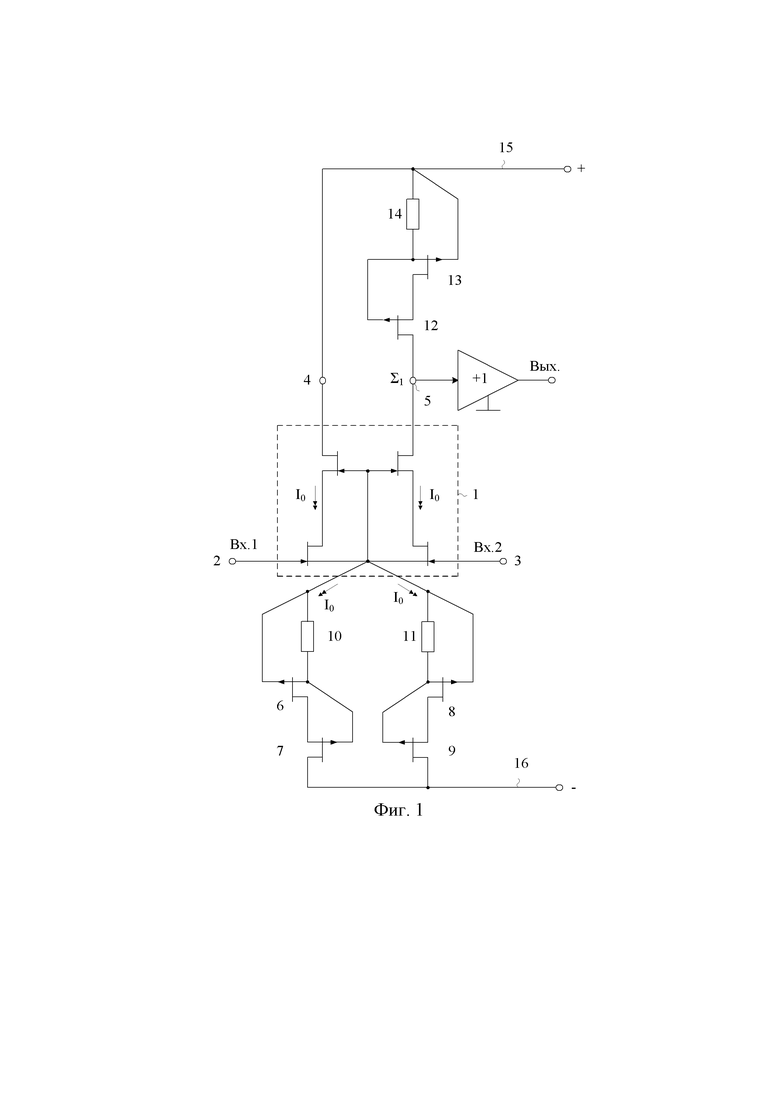

Поставленная задача решается тем, что в дифференциальном усилителе фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первым 4 и вторым 5 токовыми выходами, истоковую цепь стабилизации статического режима, которая включает первый 6, второй 7, третий 8 и четвертый 9 вспомогательные полевые транзисторы, а также первый 10 и второй 11 вспомогательные резисторы, пятый 12 и шестой 13 вспомогательные полевые транзисторы и третий 14 вспомогательный резистор, образующие цепь динамической нагрузки входного дифференциального каскада 1, первую 15 и вторую 16 шины источников питания, предусмотрены новые элементы и связи – сток пятого 12 вспомогательного полевого транзистора соединен с токовым выходом устройства 17, согласованным с первой 15 шиной источника питания, сток шестого 13 вспомогательного полевого транзистора соединен с истоком пятого 12 вспомогательного полевого транзистора и подключен к источнику напряжения смещения 18, затвор пятого 12 вспомогательного полевого транзистора связан с истоком шестого 13 вспомогательного полевого транзистора и через третий 14 вспомогательный резистор подключен ко второму 5 токовому выходу входного дифференциального каскада 1, затвор шестого 13 вспомогательного полевого транзистора соединен со вторым 5 токовым выходом входного дифференциального каскада 1, стоки первого 6 и третьего 8 вспомогательных полевых транзисторов соединены с общей истоковой цепью стабилизации статического режима входного дифференциального каскада 1, затвор первого 6 вспомогательного полевого транзистора соединен с истоком второго 7 вспомогательного полевого транзистора, который подключен ко второй 16 шине источника питания через первый 10 вспомогательный резистор, сток второго 7 вспомогательного полевого транзистора соединен с истоком первого 6 вспомогательного полевого транзистора, а затвор второго 7 вспомогательного полевого транзистора подключен ко второй 16 шине источника питания, затвор третьего 8 вспомогательного полевого транзистора соединен с истоком четвертого 9 вспомогательного полевого транзистора, который связан со второй 16 шиной источника питания через второй 11 вспомогательный резистор, сток четвертого 9 вспомогательного полевого транзистора соединен с истоком третьего 8 вспомогательного полевого транзистора, а затвор четвертого 9 вспомогательного полевого транзистора подключен ко второй 16 шине источника питания.

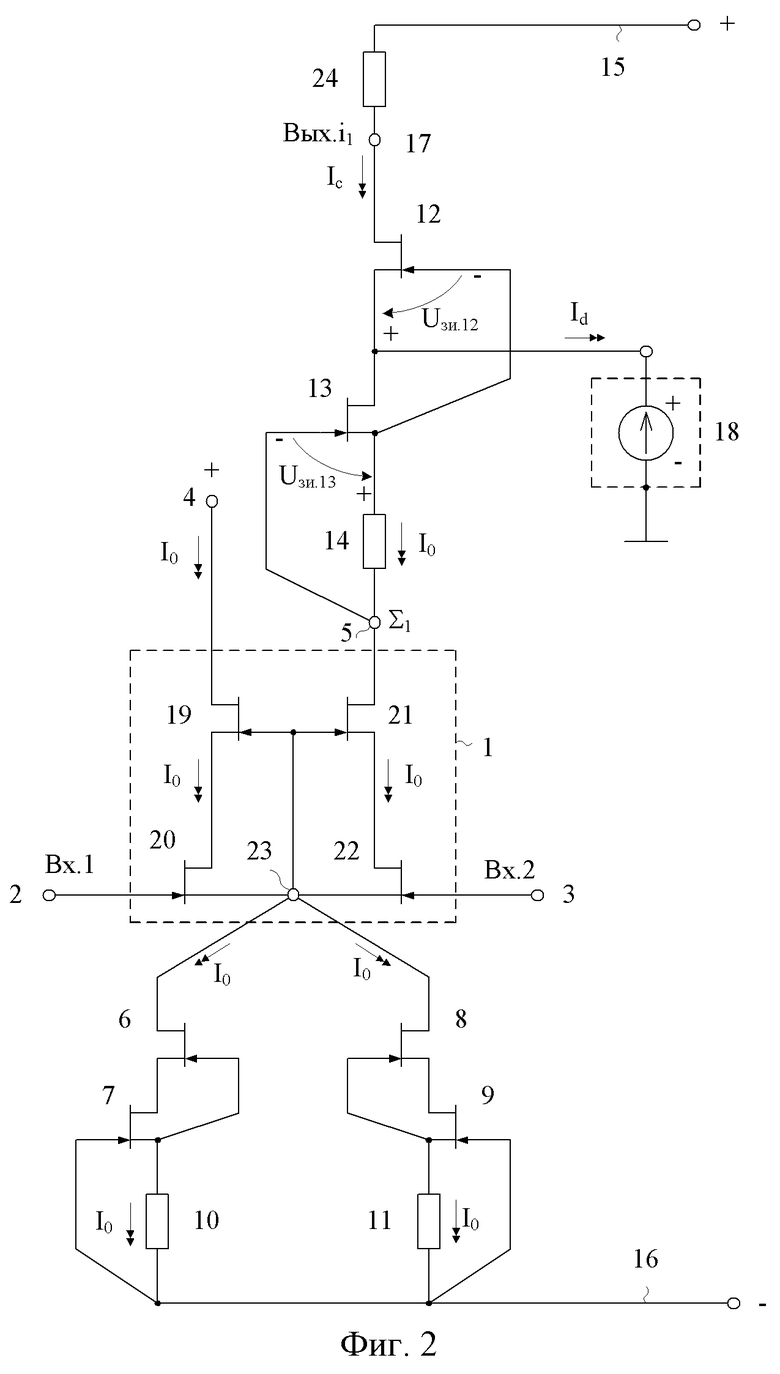

На чертеже фиг. 1 представлена схема ДУ-прототипа при его реализации на JFET транзисторах с дуальными типами каналов, а на чертеже фиг. 2 – схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

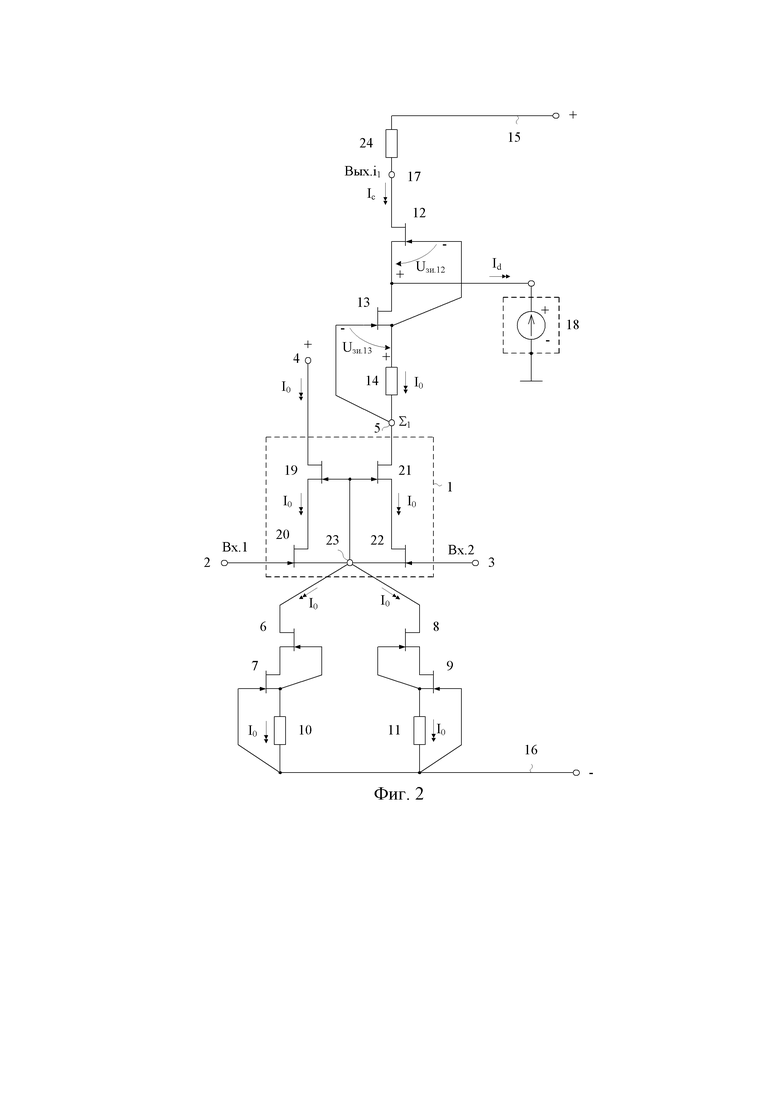

На чертеже фиг. 3 показана схема заявляемого ДУ в соответствии с п. 2 формулы изобретения.

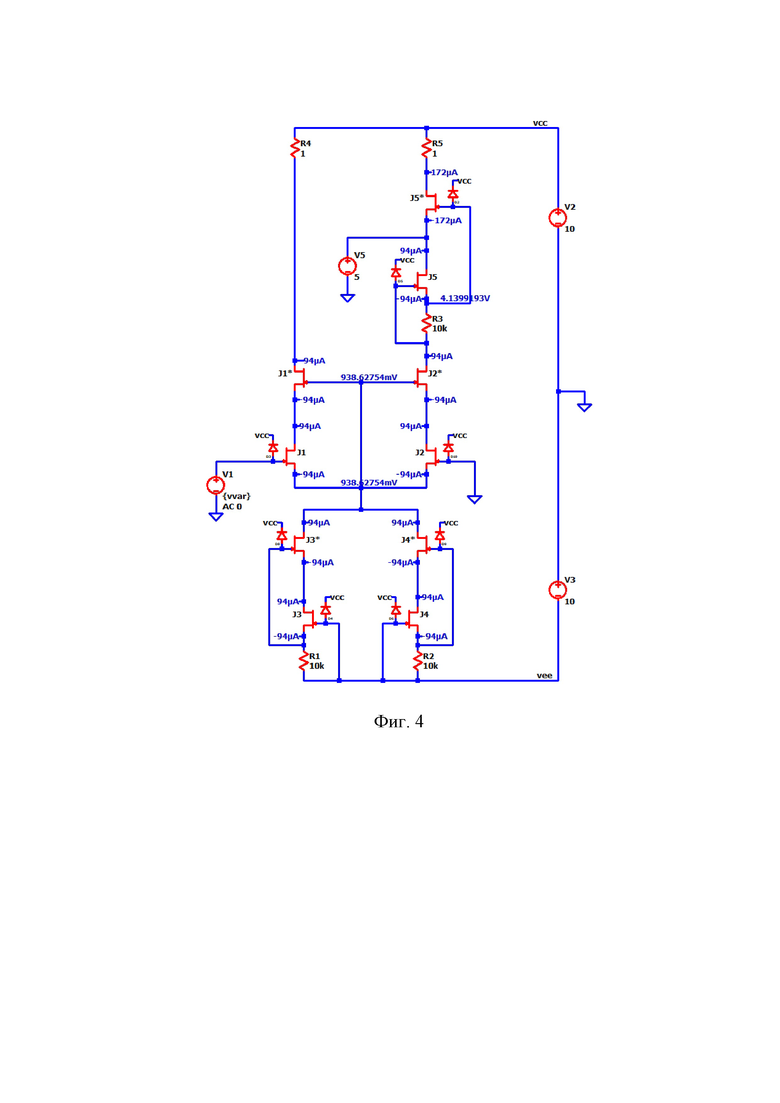

На чертеже фиг. 4 приведен статический режим схемы заявляемого ДУ фиг. 2 в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск) при температуре 27°С.

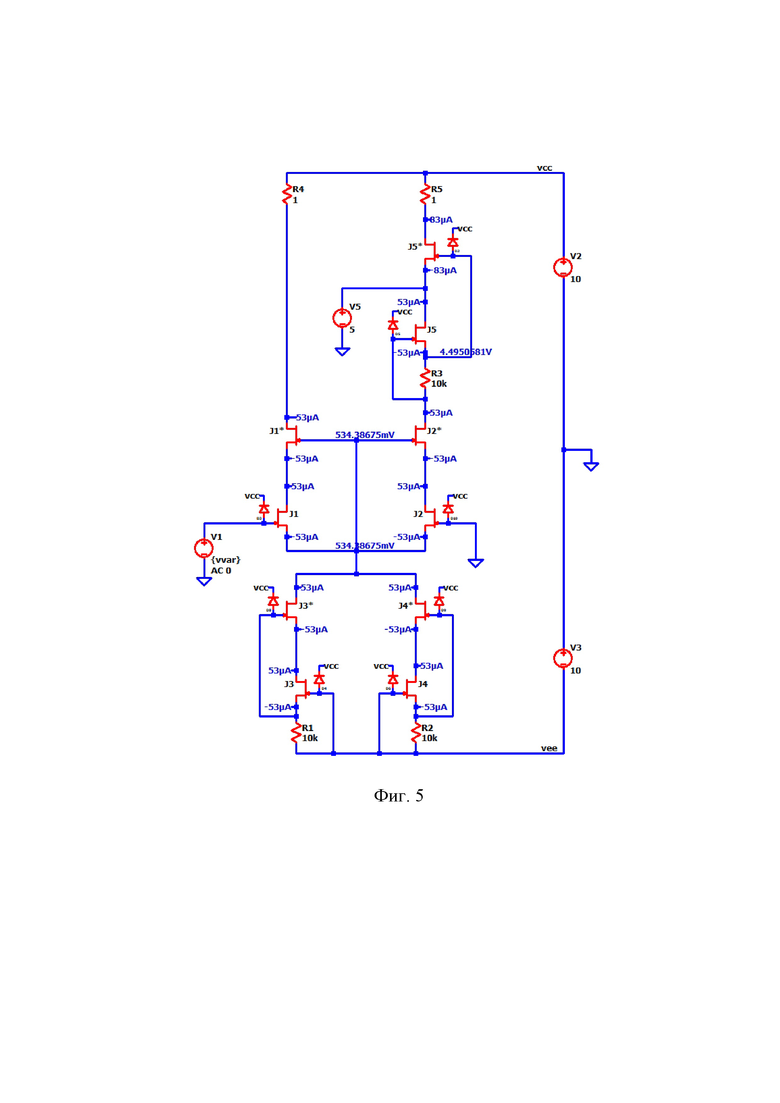

На чертеже фиг. 5 представлен статический режим схемы заявляемого ДУ фиг. 2 в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск) при температуре -197°С.

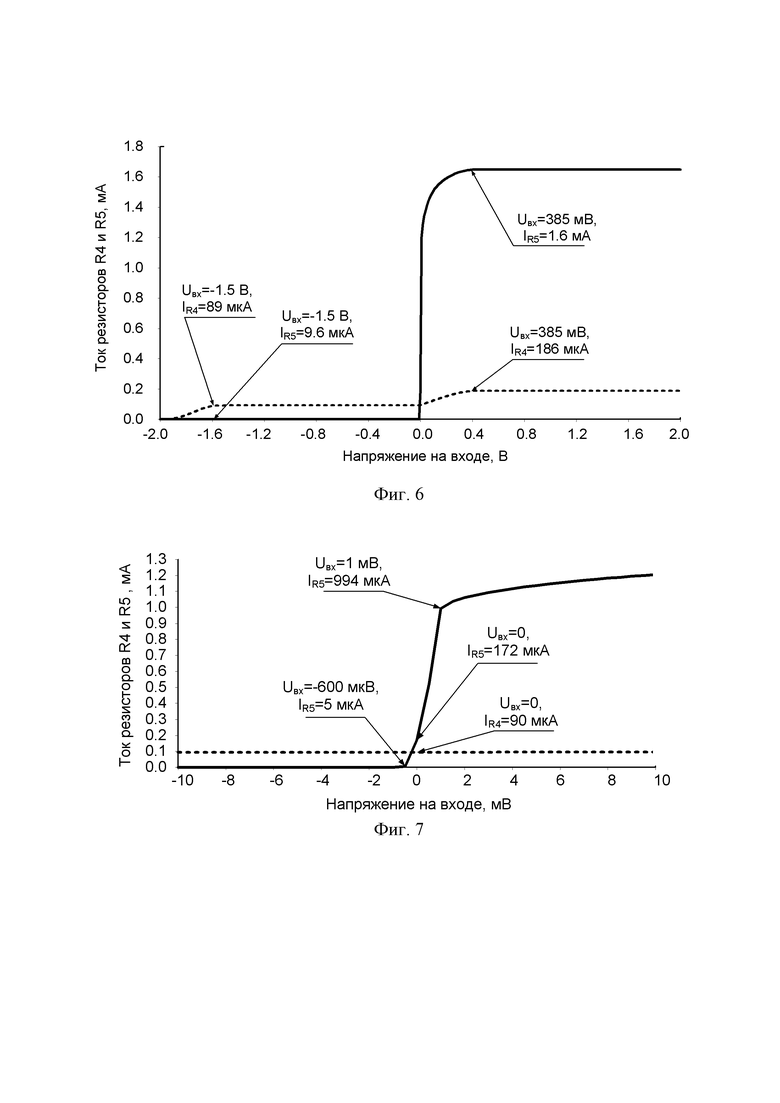

На чертеже фиг. 6 показаны зависимости выходных токов ДУ фиг. 4 от входного напряжения при температуре 27°С.

На чертеже фиг. 7 приведены зависимости (увеличенный масштаб) выходных токов ДУ фиг. 4 от входного напряжения при температуре 27°С.

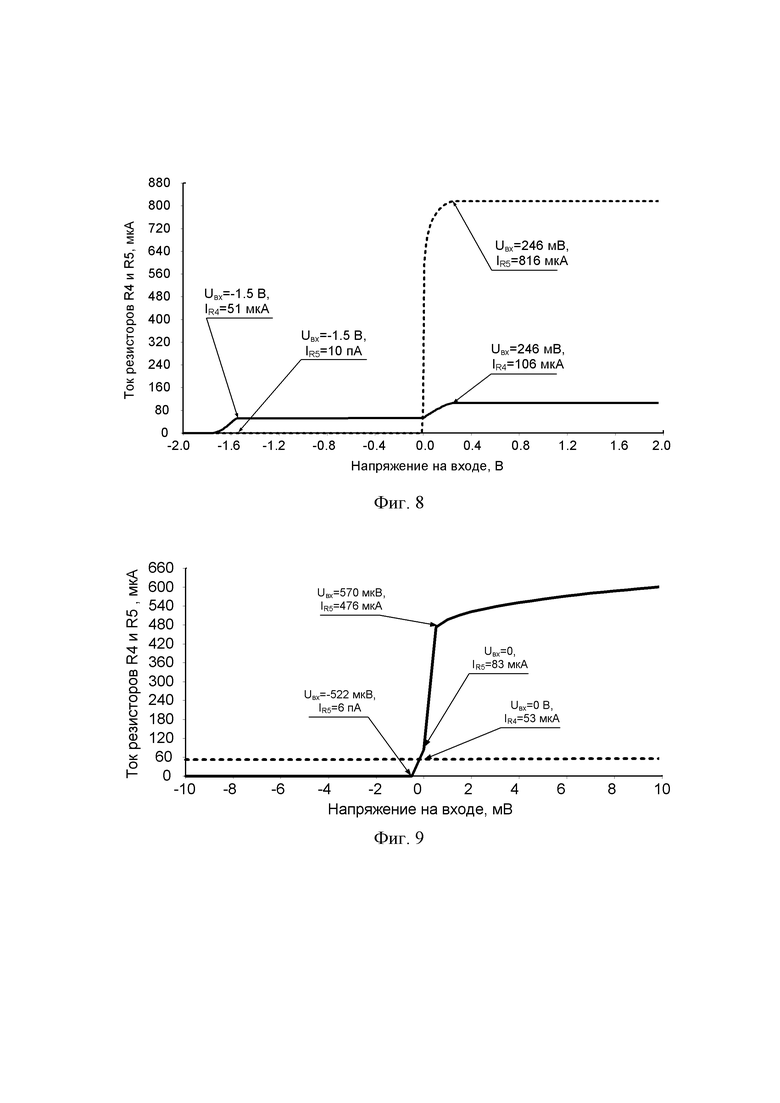

На чертеже фиг. 8 представлена зависимость выходных токов ДУ фиг. 5 от входного напряжения при температуре -197°С.

На чертеже фиг. 9 приведена зависимость (увеличенный масштаб) выходных токов ДУ фиг. 5 от входного напряжения при температуре -197°С.

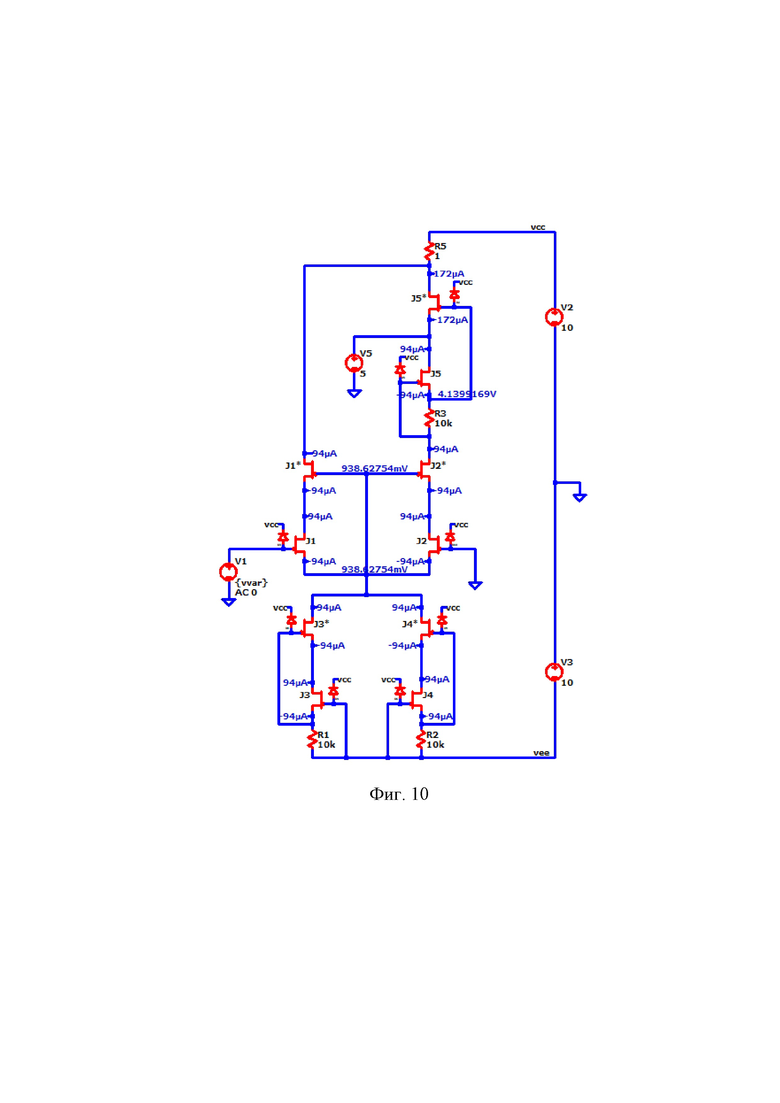

На чертеже фиг. 10 показан статический режим схемы заявляемого ДУ фиг. 3 в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск) при температуре 27°С.

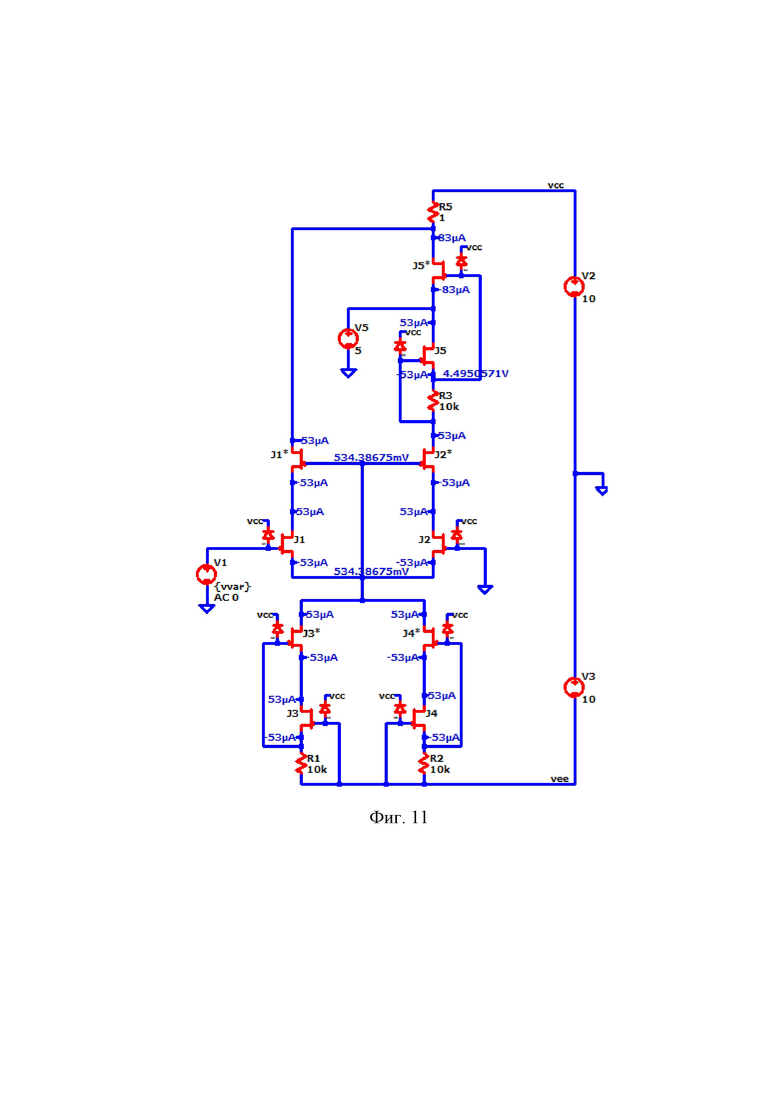

На чертеже фиг. 11 представлен статический режим схемы заявляемого ДУ фиг. 3 в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск) при температуре -197°С.

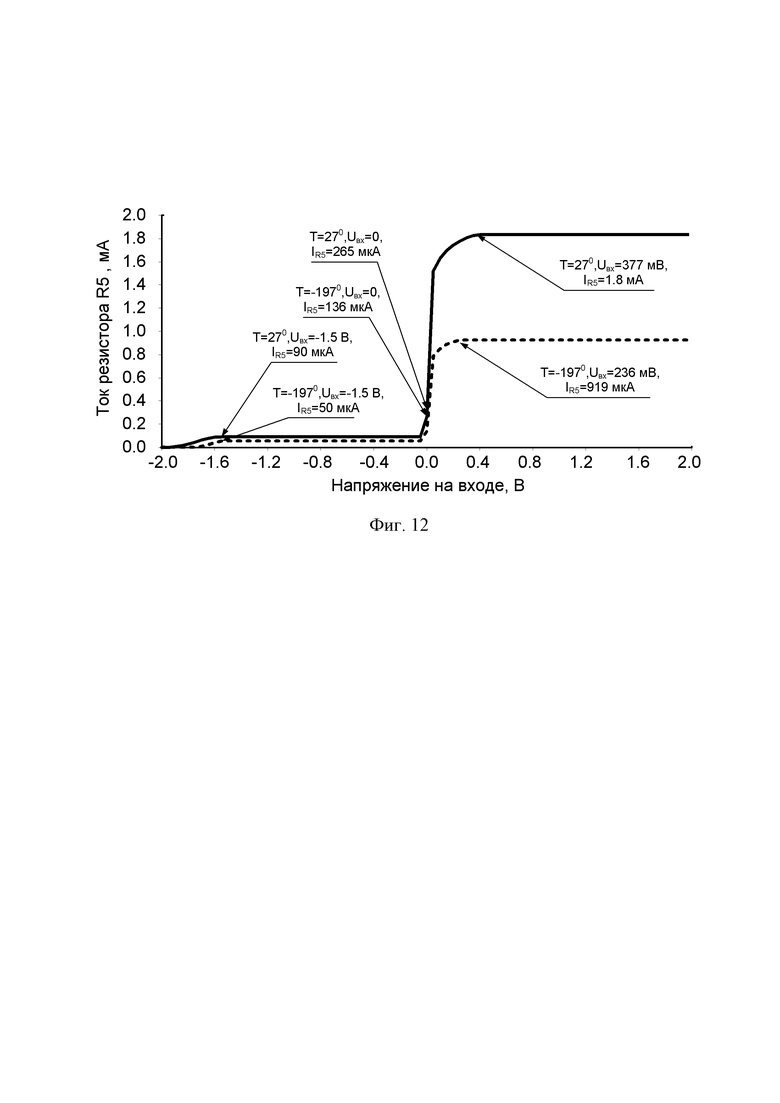

На чертеже фиг. 12 показаны зависимости выходного тока ДУ фиг. 10 и фиг. 11 от входного напряжения при температурах -197°С и 27°С

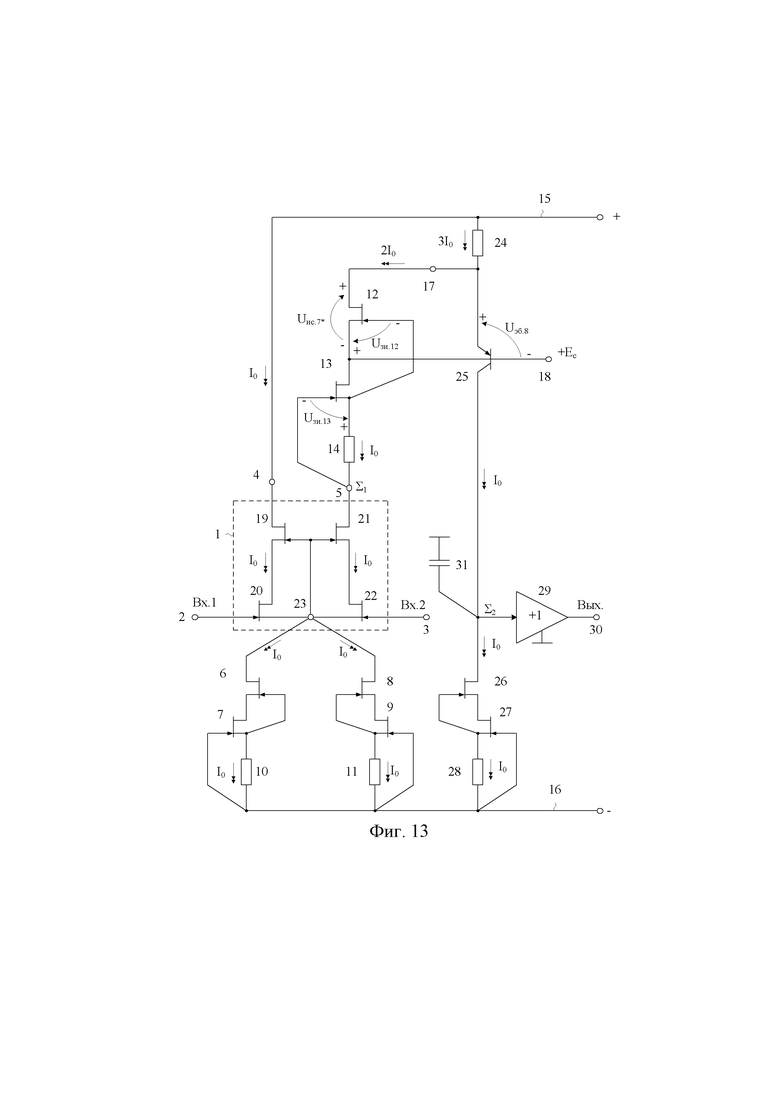

На чертеже фиг. 13 приведена схема включения заявляемого ДУ по п. 3 формулы изобретения (фиг. 3) в операционном усилителе с повышенным коэффициентом усиления.

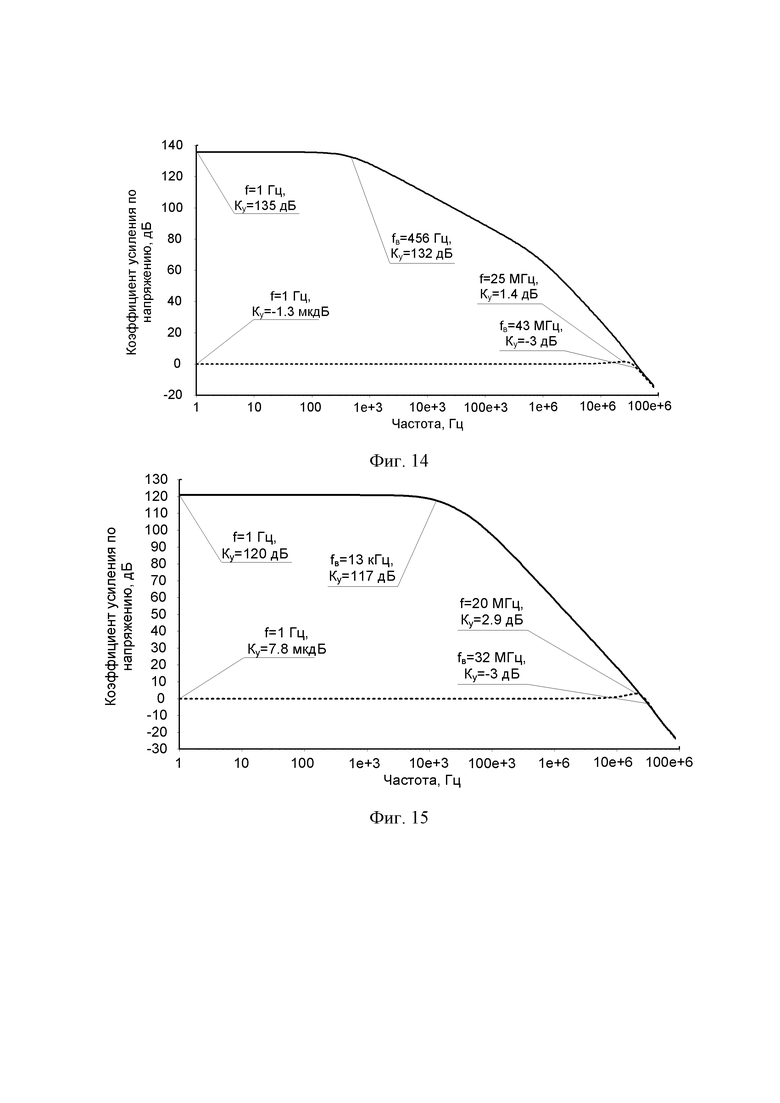

На чертеже фиг. 14 представлена амплитудно-частотная характеристика (АЧХ) операционного усилителя фиг. 13 при температуре 27°С.

На чертеже фиг. 15 показана АЧХ операционного усилителя фиг. 13 при температуре -197°С.

Дифференциальный усилитель с повышенной крутизной на полевых транзисторах фиг. 2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, первым 4 и вторым 5 токовыми выходами, истоковую цепь стабилизации статического режима, которая включает первый 6, второй 7, третий 8 и четвертый 9 вспомогательные полевые транзисторы, а также первый 10 и второй 11 вспомогательные резисторы, пятый 12 и шестой 13 вспомогательные полевые транзисторы и третий 14 вспомогательный резистор, образующие цепь динамической нагрузки входного дифференциального каскада 1, первую 15 и вторую 16 шины источников питания. Сток пятого 12 вспомогательного полевого транзистора соединен с токовым выходом устройства 17, согласованным с первой 15 шиной источника питания, сток шестого 13 вспомогательного полевого транзистора соединен с истоком пятого 12 вспомогательного полевого транзистора и подключен к источнику напряжения смещения 18, затвор пятого 12 вспомогательного полевого транзистора связан с истоком шестого 13 вспомогательного полевого транзистора и через третий 14 вспомогательный резистор подключен ко второму 5 токовому выходу входного дифференциального каскада 1, затвор шестого 13 вспомогательного полевого транзистора соединен со вторым 5 токовым выходом входного дифференциального каскада 1, стоки первого 6 и третьего 8 вспомогательных полевых транзисторов соединены с общей истоковой цепью стабилизации статического режима входного дифференциального каскада 1, затвор первого 6 вспомогательного полевого транзистора соединен с истоком второго 7 вспомогательного полевого транзистора, который подключен ко второй 16 шине источника питания через первый 10 вспомогательный резистор, сток второго 7 вспомогательного полевого транзистора соединен с истоком первого 6 вспомогательного полевого транзистора, а затвор второго 7 вспомогательного полевого транзистора подключен ко второй 16 шине источника питания, затвор третьего 8 вспомогательного полевого транзистора соединен с истоком четвертого 9 вспомогательного полевого транзистора, который связан со второй 16 шиной источника питания через второй 11 вспомогательный резистор, сток четвертого 9 вспомогательного полевого транзистора соединен с истоком третьего 8 вспомогательного полевого транзистора, а затвор четвертого 9 вспомогательного полевого транзистора подключен ко второй 16 шине источника питания.

На чертеже фиг. 2 входной дифференциальный каскад 1 выполнен в частном случае на полевых транзисторах 19, 20, 21 и 22, причем объединенные истоки транзисторов 20 и 22 являются истоковой цепью 23 стабилизации статического режима входного дифференциального каскада 1. Кроме этого, на чертеже фиг. 2 резистор 24 моделирует свойства нагрузки, которая подключается к токовому выходу устройства 17.

На чертеже фиг. 3 показана схема заявляемого устройства в соответствии с п. 2 формулы изобретения, в которой первый 4 токовый выход входного дифференциального каскада 1 связан с токовым выходом устройства 17. При таком включении заявляемый ДУ обеспечивает усиление сигнала по двум разным каналам, что положительно сказывается на расширении диапазона рабочих частот.

На чертежах фиг. 4 – фиг. 12 приведены схемы заявляемого устройства в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск) и результаты их компьютерного моделирования.

На чертеже фиг. 13 приведена схема заявляемого устройства в соответствии с п. 3 формулы изобретения, в которой токовый выход 17 устройства соединен с эмиттером дополнительного транзистора 25, база которого подключена к цепи смещения 18, коллектор соединен со стоком транзистора 26, исток которого связан со стоком транзистора 27, затвор подключен к истоку транзистора 27 и через резистор 28 соединен со второй 16 шиной источника питания, затвор транзистора 27 со второй 16 шиной источника питания, причем коллектор транзистора 25 связан со входом дополнительного буферного усилителя 29, потенциальный выход которого является потенциальным выходом устройства.

В соответствии с п. 4 формулы изобретения, в качестве полевых транзисторов заявляемой схемы ДУ могут использоваться полевые транзисторы с управляющим pn-переходом (фиг. 2, фиг. 3).

В соответствии с п. 5 формулы изобретения, в качестве всех полевых транзисторов схемы ДУ используются КМОП транзисторы со встроенным каналом. Для этого все полевые JFET транзисторы на чертежах фиг. 2 (фиг. 3) следует формально заменить на КМОП транзисторы со встроенным каналом. При этом основные свойства заявляемого ДУ и схем его включения в ОУ сохраняются.

Рассмотрим работу ДУ фиг. 2.

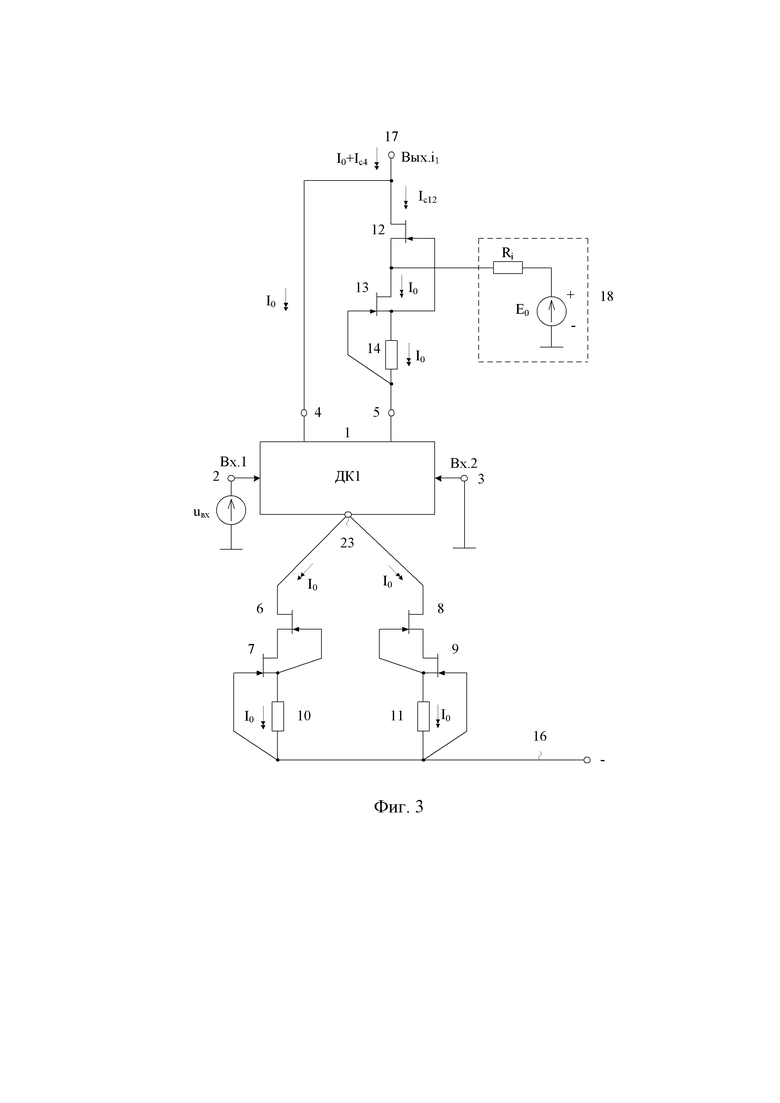

В статическом режиме, например, при подключении первого 2 и второго 3 входов ДУ фиг. 2 к общей шине источников питания, статические токи истоков первого 6, второго 7, третьего 8, четвертого 9, шестого 13 вспомогательных полевых транзисторов, а также полевых транзисторов 19, 20, 21, 22, входящих в структуру входного дифференциального каскада 1, определяются численными значениями идентичных сопротивлений первого 10, второго 11 и третьего 14 вспомогательных резисторов:

, (1)

, (1)

где Iиi – ток истока i-го полевого транзистора;

Uзи.i – напряжение затвор-исток соответствующих полевых транзисторов в рабочей точке при токе истока, равном I0;

Ri – сопротивления соответствующих вспомогательных резисторов (10, 11, 14).

Таким образом, в схеме фиг. 2 за счет выбора сопротивлений первого 10, второго 11 и третьего 14 вспомогательных резисторов при известных стоко-затворных характеристиках JFET обеспечивается заданный статический режим по току.

Если на вход 2 подается положительное входное напряжение uвх относительно входа 3, то это вызывает увеличение тока в цепи первого 4 токового выхода и уменьшение на такую же величину тока второго 5 токового выхода. Приращение напряжения на втором 5 токовом выходе входного каскада 1 передается без изменения фазы в истоковую цепь транзистора 13 и далее на затвор пятого 12 вспомогательного полевого транзистора. Как следствие, при относительно низком выходном сопротивлении источника напряжения смещения 18 увеличивается ток истока и, следовательно, ток стока транзистора 12. Таким образом, токовый выход устройства 17 оказывается имеет такую же фазу сигнала, что и первый 4 токовый выход входного дифференциального каскада 1. Поэтому, в соответствии с п. 2 формулы изобретения, первый 4 токовый выход входного дифференциального каскада 1 может быть соединен с токовым выходом устройства 17. Представленные на чертежах фиг. 6 – фиг. 9, фиг.12 графики подтверждают работоспособность предлагаемого ДУ в данном режиме. В частном случае токовый выход устройства 17 может быть соединен со входом «перегнутого» каскода на транзисторе 25 в схеме ОУ фиг. 13.

За счет введения новых элементов и связей между ними предлагаемый ДУ (в сравнении с прототипом) имеет (при малых одинаковых статических токах транзисторов) повышенные значения крутизны усиления:

SДУ= ΔIвх / ΔUвх,

где ΔIвых – приращение выходного тока ДУ по выходу Вых.i1 (17) при изменении входного напряжения между первым 2 и вторым 3 входами на величину ΔUвх.

Данный вывод следует из рассмотрения графиков фиг. 6 – фиг. 9. Это позволяет получать на основе заявляемого ДУ более высокое малосигнальное усиление по напряжению в операционных усилителях (фиг. 14, фиг. 15).

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ДУ-прототипом, что позволяет рекомендовать его для практического использования в различных аналоговых схемах – операционных усилителях, компараторах, стабилизаторах напряжения. БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU 2710296, 2019 г.

2. Авт.св. СССР 537435, 1976 г.

3. Патентная заявка RU 2020134402, 2020 г.

4. Патент US 5.291.149, fig. 3, 1994 г.

5. Патент RU 2679970, fig. 2, 2019 г.

6. Патент RU 2624565, fig. 1, 2016 г.

7. Патент RU 2571399, fig. 2, 2014 г.

8. Авт.св. СССР 437193, 1972 г.

9. Патентная заявка US 2006/01255222, 2006 г.

10. Патент US 4.121.169, fig. 5, fig. 6, 1978 г.

11. Патент US 9.668.045, 2017 г.

12. Патент US 9.888.315, 2018 г.

13. Патент US 9.167.327, 2015 г.

14. Патент EP 0293488, fig. 1, 1988 г.

15. Патент US 5.166.553, fig. 14, 1992 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2766864C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770913C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784666C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННОЙ ТЕМПЕРАТУРНОЙ СТАБИЛЬНОСТЬЮ СТАТИЧЕСКОГО РЕЖИМА | 2020 |

|

RU2746888C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННОЙ СТАБИЛЬНОСТЬЮ СТАТИЧЕСКОГО РЕЖИМА | 2019 |

|

RU2710930C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ И РАДИАЦИОННО-СТОЙКИЙ КОМПЕНСАЦИОННЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2732950C1 |

Изобретение относится к области радиотехники. Технический результат: повышение крутизны преобразования входного напряжения в выходной ток устройства, в итоге повышение коэффициента усиления по напряжению. Для этого в известном дифференциальном усилителе с повышенной крутизной на полевых транзисторах сток пятого (12) вспомогательного полевого транзистора соединен с токовым выходом устройства (17), согласованным с первой (15) шиной источника питания, сток шестого (13) вспомогательного полевого транзистора соединен с истоком пятого (12) вспомогательного полевого транзистора и подключен к источнику напряжения смещения (18), затвор пятого (12) вспомогательного полевого транзистора связан с истоком шестого (13) вспомогательного полевого транзистора и через третий (14) вспомогательный резистор подключен ко второму (5) токовому выходу входного дифференциального каскада (1), затвор шестого (13) вспомогательного полевого транзистора соединен со вторым (5) токовым выходом входного дифференциального каскада (1), а также использованы другие связи и элементы. 4 з.п. ф-лы, 15 ил.

1. Дифференциальный усилитель с повышенной крутизной на полевых транзисторах, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) входами, первым (4) и вторым (5) токовыми выходами, истоковую цепь стабилизации статического режима, которая включает первый (6), второй (7), третий (8) и четвертый (9) вспомогательные полевые транзисторы, а также первый (10) и второй (11) вспомогательные резисторы, пятый (12) и шестой (13) вспомогательные полевые транзисторы и третий (14) вспомогательный резистор, образующие цепь динамической нагрузки входного дифференциального каскада (1), первую (15) и вторую (16) шины источников питания, отличающийся тем, что сток пятого (12) вспомогательного полевого транзистора соединен с токовым выходом устройства (17), согласованным с первой (15) шиной источника питания, сток шестого (13) вспомогательного полевого транзистора соединен с истоком пятого (12) вспомогательного полевого транзистора и подключен к источнику напряжения смещения (18), затвор пятого (12) вспомогательного полевого транзистора связан с истоком шестого (13) вспомогательного полевого транзистора и через третий (14) вспомогательный резистор подключен ко второму (5) токовому выходу входного дифференциального каскада (1), затвор шестого (13) вспомогательного полевого транзистора соединен со вторым (5) токовым выходом входного дифференциального каскада (1), стоки первого (6) и третьего (8) вспомогательных полевых транзисторов соединены с общей истоковой цепью стабилизации статического режима входного дифференциального каскада (1), затвор первого (6) вспомогательного полевого транзистора соединен с истоком второго (7) вспомогательного полевого транзистора, который подключен ко второй (16) шине источника питания через первый (10) вспомогательный резистор, сток второго (7) вспомогательного полевого транзистора соединен с истоком первого (6) вспомогательного полевого транзистора, а затвор второго (7) вспомогательного полевого транзистора подключен ко второй (16) шине источника питания, затвор третьего (8) вспомогательного полевого транзистора соединен с истоком четвертого (9) вспомогательного полевого транзистора, который связан со второй (16) шиной источника питания через второй (11) вспомогательный резистор, сток четвертого (9) вспомогательного полевого транзистора соединен с истоком третьего (8) вспомогательного полевого транзистора, а затвор четвертого (9) вспомогательного полевого транзистора подключен ко второй (16) шине источника питания.

2. Дифференциальный усилитель с повышенной крутизной на полевых транзисторах по п. 1, отличающийся тем, что первый (4) токовый выход входного дифференциального каскада (1) связан с токовым выходом устройства (17).

3. Дифференциальный усилитель с повышенной крутизной на полевых транзисторах по п. 1, отличающийся тем, что токовый выход (17) устройства соединен с эмиттером дополнительного транзистора (25), база которого подключена к цепи смещения (18), коллектор соединен со стоком транзистора (26), исток которого связан со стоком транзистора (27), затвор подключен к истоку транзистора (27) и через резистор (28) соединен со второй (16) шиной источника питания, причем затвор транзистора (27) соединен со второй (16) шиной источника питания, а коллектор дополнительного транзистора (25) связан со входом дополнительного буферного усилителя (29), потенциальный выход которого является потенциальным выходом устройства (30).

4. Дифференциальный усилитель с повышенной крутизной на полевых транзисторах по п. 1, отличающийся тем, что в качестве полевых транзисторов используются полевые транзисторы с управляющим pn-переходом.

5. Дифференциальный усилитель с повышенной крутизной на полевых транзисторах по п. 1, отличающийся тем, что в качестве полевых транзисторов используются КМОП со встроенным каналом.

| РАДИАЦИОННО-СТОЙКИЙ И НИЗКОТЕМПЕРАТУРНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2020 |

|

RU2741056C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ JFET ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2019 |

|

RU2710296C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736412C1 |

| US 5291149 A1, 01.03.1994. | |||

Авторы

Даты

2022-04-25—Публикация

2021-10-06—Подача