Изобретение относится к автоматике и вычислительной технике, а именно к устройствам контроля работоспособности и поиска дефектов цифровых узлов и блоков.

Цель изобретения - расширение области применения за счет возможности диагностирования цифровых блоков с двунаправленными входами-выходами.

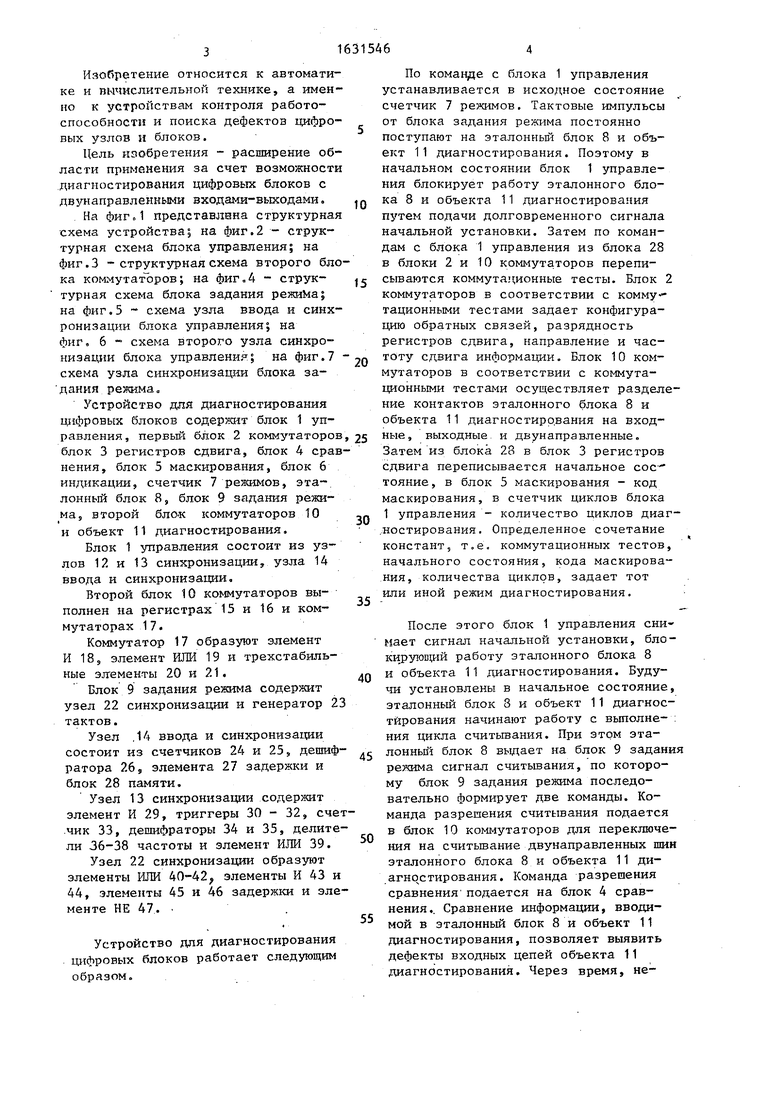

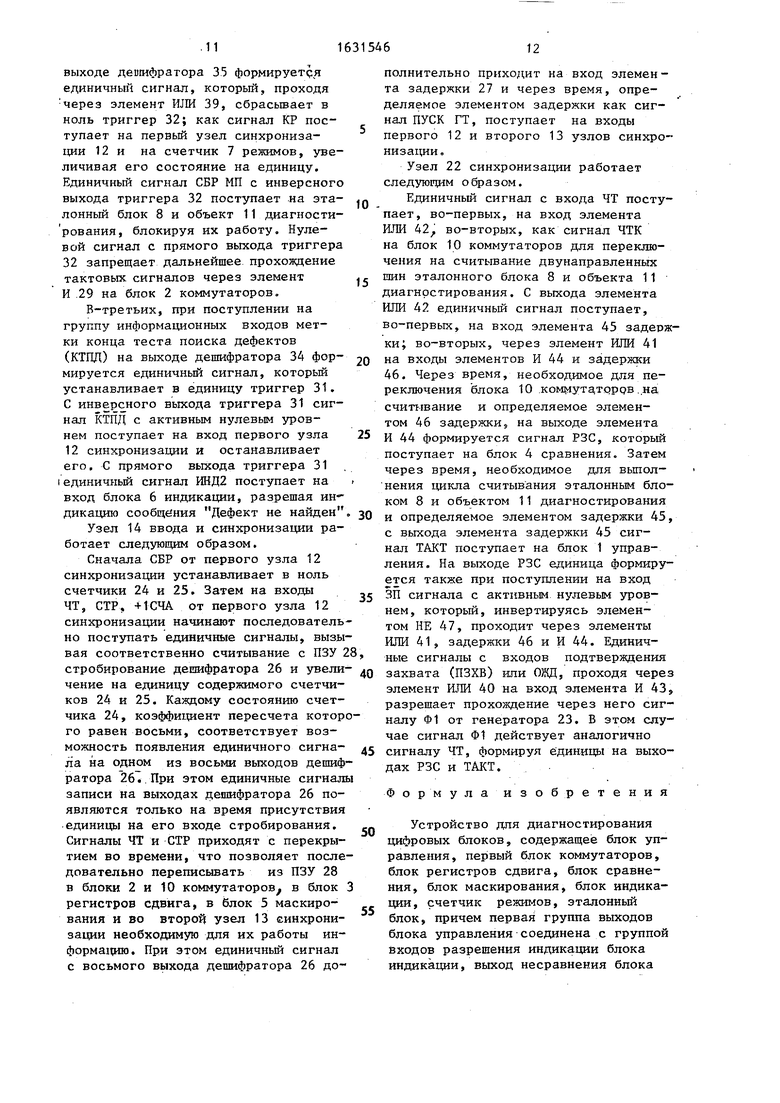

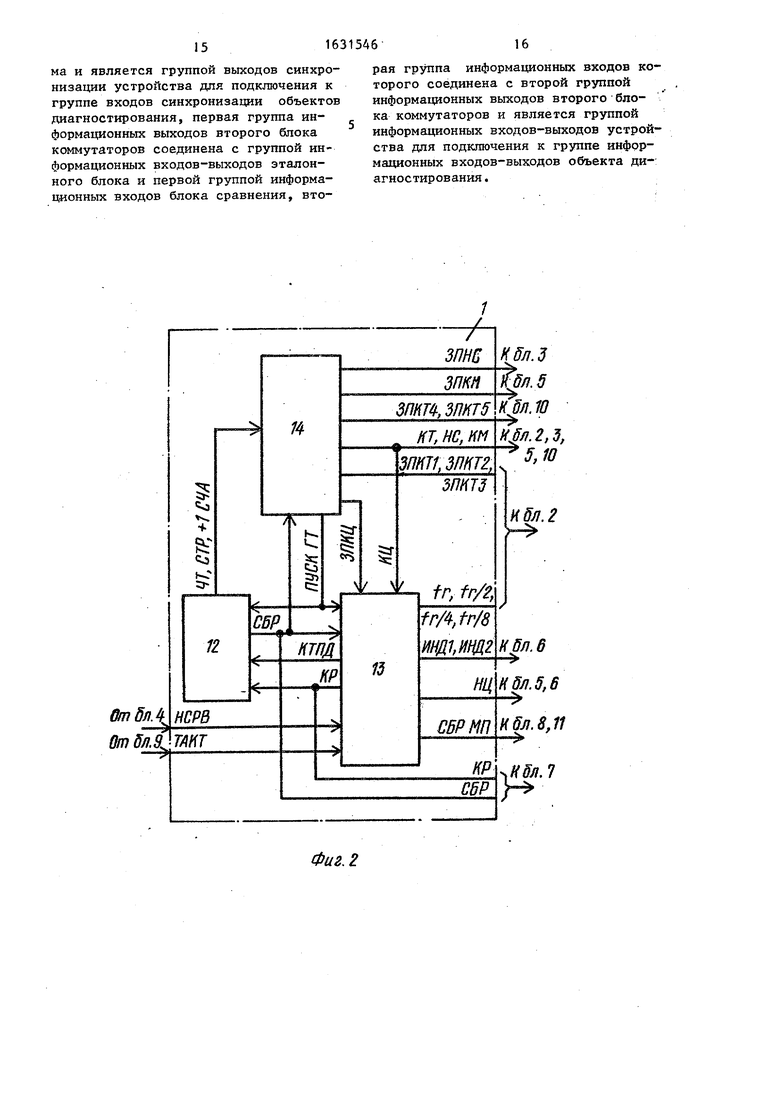

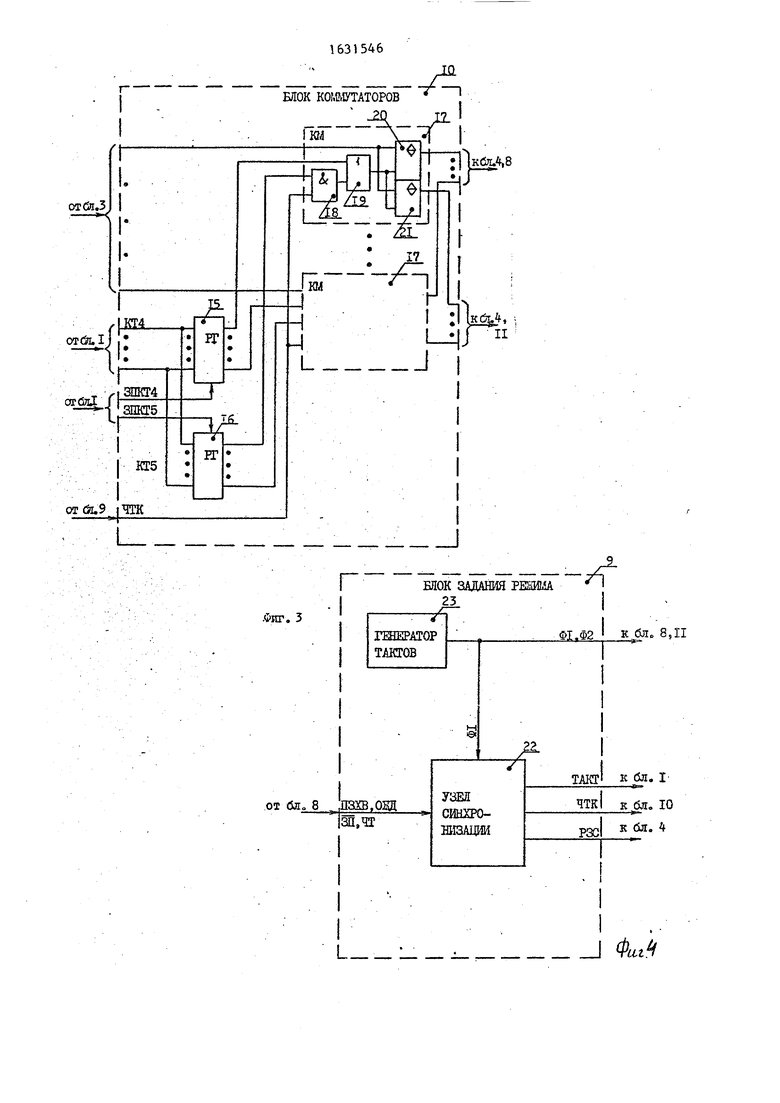

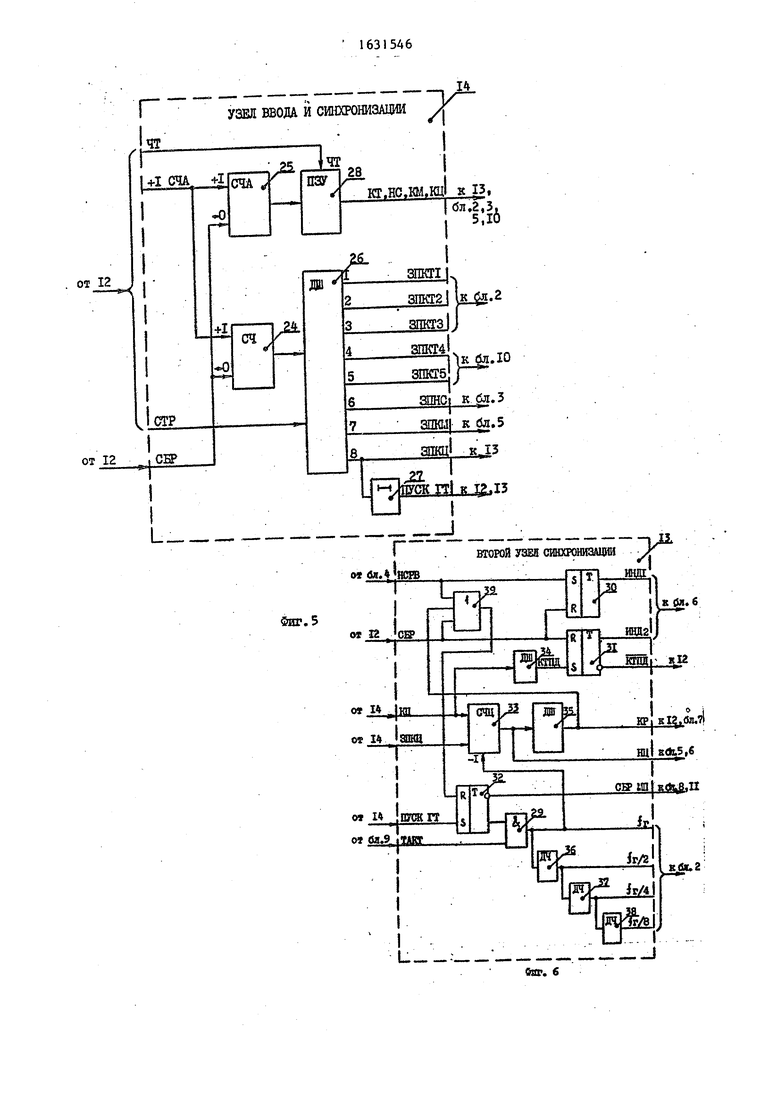

На представлена структурная схема устройства на фиг.2 - структурная схема блока управления; на фиг.З - структурная схема второго блока коммутаторов; на фиг,4 - структурная схема блока задания режима; на фиг.5 - схема узла ввода и синхронизации блока управления; на фиг, б - схема второго узла синхронизации блока управления; на фиг.7 схема узла синхронизации блока задания режима.

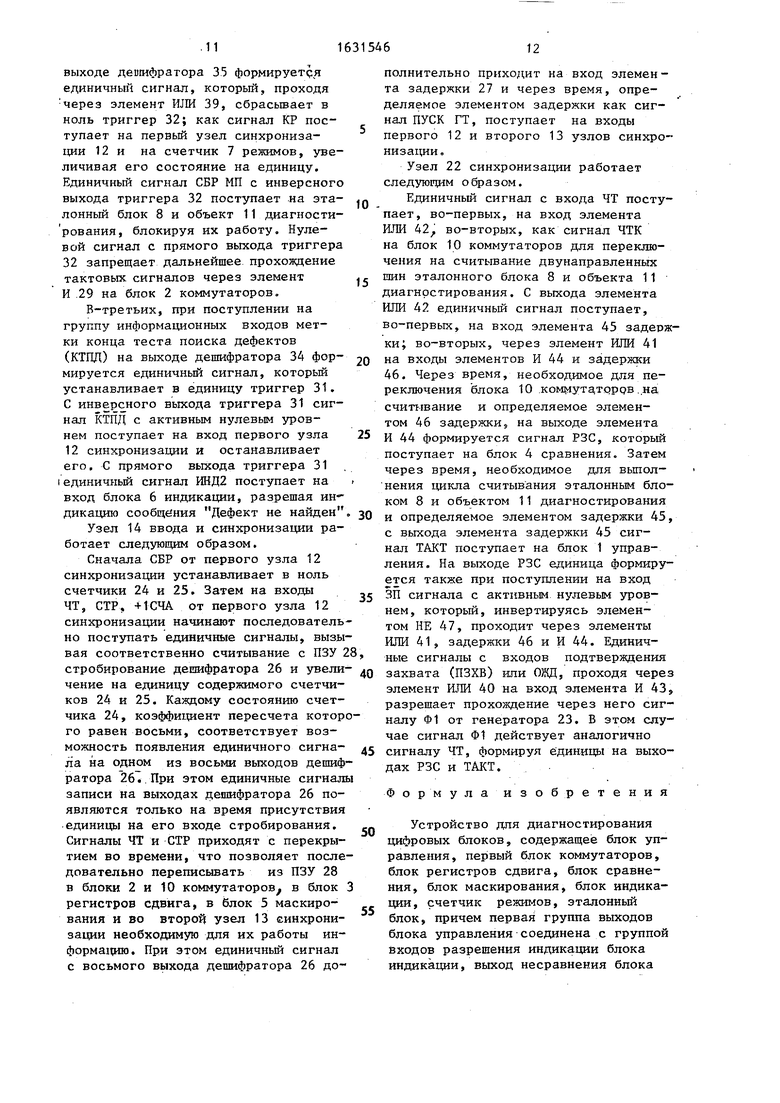

Устройство для диагностирования цифровых блоков содержит блок 1 управления, первый блок 2 коммутаторов блок 3 регистров сдвига, блок 4 сравнения, блок 5 маскирования, блок 6 индикации, счетчик 7 режимов, эта лонный блок 8, блок 9 задания режима, второй блок коммутаторов 10 и объект 11 диагностирования.

Блок 1 управления состоит из узлов 12 и 13 синхронизации, узла 14 ввода и синхронизации.

Второй блок 10 коммутаторов выполнен на регистрах 15 и 16 и коммутаторах 17.

Коммутатор 17 образуют элемент И 18, элемент ИЛИ 19 и трехстабиль- ные элементы 20 и 21.

Блок 9 задания режима содержит узел 22 синхронизации и генератор 23 тактов.

Узел 14 ввода и синхронизации состоит из счетчиков 24 и 25, дешифратора 26, элемента 27 задержки и блок 28 памяти.

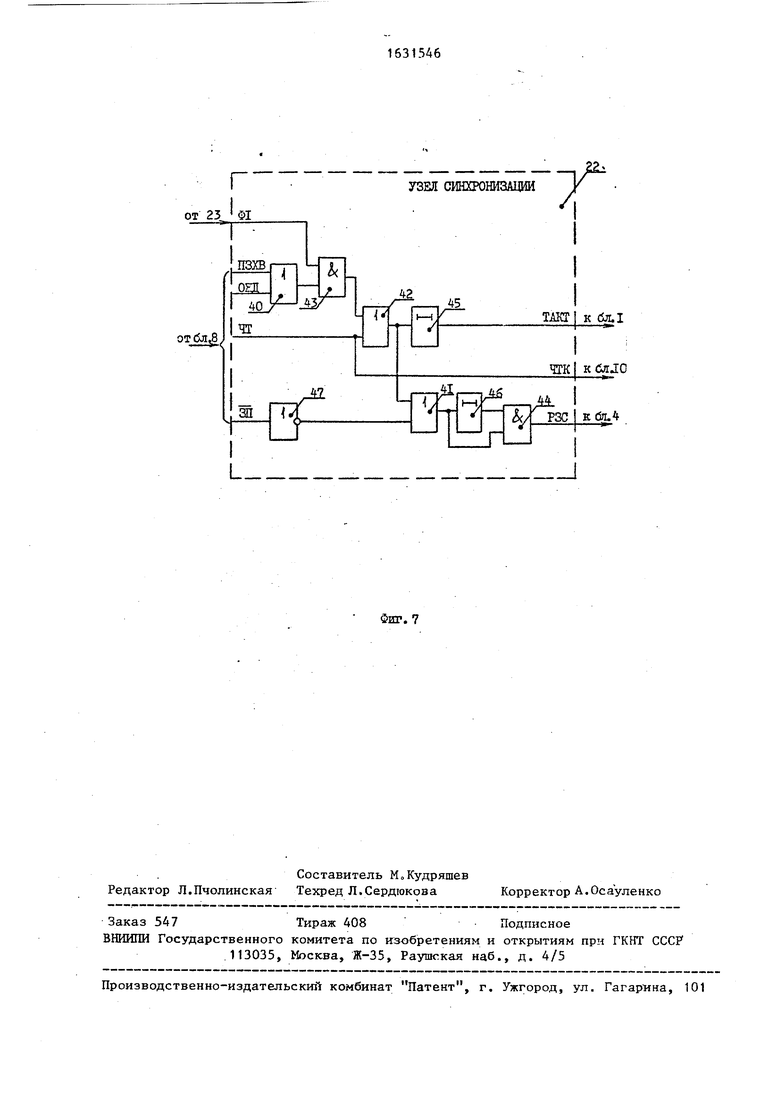

Узел 13 синхронизации содержит элемент И 29, триггеры 30 - 32, счетчик 33, дешифраторы 34 и 35, делители 36-38 частоты и элемент ИЛИ 39. Узел 22 синхронизации образуют элементы ИЛИ 40-42 элементы И 43 и 44, элементы 45 и 46 задержки и элементе НЕ 47.

Устройство для диагностирования цифровых блоков работает следующим образом.

0

5

0

5

0

5

0

5

0

5

По команде с блока 1 управления устанавливается в исходное состояние счетчик 7 режимов. Тактовые импульсы от блока задания режима постоянно поступают на эталонный блок 8 и объект 11 диагностирования. Поэтому в начальном состоянии блок 1 управления блокирует работу эталонного блока 8 и объекта 11 диагностирования путем подачи долговременного сигнала начальной установки. Затем по командам с блока 1 управления из блока 28 в блоки 2 и 10 коммутаторов переписываются коммутационные тесты. Блок 2 коммутаторов в соответствии с коммутационными тестами задает конфигурацию обратных связей, разрядность регистров сдвига, направление и частоту сдвига информации. Блок 10 коммутаторов в соответствии с коммутационными тестами осуществляет разделение контактов эталонного блока 8 и объекта 11 диагностирования на входные, выходные и двунаправленные. Затем из блока 28 в блок 3 регистров сдвига переписывается начальное сое тояние, в блок 5 маскирования - код маскирования, в счетчик циклов блока 1 управления - количество циклов диагностирования. Определенное сочетание констант, т.е. коммутационных тестов, начального состояния, кода маскирования, количества циклов, задает тот или иной режим диагностирования.

После этого блок 1 управления снимает сигнал начальной установки, блокирующий работу эталонного блока 8 и объекта 11 диагностирования. Будучи установлены в начальное состояние, эталонный блок 8 и объект 11 диагностирования начинают работу с выполнения цикла считывания. При этом эталонный блок 8 выдает на блок 9 задания режима сигнал считывания, по которому блок 9 задания режима последовательно формирует две команды. Команда разреиения считывания подается в блок 10 коммутаторов для переключения на считывание двунаправленных шин эталонного блока 8 и объекта 11 ди- агночстирования. Команда разрешения сравнения подается на блок 4 сравнения. Сравнение информации, вводимой в эталонный блок 8 и объект 11 диагностирования, позволяет выявить дефекты входных цепей объекта 11 диагностирования. Через время, необходимое для осуществления цикла считывания, блок 9 задания режима вырабатывает тактовый сигнал для блока 1 управления. Тактовые сигналы от блока 9 задания режима служат основой для формирования в блоке 1 управления набора тактовых сигналов кратных частот, которые поступают в блок 3 регистров сдвига через блок 2 коммутато- ров. По тактовым сигналам в блоке 3 регистров сдвига формируются тестовые воздействия, поступающие на входы эталонного блока 8 и объекта 11

налов,во-вторых, блок 1 управления блокирует работу эталонного блока 8 и объекта 11 диагностирования. Затем содержимое счетчика 7 режимов увели-( чивается на единицу, после чего производится запись констант, определяющих следующий режим диагностирования .

Если при попытке считать коммутационный тест с блока 28 блока 1 управления поступает метка конца теста поиска дефектов, то работа устройства прекращается, а от блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностирования цифровых блоков | 1987 |

|

SU1548789A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Устройство для диагностирования цифровых узлов | 1986 |

|

SU1520517A1 |

| Устройство для диагностирования группы из @ логических узлов | 1985 |

|

SU1390611A1 |

| Устройство для диагностирования группы логических узлов | 1987 |

|

SU1520520A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

Изобретение относится к автоматике и вычислительной технике и мо- кет быть использовано для контроля работоспособности и поиска дефектов цифровых узлов и блоков. Цель изобретения - расширение области применения за счет возможности диагностирования цифровых блоков с двунаправленными входами - выходами. Устройство содержит блок 1 управления, два блока коммутаторов 2,10, блок регистров сдвига 3, блок сравнения 4, блок маскирования 5, блок инднкаипи 6, счетчик режимов 7, эталонный блок 8, блок задания режима 9. 7 нл.

диагностирования через блок 10 комму- 15 управления на блок 6 индикации

таторов. При этом в блоке 5 маскирования на основании анализа содержимого счетчика циклов блока 1 управления и кода маскирования, вырабатываются сигналы запрета считывания, которые 20 поступают на блок 3 регистров сдвига и предотвращают поступление на входы эталонного блока 8 и объекта 11 диагностирования запрещенных комбинаций .25

Вывод ответных реакций из эталонного блока 8 и объекта 11 диагностирования осуществляется во время цикла записи. В этом случае эталонный блок 8 выдает на блок 9 задания 30 режима сигнал записи, по которому формируема команда разрешения сравнения для блока 4 сравнения. По команде разрешения сравнения в блоке 4 сравнения производится сравнение ответных реакций эталонного блока 8 и объекта 11 диагностирования и в случае их различия вырабатывается сигнал несравнения, который поступает в блок.1 управления. В случае получения сигнала несравнения блок 1 управления останавливает работу устройства и вырабатывает сигнал на блок 6 индикации,разрешающий индикацию содержимого счетчика циклов д$ блока 1 управления и счетчика 7 режимов. При отсутствии сигнала несравнения работа устройства продолжается. При этом количество подаваемых на объект 11 диагностирования и эта- 50 лонный блок 8 тестовых воздействий определяется содержимым счетчика циклов блока 1 управления. После подачи заданного количества тестовых воздействий осуществляется переход к $5 следующему режиму диагностирования. При этом, во-первых, прекращается поступление с блока 1 управления на блок 3 регистров сдвига тактовых сиг35

40

поступает сигнал, разрешающий инд кацию сообщения Дефект не найден

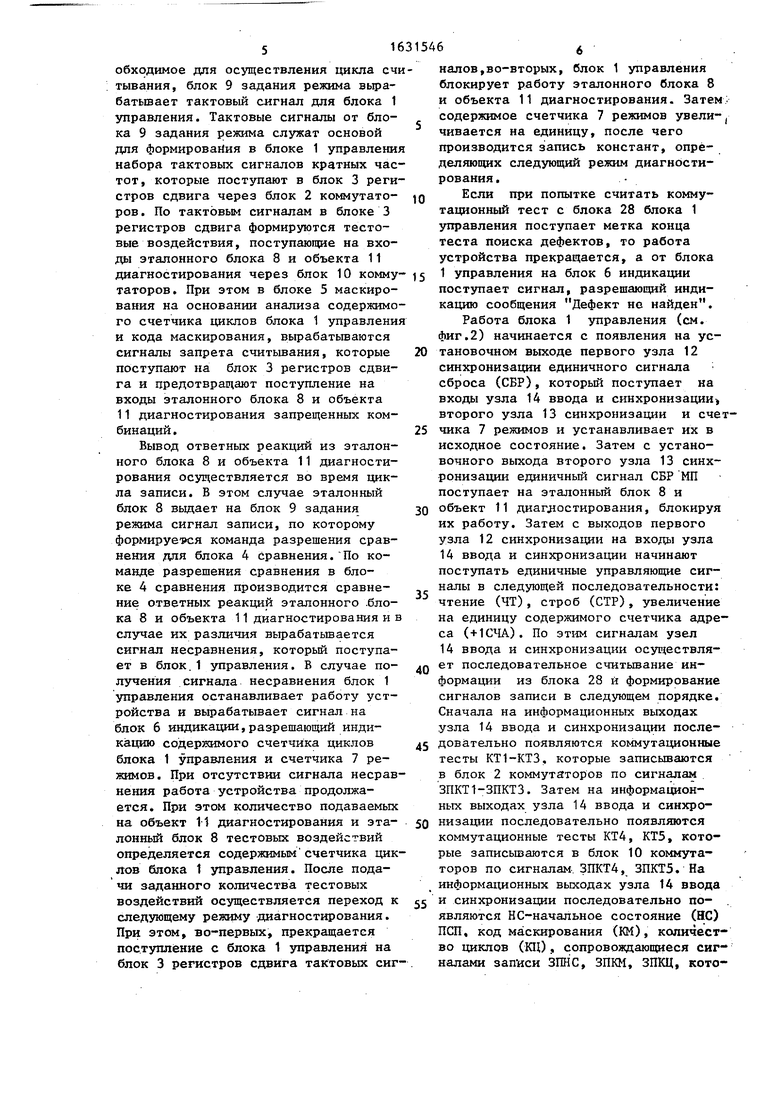

Работа блока 1 управления (см фиг.2) начинается с появления на тановочном выходе первого узла 12 синхронизации единичного сигнала сброса (СВР), который поступает входы узла 14 ввода и синхронизац второго узла 13 синхронизации и чика 7 режимов и устанавливает их исходное состояние. Затем с устан вочного выхода второго узла 13 си ронизации единичный сигнал СВР МП поступает на эталонный блок 8 и объект 11 диагностирования, блоки их работу. Затем с выходов первог узла 12 синхронизации на входы уз 14 ввода и синхронизации начинают поступать единичные управляющие с налы в следующей последовательнос чтение (ЧТ), строб (СТР), увеличе на единицу содержимого счетчика а са (+1СЧА). По этим сигналам узел 14 ввода и синхронизации осуществ ет последовательное считывание ин формации из блока 28 и формирова сигналов записи в следующем поряд Сначала на информационных выходах узла 14 ввода и синхронизации пос довательно появляются коммутацион тесты КТ1-КТЗ, которые записывают в блок 2 коммутаторов по сигналам ЗПКТ1-ЗПКТЗ. Затем на информацион ных выходах узла 14 ввода и синхр низации последовательно появляютс коммутационные тесты КТ4, КТ5, ко рые записываются в блок 10 коммут торов по сигналам ЗПКТ4, ЗПКТ5. Н информационных выходах узла 14 вв и синхронизации последовательно п являются НС-начальное состояние ( ПСП, код маскирования (КМ), колич во циклов (КЦ), сопровождающиеся налами записи ЗПНС, ЗПКМ, ЗПКЦ, к

0 5

0 $ 0 5

5

0

поступает сигнал, разрешающий индикацию сообщения Дефект не найден.

Работа блока 1 управления (см. фиг.2) начинается с появления на установочном выходе первого узла 12 синхронизации единичного сигнала сброса (СВР), который поступает на входы узла 14 ввода и синхронизации второго узла 13 синхронизации и счетчика 7 режимов и устанавливает их в исходное состояние. Затем с установочного выхода второго узла 13 синхронизации единичный сигнал СВР МП поступает на эталонный блок 8 и объект 11 диагностирования, блокируя их работу. Затем с выходов первого узла 12 синхронизации на входы узла 14 ввода и синхронизации начинают поступать единичные управляющие сигналы в следующей последовательности: чтение (ЧТ), строб (СТР), увеличение на единицу содержимого счетчика адреса (+1СЧА). По этим сигналам узел 14 ввода и синхронизации осуществляет последовательное считывание информации из блока 28 и формирование сигналов записи в следующем порядке. Сначала на информационных выходах узла 14 ввода и синхронизации последовательно появляются коммутационные тесты КТ1-КТЗ, которые записываются в блок 2 коммутаторов по сигналам ЗПКТ1-ЗПКТЗ. Затем на информационных выходах узла 14 ввода и синхронизации последовательно появляются коммутационные тесты КТ4, КТ5, которые записываются в блок 10 коммутаторов по сигналам ЗПКТ4, ЗПКТ5. На информационных выходах узла 14 ввода и синхронизации последовательно появляются НС-начальное состояние (НС) ПСП, код маскирования (КМ), количество циклов (КЦ), сопровождающиеся сигналами записи ЗПНС, ЗПКМ, ЗПКЦ, кото

рые поступают на блок 3 регистров сдвига, блок 5 маскирования и второй узел 13 синхронизации. Затем о выхода узла 14 ввода и синхронизации на входы первого 12 и второго 13 узлов синхронизации поступает единичный сигнал пуска генератора (ПУСК ГТ) тактовых сигналов, по которому первый узел 12 синхрониазции прекращает формирование управляющих сигналов ЧТ, СТР, +1СЧА, а на выходе СВР МП второго узла 13 синхронизации снимается единичный сигнал, блокирующий работу эталонного блока 8 и объекта 11 диагностирования, Затем на вход ТАКТ блока 1 управления от блока 9 задания режима начинают поступать тактовые импульсы, на основе которых второй узел 13 синхронизации формирует набор тактовых сигналов с частотами, необходимыми для сдвига информации в блоке 3 регистров сдвига. Второй узел 13 синхронизации, сформировав заданное число тактовых сигналов, определяемое КЦ, прекращает работу и выставляет единичные сигналы на выходах конца режима (КР) и СВР МП. Сигнал КР поступает, во- первых, на счетчик 7 режимов, увеличивая его содержимое на единицу; во-вторых, на первый узел 12 синхронизации, инициируя формирование сигналов ЧТ, СТР, +1СЧА, т.е. работа блока 1 управления повторяется.

Работа блока 1 управления прекращается в двух случаях.

вход второго узла 13 синхронизации во время формирования тактовых сиг-ч налов. При этом, во-первых, на выходах второго узла 13 синхронизации прекращается формирование тактовых сигналов; во-вторых, на выходах разрешения индикации (ИНД1) и СВР МП появляются единичные сигналы. Сигнал ИНД1, поступая на вход блока 6 индикации, разрешает индикацию номера цикла (НЦ), присутствующего на группе выходов второго узла 13 синхронизации, а также содержимого счетчика 7 режимов.

,КТЦД появляется на информационных вы ходах узла 14 ввода и синхронизации при попытке считывания очередного КТ1 и распознается вторым узлом 13

синхронизации При этом, во-первых, на выходе КТПД второго узла 13 синхрнизации появляется сигнал с активным нулевым уровнем, который поступает на вход первого узла 12 синхронизаци и останавливает его работу, во-вторых, с выхода ИНД2 единичный сигнал поступает на блок б индикации и раз« решает индикацию сообщения Дефект не найден.

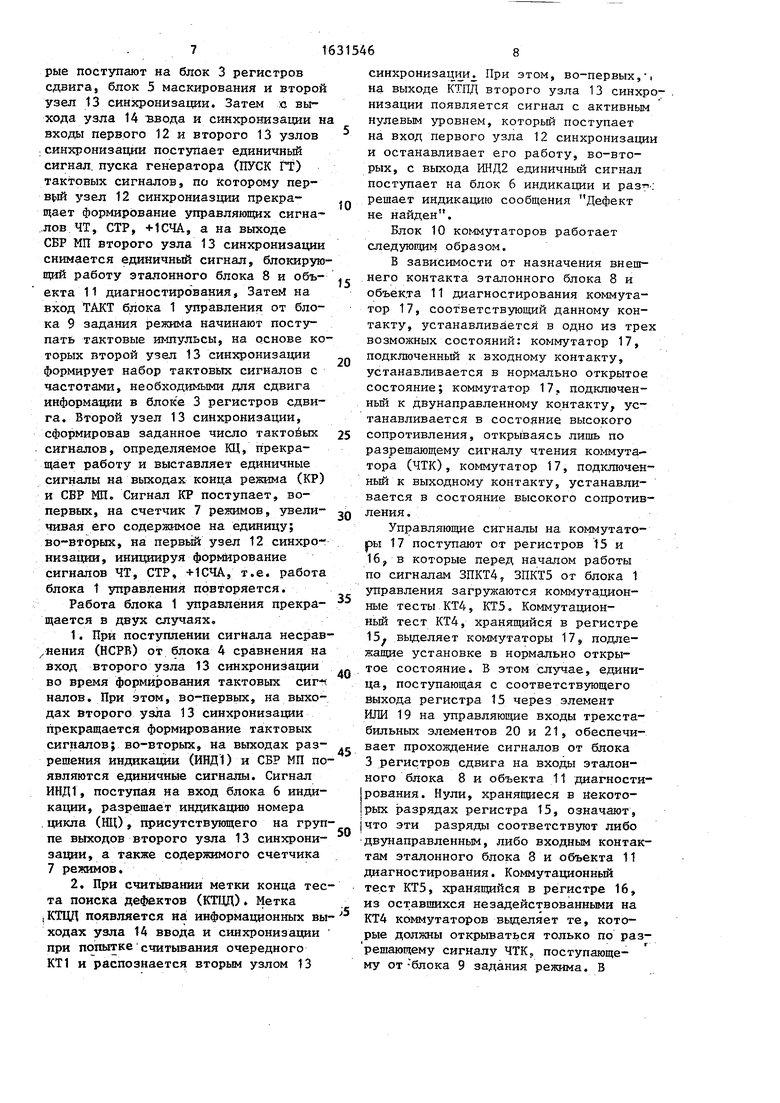

Блок 10 коммутаторов работает следующим образом.

В зависимости от назначения внешнего контакта эталонного блока 8 и объекта 11 диагностирования коммутатор 17, соответствующий данному контакту, устанавливается в одно из тре возможных состояний: коммутатор 17, подключенный к входному контакту, устанавливается в нормально открытое состояние; коммутатор 17. подключенный к двунаправленному контакту, устанавливается в состояние высокого сопротивления, открываясь лишь по разрешающему сигналу чтения коммутатора (ЧТК), коммутатор 17, подключенный к выходному контакту, устанавливается в состояние высокого сопротивления .

Управляющие сигналы на коммутаторы 17 поступают от регистров 15 и 16, в которые перед началом работы по сигналам ЗПКТ4, ЗПКТ5 от блока 1 управления загружаются коммутационные тесты КТ4, КТ5. Коммутационный тест КТ4, хранящийся в регистре 15 выделяет коммутаторы 17 9 подлежащие установке в нормально открытое состояние. В этом случае, единица, поступающая с соответствующего выхода регистра 15 через элемент ИЛИ 19 на управляющие входы трехста- бильных элементов 20 и 21, обеспечивает прохождение сигналов от блока 3 регистров сдвига на входы эталонного блока 8 и объекта 11 диагностирования. Нули, хранящиеся в некоторых разрядах регистра 15, означают, что эти разряды соответствуют либо двунаправленным, либо входным контактам эталонного блока 8 и объекта 11 диагностирования. Коммутационный тест КТ5, хранящийся в регистре 16, из оставшихся незадействованными на КТ4 коммутаторов выделяет те, которые должны открываться только по разрешающему сигналу ЧТК, поступающему от- блока 9 задания режима. В

этом случае единица поступает с соответствующего выхода регистра 16 на вход элемента И 18, разрешая прохождение через него единичному сигналу ЧТК. Сигнал ЧТК, поступая через элементы И 18, ИЛИ 19 на управяющие входы трехстабильных элементов

20 и 21, разрешает считывание эталонному блоку 8 и объекту 11 диагностиро вания информации из блока 3 регистров сдвига. Нули, хранящиеся в оставшихся разрядах регистра 16, означают, что эти разряды соответствуют выходным контактам.

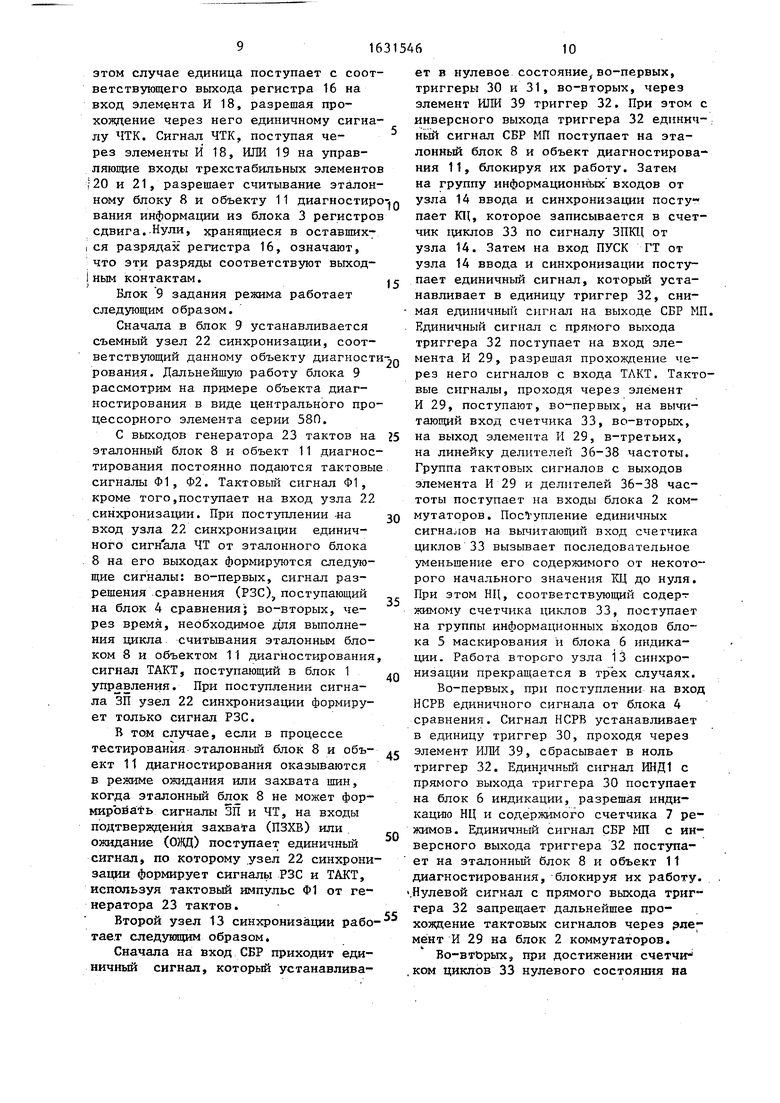

Блок 9 задания режима работает следующим образом.

Сначала в блок 9 устанавливается съемный узел 22 синхронизации, соответствующий данному объекту диагности рования. Дальнейшую работу блока 9 рассмотрим на примере объекта диагностирования в виде центрального процессорного элемента серии 58П.

С выходов генератора 23 тактов на эталонный блок 8 и объект 11 диагностирования постоянно подаются тактовые сигналы Ф1, Ф2. Тактовый сигнал Ф1, кроме того,поступает на вход узла 22 синхронизации. При поступлении на вход узла 22 синхронизации единичного сигнала ЧТ от эталонного блока 8 на его выходах формируются следующие сигналы: во-первых, сигнал разрешения сравнения (РЗС) поступающий на блок 4 сравнения; во-вторых, через время, необходимое для выполнения цикла считывания эталонным блоком 8 и объектом 1i диагностирования, сигнал ТАКТ, поступающий в блок 1 управления. При поступлении сигнала ЗП узел 22 синхронизации формирует только сигнал РЗС.

В том случае, если в процессе тестирования эталонный блок 8 и объект 11 диагностирования оказываются в режиме ожидания или захвата шин, когда эталонный блок 8 не может форировать сигналы ЗП и ЧТ, на входы подтверждения захвата (ПЗХВ) или ожидание (ОВД) поступает единичный сигнал, по которому узел 22 синхронизации формирует сигналы РЗС и ТАКТ, используя тактовый импульс Ф1 от ге- нератора 23 тактов.

Второй узел 13 синхронизации работает следующим образом.

Сначала на вход СВР приходит единичный сигнал, который устаиавлйва0

5

0

5

0

5

0

5

0

5

ет в нулевое состояние, во-первых, триггеры 30 и 31, во-вторых, через элемент ИЛИ 39 триггер 32. При этом с инверсного выхода триггера 32 единичный сигнал СВР МП поступает на эталонный блок 8 и объект диагностирования 11, блокируя их работу. Затем на группу информационных входов от узла 14 ввода и синхронизации посту14 пает КЦ, которое записывается в счетчик циклов 33 по сигналу ЗПКЦ от узла 14. Затем на вход ПУСК ГТ от узла 14 ввода и синхронизации поступает единичный сигнал, который устанавливает в единицу триггер 32, сни мая единичный сигнал на выходе СВР МП. Единичный сигнал с прямого выхода триггера 32 поступает на вход элемента И 29, разрешая прохождение через него сигналов с входа ТАКТ. Тактовые сигналы, проходя через элемент И 29, поступают, во-первых, на вычитающий вход счетчика 33, во-вторых, на выход элемента И 29, в-третьих, на линейку делителей 36-38 частоты. Группа тактовых сигналов с выходов элемента И 29 и делителей 36-38 частоты поступает на входы блока 2 коммутаторов. Поступление единичных сигналов на вычитающий вход счетчика циклов 33 вызывает последовательное уменьшение его содержимого от некоторого начального значения КЦ до нуля. При этом НЦ, соответствующий содерт жимому счетчика циклов 33, поступает на группы информационных входов блока 5 маскирования и блока 6 индикации. Работа второго узла 13 синхронизации прекращается в трёх случаях.

Во-первых, при поступлении на вход НСРВ единичного сигнала от блока 4 сравнения. Сигнал НСРВ устанавливает в единицу триггер 30, проходя через элемент ИЛИ 39, сбрасывает в ноль триггер 32. Единичный сигнал ИНД1 с прямого выхода триггера 30 поступает на блок 6 индикации, разрешая индикацию НЦ и содержимого счетчика 7 режимов. Единичный сигнал СВР МП с инверсного выхода триггера 32 поступает на эталонный блок 8 и объект 11 диагностирования, блокируя их работу.

Нулевой сигнал с прямого выхода триггера 32 запрещает дальнейшее прохождение тактовых сигналов через элемент И 29 на блок 2 коммутаторов. Во-втЬрых, при достижении счетчи.ком циклов 33 нулевого состояния на

выходе дешифратора 35 формируется единичный сигнал, который, проходя через элемент ИЛИ 39, сбрасывает в ноль триггер 32; как сигнал КР поступает на первый узел синхронизации 12 и на счетчик 7 режимов, увеличивая его состояние на единицу. Единичный сигнал СВР МП с инверсного выхода триггера 32 поступает на эта- лонный блок 8 и объект 11 диагностирования, блокируя их работу. Нулевой сигнал с прямого выхода триггера 32 запрещает дальнейшее прохождение тактовых сигналов через элемент, И 29 на блок 2 коммутаторов.

В-третьих, при поступлении на группу информационных входов метки конца теста поиска дефектов (КТПД) на выходе дешифратора 34 фор- мируется единичный сигнал, который устанавливает в единицу триггер 31. С инверсного выхода триггера 31 сигнал КТПД с активным нулевым уровнем поступает на вход первого узла 12 синхронизации и останавливает его. С прямого выхода триггера 31 iединичный сигнал ИНД2 поступает на вход блока 6 индикации, разрешая индикацию сообщения Дефект не найден

Узел 14 ввода и синхронизации работает следующим образом.

Сначала СВР от первого узла 12 синхронизации устанавливает в ноль счетчики 24 и 25. Затем на входы ЧТ, СТР. + 1СЧА от первого узла 12 синхронизации начинают последовательно поступать единичные сигналы, вызывая соответственно считывание с ПЗУ 2 стробирование дешифратора 26 и увели чение на единицу содержимого счетчиков 24 и 25. Каждому состоянию счетчика 24, коэффициент пересчета которго равен восьми, соответствует возможность появления единичного сигна- ла на одном из восьми выходов дешифратора 26. При этом единичные сигнал записи на выходах дешифратора 26 появляются только на время присутствия единицы на его входе стробирования. Сигналы ЧТ и СТР приходят с перекрытием во времени, что позволяет последовательно переписывать из ПЗУ 28 в блоки 2 и 10 коммутаторов, в блок регистров сдвига, в блок 5 маскирования и во второй узел 13 синхронизации необходимую для их работы информацию. При этом единичный сигнал с восьмого выхода дешифратора 26 до

c

Q 5 0

д 5 Q

5

5

полнительно приходит на вход элемен - та задержки 27 и через время, определяемое элементом задержки как сигнал ПУСК ГТ, поступает на входы первого 12 и второго 13 узлов синхронизации.

Узел 22 синхронизации работает следующим образом.

Единичный сигнал с входа ЧТ поступает, во-первых, на вход элемента ИЛИ 42, во-вторых, как сигнал ЧТК на блок 10 коммутаторов для переключения на считывание двунаправленных шин эталонного блока 8 и объекта 11 диагностирования. С выхода элемента ИЛИ 42 единичный сигнал поступает, во-первых, на вход элемента 45 задержки; во-вторых, через элемент ИЛИ 41 на входы элементов И 44 и задержки 46. Через время, необходимое для переключения блока 10 коммутаторов на считывание и определяемое элементом 46 задержкиs на выходе элемента И 44 формируется сигнал РЗС, который поступает на блок 4 сравнения. Затем через время, необходимое для выполнения цикла считывания эталонным блоком 8 и объектом 11 диагностирования и определяемое элементом задержки 45, с выхода элемента задержки 45 сигнал ТАКТ поступает на блок 1 управления. На выходе РЗС единица формируется также при поступлении на вход ЗП сигнала с активным нулевым уровнем, который, инвертируясь элементом НЕ 47, проходит через элементы ИЛИ 41, задержки 46 и И 44. Единичные сигналы с входов подтверждения захвата (ПЗХВ) или ОЖД, проходя через элемент ИЛИ 40 на вход элемента И 43, разрешает прохождение через него сигналу Ф1 от генератора 23. В этом случае сигнал Ф1 действует аналогично сигналу ЧТ, формируя единицы на выходах РЗС и ТАКТ.

Формула изобретения

Устройство для диагностирования цифровых блоков, содержащее блок управления, первый блок коммутаторов, блок регистров сдвига, блок сравнения, блок маскирования, блок индикации, счетчик режимов, эталонный блок, причем первая группа выходов блока управления соединена с группой входов разрешения индикации блока индикации, выход несравнения блока

сравнения соединен с входом ошибки блока управления, вторая группа выходов которого соединена с группой входов маски блока маскирования, труп- вой входов начального состояния блока регистров сдвига и группой управляющих входов первого блока коммутаторов, группа входов синхронизации которого соединена с третьей группой выходов блока управления, четвертая группа выходов которого соединена с группой входов синхронизации счетчика режимов, группа информационных выходов которого соединена с первой группой информационных входов блока индикации, вторая группа информационных входов которого соединена с пятой группой выходов блока управления и группой информационных входов блока маскирования, вход разрешения записи которого соединен с первым выходом блока управления, второй выход которого соединен с входом разрешения записи блока регистров сдвига, вход блокировки считывания которого соединен с выходом блока маскирования, группа разрядных входов-выходов блока регистров сдвига соединена с группой информационных в ходов- выходов первого блока коммутаторов, группа выходов которого соединена с группой входов синхронизации блока регистров сдвига, причем блок управления содержит два узла синхронизации, узел ввода и синхронизации, выход начальной установки первого узла синхронизации соединен с первым выходом четвертой группы выходов блока управления, входом начальной установки второго узла синхронизации и входом начальной установки узла ввода и синхронизации, группа входов синхронизации которого соединена с группой выходов первого узла синхронизации, вход запуска которого соединен с первым выходом узла ввода и синхронизации и входом запуска второго узла синхронизации, первый выход которого соединен с первым входом останова первого узла синхронизации, второй вход останова которого соединен с вторым выходом второго узла синхронизации и вторым выходом четвертой группы выходов блока управления, первая группа выходов которого соединена с первой группой выходов второго узла синхронизации, вторая группа выходов которого соединена с пятой группой

0

0

5

0

5

0

5

0

5

выходов блока управления, первый выход которого соединен с первым выходом узла ввода и синхронизации, второй выход которого является вторым выходом блока управления, вторая группа выходов которого соединена с группой информационных выходов узла ввода и синхронизации и группой входов начального условия второго узла синхронизации, стробирующий вход которого соединен с третьим выходом узла ввода и синхронизации, первая группа выходов которого вместе с третьей группой выходов второго узла синхронизации является третьей группой выходов блока управления, вход ошибки которого соединен с входом останова второго узла синхронизации, вход синхронизации блока управления соединен с входом синхронизации второго узла синхронизации, третий выход которого является установочным выходом блока управления, шестая группа выходов которого соединена с второй группой стробирутощих выходов узла ввода и синхронизации, отличающееся тем, что, с целью расширения области применения за счет возможности диагностирования цифровых блоков с двунаправленными

-входами-выходами, в него введены блок задания режима и второй блок коммутаторов, причем группа информационных выходов блока регистров сдвига соединена с группой информационных входов второго блока коммутаторов, группа управляющих входов которого соединена с второй группой выходов блока управления, установочный выход которого соединен с установочным входом эталонного блока и является установочным выходом устройства для подключения к установочному входу объекта диагностирования, вход разрешения сравнения блока сравнения соединен с первым выходом блока задания режима, второй выход которого соединен с входом синхронизации блока управления, шестая группа выходов которого соединена с группой входов разрешения записи второго блока коммутаторов, вход,разрешения

.чтения которого соединен с гретым выходом блока задания режима, группа входов которого соединена с группой выходов эталонного блока, группа входов синхронизации которого соединена с группой выходов блока задания режима и является группой выходов синхронизации устройства для подключения к группе входов синхронизации объектов диагностирования, первая группа информационных выходов второго блока коммутаторов соединена с группой информационных входов-выходов эталонного блока и первой группой информационных входов блока сравнения, вто

п

1Ј

5

t

I

с:

I

СВР

-

KW

КР

Om5n.ltНСРВ

От 6л. 9

ТАКТ

Фиг. 2

рая группа информационных входов которого соединена с второй группой информационных выходов второго блока коммутаторов и является группой информационных входов-выходов устройства для подключения к группе информационных входов-выходов объекта диагностирования .

/

зпнс

зпкп

зпкт,зпкг5

КТ, НС, №

ЗЛЩ ЖТ2,

жтз

Кбл.2

Г

V

fr, fr/г,

fГ/4, fг/8 ИНД1,ИЩ2

ни,

СВР МП

КР СВР

Ибл.6

КВл.5,6 Квл.8,11

.

. 7

1631546

.:/

БЯОК КОММУТАТОРОВ

-2R12. I

пи ил I

:,I (huff

И

IУЗЕЯ ВВОДА И СИНХРОНИЗАЦИИ У

I

L:.

f

Г

от 23 Ul

L

OTOJtjL

I

УЗЕЛ СИНХРОНИЗАЦИИ

Г

|

| Устройство для контроля и диагностики логических схем | 1981 |

|

SU972516A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для диагностирования цифровых блоков | 1987 |

|

SU1548789A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-02-28—Публикация

1988-07-01—Подача