i

О1

00 4

сл

:

Изобретение относится к вычислительной технике, а именно к устройствам проверки правильности выполнения программ и к устройствам поиска дефектов программ и функциональных узлов микропроцессоров.

Целью изобретения является расширение диагносФических возможностей устройства за счет обеспечения поиска и локализации дефектов в контролируемых узлах процессора и программы.

Работа данного изобретения основывается на следующих положениях. Проверка каждой программы состоит из ряда примеров (идентификаторов). Критерием для выбора примеров может быть, например, следующее: совокупность наборов входных переменных должна обеспечивать прохождение по всем ребрам алгоритма, по которому реализована программа, хотя бы два раза. Используя этот критерий, почти во всех случаях удается обнаружить однократньш дефект функционального, предикатного и константного символов, из которых состоит программа. Работа устройства в режиме проверки основана на сравнении ..времени выполнения программы с заданным промежутком времени и на сравнении результатов выполнения программы с эталонными результатами. Сначала осуществляется анализ времени выполнения программы. Если до истечения заданного промежутка времени на устройство не поступил сигнал об окончании работы программы, то данная ситуация классифицируется как зацикливание. Если фактическое время выполнения программы оказалось меньше расчетного, заданного с учетом определенного допуска, то данная ситуация классифицируется как преждевременное завершение программы. Необходимость допуска объясняется тем, что время выполнения программы зависит от места нахождения микрокоманд, входящих в команду. Например, одна и та же микрокоманда мож.ет находитьс в арифметико-логическом устройстве или в постоянном запоминающем устройстве в зависимости от того, выполнялась она или нет в предьщущей команде. Допуск характеризует эти различия для всей программы. Если фактическое время выполнения программы уложилось в заданный допуск, то

5

0

5

0

5

0

5

0

5

происходит сравнение результатов выполнения программы с эталонными результатами. Если результаты не равны, то данная ситуация классифицируется как дефект в программе. При равенстве результатов делается вывод об отсутствии дефектов в программе.

В режиме поиска дефектов используется то обстоятельство, что каждая команда программы при своем выполнении активизирует .определенные функ- 1диональные узлы (ФУ) микропроцессора. Это позволяет каждой команде поставить в соответствие совокупность активизируемых ФУ. В системе команд микропроцессора содержатся команды записи в соответствии ФУ и команды считывания из ФУ. Первая группа команд относится к устанавливаюш:им, а вторая - транслирующим командам. Сопоставив каждой команде микропроцессора входные, выходные ФУ и функцию преобразования информации, также соотнесенную с ФУ,и вьщелив устанавливающие и транслирующие команды, можно сформировать логически завершенные последовательности команд. Эти последовательности осуществляют передачу информации с преобразованием или без него от входа микропроцессора к выходу и называются подмоделями. Так как вся система команд микропроцессора определяет функционирование управляющего и операционного автоматов, из которых состоит микропроцессор, . то эти подмодели покрывают весь микропроцессор и обеспечивают полноту диагностирования. Подмодели упорядочиваются по включению на основе совокупности активизируемых ФУ. При этом в качестве первого элемента упорядоченной последовательности для теста поиска дефектов (ТПД) берется подмодель с минимальной совокупностью ФУ. Упорядоченная последовательность подмоделей определяет решетчатую модель микропроцессора, описываемого системой команд. Для получения входной тестовой программы подмодели дополняются данными. В качестве данных могут быть использованы специальные входные наборы,созданные предварительно для тестирования соответствующего ФУ, либо псевдослучайная последовательность.

Если для всех наборов подмодели выходные результаты не совпадают с

5t5

эталонными, тестирование прекращается и вьщается сообщение, позволяющее установить на каком элементе решетчатой модели произошла ошибка. В противном случае на следующую подмодель подаются соответствующие тестовые данные и поиск дефектов продолжается. Если тест поиска дефектов прошел до конца без остановки, то индицируется сообщение об отсутствии дефектов.

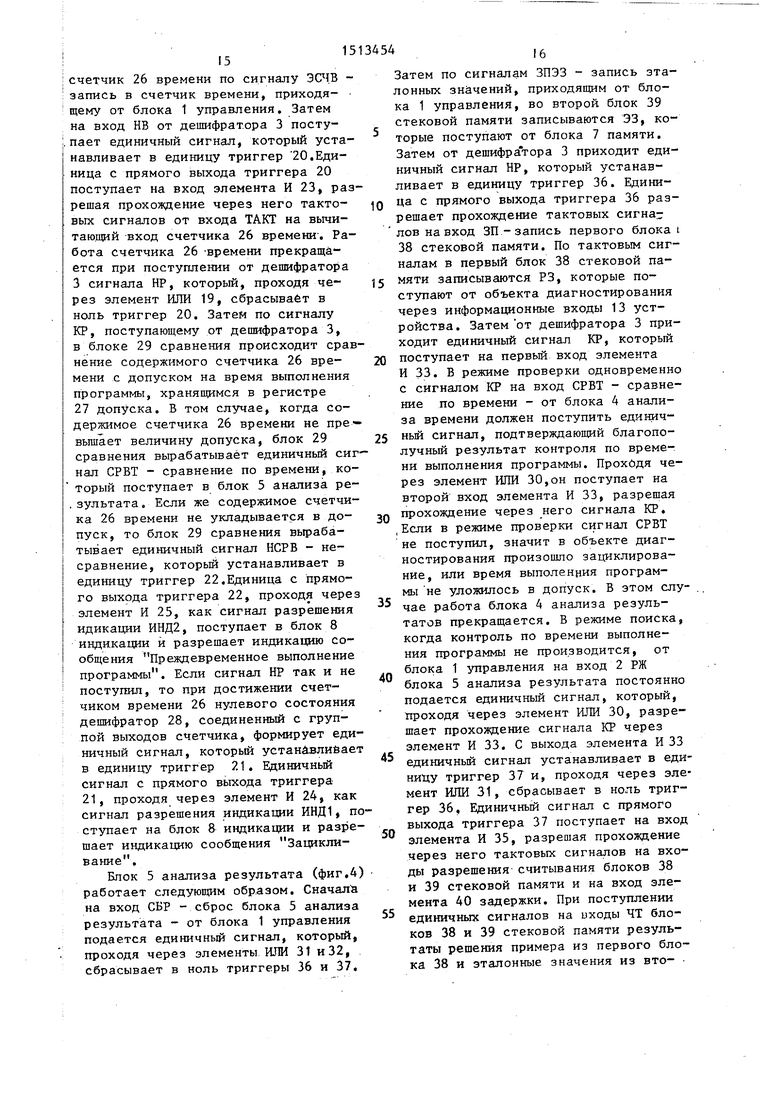

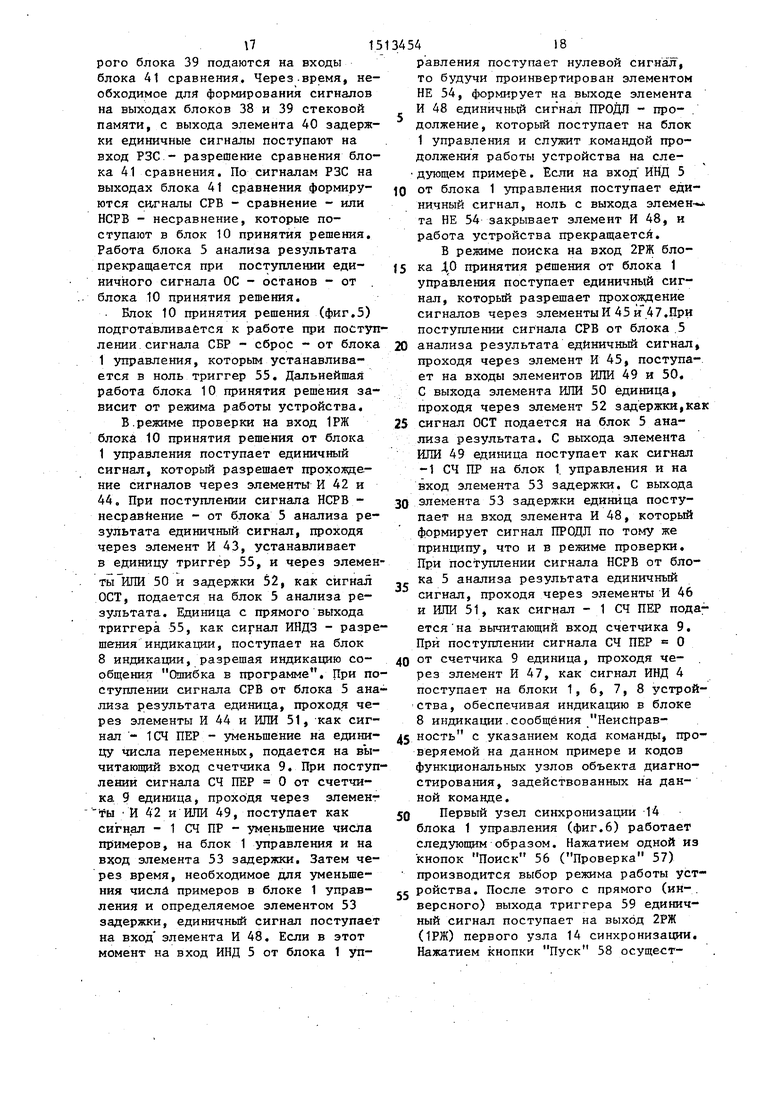

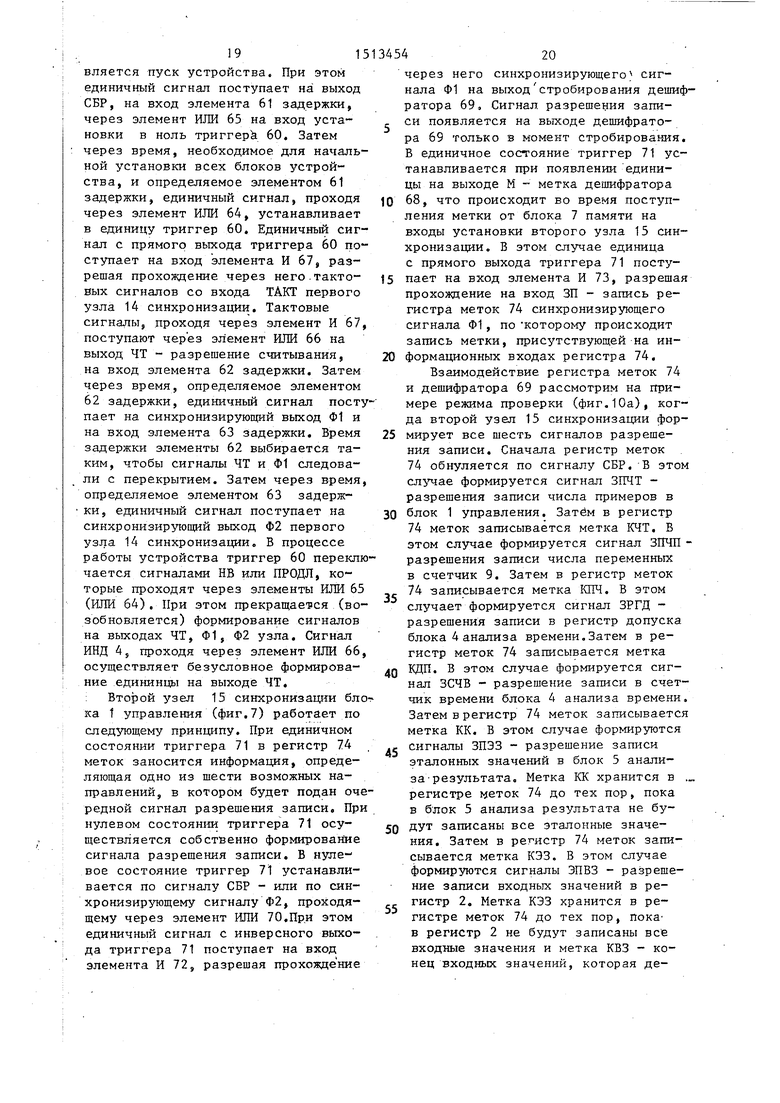

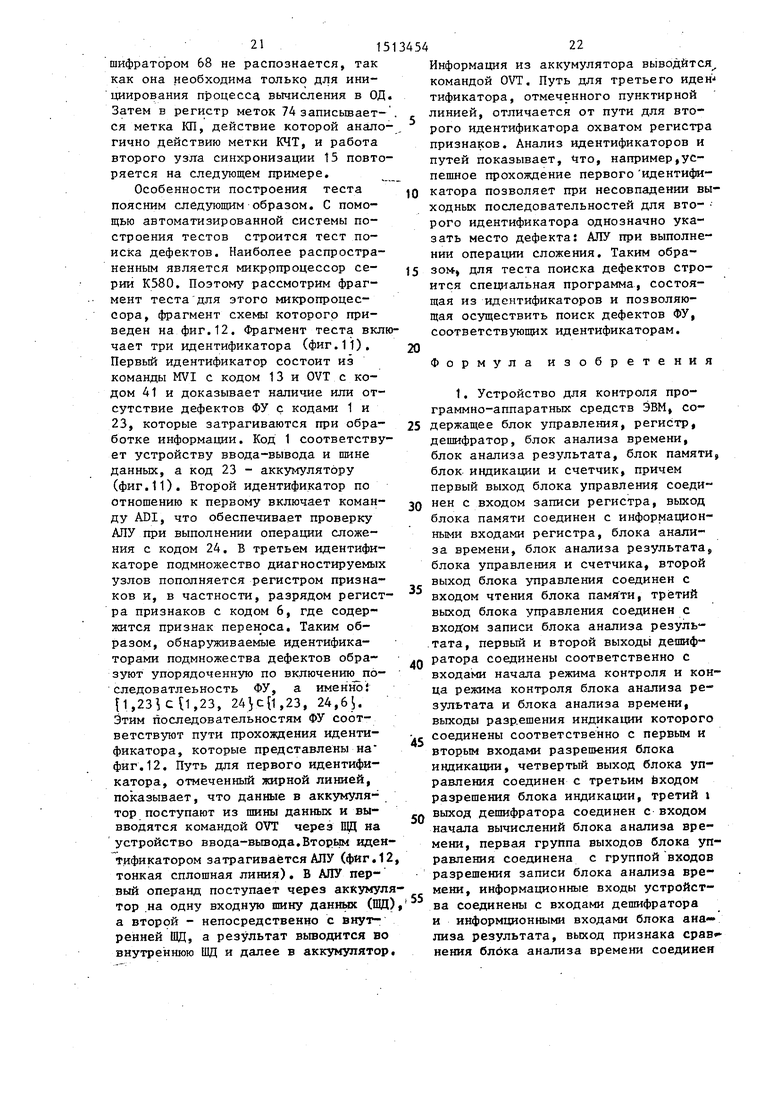

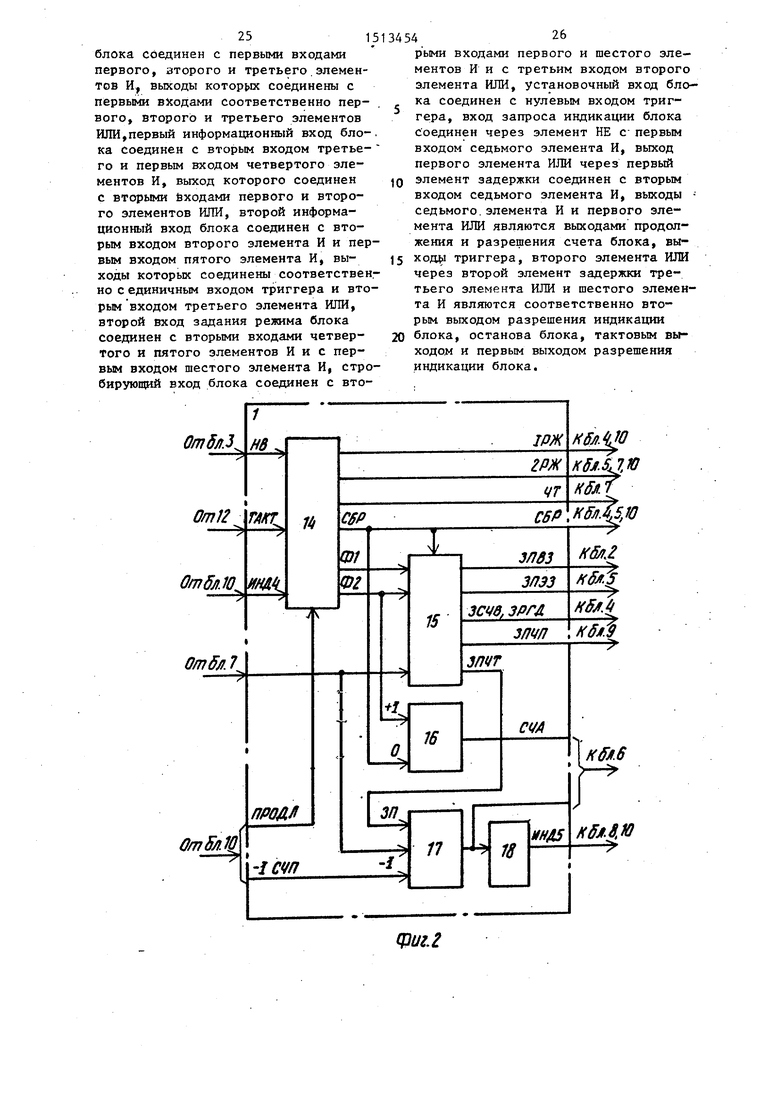

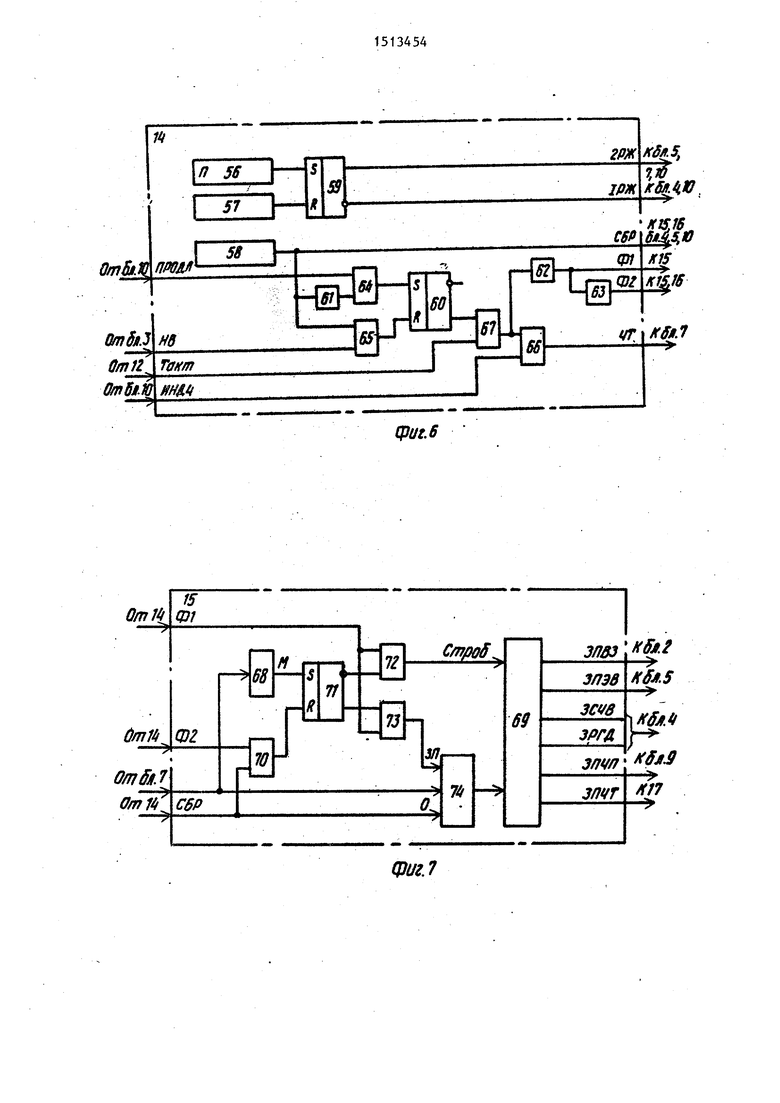

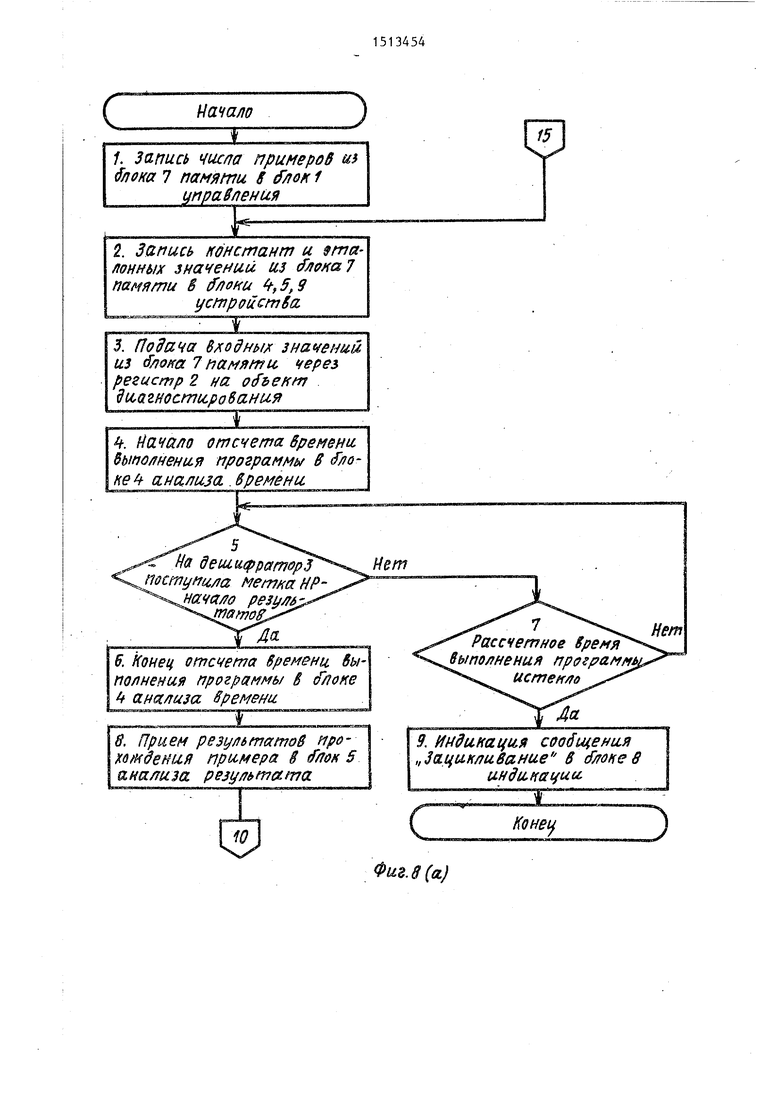

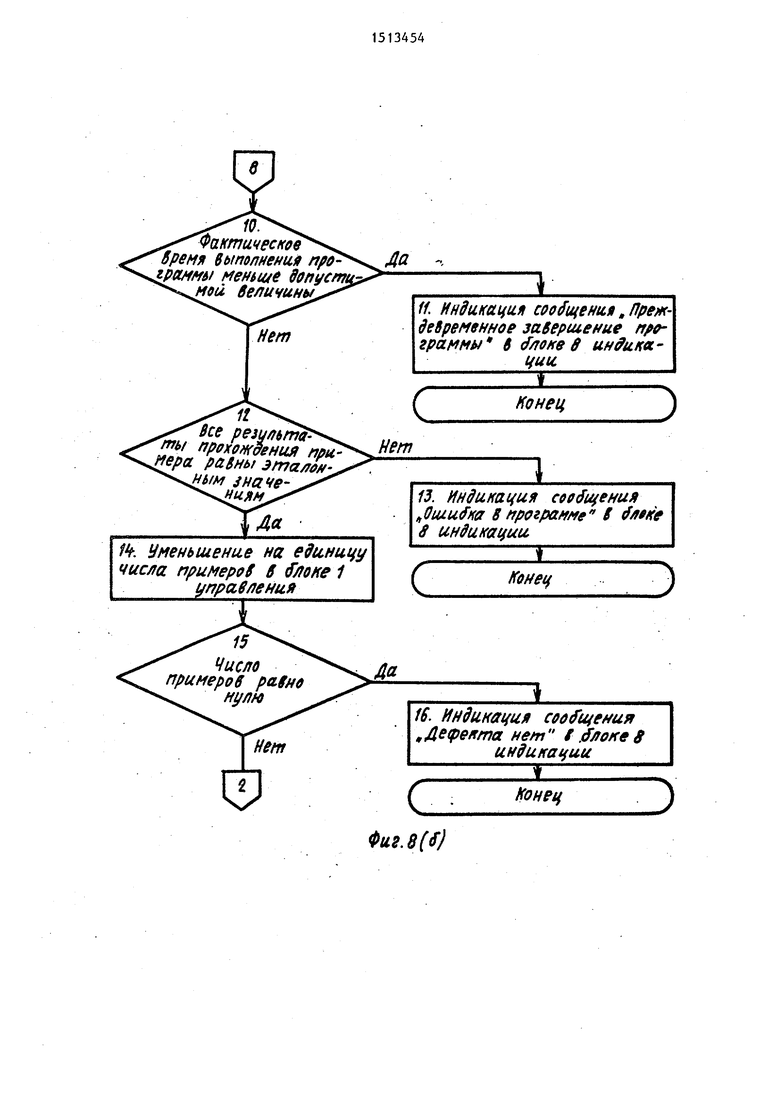

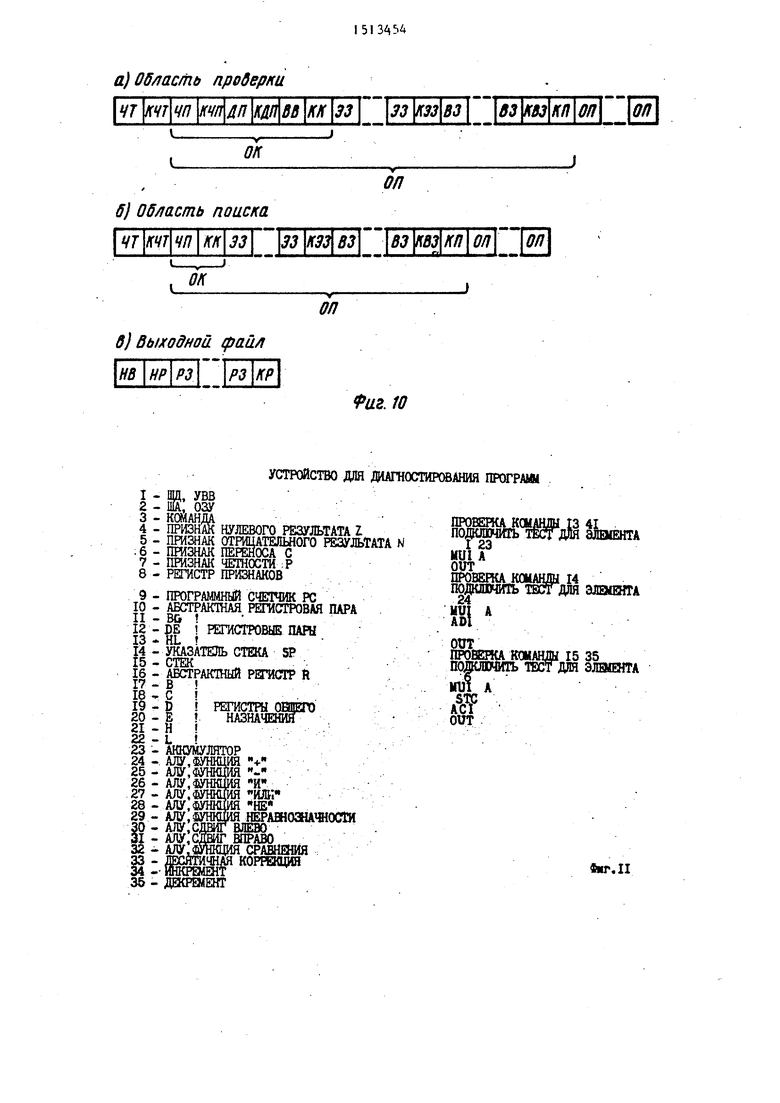

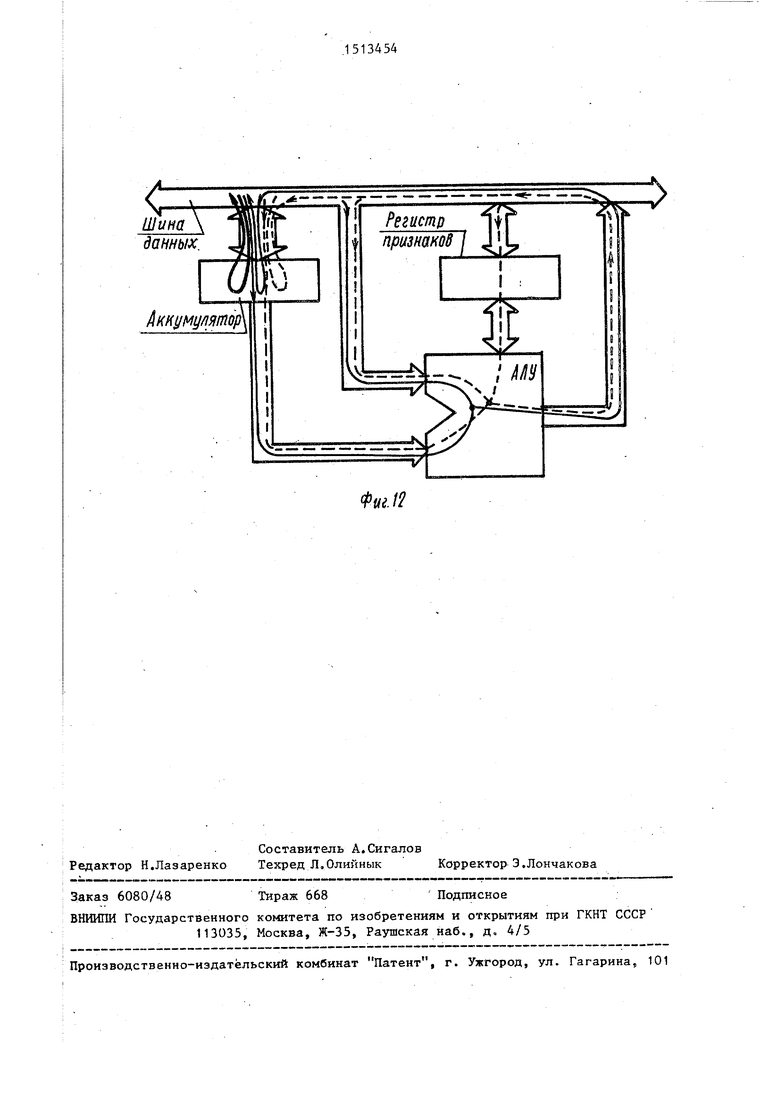

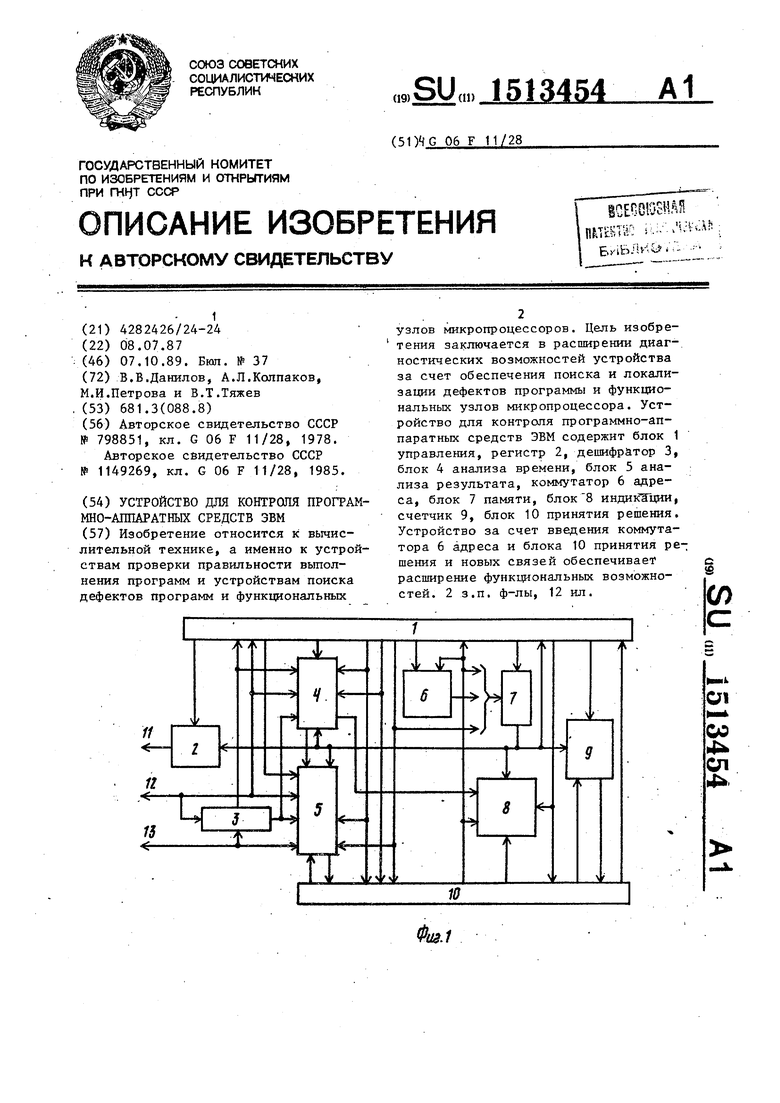

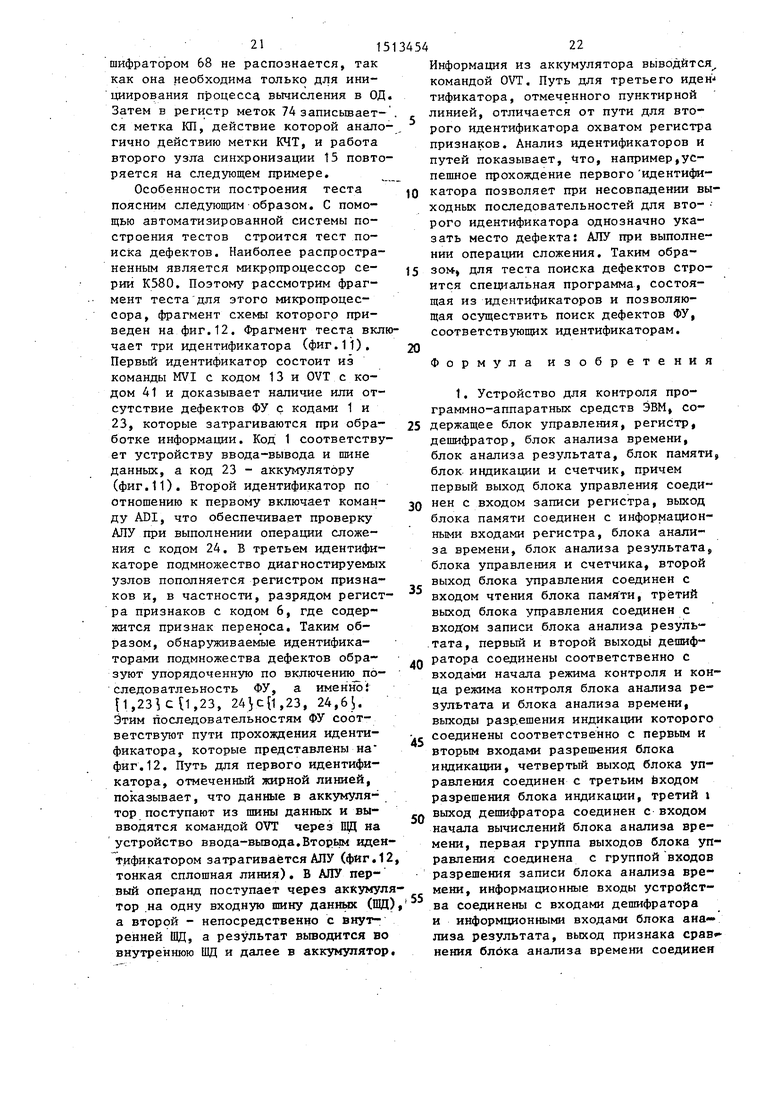

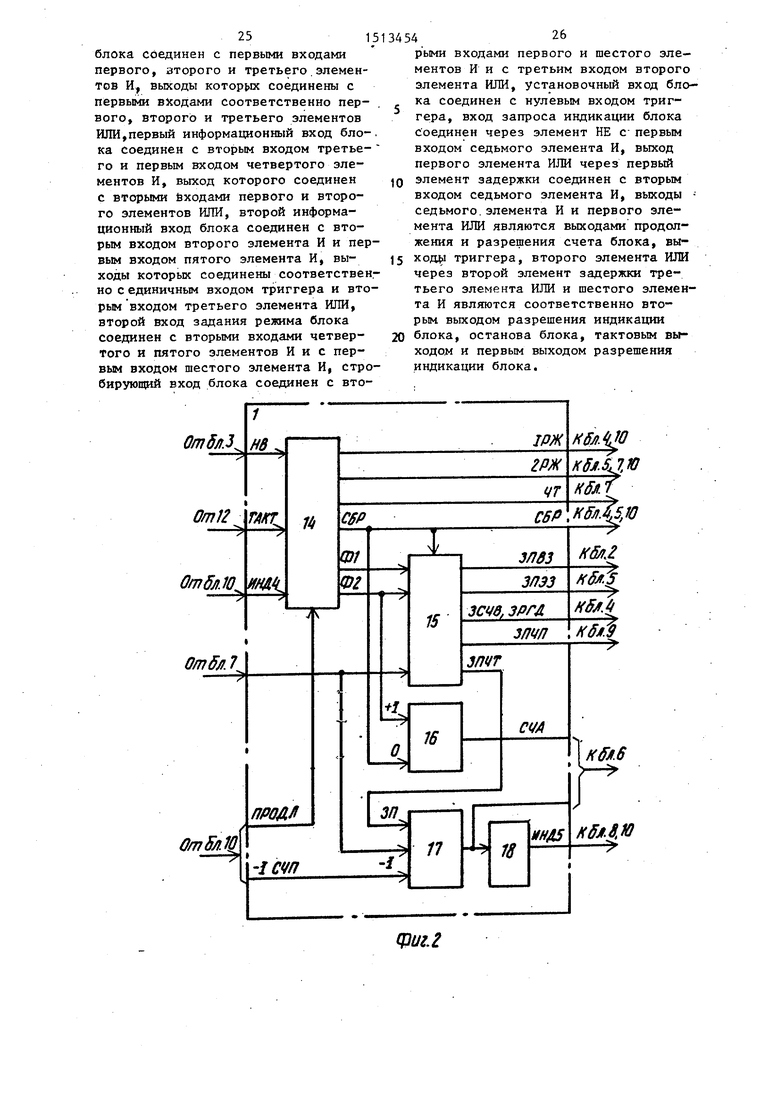

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 - схема блока управления; на фиг.З - схема блока анализа времени; на иг.4 - схема блока анализа результата; на фиг.5 - схема блока принятия решения;- на фиг.6 - схема первого узла синхронизации; на фиг.7 - схема второго узла синхронизации; на фиг.З - алгоритм работы устройства в режиме проверки; на фиг.9 - алгоритм работы устройства в режиме поиска; на фиг.10 - схема информации из области проверки, поиска и выходного файла объекта диагностирования; на фиг.11 - фрагмент теста; на фиг.12 - пример, поясняющий прохождение теста в структуре микропроцессора. На фиг.10а-в обозначены: ЧТ - число примеров (идентификаторов) в тесте, КЧТ - метка конца ЧТ, Ш - число проверяемых переменных, ШЧ - метка конца ЧП, ДП - значение опуска на время выполнения програм- ы, КДП - метка конца ДП, ВВ - знаение расчетного времени выполнения рограммы, ОК - область констант, КК - метка конца ОК, 33 - эталонные значения выходных переменных, КЭЗ - метка конца 33, ВЗ - значения входных переменных, КВЗ - метка конца ВЗ, СП - область примера, КП - метка конца СП, ИВ - метка начала вычислений, ИР - метка, начала результа тов, РЗ - результаты вычисления примера (-выходные переменные), КР - метка конца РЗ....

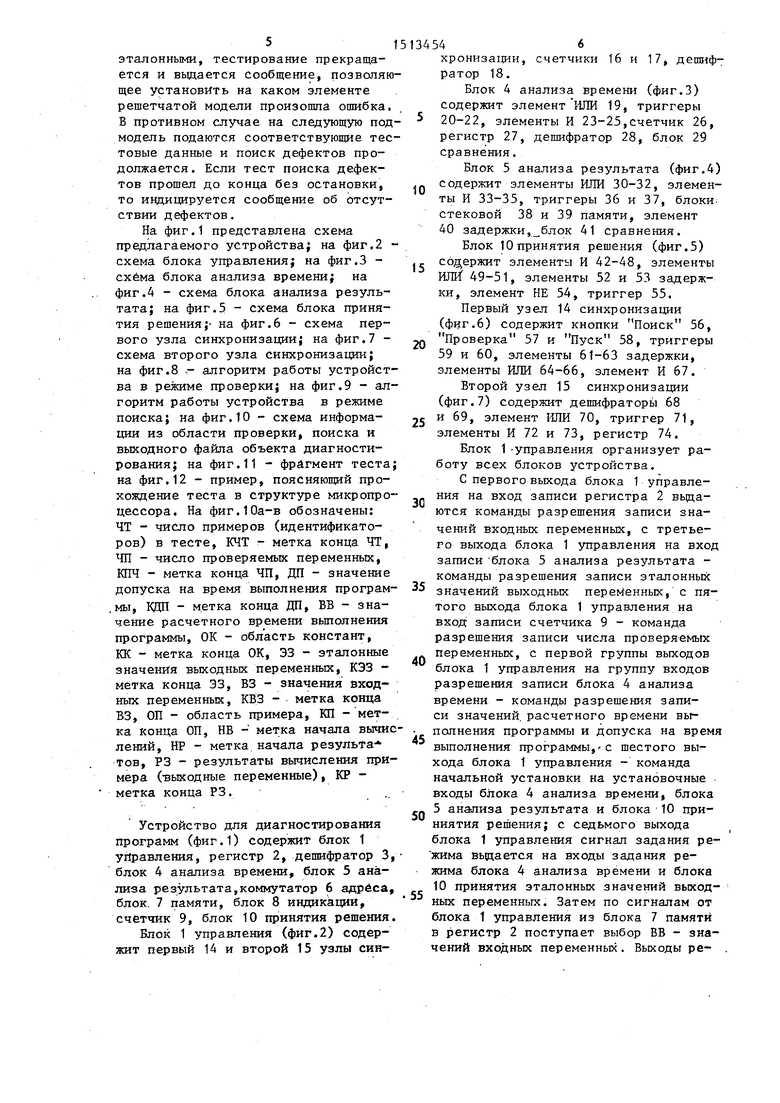

Устройство для диагностирования программ (фиг.1) содержит блок 1 правления, регистр 2, дешифратор 3, блок 4 анализа времени, блок 5 анаиза результата,коммутатор 6 адреса, блок. 7 памяти, блок 8 индикации, счетчик 9, блок 10 принятия решения.

Блок 1 управления (фиг.2) содержит первый 14 и второй 15 узлы син4546

хронизаили, счетчики 16 и 17, дешифратор 18.

Блок 4 анализа времени (фиг.З) содержит элемент ИЛИ 19, триггеры 5 20-22, элементы И 23-25,счетчик 26, регистр 27, дешифратор 28, блок 29 сравнения.

Блок 5 анализа результата (фиг.4) Q содержит элементы ИЛИ 30-32, элементы И 33-35, триггеры 36 и 37, блоки- стековой 38 и 39 памяти, элемент 40 задержки,блок 41 сравнения.

Блок 10 принятия решения (фиг.З) , содержит элементы И 42-48, элементы ИЛРГ 49-51, элементы 52 и 53 задержки, элемент НЕ 54, триггер 55.

Первый узел 14 синхронизации (фиг.6) содержит кнопки Поиск 56, Q Проверка 57 и Пуск 58, триггеры 59 и 60, элементы 61-63 задержки, элементы ИЛИ 64-66, элемент И 67. Второй узел 15 синхронизации (фиг.7) содержит дешифраторы 68 5 и 69, элемент ИЛИ 70, триггер 71, элементы И 72 и 73, регистр 74.

Блок 1 -управления организует работу всех блоков устройства.

С первого выхода блока 1 управления на вход записи регистра 2 вьща- ются команды разрешения записи значений входных переменных, с третьего выхода блока 1 управления на вход записи блока 5 анализа результата - команды разрешения записи эталонных значений выходных переменных, с пятого выхода блока 1 управления на вход записи счетчика 9 - команда разрешения записи числа проверяемых переменных, с первой группы выходов блока 1 управления на группу входов разрешения записи блока 4 анализа времени - команды разрешения записи значений, расчетного времени вы- полнения программы и допуска на время выполнения программы,-с шестого выхода блока 1 управления - команда начальной установки на установочные входы блока 4 анализа времени, блока - 5 анализа результата и блока 10 при- ниятия решения; с седьмого выхода блока 1 управления сигнал задания ре- жима вьдается на входы задания режима блока 4 анализа времени и блока 10 принятия эталонных значений выходных переменных. Затем по сигналам от блока 1 управления из блока 7 памяти в регистр 2 поступает выбор ВВ - значений входных переменных. Выходы ре- .

0

0

10

15

20

гистра 2 соединены с информационными выходами 11 устройства, с которых входные значения последовательно счи- тываются в ОД. Метка КВЗ - конца об- ласти входных значений - также посту- 5 пает на ОД и служит для него сигналом начала вычислений. Начало вычислений подтверждается поступлением метки НВ- начала вычислений (фиг.10в5 от ОД на информационные входы 13 устройства. Метка НВ распознается дешифратором 3, который вырабатывает команду начала отсчета времени выполнения программы, поступающую в блок 4 анализа времени. Отсчет времени прекращается только после поступления на входы дешифратора 3 от ОД метки HP - начала результатов. Если расчетное время выполнения программы истекло, а метка начала результатов еще не принята, то блок 4 анализа времени вырабатывает команду, раз- решаюшую индикацию в блоке 8 ивдика- ции сообщения Зацикливание. При по- ступлении метки начала результатов дешифратор 3 вырабатывает команду подготовки к приему результатов, которая поступает в блок 5 анализа результата. Затем в блок 5 анализа результата последовательно записываются РЗ - результаты вычисления данного примера, поступающие от ОД на информационные входы 13 устройства. Набор результатов завершается меткой КР - конца результатов, по кото- 35 рой дешифратор 3 вырабатывает команду в блок 4 анализа времени, разрешающую сравнение фактического времени вьшолнения программы со значением допуска. Если фактическое время вы- . 40 полнения программы оказывается меньше допустимой величины, то блок 4 анализа времени вырабатывает команду, разрешающую индикацию решения; с седьмого выхода блока 1 управления сигнал задания режима выдается на .входы задания режима блока 5 анали- ,за результата, блока 10 принятия решения, на адресный вход блока 7 памяти; со второй группы выходов блока 50 1 управлени5 на группу информационных входов коммутатора 6 адреса выдается информация о текущем номере примера и содержимое счетчика адреса; со второго выхода блока 1 .управ- 55 ления на вход чтения блока 7 памяти выдается команда разрешения считывания; с четвертого выхода блока 1

30

0

5

0

5 5 0 0 55

0

управления команда разрешения индикации вьщается на третий вход разрешения индикации блока 8 индикации и на вход запроса индикации блока 10 принятия решения.

Регистр 2 предназначен для фиксации информации, поступающей на объект диагностирования. С информационных выходов регистра 2 на группу ин- ф.ормационных входов объекта диагностирования выдаются значения входных переменных и метка конца входных значений.

Дешифратор 3 предназначен для распознавания команд в потоке информации, поступающей от объекта диагностирования. С третьего выхода дешифратора 3 командная информация выдается на входы начала вычислений блока 1 управления и блока 4 анализа времени; с первого и второго выходов дешифратора 3 командная информация выдается на входы начала и конца режима блоков 4 анализа времени и 5 анализа результата.

Блок 4 анализа времени предназначен для анализа времени выполнения программы. С выхода признака сравнения блока 4 анализа времени на вход начала сравнения блока 5 анализа результата вьщается сигнал сравнения; с выходов разрешения индикации блока 4 анализа времени ha пер-, вый и второй входы разрешения индикации блока 8 выдаются команды разрешения индикации.

Блок 5 анализа результата предназначен для сравнения результатов прохождения программы с эталонными значениями. С выходов результата сравнения блока 5 анализа результата на информационные входы блока 10 принятия решения выдаются сигналы сравнения (несравнения).

Коммутатор 6 адреса предназначен для реализации обращений к различным областям адресного пространства блока 7 памяти. С выходов коммутатора 6 адреса на группу адресных входов блока 7 памяти выдается адресная информация.

Блок 7 памяти предназначен для . хранения диагностической информации. С выходов блока 7 памяти на информационные входы блока 1 управления выдается число примеров, метки, на информационные входы регистра 2 выдаются значения входных переменных,на

информационные входы блока 4 анализа времени - значения рассчетного времени и допуска на время выполнения программы, на информационные вхды блока 5 анализа результата - эталонные значения вькодных переменных, на группу информационных входов блока 8 индикации - информация характере обнаруженных дефектов, на информационные входы счетчика 9 - число проверяемых переменных.

Блок 8 индикации пр.едназначен дл индикации результатов диагностирования.

Счетчик 9 предназначен для хранения числа проверяемых переменных. G выхода переполнения счетчика 9 на стробирующий вход блока 10 принятия решения выдается сигнал обнуления счетчика.

Блок 10 принятия решения предназначен для анализа процесса сравнения результатов вычисления примера с эталонными значениями. С выхода останова блока 10 принятия решения на вход останова блока 5 анализа результата вьщается команда остановки работы, с тактового выхода блока 10 принятия решения на вычи- таюпщй вход сметчика 9 - команда изменения состояния, с выходов продолжения и разрешения счета блока 10 принятия решения на входы продолжения и вычитания блока 1 управления - команды продолжения работы, перехода к следующему примеру, с первого выхода разрешения индикации блока 10 принятия решения команда разрешения индикации вьца- ется на управляющий вход блока 1 управления,, на управляющий вход коммутатора 6 адреса, на адресный вход блока 7 памяти, на второй вход раз- решения блока 8 индикации, с второ- го выхода разрешения индикации блика 10 принятия решения на третий вход разрешения индикации блока 8 - команда разрешения индикации.

Устройство для диагностирования программ (фиг.1) работает следующим образом.

Сначала происходит установка в исходное состояние блока 1 управления, а т-акже блоков анализа времени 4, анализа результата 5, принятия решения 10 по сигналу от блока 1 управления . При этом на управляющий вход коммутатора 6 адреса от блока

0

0

5

10 принятия решения поступает нулевой сигнал, в соответствии с которым коммутатор 6 адреса подключает к группе адресных входов блока 7 памяти группу выходов блока 1 управления. .Кроме выходов коммутатора 6 адреса, к группе адресных входов блока 7 памяти подсоединены: первый выход разрешения индикации блока 10 принятия решения, имеющий нулевое состояние после начальной установки, и восьмой выход блока 1 управления, состояние которого оп- 5 редаляется выбранным режимом работы устройства. При нулевом значении восьмого выхода блока 1 управления происходит обращение к области проверки (фиг.Юа), а при единичном - к области поиска (фиг.106) блока 7 памяти. Дальнейшая работа устройства осуществляется по синхронизирующим импульсам, поступающим от объекта диагностирования (ОД) на так- товьпЧ вход 12 устройства. Работа устройства.в каждом из режимов начинается С осуществления серии операций считывания-записи. С этой целью блок 1 управления каждый раз выполняет следующие действия: вьща- ет адрес считываемой информации, который поступает через коммутатор 6 адреса на группу адресных входов блока 7 памяти; формирует команду разрешения считывания,поступающую на блок 7 памяти; через бремя, необходимое для появления информации на выходах блока 7 памяти, блок 1 управления вьдает команду разрешения записи в один из блоков устройства. Рассмотрим работу устройства в каждом из режимов.

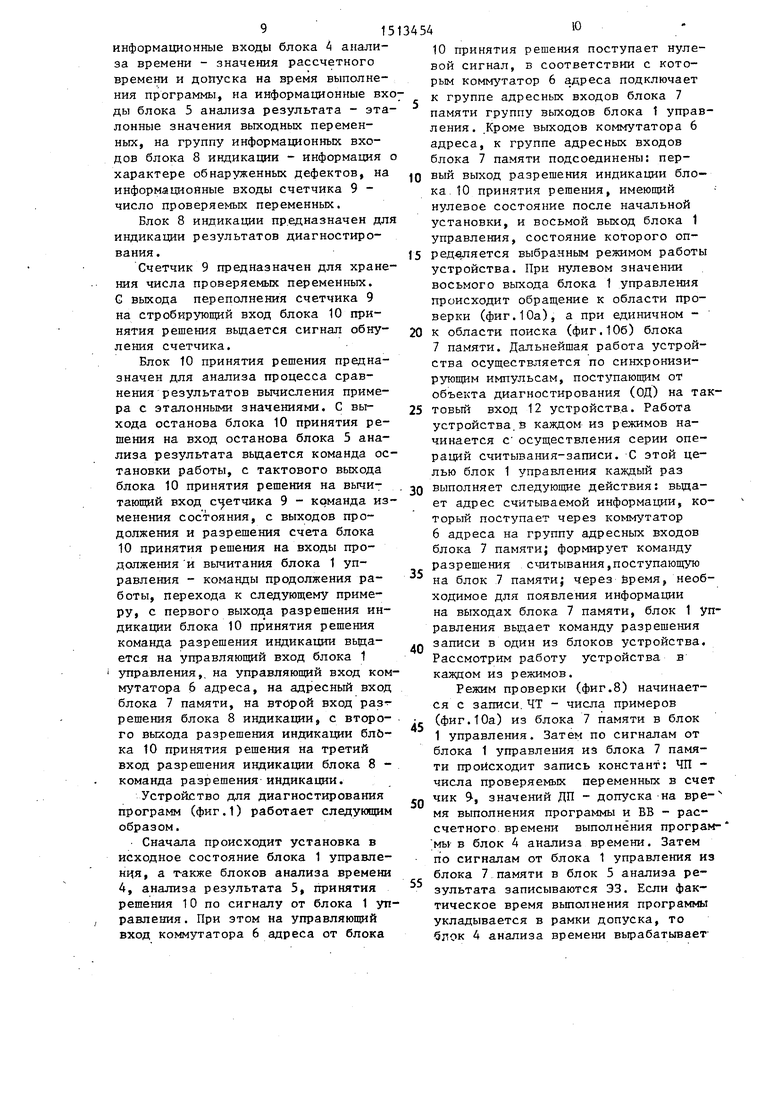

Режим проверки (фиг.8) начинается с записи. ЧТ - числа примеров (фиг.Юа) из блока 7 памяти в блок 1 управления. Затем по сигналам от блока 1 управления иа блока 7 памяти происходит запись констант: ЧП - числа проверяемых переменных в счет чик 9, значений ДП - допуска-на вре- мя выполнения программы и БВ - рассчетного. времени выполнения програм- MbJ в блок 4 анализа времени. Затем по сигналам от блока 1 управления из блока 7 памяти в блок 5 анализа результата записываются ЭЗ. Если фактическое время выполнения программы укладывается в рамки допуска, то 5лок 4 анализа времени вырабатывает

0

5

0

5

0

5

n

-команду, разрушающую последовательное сравнение результатов вычисления примера с эталонными значениями в блоке 5 анализа результата. Данные

0совпадении или несовпадении каждой пары сравниваемых величин поступают для анализа в блок 10 принятия решения. Условия анализа сигналов сравнения (несравнения) в блоке 10 принятия решения зависят от выбранного режима работы устройства и определяются состоянием седьмого (восьмого) выходов блока 1 управления В данном случае единичный сигнал присутствует на восьмом выходе блока 1 управления и задает следующий алгоритм анализа результатов. При несовпадении результата с эталонным значетем блок 10 принятия решения вырабатывает команду, разрешающую индикацию

в блоке 8 индикации сообщения Сшиб ка в программе. При совпадении результата с эталонным значением блок 10 принятия решения вьфабатьшает команду уменьшения на единицу содержимого счетчика 9. Если же все результаты прохождения примера совпадают с эталонными значениями, счётчик 9, достигнув нулевого состояния, выдает соответствующий сигнал на блок 10 принятия решения, который формирует команду остановки работы блока 5 анализа результата и команду перехода к следующему примеру в блоке

1управления. При этом число примеров в блоке 1 управления уменьшается на единицу, и работа устройства повторяется на следующем примере. Когда число примеров в блоке 1 управления достигает нуля, блок 1 управления выдает соответствующую команду, которая поступает в блок 8 индикации, разрешая индикацию соотношения Дефекта нет и в блок 10 принятия решения, запрещая дальнейшую работу устройства .

,

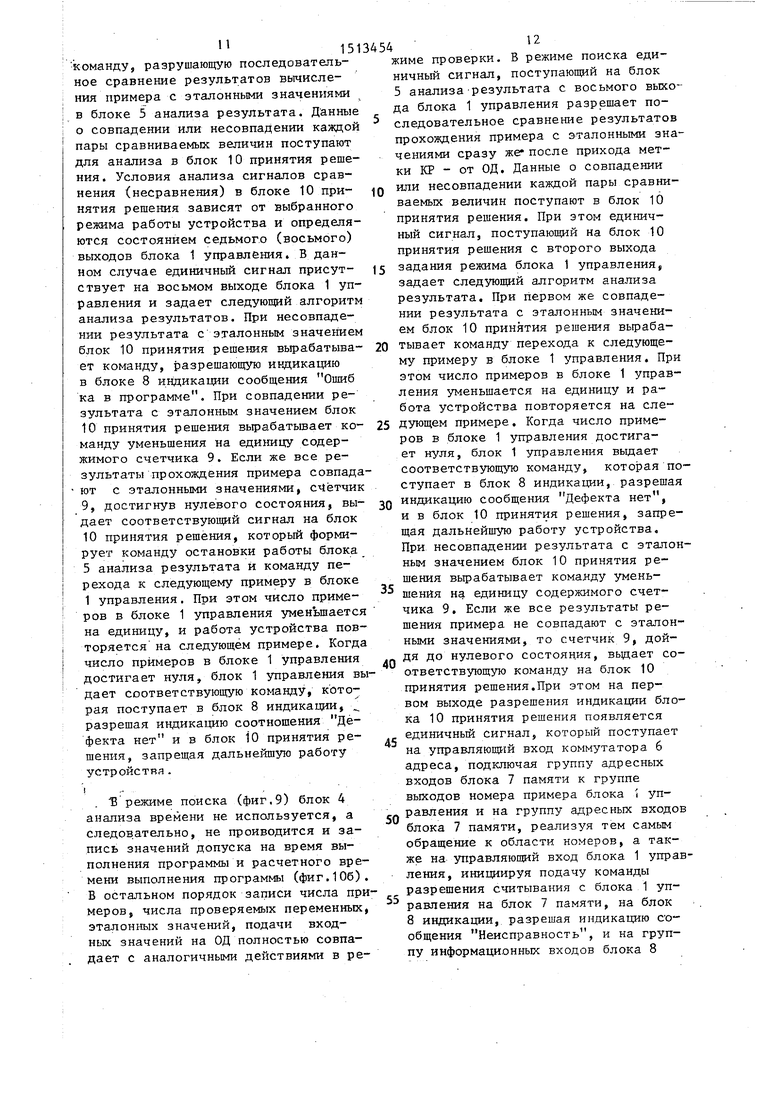

В режиме поиска (фиг.9) блок 4 анализа времени не используется, а следовательно, не проиводится и запись значений допуска на время выполнения программы и расчетного времени выполнения программы (фиг. 106). В остальном порядок записи числа примеров, числа проверяемых переменных, эталоннь:х значений, подачи входных значений на ОД полностью совпадает с аналогичными действиями в ре13454

12

10

20

25

жиме проверки. В режиме поиска единичный сигнал, поступающий на блок 5 анализа-результата с восьмого выхода блока 1 управления разрешает последовательное сравнение результатов прохождения примера с эталонными значениями сразу же после прихода метки КР - от ОД. Данные о совпадении или несовпадении каждой пары сравниваемых величин поступают в блок 10 принятия решения. При этом единичный сигнал, поступающий на блок 10 принятия решения с второго выхода (5 задания режима блока 1 управления, задает следзпощий алгоритм анализа результата. При первом же совпадении результата с зталоннь{м значением блок 10 принятия решения вырабатывает команду перехода к следующему примеру в блоке 1 управления. При этом число примеров в блоке 1 управления уменьшается на единицу и работа устройства повторяется на следующем примере. Когда число примеров в блоке 1 управления достигает нуля, блок 1 управления вьщает соответствуюшую команду, которая поступает в блок 8 индикации, разрешая индикацию сообщения Дефекта нет, и в блок 10 принятия решения, запрещая дальнейшую работу устройства. При несовпадении результата с эталонным значением блок 10 принятия решения вырабатывает команду уменьшения на единицу содержимого счетчика 9, Если же все результаты решения примера не совпадают с эталонными значениями, то счетчик 9, дойдя до нулевого состояния, вьщает соответствующую команду на блок 10 принятия решения.При этом на первом выходе разрешения индикации блока 10 принятия решения появляется единичный сигнал, который поступает на управляющей вход коммутатора 6 адреса, подключая группу адресных входов блока 7 памяти к группе выходов номера примера блока управления и на группу адресных входов блока 7 памяти, реализуя тем самым обращение к области номеров, а также на управляющий вход блока 1 управления, инициируя подачу команды разрешения считывания с блока 1 управления на блок 7 памяти, на блок 8 индикации, разрешая индикацию сообщения Неисправность, и на группу информационных входов блока 8

30

35

40

45

50

55

индикации от блока 7 памяти. Информация из области номеров блока 7 памяти, соответствующая номеру данного примера, содержит код команды, проверяемой на данном примере, и коды функциональных узлов ОД, задействованных на данной команде.

Блок управления (фиг.2) работает следующим образом.

Предварительно выбранный режим работы устройства определяет поступление единичного сигнала на один из двух выходов задания режима - 1РЖ (2РЖ). Работа блока начинается с появления на выходе СВР (сброс первого узла синхронизации 14) единичного сигнала, который поступает на выход СВР блока, входы сброса второго узла

10

15

хронизации как вспомогательный синхронизирующий сигнал и на счетный вход счетчика 16 адреса, увеличивая его содержимое на единицу. Работа первого узла 14 синхронизации прекращается по сигналу НВ и во зобновляется по сигналу Продолжение. При поступлении на вход ИНД 4 блока 1 управления единичного сиг нала обеспечивается безусловное фор мирование сигнала ЧТ. По сигналу ЗПЧТ - запись числа примеров, поступающему от второго узла 15 синхронизации, в счетчик 17 записывается ЧТ из блока 7 памяти. Содержимое счетчика 17 уменьшается на единицу всякий раз при поступлении сигнала - СЧП на вычитающий вход. При дости-

синхронизации 15 и на вход нуля счет- 20 счетчиком 17 нулевого состоячика 16 адреса, приводя их в исходное состояние. Затем по сигналам, поступающим на тактовьй вход блока,первый узел 14 синхронизации начинает . формировать сигналы в следующей по- 25 следовательности: ЧТ, Ф1, Ф2. Сигналь ЧТ - разрешение считывания и синхронизирующий Ф1 формируются с перекрытием, как это необходимо для выполНИН дешифратор 16, соединенный с вы ходами счетчика 17, вырабатывает си нал разрешения индикации ИНД 5, который поступает в блок 8 индикации, разрешая индикацию сообщения Дефекта нет и в блок 10 принятия решения, запрещая дальнейшую работу устройства. Информационные выходы счетчиков 17 и 16 адреса как НП - группа выходов номера примера и СЧА группа адресных выходов блока 1 управления, поступают в коммутатор 6 адреса.

нения операции считывания-записи. Сначала сигнал ЧТ, поступающий на блок 7 памяти, разрешает считывание с него информации, а затем через врмя, необходимое дляпоявления сигналов на выходах блока 7 памяти, на второй узел 15 синхронизации посту- пает сигнал Ф1. Если информация, поступившая от блока 7 памяти на вход второго узла синхронизации 15 классифицируется им как метка, то по сигналу Ф1 она записывается во второй узел 15 синхронизации и опре деляет направление подачи следующег сигнала разрешения записи. Если данная информация меткой не признается, то по сигналу Ф1 второй узел 15 синхронизации формирует один из шести возможных сигналов разрешения записи, направление подачи которого -определяется предварительно принятой меткой. Направление подачи первого сигнала разрешения записи обусловлено поступлением сигнала СВР на второй узел 15 синхронизации в начале работы. Затем через время, необходимое для осуществления счи- тьшания-записи, сигнал Ф2 с выхода первого узла 14 синхронизации поступает: на вход второго узла 15 син

5

хронизации как вспомогательный синхронизирующий сигнал и на счетный вход счетчика 16 адреса, увеличивая его содержимое на единицу. Работа первого узла 14 синхронизации прекращается по сигналу НВ и возобновляется по сигналу Продолжение. При поступлении на вход ИНД 4 блока 1 управления единичного сигнала обеспечивается безусловное формирование сигнала ЧТ. По сигналу ЗПЧТ - запись числа примеров, поступающему от второго узла 15 синхронизации, в счетчик 17 записывается ЧТ из блока 7 памяти. Содержимое счетчика 17 уменьшается на единицу всякий раз при поступлении сигнала - СЧП на вычитающий вход. При дости-

счетчиком 17 нулевого состоя

НИН дешифратор 16, соединенный с выходами счетчика 17, вырабатывает сигнал разрешения индикации ИНД 5, который поступает в блок 8 индикации, разрешая индикацию сообщения Дефекта нет и в блок 10 принятия решения, запрещая дальнейшую работу устройства. Информационные выходы счетчиков 17 и 16 адреса как НП - группа выходов номера примера и СЧА - группа адресных выходов блока 1 управления, поступают в коммутатор 6 адреса.

Влок 4 анализа времени (фиг.З) используется только в режиме проверки, когда на вход 1РЖ от блока 1 управления поступает единичный сигнал, разрешающий формирование команд ИНД1, ИНД2, на выходах элементов И 24 и 25. В режиме поиска на вход 1РЖ приходит нулевой сигнал. Работа блока 4 анализа времени начинается с поступления на вход СВР - сброс от блока 1 управления единичного сигнала, Который прохо- дя через элемент ИЛИ, 19, устанавливает в ноль триггеры 20-22, Затем на информационные входы блока 4 анализа времени от блока 7 памяти поступает ДП - значение допуска на время выполнения программы, которое записывается в регистр 27 допуска по сигналу ЭРГД - запись в регистр допуска, приходящему от блока 1 управления. Затем на информационные, входы блока 4,анализа времени от блока 7 памяти поступает ВВ - значение расчетного времени выполнения програм1-ш1, которое записывается в

счетчик 26 времени по сигналу ЭСТВ - запись в счетчик времени, приходя- щему от блока 1 управления. Затем

на вход НВ от дешифратора 3 посту- пает единичный сигнал, который устанавливает в единицу триггер 20.Единица с прямого выхода триггера 20 поступает на вход элемента И 23, разрешая прохождение через него тактовых сигналов от входа ТАКТ на вычи- таю.щий вход счетчика 26 времени-. Работа счетчика 26 -времени прекращается при поступлении от дешифратора 3 сигнала HP, который, проходя через элемент ИЛИ 19, сбрасывает в ноль триггер 20. Затем по сигналу КР, поступаюш;ему от дешифратора 3, в блоке 29 сравнения происходит сравнение содержимого счетчика 26 времени с допуском на время выполнения программы, хранящимся в регистре 27 допуска. В том случае, когда содержимое счетчика 26 времени не пре - вьшгает величину допуска, блок 29 сравнения вьфабатываёт единичный сигнал СРВТ - сравнение по времени, который поступает в блок 5 анализа результата . Если же содержимое счетчика 26 времени не укладывается в допуск, то блок 29 сравнения вырабатывает единичный сигнал НСРВ - несравнение, который устанавливает в единицу триггер 22.Единица с прямого выхода триггера 22, проходя через элемент И 25, как сигнал разрешения идикации ИНД2, поступает в блок 8 индикации и разрешает индикацию сообщения преждевременное выполнение программы. Если сигнал HP так и не поступил, то при достижении счетчиком времени 26 нулевого состояния дешифратор 28, соединенный с группой выходов счетчика, формирует единичный сигнал, который устанйвлийает в единицу триггер 21. Единичный сигнал с прямого выхода триггера 21, проходя через элемент И 24, как сигнал разрешения индикации ИНД1, поступает на блок 8 индикации и разрешает индикацию сообщения Задакли- вание.

Блок 5 анализа результата (фиг,4) работает следуюшлм образом. Сначала на вход СБ - сброс блока 5 анализа результата - от блока 1 управления подается единичный сигнал, который, проходя через элементы ИЛИ 31 и32, сбрасывает в ноль триггеры 36 и 37.

5

0

5

0

5

0

5

0

5

Затем по сигналам ЗПЭЗ - запись эталонных значений, приходящим от блока 1 управления, во второй блок 39 стековой памяти записываются ЭЗ, которые поступают от блока 7 памяти. Затем от дешифра тора 3 приходит единичный сигнал HP, который устанавливает в единицу триггер 36. Единица с прямого выхода триггера 36 разрешает прохождение тактовых сигна; лов на вход ЗП-запись первого блока t 38 стековой памяти. По тактовым сигналам в первый блок 38 стековой памяти записываются РЗ, которые по- ст-упают от объекта диагностирования через информационные входы 13 устройства. Затем от дешифратора 3 приходит единичный сигнал КР, который Поступает на первьй вход элемента И 33. В режиме проверки одновременно с сигналом КР на вход СРВТ - сравнение по времени - от блока 4 анализа времени должен поступить единичный сигнал, подтверждающий благополучный результат контроля по времени выполнения программы. Проходя через элемент ИЛИ 30,он поступает на второй вход элемента И 33, разрешая прохождение через него сигнала КР, ,Если в режиме проверки сигнал СРВТ не поступил, значит в объекте диагностирования произошло зациклирова- ние, или время выполенния программы не уложилось в допуск. В этом случае работа блока 4 анализа результатов прекращается. В режиме поиска, когда контроль по времени выполнения программы не производится, от блока 1 управления на вход 2 РЖ блока 5 анализа результата постоянно подается единичный сигнал, который, проходя через элемент ИЛИ 30, разрешает прохозвдение сигнала КР через элемент И 33. С выхода элемента И 33 единичный сигнал устанавливает в единицу триггер 37 и, проходя через элемент ИЛИ 31, сбрасывает в ноль триггер 36, Единичный сигнал с прямого выхода триггера 37 поступает на вход элемента И 35, разрешая прохождение через него тактовых сигналов на входы разрешения считывания блоков 38 и 39 стековой памяти и на вход элемента 40 задержки. При поступлении единичных сигналов на входы ЧТ блоков 38 и 39 стековой памяти результаты решения примера из первого блока 38 и эталонные значения из вто-

рого блока 39 подаются на входы блока 41 сравнения. Через.время, необходимое для формирования сигналов на выходах блоков 38 и 39 стековой памяти, с выхода элемента 40 задержки единичные сигналы поступают на вход РЗС - разрешение сравнения блока 41 сравнения. По сигналам РЗС на выходах блока 41 сравнения формируются сигналы СРВ - сравнение - или НСРВ - несравнение, которые поступают в блок 10 принятия решения. Работа блока 5 анализа результата прекращается при поступлении единичного сигнала ОС - останов - от блока 10 принятия решения.

. Влок 10 принятия решения (фиг.5) подготавливается к работе при поступлении, сигнала СВР - сброс - от блока 1 управления, которым устанавливается в ноль триггер 55, Дальнейшая работа блока 10 принятия решения зависит от режима работы устройства,

В.режиме проверки на вход 1РЖ блоки 10 принятия решения от блока 1 управления поступает единичный сигнал, который разрешает прохождение сигналов через элементы И 42 и 44, При поступлении сигнала НСРВ - несравйение - от блока 5 анализа результата единичный сигнал, проходя через элемент И 43, устанавливает в единицу триггер 55, и через элементы ИЛИ 50 и задержки 52, как сигнал ОСТ, подается на блок 5 анализа результата. Единица с прямого выхода триггера 55, как сирнал ИНДЗ - разрешения индикации, поступает на блок 8 индикации, разрешая индикацию сообщения Опгабка в программе. При поступлении сигнала СРВ от блока 5 анализа результата единица, проходя через элементы И 44 и ИЛИ 51, -как сигнал - 1СЧ ПЕР - уменьшение на единицу числа переменных, подается на вычитающий вход счетчика 9, При поступлении сигнала СЧ ПЕР О от счетчика 9 единица, проходя через элемент ты И 42 и ИЛИ 49, поступает как сигнал - 1 СЧ ПР - уменьшение числа примеров, на блок 1 управления и на вход элемента 53 задержки. Затем через время, необходимое для уменьшения числа примеров в блоке 1 управления и определяемое элементом 53 задержки, единичный сигнал поступает на вход элемента И 48. Если в этот момент на вход ИНД 5 от блока 1 уп

5

5

равления поступает нулевой сигнал , то будучи проинвертирован элементом НЕ 54, формирует на выходе элемента И 48 единичнь1й сиг нал ПРОДП - продолжение, который поступает на блок 1 управления и служит командой продолжения работы устройства на следующем примере. Если на вход ИНД 5 от блока 1 управления поступает единичный сигнал, ноль с выхода элемен-«. та НЕ 54 закрывает элемент И 48, и работа устройства прекращаете.

В режиме поиска на вход 2РЖ блока 4,0 принятия решения от блока 1 управления поступает единичнь5й сигнал, который разрешает прохождение сигналов через элементы И 45 и 47.При поступлении сигнала СРВ от блока .5

0 анализа результата единичный сигнал, проходя через элемент И 45, поступа-. ет на входы элементов ИЛИ 49 и 50, С выхода элемента ШШ 50 единица, проходя через элемент 52 задержки,как сигнал ОСТ подается на блок 5 анализа результата. С выхода элемента ШШ 49 единица поступает как сигнал -1 СЧ ПР на блок 1. управления и на вход элемента 53 задержки. С выхода элемента 53 задержки единица поступает на вход элемента И 48, который формирует сигнал ПРОДЛ по тому же принципу, что и в режиме проверки. При поступлении сигнала НСРВ от блока 5 анализа результата единичный сигнал, проходя через элементы И 46 и ИЛИ 51, как сигнал - 1 СЧ ПЕР подается на вычитающий вход счетчика 9, При поступлении сигнала СЧ ПЕР О от счетчика 9 единица, проходя через элемент И 47, как сигнал ИНД 4 поступает на блоки 1, 6, 7, 8 устрой- ства, обеспечивая индикацию в блоке 8 индикации.сообщения НеисПрав5 ность с указанием кода команды, проверяемой на данном примере и кодов функциональных узлов объекта диагностирования, задействованных на данной команде.

0 Первый узел синхронизации 14 блока 1 управления (фиг.6) работает следующим образом. Нажатием одной из кнопок Поиск 56 (Проверка 57)

производится выбор режима работы устс ройства. После этого с прямого (ин-. версного) выхода триггера 59 единичный сигнал поступает на выход 2РЖ (1РЖ) первого узла 14 синхронизации. Нажатием кнопки Пуск 58 осуще-ст0

5

0

,19151

вляется пуск устройства. При этом единичный сигнал поступает на выход СВР, на вход элемента 61 задержки, через элемент ИЛИ 65 на вход уста- новки в ноль триггер 60. Затем : через время, необходимое для начальной установки всех блоков устройства, и определяемое элементом 61 задержки, единичный сигнал, проходя через элемент ИЛИ 64, устанавливает в единицу триггер 60. Единичный сигнал с прямого выхода триггера 60 поступает на вход элемента И 67, разрешая прохождение через него.тактовых сигналов со входа ТАКТ первого узла 14 синхронизации. Тактовые сигналы, проходя через элемент И 67, поступают через элемент ИЛИ 66 на выход ЧТ - разрешение считывания, на вход элемента 62 задержки. Затем через время, определяемое элементом 62 задержки, единичный сигнал посту- пает на синхронизирующий выход Ф1 и на вход элемента 63 задержки. Время задержки элементы 62 выбирается таким, чтобы сигналы ЧТ и Ф1 следовали с перекрытием. Затем через время, определяемое элементом 63 задерж- ки, единичный сигнал поступает на синхронизирующий выход Ф2 первого узла 14 синхронизации. В процессе работы устройства триггер 60 переключается сигналами НЕ или ПРОДЛ, которые проходят через элементы ИЛИ 65 (или 64). При этом прекращается (возобновляется) формирование сигналов на выходах ЧТ, Ф1, Ф2 узла. Сигнал ИНД 4, проходя через элемент ИЛИ 66, осуществляет безусловное формирование едининцы на выходе ЧТ. ; Второй узел 15 синхронизации блока t управления (фиг.7) работает по следзтощему принципу. При единичном состоянии триггера 71 в регистр 74 меток заносится информация, определяющая одно из шести возможных направлений, в котором будет подан очередной сигнал разрешения записи. При нулевом состоянии триггера 71 осуществляется собственно формировайие сигнала разрешения записи. В нуле- вое состояние триггер 71 устанавливается по сигналу СВР - или по синхронизирующему сигналу Ф2, проходящему через элемент ИЛИ 70.При этом единичный сигнал с инверсного выхода триггера 71 поступает на вход элемента И 72, разрешая прохояде ние

3454

20

через него синхронизирующего сигнала Ф1 на выход стробирования дешифратора 69, Сигнал разрешения записи появляется на выходе дешифратора 69 только в момент стробирования. В единичное состояние триггер 71 устанавливается при появлении единицы на выходе М - метка дешифратора

68, что происходит во время поступления метки от блока 7 памяти на входы установки второго узла 15 синхронизации, В этом случае единица с прямого выхода триггера 71 поступает на вход элемента И 73, разрешая прохождение на вход ЗП - запись регистра меток 74 синхронизирующего сигнала Ф1, по которому происходит запись метки, присутствующей на информационных входах регистра 74.

Взаимодействие регистра меток 74 и дешифратора 69 рассмотрим на примере режима проверки (фиг.Юа), когда второй узел 15 синхронизации формирует все шесть сигналов разрешения записи. Сначала регистр меток 74 обнуляется по сигналу СВР. В этом случае формируется сигнал ЗПЧТ - разрешения записи числа примеров в

блок 1 управления. Затем в регистр 74 меток записывается метка КЧТ. В этом случае формируется сигнал ЗПЧП - разрешения записи числа переменных в счетчик 9. Затем в регистр меток 74 записывается метка КПЧ. В этом случает формируется сигнал ЗРГД - разрешения записи в регистр допуска блока 4 анализа времени,Затем в регистр меток 74 записывается метка

КДП. Б этом случае формируется сигнал ЗСЧВ - разрешение записи в счетчик времени блока 4 анализа времени. Затем в регистр 74 меток записывается метка КК. В этом случае формируются сигналы ЗПЭЗ - разрешение записи эталонных значений в блок 5 анализа-результата. Метка КК хранится в .„ регистре меток 74 до тех пор, пока в блок 5 анализа результата не буР-У записаны все эталонные значения. Затем в регистр 74 меток записывается метка КЭЗ. В этом случае формируются сигналы ЭПВЗ - разрешение записи входных значений в регистр 2. Метка КЭЗ хранится в регистре меток 74 до тех пор, пока в регистр 2 не будут записаны все входные значения и метка КБЗ - конец входных значений, которая де

2115

шифратором 68 не распознается, так как она необходима только для инициирования процесса вычисления в ОД Затем в регистр меток 74 записьшается метка КП, действие которой аналогично действию метки КЧТ, и работа второго узла синхронизации 15 повторяется на следующем примере.

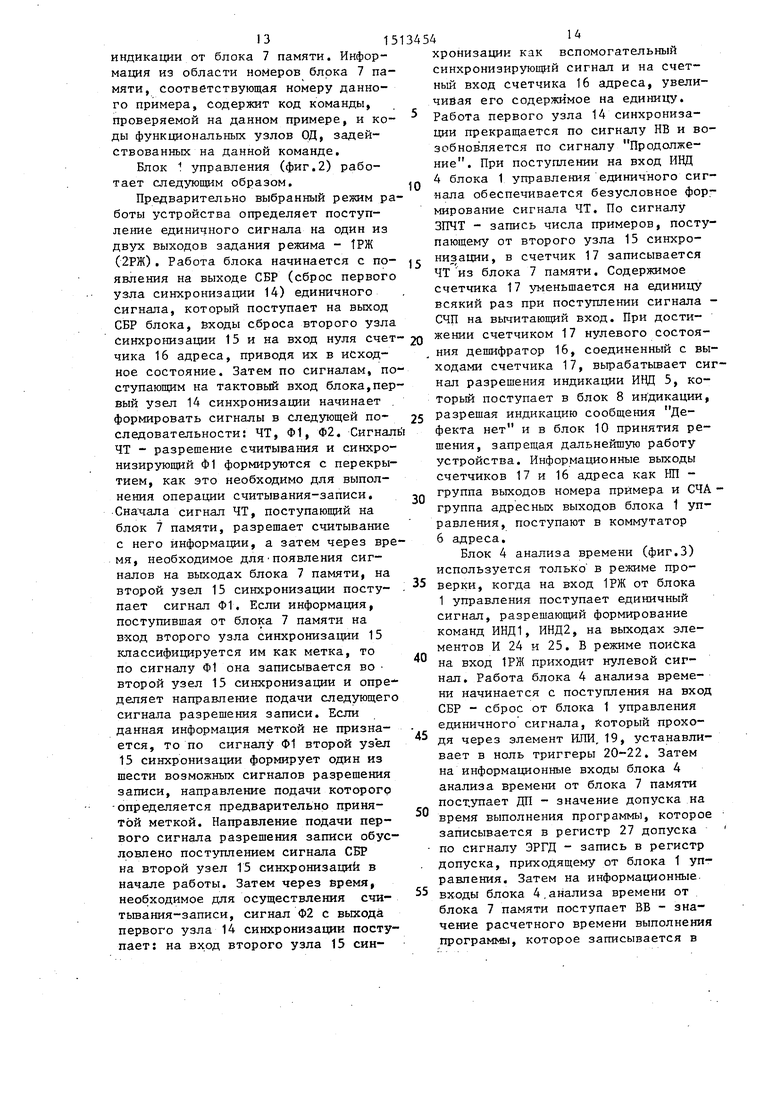

Особенности построения теста поясним следующим образом. С помощью автоматизированной системы построения тестов строится тест поиска дефектов. Наиболее распространенным является микропроцессор серии К580. Поэтому рассмотрим фрагмент теста для этого микропроцессора, фрагмент схемы которого приведен на фиг.12. Фрагмент теста включает три идентификатора (фиг.11). Первый идентификатор состоит из команды MVI с кодом 13 и OVT с кодом 41 и доказывает наличие или отсутствие дефектов ФУ с кодами 1 и 23, которые затрагиваются при обработке информации. Код 1 соответствует устройству ввода-вывода и шине данных, а код 23 - аккумулятору (фиг.11). Второй идентификатор по отношению к первому включает команду ADI, что обеспечивает проверку АПУ при выполнении операции сложения с кодом 24. В третьем идентификаторе подмножество диагностируемых узлов пополняется регистром признаков и, в частности, разрядом регистра признаков с кодом 6, где содержится признак переноса. Таким образом, обнаруживаемые идентификаторами подмножества дефектов образуют упорядоченную по включению п6- следоватлеьность ФУ, а именно П,,23, 24ус{1,23, 24,65. Этим последовательностям ФУ соответствуют пути прохождения идентификатора, которые представлены на фиг.12. Путь для первого идентификатора, отмеченный жирной линией, показывает, что данные в аккумулятор поступают из шины данных и вы- вводятся командой OVT через ПЩ на устройство ввода-вывода.Вторым идентификатором затрагивается АЛУ (фиг.12 тонкая сплошная линия). В АЛУ первый операнд поступает через аккумулятор .на одну входную шину данных (ЩД) а второй - непосредственно с внутренней ШД, а результат выводится во внутреннюю ШД и далее в аккумулятор.

45422

Информация из аккумулятора выводится командой OVT. Путь для третьего иден тификатора, отмеченного пунктирной , линией, отличается от пути для второго идентификатора охватом регистра признаков. Анализ идентификаторов и путей показывает, 1то, например,успешное прохождение первого идентифи0 катора позволяет при несовпадении выходных последовательностей для вто- рого идентификатора однозначно указать место дефекта: АЛУ при выполнении операции сложения. Таким обра5 ЗОМ- для теста поиска дефектов строится специальная программа, состоящая из идентификаторов и позволяющая осуществить поиск дефектов ФУ, соответствующих идентификаторам.

20

5

0

5

0

5

0

5

Формула изобретения

1. Устройство для контроля программно-аппаратных средств ЭВМ, содержащее блок управления, регистр, дешифратор, блок анализа времени, блок анализа результата, блок памяти, блок индикации и счетчик, причем первый выход блока управления соединен с входом записи регистра, выход блока памяти соединен с информационными входами регистра, блока анализа времени, блок анализа результата, блока управления и счетчика, второй выход блока управления соединен с входом чтения блока памя ти, третий выход блока управления соединен с входом записи блока анализа резуль- -тата, первый и второй выходы дешифратора соединены соответственно с входами начала режима контроля и конца режима контроля блока анализа результата и блока анализа времени, выходы разр.ешения индикации которого соединены соответственно с первым и вторым входами разрешения блока индикации, четвертый выход блока управления соединен с третьим йходом разрешения блока индикации, третий i выход дешифратора соединен с входом начала вычислений блока анализа времени, первая группа выходов блока управления соединена с группой входов разрешения записи блока анализа времени, информационные входы устройства соединены с входами дешифратора и информционными входами блока анализа результата, выход признака срав нения блока анализа времени соединен

с входом начала сравнения блока анализа результата, тактовый вход устройства соединен с тактовым входом блока анализа времени, информационные выходы регистра являются информационными выходами устройства, пятый выход блока управления соединен с входом записи счетчика, отличающееся тем, что, с целью расширения диагностических возможностей устройства за счет обеспечения поиска и локализации дефектов в контролируемых-узлах процессора и программы, в устройство введены коммутатор адреса и блок принятия решения, причем тактовый вход устройства соединен с входом стробиро- вания дешифратора,, с тактовыми входами блоков управления и анализа результата, третий выход дешифратора соединен с входом начала вычислений блока управления, шестой выход которого соединен с установочными входами блока анализа времени, блока анализа результата и блока принятия решения, выход останова которого соединен с входом останова блока анализа результата, выходы резул ь- татов сравнения блока анализа результата соединены с информационными входами блока принятия решения,пер- вьй выход разрешения индикации кото- рого соединен с вторым входом разрешения блока индикации, адресным входом блока памяти и управляющими входами коммутатора а,цреса и блока управления, седьмой выход которого соединен с входом задания режима блока анализа времени и первым входом задания режима блока принятия решения, выходы продолжения и разрешения счета которого соединены соответственно с входами продолжения и вычитания блока управления, восьмой выход блока управления соединен с адресным-входом блока памяти, входом задания режима блока.анализа результата и вторым входом зйдания режима блока принятия решения, тактовый выход которого соединен С вычи- таюшзим входом счетчика, выход переполнения которого соединен со стро- бирующим входом блока принятия решения, четвертый выход.блока управ- ления соединен с входом запроса индикации блока принятия решения, вторая группа выходов блока з правления соединена с группой информационных

0

5

0

5

0

5

0

5

входов коммутатора адреса, выходы , которого соединены с группой адресных входов блока памяти, выходы блока памяти соединены с группой информационных входов блока индикации, второй выход разрешения индикации блока принятия решения соединен-с третьим входом разрешения блока индикации,

.«

2. Устройство по п.1, о т л и - чающееся тем, что блок управления содержит счетчик, дешифратор, первый и второй узлы синхронизации, счетчик адреса, причем вход начала вычислений блока соединен с .входом останова первого узла синхронизации, первый, второй, третий и четвертый, пятый и шестой выходы которого соединены соответственно с седьмым выходом блока, восьмым выходом блока, с вторым выходом блока, с шестым выходом блока, с первым и вторым тактовыми входами второго узла синхронизации, тактовый вход и управляюш;ий вход блока соединены соответственно с тактовым входом и входом запуска индикации первого узла синхронизации, четвертьй выход и шестой выход которого соединены соответственно с входом сброса второго узла синхронизации и счетным входом счетчика адреса, информационней вход блока соединен с входом установки второго узла синхронизации и информационным входом . счетчика, входы продолжения и вычитания блока соединены соответственно с входом запуска первого узла синхронизации и вычитающим входом счетчика, выход которого соединен с дешифратором и выход которого является четвертым выходом блока, первый - пяТьш выходы второго узла синхронизации соединены соответственно с первым, третьим и пятым выходами блока с первой группой выходов блока и входом записи счетчика, четвёртый выход первого узла синхронизации соединен с входом нуля счетчика адреса, выходы счетчика адреса и счетчика образуют вто рую группу вь ходов блока.

3« Устройство по п.1, о т л и - чающееся тем, что блок принятия решения содержит семь элементов И, три элемента ИЛИ, два элемента задержки, триггер и элемент НЕ, причем, первый вход задания реяшма

251

блока соединен с первыми входами первого, аторого и третьего.элементов И, выходы котор{ 1х соединены с первыми входами соответственно первого, второго и третьего элементов Ш1И,первый информационный вход блока соединен с вторым входом третьего и первым входом четвертого элементов И, выход которого соединен с вторыми йходами первого и второго элементов ИЛИ, второй информационный вход блока соединен с вторым входом второго элемента И и первым входом пятого элемента И, выходы которых соединены соответствен; но с единичным входом триггера и вторым входом третьего элемента ИЛИ, второй вход задания режима блока соединен с вторыми входами четвертого и пятого элементов Икс первым входом шестого элемента И, стро- бирующий вход блока соединен с вто1345426

,

рыми входами первого и шестого элементов И и с третьим входом второго элемента ИЛИ, установочный вход бло- . ка соединен с нулевым входом триггера, вход эапроса индикации блока Соединен через элемент НЕ с- первым входом седьмого элемента И, выход первого элемента ИЛИ через первый

10 элемент задержки соединен с вторым входом седьмого элемента И, выходы - седьмого.элемента И и первого элемента ИЛИ являются выходами продолжения и разрешения счета блока, вы15 триггера, второго элемента ИЛИ через второй элемент задержки третьего элемента ИЛИ и шестого элемента И являются соответственно вторым выходом разрешения индикации

20 блока, останова блока, тактовым выходом и первым выходом разрешения индикации блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1983 |

|

SU1149269A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Устройство для диагностирования группы из @ логических узлов | 1985 |

|

SU1390611A1 |

| Устройство для поиска дефектов дискретных блоков | 1985 |

|

SU1379784A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для диагностирования группы логических узлов | 1987 |

|

SU1520520A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

| Устройство для диагностирования цифровых блоков | 1987 |

|

SU1548789A1 |

Изобретение относится к вычислительной технике, а именно к устройствам проверки правильности выполнения программ и устройствам поиска дефектов программ и функциональных узлов микропроцессоров. Цель изобретения заключается в расширении диагностических возможностей устройства за счет обеспечения поиска и локализации дефектов программы и функциональных узлов микропроцессора. Устройство для контроля программно-аппаратных средств ЭВМ содержит блок 1 управления, регистр 2, дешифратор 3, блок 4 анализа времени, блок 5 анализа результата, коммутатор 6 адреса, блок 7 памяти, блок 8 индикации, счетчик 9, блок 10 принятия решения. Устройство за счет введения коммутатора 6 адреса и блока 10 принятия решения и новых связей обеспечивает расширение функциональных возможностей. 2 з.п. ф-лы, 12 ил.

OfnSt.l

СВР

20

Vn

-If

ЗРГй

ЗП

От5лЛ

88,АП

АП

21

0/пбл.1

1РЖ

2-1

21/

25

ННА1

ИНД2

.s

29

СР8

CPST

ffSff.S

1/7 56

фиг, 6

фиг. 7

С

Начало

Л.

На дешифратор тупи,т меттНР- начс( резу/ б;; smo

Да.

6, Коиеч ( брем&нц. Вы- пол нения npo jjctHMb/ В локе 4 аиа,лиш Времени.

®

Нет

Рассчетное 8ремя

вьто/гнения frp0 paMMi ucmeff/fo

а

9, индикация соо6щени,й „Зацикливание В fдоне8 uHduHaifuu,

KoHei

Фиг. 8 (а)

Фактическое бремя Вьтопнеииа про- Mmi MeHtiu6 ддпусг мой величины

Нет

-. ти 1 Р УЛьтсГ- -V L Pf J S yeHua при- ра рйВны 3mciffS/f- iM jHafe- иям

Ла

ff. Инди.каци.11 , преждевременное завершение п грамма 6 (лонв6 индикации.

Конец

Нет

/J. Индикация OuiudiHa 8 программе g S индикации.

С

Конец

1

IS. Индинация сообщения .4etpetTma нет f jf/forre S индикации

Конец

Фиг.8()

с

Иачапо

I.

Д Подача Вкчднъо зиачемий из f/ioKa 7 nanftmu чер&з регистр 2 ffd объект диагностирование

5

Komfi д ы

один 11рохо дений примера DuSeH эта/roHffofiji

JHQtfsnii O

Нет

С

Конец

Фи.г.§

. Уменьшение на edunut y числа примеров S dJffone 1 управления

$

Чис/го примеров равно

Ht/fffO

Ди

„Де(екта В- локе8 инди,каци.и.

С

Конец

а} Область проберки

6} Область поиска

6} Выходной. cpatL/i

УСТРОЙСТВО для даЛГНОСТИРШАНИЯ ПРСГРАМИ

ЩЦ, УВВ

ж, ОЗУ

КОЛАНДА

ПРИЗНАК НУЛЕВОГО РЕЗУЛЬ

iiSiiffi

ПРИЗНАК ЧЕГШОСТИ :Р РЕГИСТР ПРИЗНАКОВ

ПРОГРАММНЫЙ СЧЕТЧИК PC АБСТРАКТНАЯ РЕГИСТРОВАЯ Вй IE РЕГИСТРОШЕ ПАРИ

УКАЗАТЕЛЬ СТЕКА 5Р

СТЕК

АБСТРАКТНЫЙ РЕГИСТР fi

В

-

1ЙЕ

:1

РЕГИСТРЫ НАЗНАЧ

И ИЛИ

И

-АККУМУЛЯТОР

-. АЛУ.ШШИЯ -(

-АЛУ ФУШШЯ -АЛУ. ШШЯ

-АЛУ.ШВйИЯ . -АЛУ,ФУНКЦИЯ НЕ

-АЛУ, ЗШШИЯ 1 АШОЗНАЧ

-А)У,СДВИГ ВЛЕЮ

-W.CfflHr ВПРАВО

-АЛУ-ШЗЩИЯ СРАВНЕНИЯ

-ЛЕЁЙТИЧНАЯ КОРРЕКЦИЯ

-ДНСРШЕНТ

ILZ. to

И 14 ДЛЯ ЭЛЕХВНТА

КОМАНДЫ 15 35 ТЕСтДЛЯ ЭЛЕМЕНТА

Шина данных,

« Аккумулятор

Фш.11

| Устройство для контроля времениВыпОлНЕНия пРОгРАММ | 1978 |

|

SU798851A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля программ | 1983 |

|

SU1149269A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1987-07-08—Подача