1

зи с ЭВМ, буферный регистр 1, буферный блок памяти 2, блок 3 микропрограммного управления, блок обмена 4 с контролируемым цифровым блоком, счетчик 5 логических номеров, блок памяти 6, счетчик 7 длины вектора тестового набора, регистр 8 текущих состояний, выходной коммутатор 9, блок 10 определения интервалов диагностирования, блок памяти 11 эта-- лонных диагностических данных, мультиплексор 12, регистр набора 13, блок сравнения 14. Процесс диагностирования разделяется на два этапа - подготовка диагностических данных и процесс контроля. Процесс диагностирования выполняется в два этапа - этап подготовки массива диагностических данных и этап диагностики. На первом этапе при многократной выдаче теста из канальных ОЗУ на входы эталонного цифрового блока осуществляется поиск функций, выполняемых

1

Изобретение относится к автомати- . ке и вычислительной технике, может бь1ть использовано для контроля и диагностики цифровых блоков и является дополнительным к авт.св. № 1251084.

Цель изобретения - повьш1ение достоверности контроля.

Известно, что при выдаче тестовых наборов из канальных ОЗУ на контро- лируемый цифровой блок на входы приборов, входящих в состав блока, поступают коды функций, выполняемых этими приборами.

Входы задания кода функции бывают синхронными и асинхронными (т.е. функция выполняется по коду функции и синхронизирующему сигналу или просто по коду функции).

Каждая функция характеризуется двумя параметрами: адресом канальных ОЗУ, на котором код функции поступает на входы прибора, и количеством следующих за этим адресом ячеек памяти канальных ОЗУ, содержимое которых должно быть подано на входы контролируемого цифрового блок

9

приборами, и определение их параметров. Затем эти данные передаются в ЭВМ, которая производит анализ полноты набора функций, выполняемых прибором. При обнаружении неполного набора выполняемых функций каким-либо прибором ЭВМ выдает сообщение о необходимости корректировки програм- мы теста. Кроме того, ЭВМ формирует массив данных маскирования некоторых контактов приборов, состояния которых являются неопределенными или несущественными для выполнения заданной функции. На этапе диагностики происходит локализация неисправности в контролируемом цифровом блоке, для чего используется заготовленный массив диагностических данных. Сравнивая состояние контактов приборов эталонного и контролируемого блоков, определяется функция, при вьтолнении которой произопшо несравнение. 1 з.п. ф-лы, 6 ил.

5

О

0

5

для выполнения прибором данной функции. Прибор считается проверен- jHbiM полностью, если он в процессе выдачи теста на входы контролируемого цифрового блока выполняет полный набор функций, определяемый техни- . ческой документацией на этот прибор.

Обычно же в процессе тестирования прибор выполняет некоторые свои функции многократно (например, приборы, обеспечивакнцие многотактный доступ к встроенной памяти цифрового блока, триггеры многоразрядных делителей частоты и т.п.). Если т акая информация используется в качестве диагностической, она избыточная.

Необходимо получить диагностическую информацию минимальной длины о всех приборах, входящих в состав контролируемого цифрового блока, а затем использовать ее при локализации неисправности.

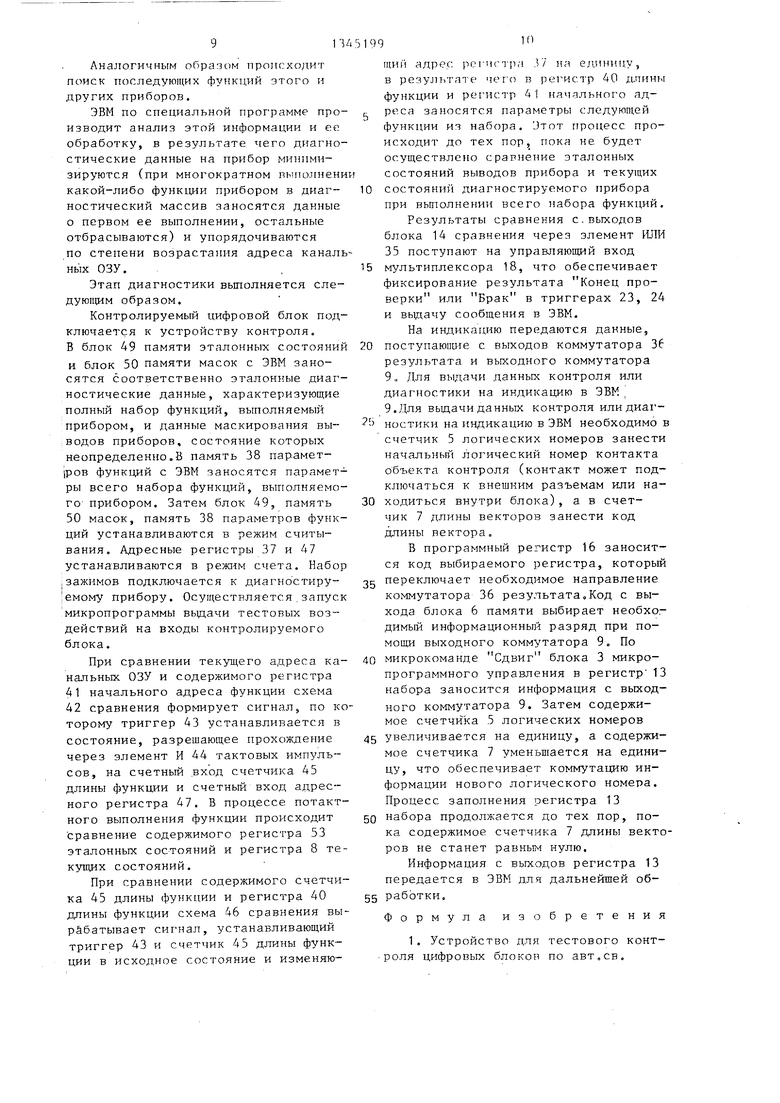

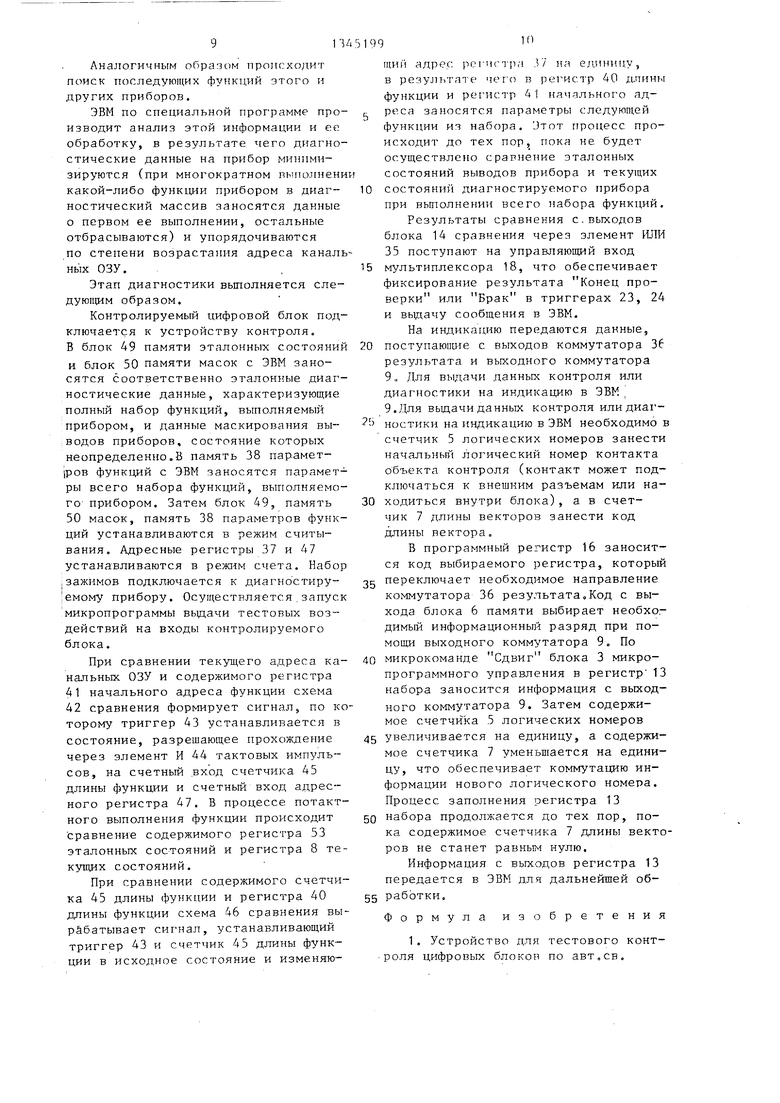

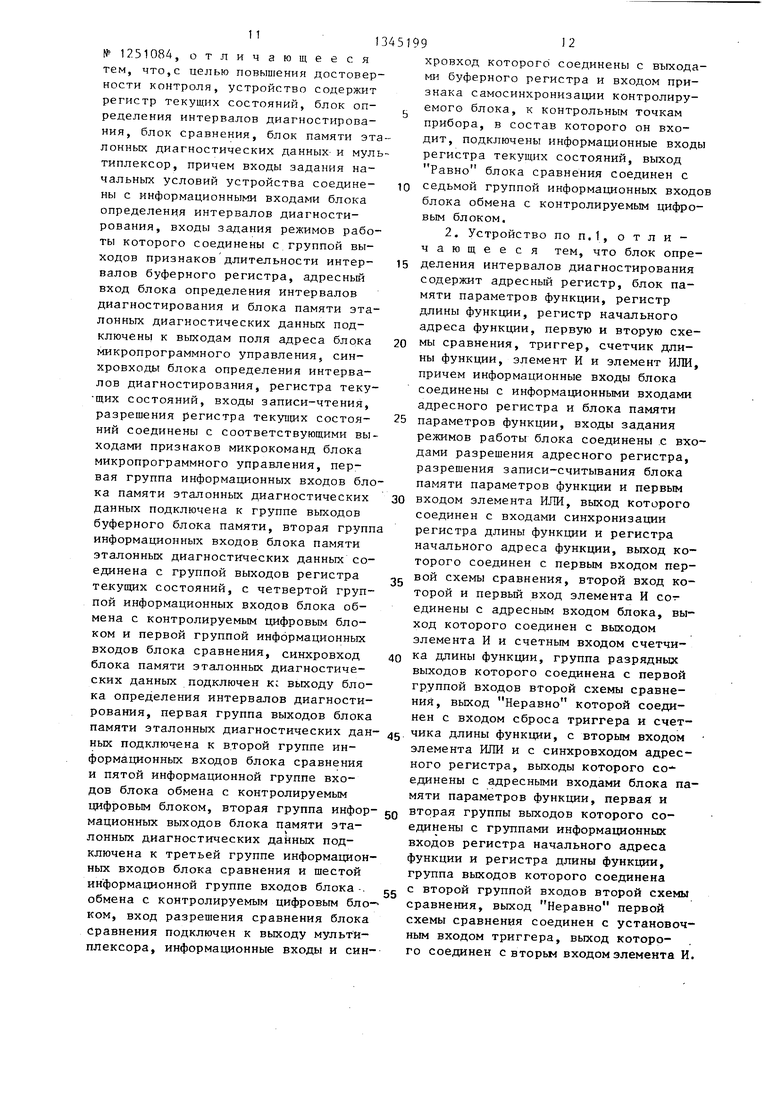

На фиг.1 представлена функциональная схема устройства; на фиг.2 - то же, блока микропрограммного управления; на фиг.З - то же, блока обмена с контролируемым цифровым блоком; на

фиг,4 - то же, блока определения интервалов диагностирования;на фиг,5 - то же, блока памяти эталонных диагностических данных; на фиг,6 - то же, мультиплексора.

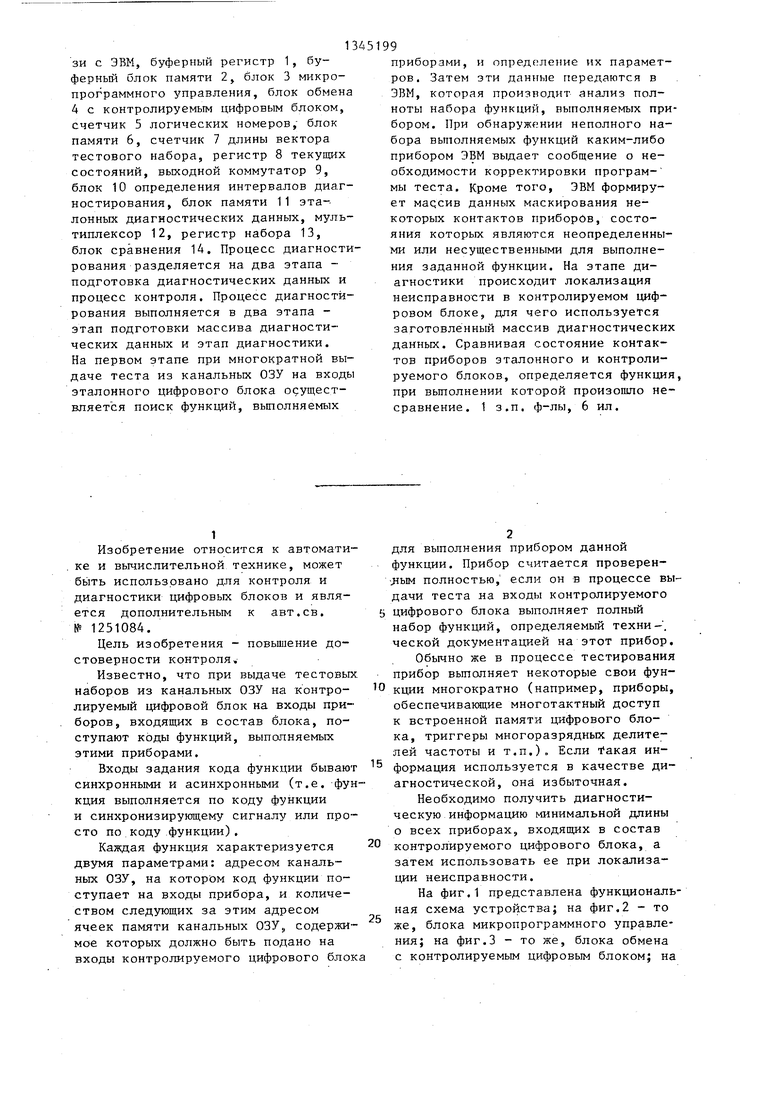

Устройство (фиг.1) содержит входную и выходную шины связи с ЭВМ, буферный регистр 1, буферный блок 2 памяти, блок 3 микропрограммного управления, блок 4 обмена с контроли- руемьп цифровым блоком, счетчик 5 логических номеров, блок 6 памяти, счетчик 7 длины вектора тестового набора, регистр 8 текущих состояний, выходной коммутатор 9, блок 10 определения интервалов диагностирования, блок 11 памяти эталонных диагностических данных, мультиплексор 12, регистр 13 набора, блок 14 сравнения.

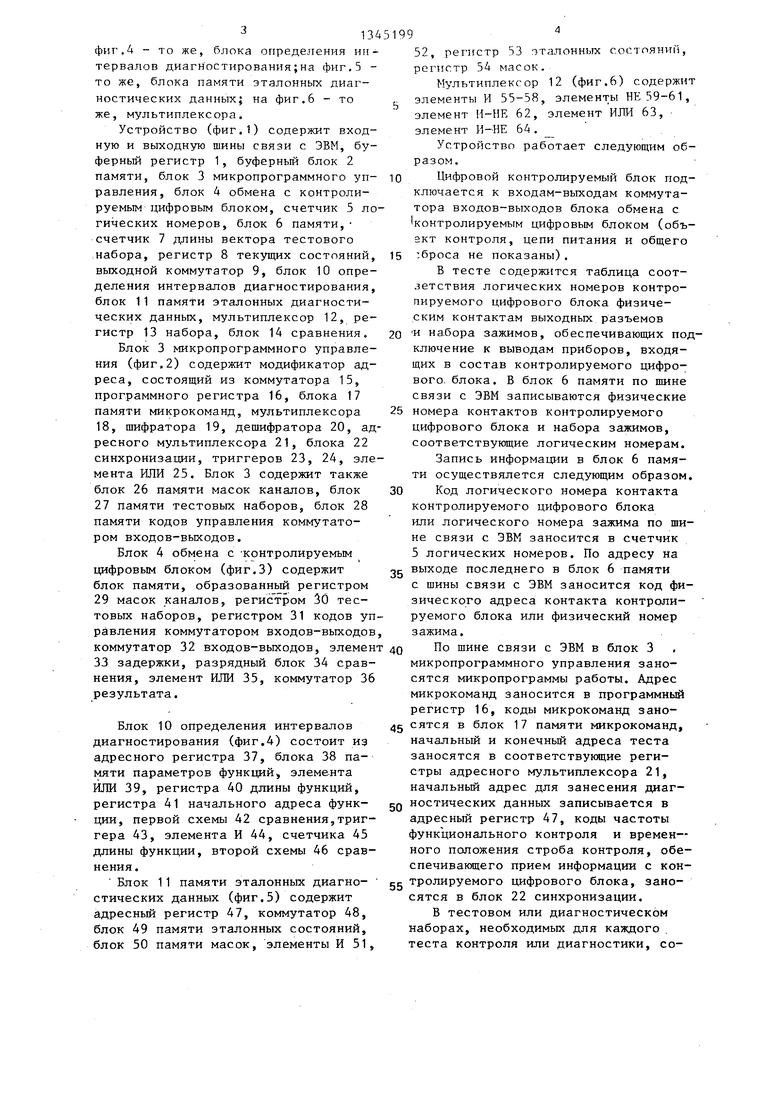

Блок 3 микропрограммного управления (фиг.2) содержит модификатор адреса, состоящий из коммутатора 15, программного регистра 16, блока 17 памяти микрокоманд, мультиплексора 18, шифратора 19, дешифратора 20, адресного мультиплексора 21, блока 22 синхронизации, триггеров 23, 24, элемента ИЛИ 25. Блок 3 содержит также блок 26 памяти масок каналов, блок 27 памяти тестовых наборов, блок 28 памяти кодов управления коммутатором входов-выходов.

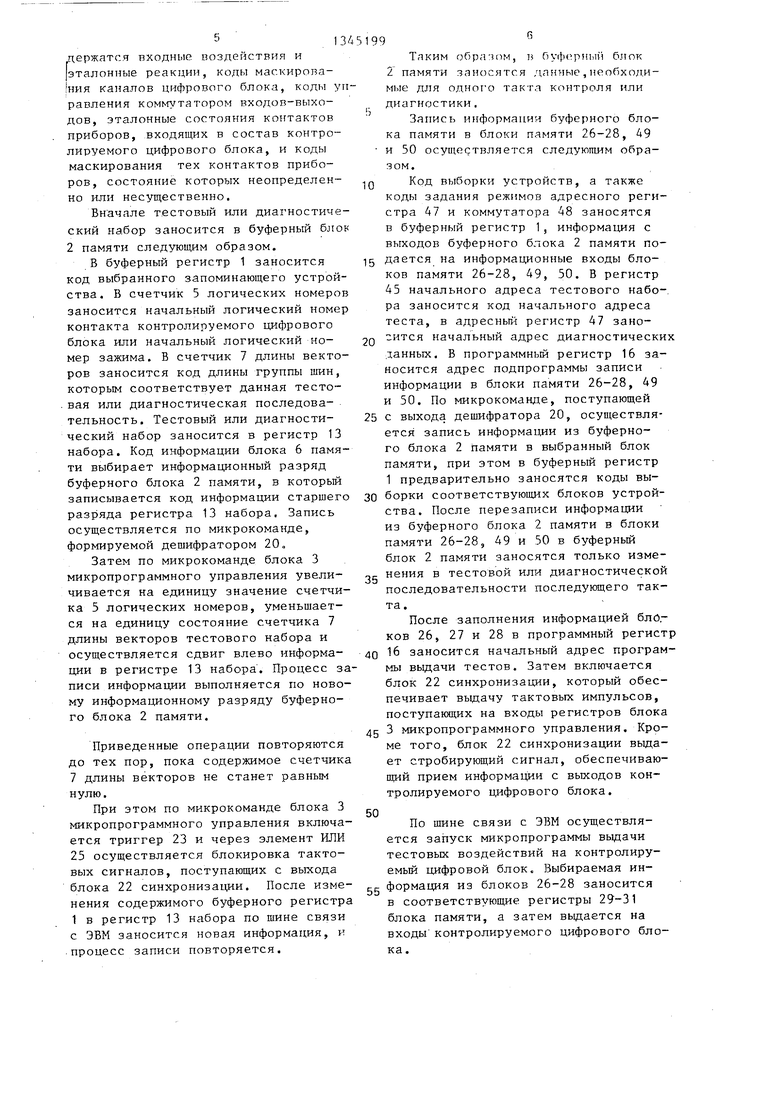

Блок 4 обмена с контролируемым цифровым блоком (фиг.З) содержит блок памяти, образованный регистром 29 масок каналов, регистром 30 тестовых наборов, регистром 31 кодов управления коммутатором входов-выходов коммутатор 32 входов-выходов, элемен 33 задержки, разрядный блок 34 сравнения, элемент ИЛИ 35, коммутатор 36 результата.

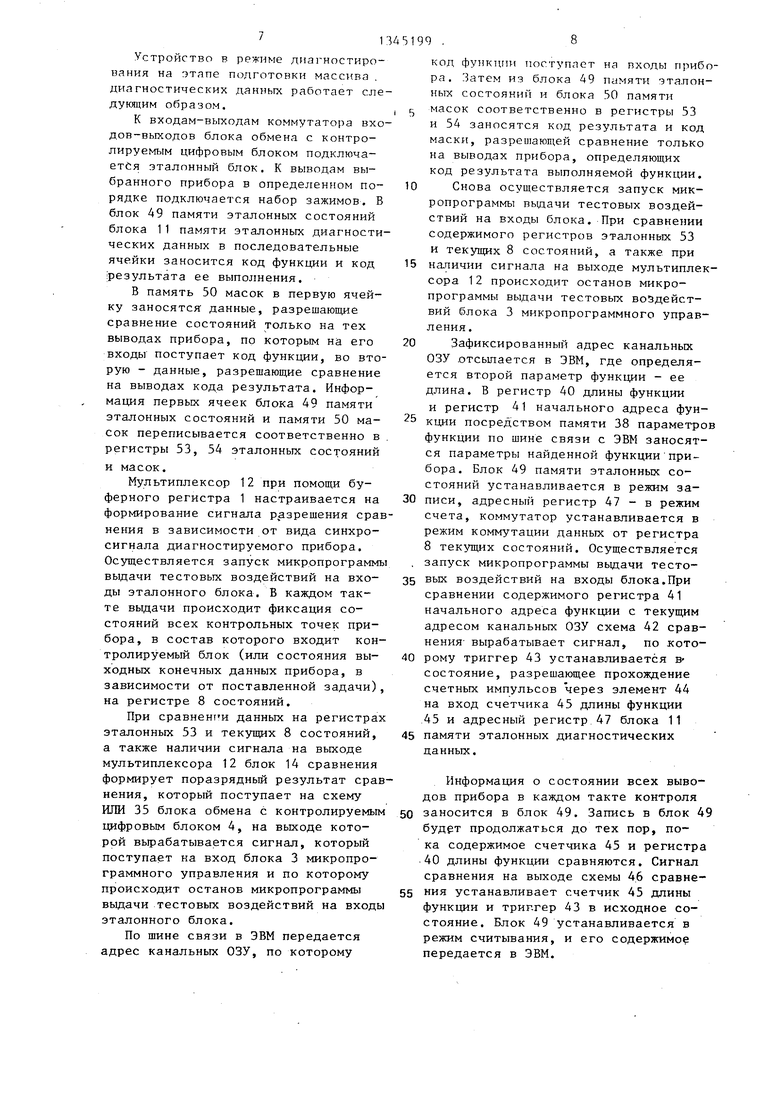

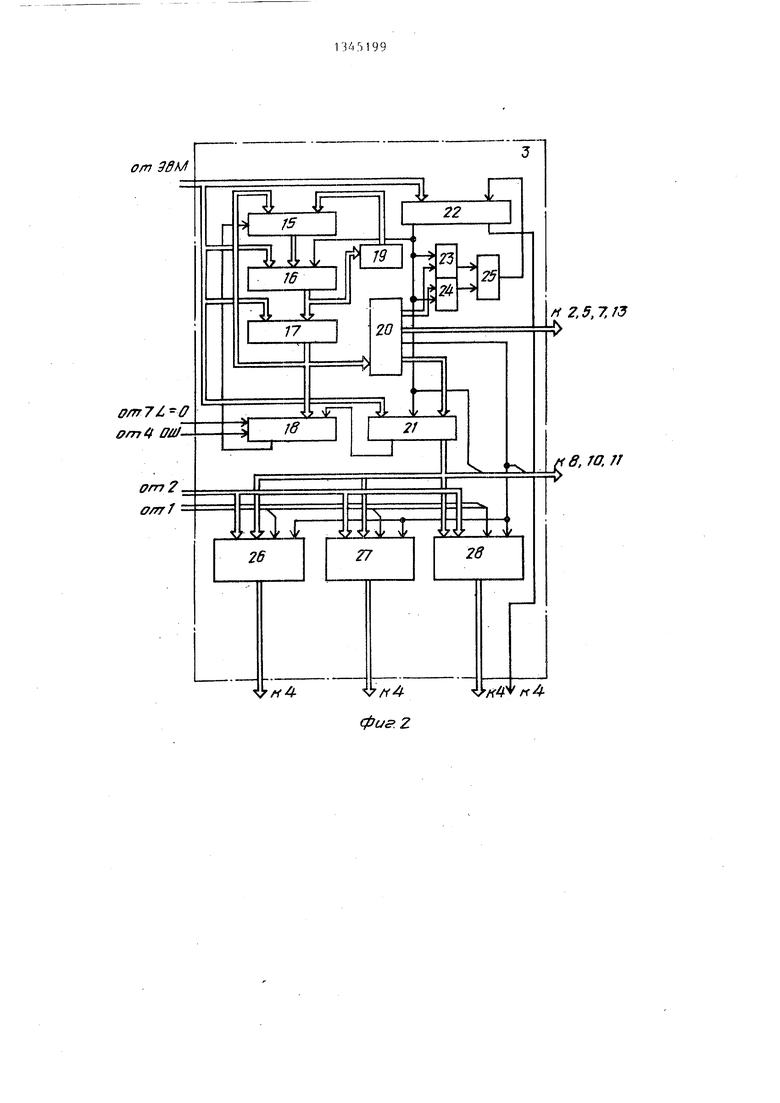

Блок 10 определения интервалов диагностирования (фиг.4) состоит из адресного регистра 37, блока 38 па- млти параметров функций, элемента ИЛИ 39, регистра 40 длины функций, регистра 41 начального адреса функции, первой схемы 42 сравнения,триггера 43, элемента И 44, счетчика 45 длины функции, второй схемы 46 сравнения.

Блок 11 памяти эталонных диагно- стических данных (фиг.5) содержит адресный регистр 47, коммутатор 48, блок 49 памяти эталонных состояний, блок 50 памяти масок, элементы И 51,

5

0

5

0

52, регистр 53 эталонных состояний, регистр 54 масок.

Мультиплексор 12 (фиг.6) содержит элементы И 55-58, элементы НЕ 59-61, элемент И-НЕ 62, элемент ИЛИ 63, элемент И-НЕ 64,

Устройство работает следующим образом.

Цифровой контролируемый блок подключается к входам-выходам коммутатора входов-выходов блока обмена с контролируемым цифровым блоком (объект контроля, цепи питания и общего :броса не показаны),

В тесте содержится таблица соот- зетствия логических номеров контролируемого цифрового блока физическим контактам выходных разъемов И набора зажимов, обеспечивающих подключение к выводам приборов, входящих в состав контролируемого цифрового, блока. В блок 6 памяти по шине связи с ЭВМ записываются физические номера контактов контролируемого цифрового блока и набора зажимов, соответствующие логическим номерам.

Запись информации в блок 6 памяти осуществялется следующим образом,

Код логического номера контакта контролируемого цифрового блока или логического номера зажима по шине связи с ЭВМ заносится в счетчик 5 логических номеров. По адресу на выходе последнего в блок 6 памяти с шины связи с ЭВМ заносится код физического адреса контакта контролируемого блока или физический номер зажима.

По шине связи с ЭВМ в блок 3 микропрограммного управления заносятся микропрограммы работы. Адрес микрокоманд заносится в программный регистр 16, коды микрокоманд зано- 5 сятся в блок 17 памяти микрокоманд, начальный и конечный адреса теста заносятся в соответствующие регистры адресного мультиплексора 21, начальный адрес для занесения диагностических данных записывается в адресный регистр 47, коды частоты функционального контроля и времен- ного положения строба контроля, обеспечивающего прием информации с кон- g тролируемого цифрового блока, заносятся в блок 22 синхронизации.

В тестовом или диагностическом наборах, необходимых для каждого теста контроля или диагностики, со5

0

, IS

держатся входные воздействия и эталонные реакции, коды маскирова- ния каналов цифрового блока, коды управления KOMNWTaropoM входов-выходов, эталонные состояния контактов приборов, входящих в состав контролируемого цифрового блока, и коды маскирования тех контактов приборов, состояние которых неопределенно или несущественно.

Бн ачале тестовый или диагностический набор заносится в буферный блок 2 памяти следующим образом.

В буферный регистр 1 заносится код выбранного запоминающего устройства. В Счетчик 5 логических номеров заносится начальный логический номер контакта контролируемого цифрового блока или начальный логический номер зажима. В счетчик 7 длины векторов заносится код длины труппы шин, которым соответствует данная тесто- .вая или диагностическая последовательность. Тестовый или диагностический набор заносится в регистр 1.3 набора. Код информации блока 6 памяти выбирает информационный разряд буферного блока 2 памяти, в которьм записывается код информации старшего разряда регистра 13 набора. Запись осуществляется по микрокоманде, формируемой дешифратором 20,

Затем по микрокоманде блока 3 микропрограммного управления увеличивается на единицу значение счетчика 5 логических номеров, уменьшается на единицу состояние счетчика 7 длины векторов тестового набора и осуществляется сдвиг влево информации в регистре 13 набора. Процесс записи информации выполняется по новому информационному разряду буферного блока 2 памяти.

Приведенные операции повторяются до тех пор, пока содержимое счетчика 7 длины векторов не станет равным нулю.

При этом по микрокоманде блока 3 микропрограммного управления включается триггер 23 и через элемент ИЛИ 25 осуществляется блокировка тактовых сигналов, поступающих с выхода блока 22 синхронизации. После изменения содержимого буферного регистра 1 в регистр 13 набора по шине связи с ЭВМ заносится новая информация, и процесс записи повторяется.

R

Таким образом, ij буферный блок 2 памяти заносятся данмые,необходимые для одного такта контроля или диагностики.

-J

Запись информации буферного блока памяти в блоки памяти 26-28, 49 и 50 осуществляется следующим образом.

0 Код выборки устройств, а также коды задания режимов адресного регистра 47 и коммутатора 48 заносятся в буферный регистр 1, информация с выходов буферного блока 2 памяти по5 дается на информационные входы блоков памяти 26-28, 49, 50. В регистр 45 начального адреса тестового набо-, ра заносится код начального адреса теста, в адресный регистр 47 заноQ сится начальный адрес диагностических данных. В программный регистр 16 заносится адрес подпрограммы записи информации в блоки памяти 26-28, 49 и 50. По микрокоманде, поступающей

5 с выхода дешифратора 20, осуществляется запись информации из буферного блока 2 памяти в выбранный блок памяти, при этом в буферный регистр 1 предварительно заносятся коды вы0 борки соответствующих блоков устройства. После перезаписи информации из буферного блока 2 памяти в блоки памяти 26-28, 49 и 50 в буферньш блок 2 памяти заносятся только изменения в тестовой или диагностической последовательности последующего такта.

После заполнения информацией бло,- ков 26, 27 и 28 в программный регистр

0 16 заносится начальный адрес программы выдачи тестов. Затем включается блок 22 синхронизации, который обеспечивает выдачу тактовых импульсов, поступающих на входы регистров блока

5 3 микропрограммного управления. Кроме того, блок 22 синхронизации выдает стробирующий сигнал, обеспечивающий прием информацией с выходов контролируемого ид фрового блока.

0

По шине связи с ЭВМ осуществляется запуск микропрограммы выдачи тестовых воздействий на контролируемый цифровой блок. Выбираемая ин- д формация из блоков 26-28 заносится в соответствуюшд1е регистры 29-31 блока памяти, а затем выдается на входы контролируемого цифрового блока .

5

Устройство в режиме диагностирования на этапе подготовки массива диагностических данных работает следующим образом.

К входам-выходам коммутатора входов-выходов блока обмена с контролируемым цифровым блоком подключается эталонный блок. К выводам выбранного прибора в определенном порядке подключается набор зажимов. В блок А9 памяти эталонных состояний блока 11 памяти эталонных диагностических данных в последовательные ячейки заносится код функции и код результата ее выполнения.

В память 50 масок в первую ячейку заносятся данные, разрешающие сравнение состояний только на тех выводах прибора, по которым на его входы поступает код функции, во вторую - данные, разрешающие сравнение на выводах кода результата. Информация первых ячеек блока 49 памяти эталонных состояний и памяти 50 масок переписывается соответственно в регистры 53, 54 эталонных состояний

и масок.

Мультиплексор 12 при помощи буферного регистра 1 настраивается на формирование сигнала разрешения сравнения в зависимости от вида синхросигнала диагностируемого прибора. Осуществляется запуск микропрограммы вьщачи тестовых воздействий на входы эталонного блока. В каждом такте вьщачи происходит фиксация состояний всех контрольных точек прибора, в состав которого входит контролируемый блок (или состояния выходных конечных данных прибора, в зависимости от поставленной задачи), на регистре 8 состояний.

При сравненг и данных на регистрах эталонных 53 и текущих 8 состояний, а также наличии сигнала на выходе мультиплексора 12 блок 14 сравнения формирует поразрядный результат сравнения, который поступает на схему ИЛИ 35 блока обмена с контролируемым цифровым блоком 4, на выходе которой вырабатывается сигнал, который поступает на вход блока 3 микропрограммного управления и по которому происходит останов микропрограммы выдачи тестовых воздействий на входы эталонного блока.

По шине связи в ЭВМ передается адрес канальных ОЗУ, по которому

код функции иоступлет на входы прибора. Затем из блока 49 памяти эталонных состояний и блока 50 памяти

масок соответственно в регистры 53 и 54 заносятся код результата и код маски, разрешающей сравнение только на выводах прибора, определяющих код результата выполняемой функции.

Снова осуществляется запуск микропрограммы выдачи тестовых воздействий на входы блока. При сравнении содержимого регистров эталонных 53 и текущих 8 состояний, а также при

наличии сигнала на выходе мультиплексора 12 происходит останов микропрограммы выдачи тестовых воздействий блока 3 микропрограммного управления.

Зафиксированный адрес канальных ОЗУ .отсылается в ЭВМ, где определяется второй параметр функции - ее длина. В регистр 40 длины функции и регистр 41 начального адреса функции посредством памяти 38 параметров функции по шине связи с ЭВМ заносятся параметры найденной функции прибора. Блок 49 памяти эталонных состояний устанавливается в режим записи, адресный регистр 47 - в режим

счета, коммутатор устанавливается в

режим коммутации данных от регистра

8 текущих состояний. Осуществляется

запуск микропрограммы выдачи тестовых воздействий на входы блока.При сравнении содержимого регистра 41 начального адреса функции с текущим адресом канальных ОЗУ схема 42 сравнения- вырабатывает сигнал, по которому триггер 43 устанавливается в- состояние, разрешающее прохождение счетных импульсов через элемент 44 на вход счетчика 45 длины функции 45 и адресный регистр 47 блока 11

памяти эталонных диагностических данных.

Информация о состоянии всех выводов прибора в каждом такте контроля

заносится в блок 49. Запись в блок 49 будет продолжаться до тех пор, пока содержимое счетчика 45 и регистра 40 длины функции сравняются. Сигнал сравнения на выходе схемы 46 сравнения устанавливает счетчик 45 длины функции и триг-гер 43 в исходное состояние. Блок 49 устанавливается в режим считывания, и его содержимое передается в ЭВМ.

Аналогичным обрагзом происходит поиск последующих функций этого и других приборов.

ЭВМ по специальной программе производит анализ этой информации и ее обработку, в результате; чего диагностические данные на прибор минимизируются (при многократном выполнени какой-либо функвди прибором в диагностический массив заносятся данные о первом ее выполнении, остальные отбрасываются) и упорядочиваются по степени возрастания адреса канальных ОЗУ.

Этап диагностики выполняется сле- дую11111м образом.

Контролируемый цифровой блок подключается к устройству контроля. В блок 49 памяти эталонных состояний и блок 50 памяти масок с ЭВМ заносятся соответственно эталонные диагностические данные, характеризующие полный набор функций, выполняемый прибором, и данные маскирования вы- :Водов приборов, состояние которых неопределенно„В память 38 параметров функций с ЭВМ заносятся параметры всего набора функций, выполняемого прибором. Затем блок 49, память 50 масок, память 38 параметров функций устанавливаются в режим считывания. Адресные регистры 37 и 47 устанавливаются в режим счета. Набор .зажимов подключается к диагностиру- ;емому прибору. Осуществляется.запуск микропрограммы выдачи тестовых воздействий на входы контролируемого блока.

При сравнении текущего адреса канальных ОЗУ и содержимого регистра

41начального адреса функции схема

42сравнения формирует сигнал, по которому триггер 43 устанавливается в состояние, разрешающее прохождение через элемент И 44 тактовых импульсов, на счетный вход счетчика 45 длины функции и счетный вход адресного регистра 47. Б процессе потакт- ного выполнения функции происходит сравнение содержимого регистра 53 эталонных состояний и регистра 8 текущих состояний.

При сравнении содержимого счетчика 45 длины функции и регистра 40 длины функции схема 46 сравнения вы- рйбатывает сигнал, устанавливающий триггер 43 и счетчик 45 длины функции в исходное состояние и изменяюnuii i адрес рсг-.и-тр.ч 37 на единицу,

в результате чег о в регистр 40 длины

функции и регистр 41 начального адреса заносятся параметры следуюп ей функции из набора. Этот процесс происходит до тех пор, пока не будет осуществлено сравнение эталонных состояний выводов прибора и текущих

состояний диагностируемого прибора при выполнении всего набора функций.

Результаты сравнения с,выходов блока 14 сравнения через элемент ИЛИ 35 поступают на управляющий вход

мультиплексора 18, что обеспечивает фиксирование результата Конец проверки или Брак в триггерах 23, 24 и выдачу сообщения в ЭВМ.

На индикацию передаются данные,

поступающие с выходов коммутатора 36 результата и выходного коммутатора 9, Для выдачр данных контроля или диагностики на индикацию в ЭВМ 9. Для выдачи данных контроля илидиах ностики на индикацию в ЭВМ необходимо в счетчик 5 логических номеров занести начальньЕй логический номер контакта объекта контроля (контакт может подключаться к внешним разъемам или находиться внутри блока), а в счет- 1-шк 7 длины векторов занести код длины вектора,

В программный регистр 16 заносится код выбираемого регистра, который

переключает необходимое направление коммутатора 36 результата,Код с выхода блока 6 памяти выбирает необходимый информационные разряд при помощи выходного коммутатора 9« По

микрокоманде Сдвиг блока 3 микропрограммного управления в регистр 13 набора заносится информация с выходного коммутатора 9. Затем содержимое счетчика 5 логических номеров

увеличивается на единицу, а содержимое счетчика 7 уменьшается на единицу, что обеспечивает коммутацию информации нового логического номера. Процесс заполнения регистра 13

набора продолжается до тех пор, пока содержимое счетчика 7 длины векторов не станет равньм нулю.

Информация с выходов регистра 13 передается в ЭВМ для дальнейшей обработки.

Формула изобретения

1, Устройство для тестового контроля цифровых блоков по авт.св.

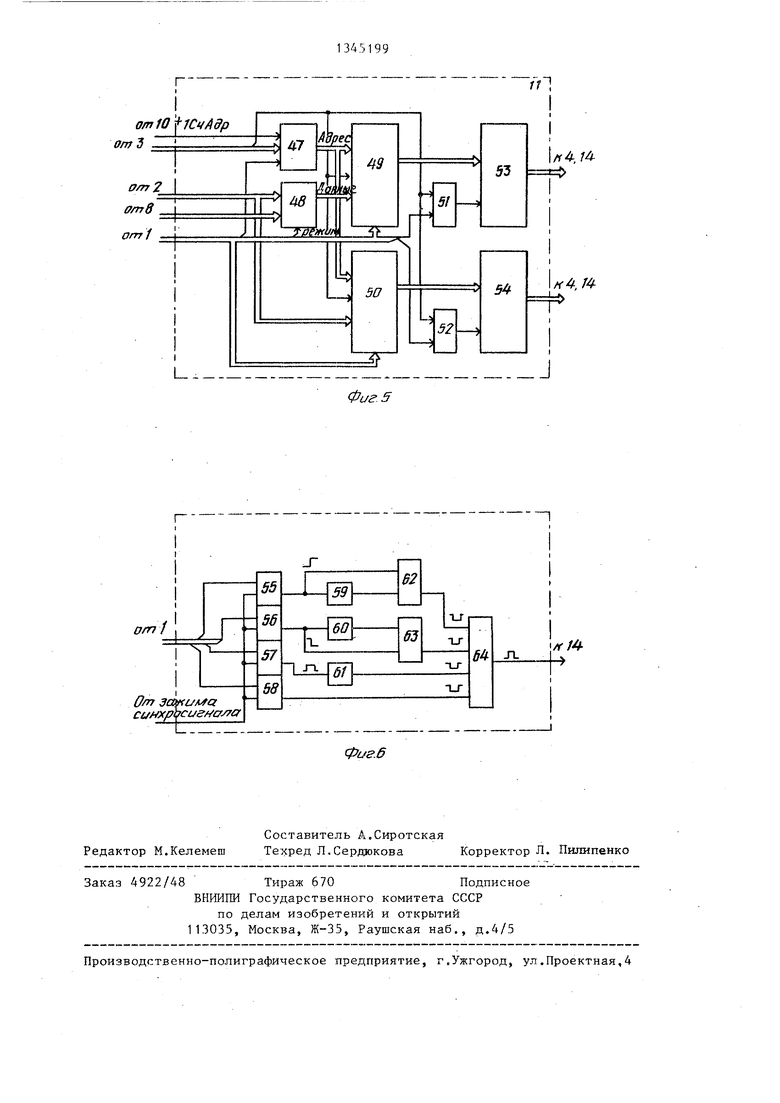

11

fp 1251084, отличающееся тем, что,с целью повышения достоверности контроля, устройство содержит регистр текущих состояний, блок определения интервалов диагностирования, блок сравнения, блок памяти эталонных диагностических данных- и мультиплексор, причем входы задания начальных условий устройства соединены с информационными входами блока определения интервалов диагностирования, входы задания режимов работы которого соединены с группой выходов признаков длительности интервалов буферного регистра, адресный вход блока определения интервалов диагностирования и блока памяти эталонных диагностических данных подключены к выходам поля адреса блока микропрограммного управления, син- хровходы блока определения интервалов диагностирования, регистра теку- щих состояний, входы записи-чтения, разрешения регистра текутцих состояний соединены с соответствующими выходами признаков микрокоманд блока микропрограммного управления, первая группа информационных входов блока памяти эталонных диагностических данных подключена к группе выходов буферного блока памяти, вторая групп информационных входов блока памяти эталонных диагностических данных соединена с группой выходов регистра текуЕцих состояний, с четвертой группой информационных входов блока обмена с контролируемым цифровым блоком и первой группой информационных входов блока сравнения, синхровход блока памяти эталонных диагностических данных подключен кс выходу блока определения интервалов диагностирования, первая группа выходов блока

П

памяти эталонных диагностических дан- 45 чика длины функции, с вторым входом

ных подключена к второй группе информационных входов блока сравнения и пятой информационной группе входов блока обмена с контролируемым цифровым блоком, вторая группа информационных выходов блока памяти эталонных диагностических данньк подключена к третьей группе информационных входов блока сравнения и шестой информационной группе входов блока -. обмена с контролируемым цифровым блоком, вход разрешения сравнения блока Сравнения подключен к выходу мультиплексора, информационные входы и синП45199

12

хровход которого соединены с выходами буферного регистра и входом признака самосинхронизации контролируемого блока, к контрольным точкам прибора, в состав которого он входит, подключены информационные входы регистра текущих состояний, выход Равно блока сравнения соединен с

седьмой группой информационных входов блока обмена с контролируемым цифровым блоком.

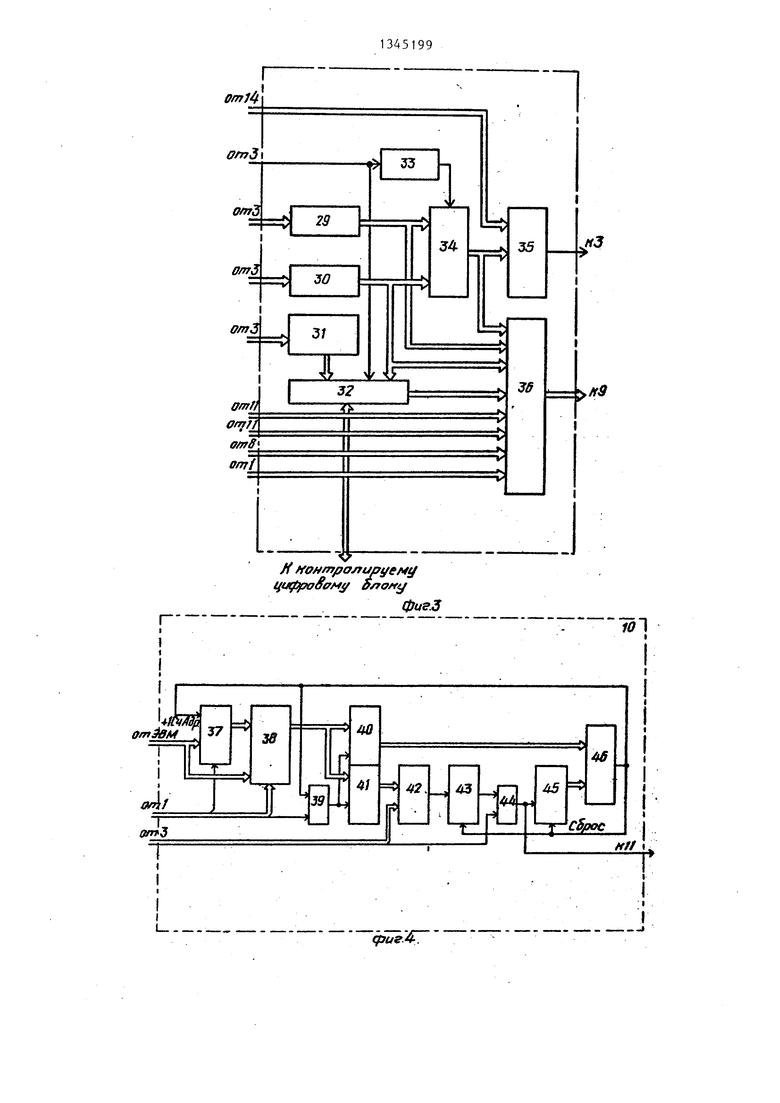

2. Устройство по П.1, отличающееся тем, что блок определения интервалов диагностирования содержит адресный регистр, блок памяти параметров функции, регистр длины функции, регистр начального адреса функции, первую и вторую схемы сравнения, триггер, счетчик длины функции, элемент И и элемент ИЛИ, причем информационные входы блока соединены с информационными входами адресного регистра и блока памяти

параметров функции, входы задания

режимов работы блока соединены с входами разрешения адресного регистра, разрешения записи-считывания блока памяти параметров функции и первым

входом элемента ИЛИ, выход которого соединен с входами синхронизации регистра длины функции и регистра начального адреса функции, выход которого соединен с первым входом первой схемы сравнения, второй вход которой и первый вход элемента И сот единены с адресным входом блока, выход которого соединен с выходом элемента И и счетным входом счетчика длины функции, группа разрядных выходов которого соединена с первой группой входов второй схемы сравнения, выход Неравно которой соединен с входом сброса триггера и счет0

5

элемента ИЛИ и с синхровходом адресного регистра, выходы которого со единены с адресными входами блока памяти параметров функции, первая и вторая группы выходов которого соединены с группами информационных входов регистра начального адреса функции и регистра длины функции, группа выходов которого соединена с второй группой входов второй схемы сравнения, выход Неравно первой схемы сравнения соединен с установочным входом триггера, выход которого соединен с вторьм входом элемента И.

от 9Bf

-О

ffm( Л4/.

Фиг.г

ff ffOH/npo upi/eMtl tftj /poSpM o/roffy

фигЗ

Idl

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1319079A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1997 |

|

RU2127447C1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для контроля блоков и узлов ЭВМ (является усовершенствованием а.с, 1251084). Цель изобретения - повьшение достоверности контроля. Устройство для тестового контроля цифровых блоков содержит входную и выходную шины свяфигЛ

,

37

3ff

тТ 4/

omS

43

45

y

cSfloc

Hit

I

I

I

дзиг

omlO IC Adp отЪ

L

Фиг.5

фие.6

Редактор М.Келемеш

Составитель А.Сиротская

Техред Л.Серлзокова Корректор Л. Пшшпенко

Заказ 4922/48 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-15—Публикация

1986-04-29—Подача