Изобретение относится к автоматике и вычислительной технике, а именно к устройствам проверки работоспособности и поиска дефектов дискретных узлов и блоков.

Целью изобретения является повышение полноты и достоверности диагностирования.

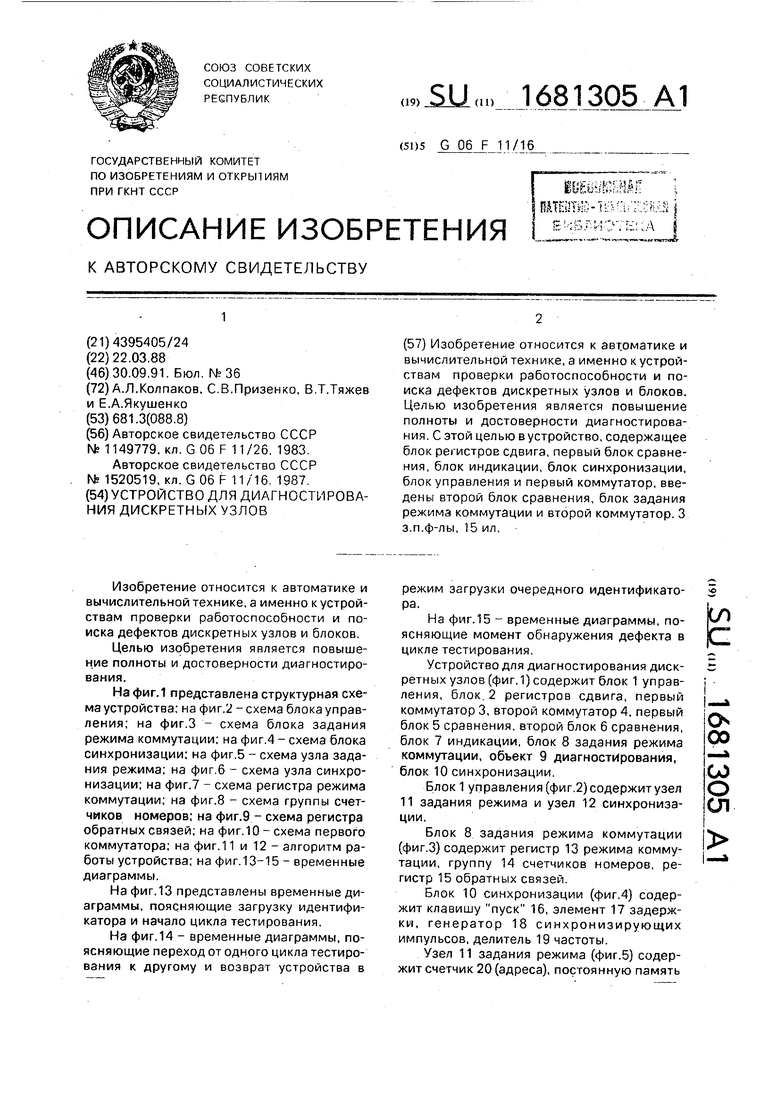

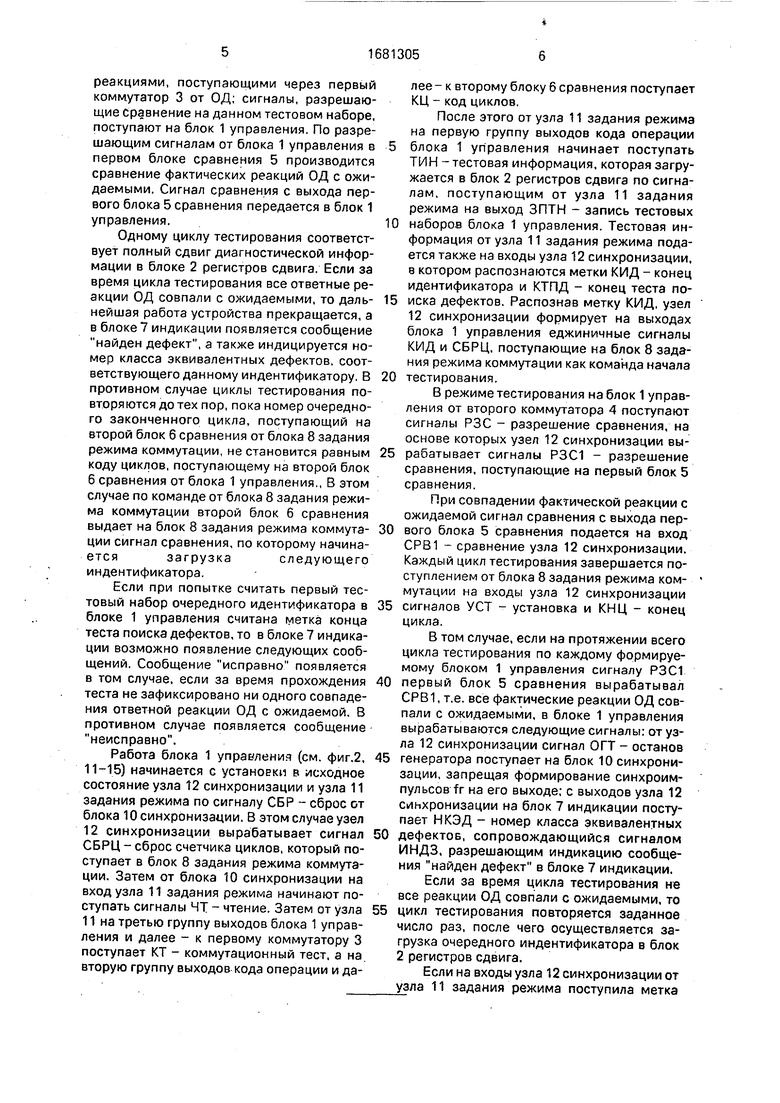

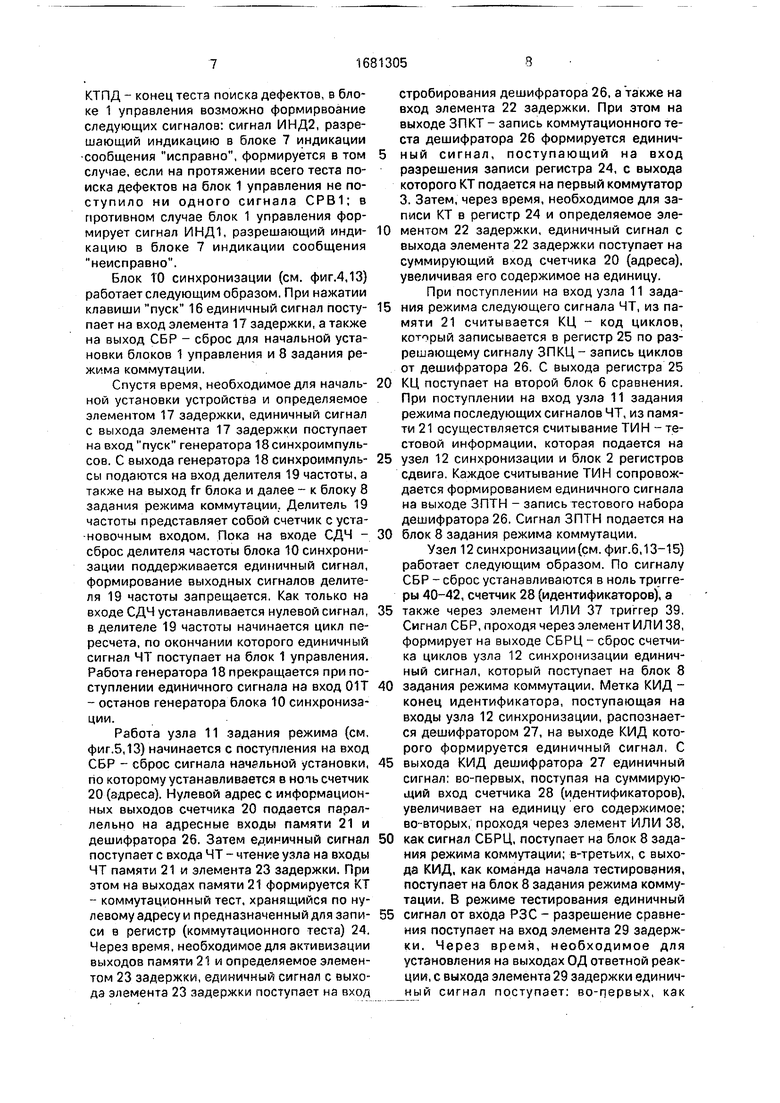

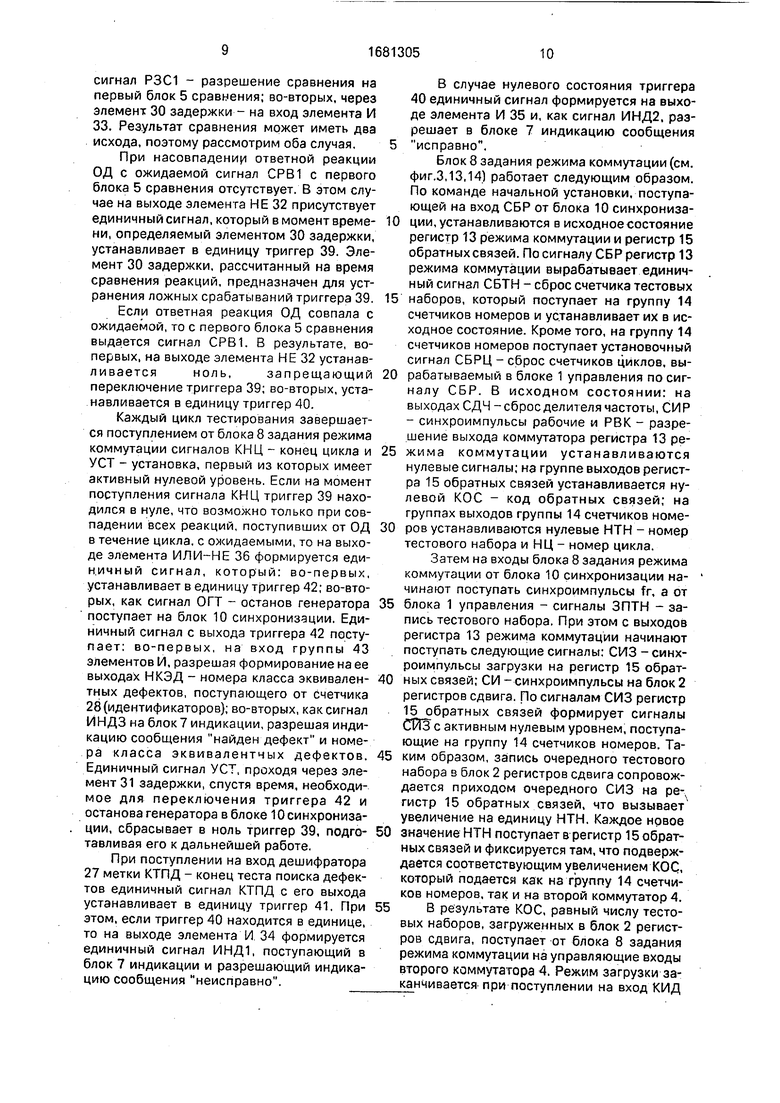

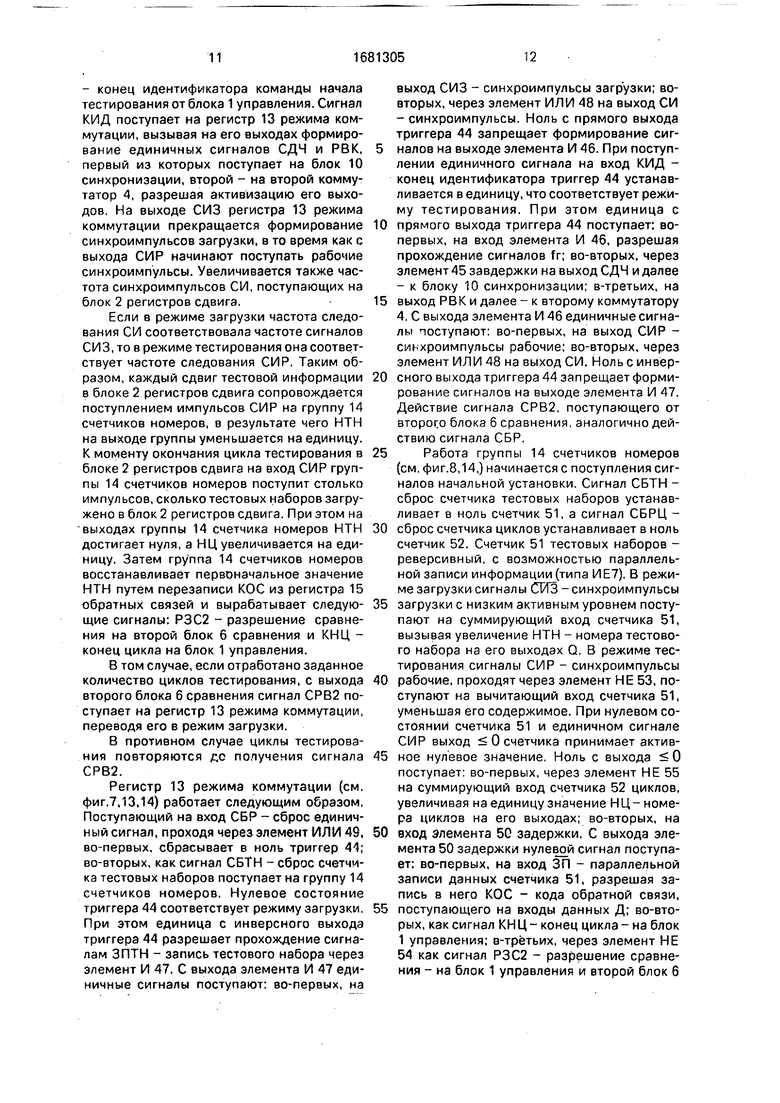

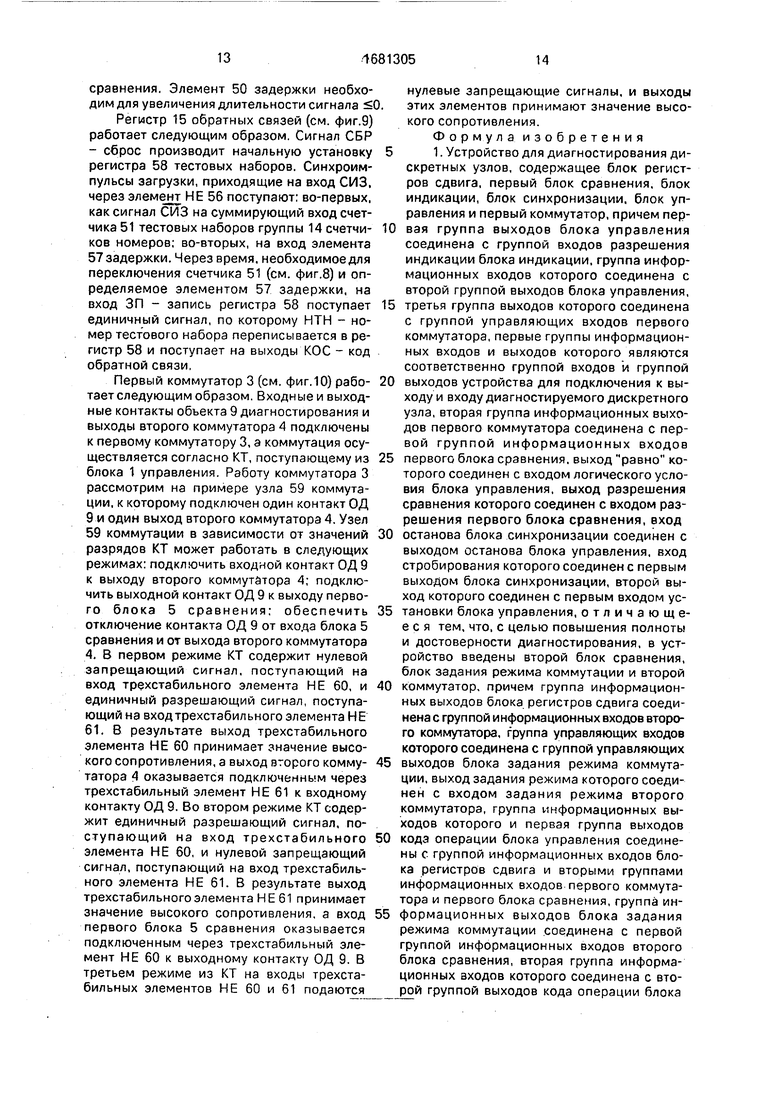

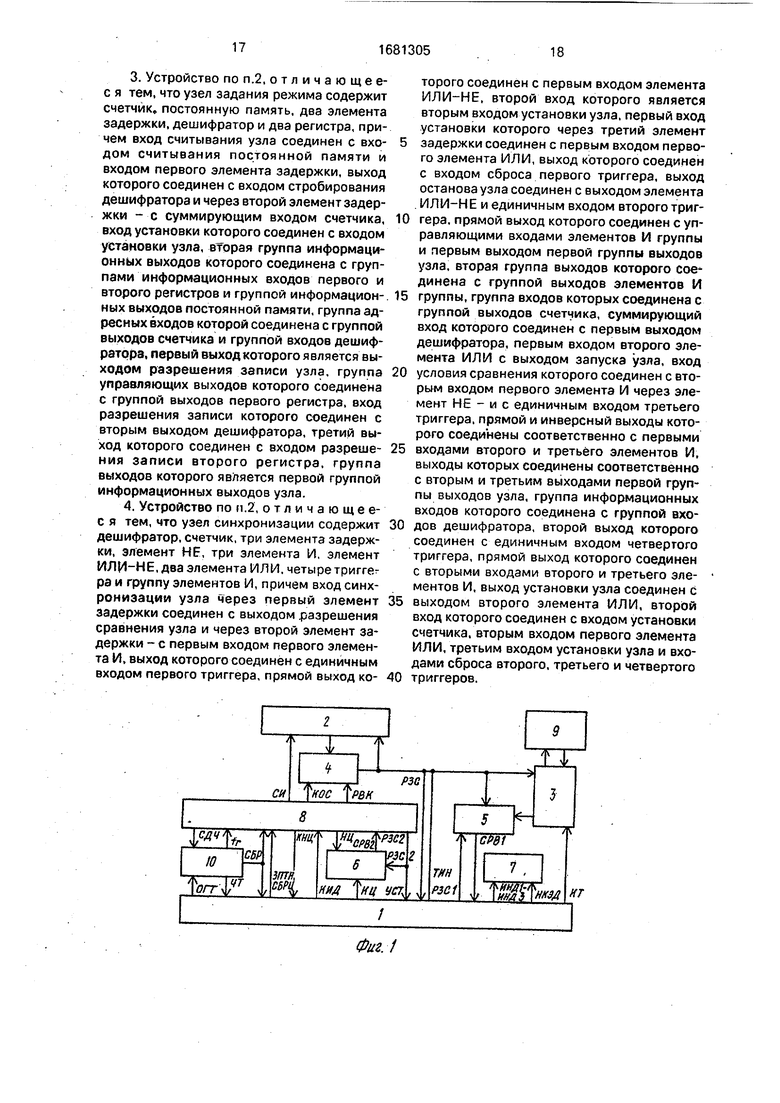

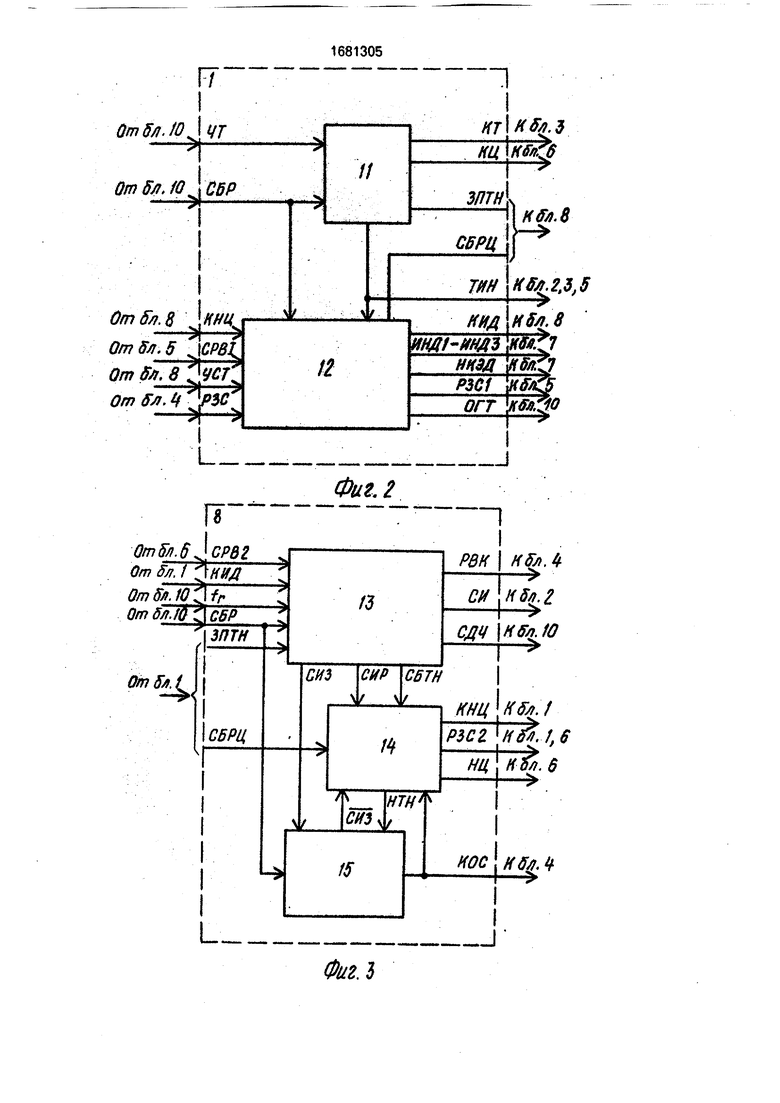

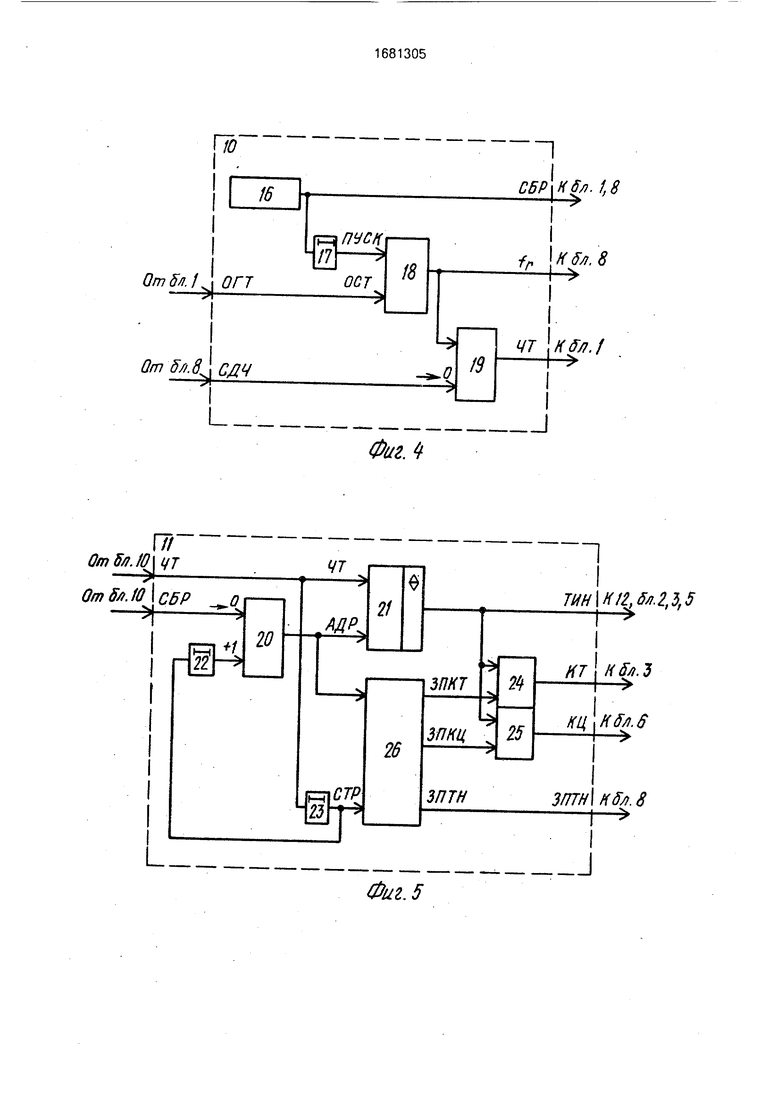

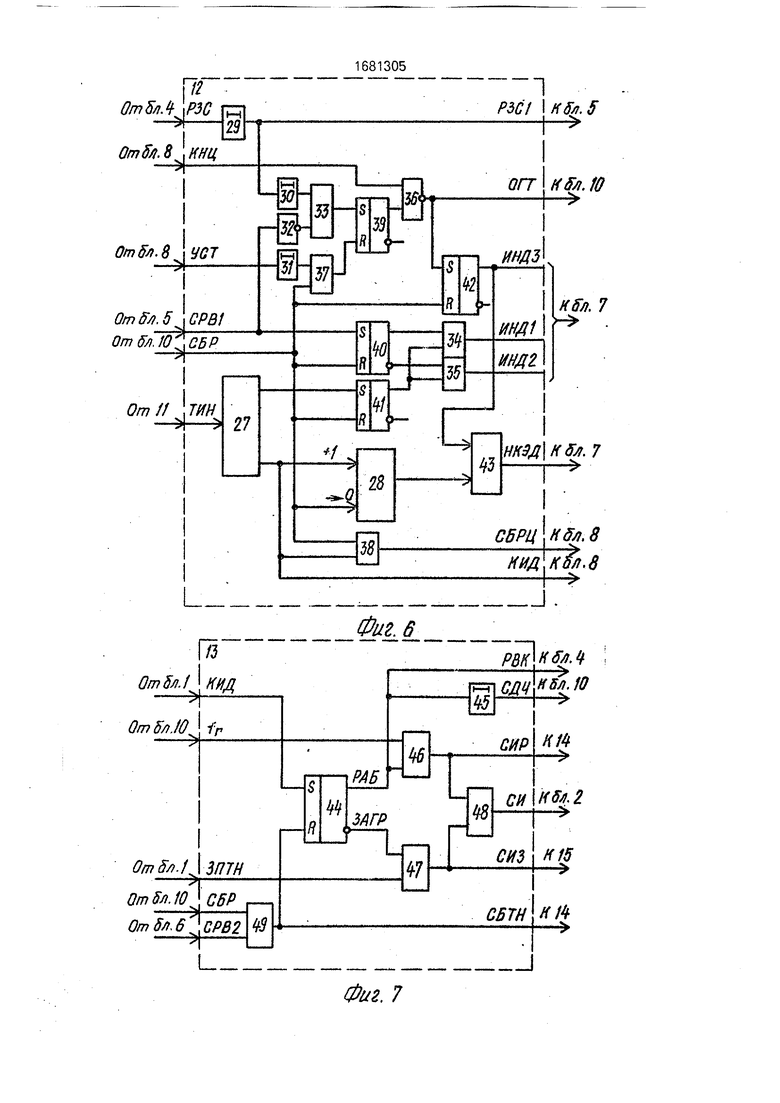

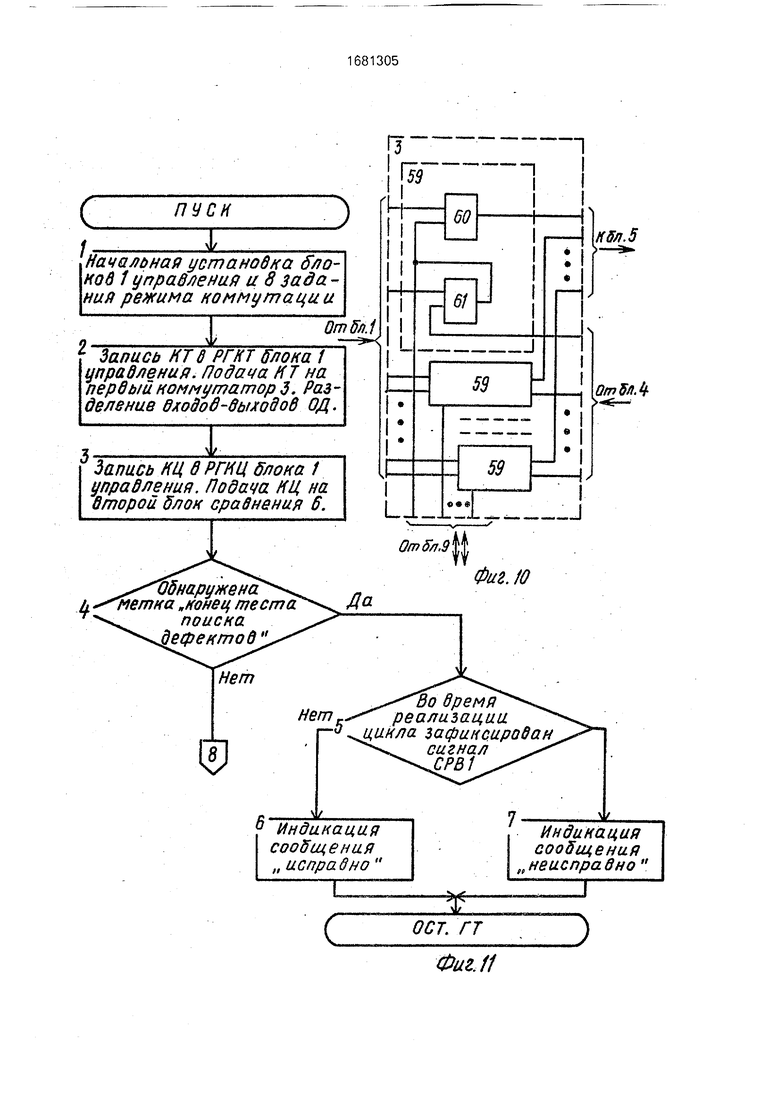

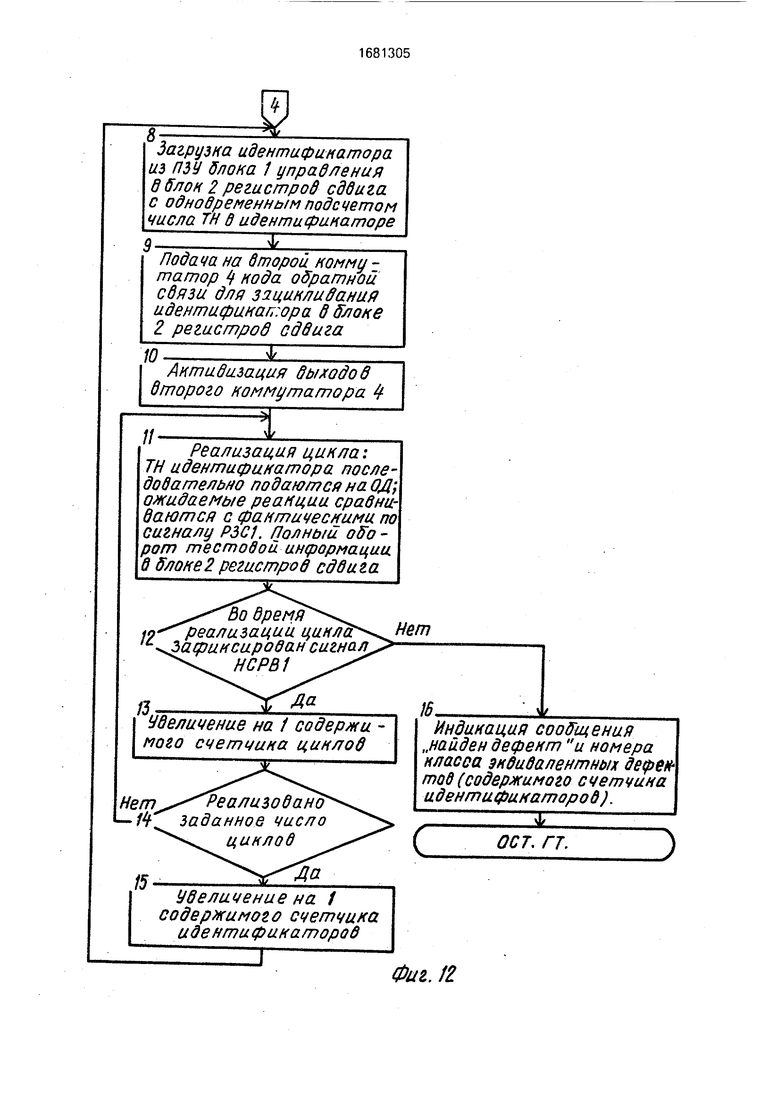

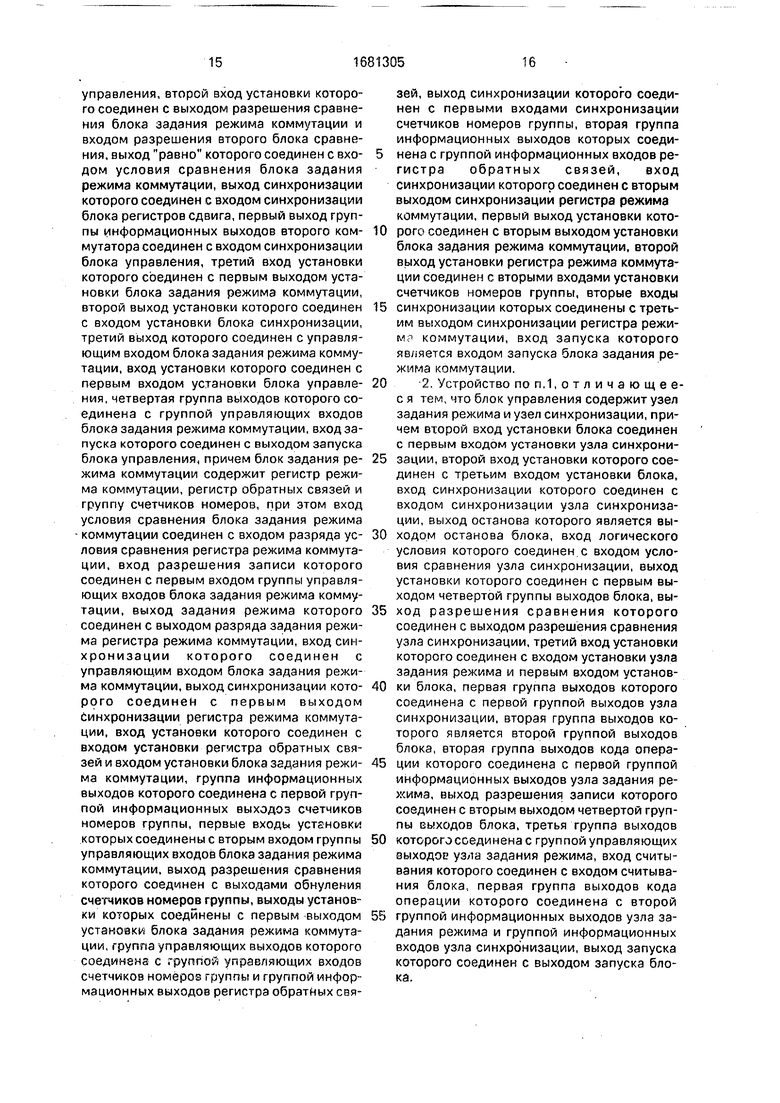

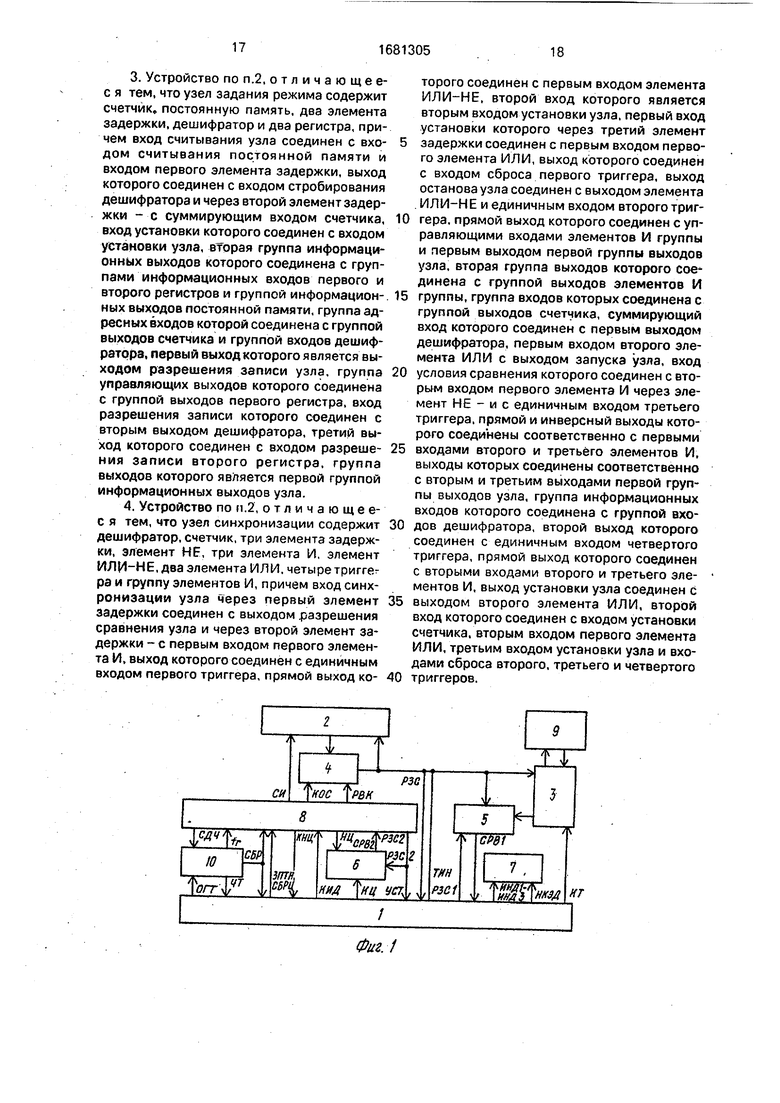

На фиг.1 представлена структурная схема устройства; на фиг.2 - схема блока управления; на фиг.З - схема блока задания режима коммутации; на фиг.4 - схема блока синхронизации; на фиг.5 - схема узла задания режима; на фиг.6 - схема узла синхронизации; на фиг.7 - схема регистра режима коммутации; на фиг.8 - схема группы счетчиков номеров; на фиг.9 - схема регистра обратных связей; на фиг. 10 - схема первого коммутатора; на фиг.11 и 12 - алгоритм работы устройства; на фиг.13-15 - временные диаграммы.

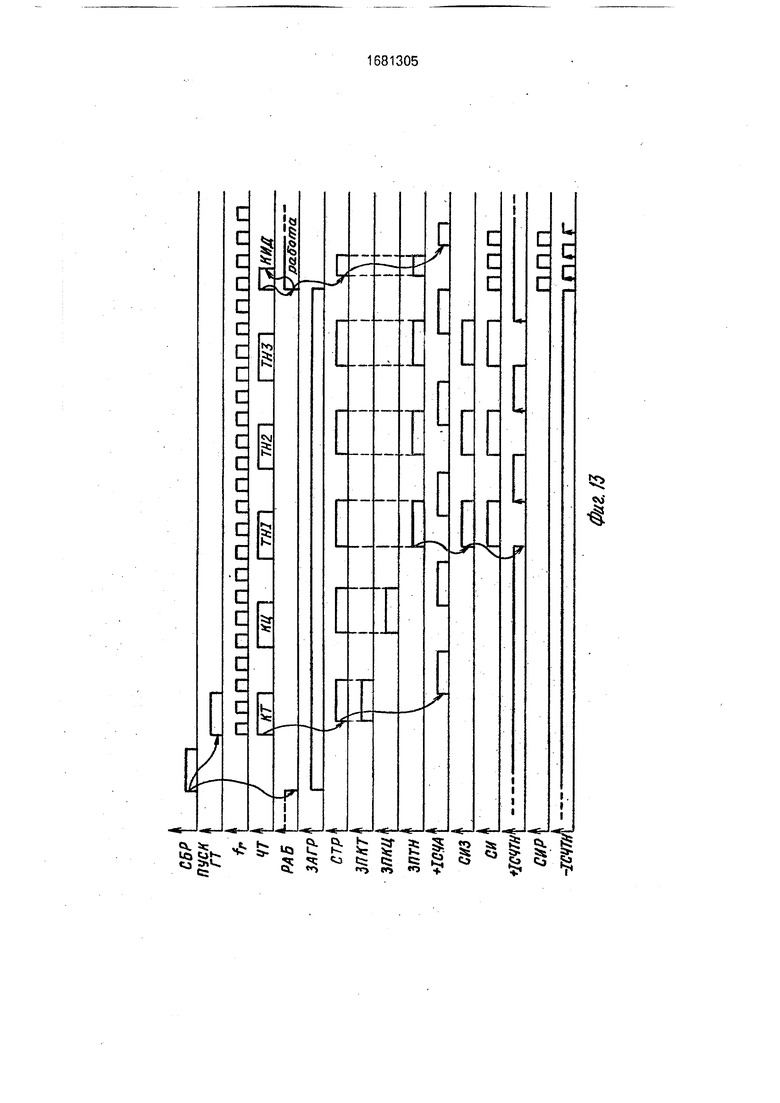

На фиг.13 представлены временные диаграммы, поясняющие загрузку идентификатора и начало цикла тестирования.

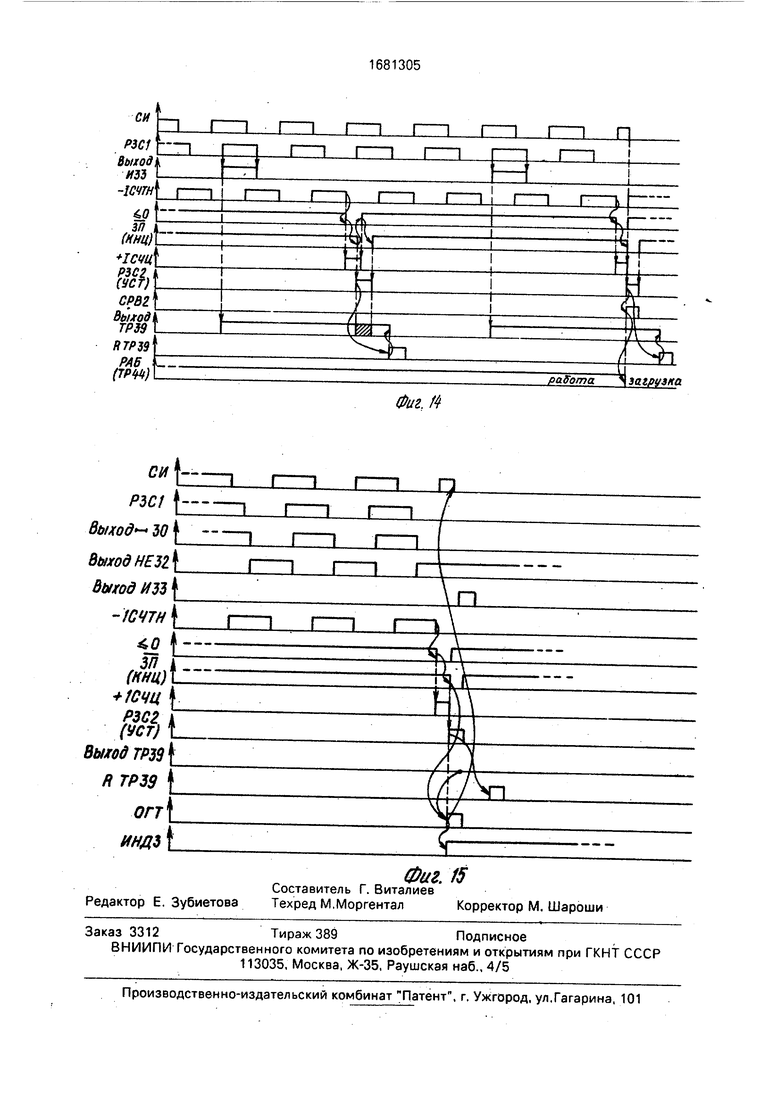

На фиг.14 - временные диаграммы, поясняющие переход от одного цикла тестирования к другому и возврат устройства в

режим загрузки очередного идентификатора.

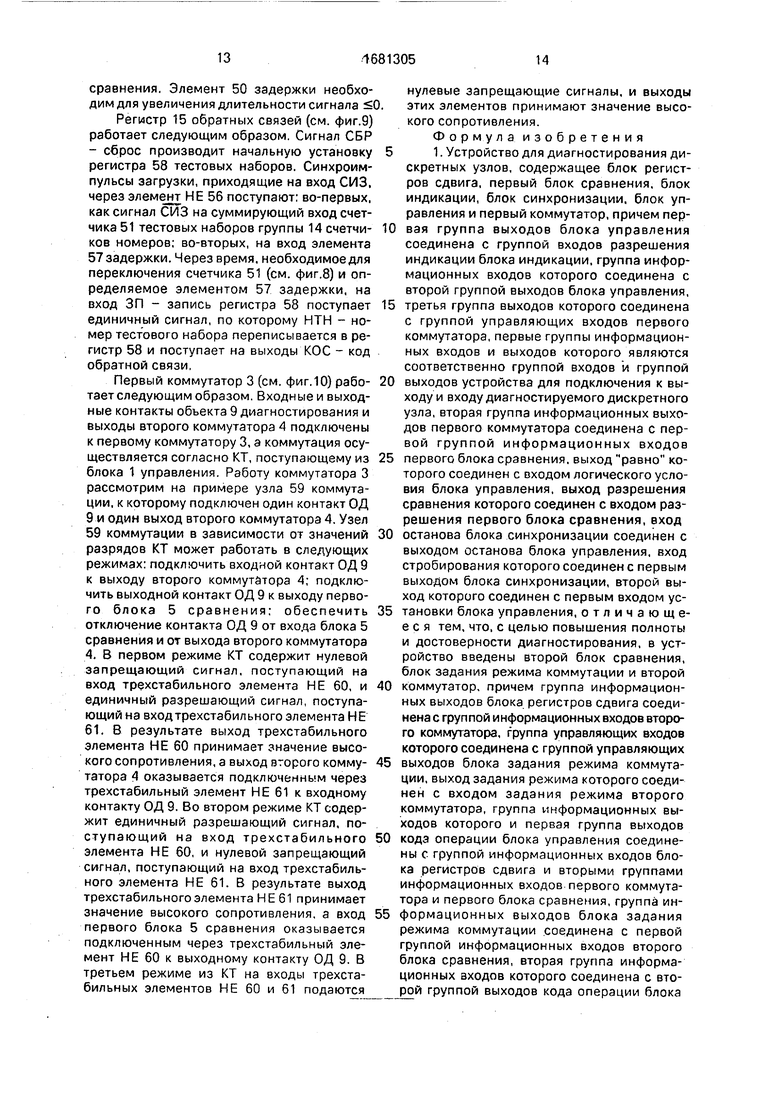

На фиг.15 - временные диаграммы, поясняющие момент обнаружения дефекта в цикле тестирования.

Устройство для диагностирования дискретных узлов (фиг.1) содержит блок 1 управления, блок. 2 регистров сдвига, первый коммутатор 3, второй коммутатор 4, первый блок 5 сравнения, второй блок 6 сравнения, блок 7 индикации, блок 8 задания режима коммутации, объект 9 диагностирования, блок 10 синхронизации.

Блок 1 управления (фиг.2) содержит узел 11 задания режима и узел 12 синхронизации.

Блок 8 задания режима коммутации (фиг.З) содержит регистр 13 режима коммутации, группу 14 счетчиков номеров, регистр 15 обратных связей.

Блок 10 синхронизации (фиг.4) содержит клавишу пуск 16, элемент 17 задержки, генератор 18 синхронизирующих импульсов, делитель 19 частоты.

Узел 11 задания режима (фиг.5) содержит счетчик 20 (адреса), постоянную память

сь

00

со

о ел

21, элементы задержки 22,23, регистр 24 (коммутационного теста), регистр 25 (кода циклов), дешифратор 26.

Узел 12 синхронизации (фиг.6) содержит дешифратор 27, счетчик (идентификаторов) 28, элементы задержки 29-31, элемент НЕ 32, элементы И 33-35, элемент ИЛИ-НЕ 36, элементы ИЛИ 37,38, триггеры 39-42. группу 43 элементов И.

Регистр 13 режима коммутации (фиг.7) содержит триггер 44, элемент задержки 45, элементы И 46. 47. элементы ИЛИ 48.49.

Группа 14 счетчиков номеров (фиг.8) содержит элемент 50 задержки, счетчик 51 тестовых наборов, счетчик 52 циклов, элементы НЕ 53-55.

Регистр 15 обратных связей (фиг.9) содержит элемент НЕ 56, элемент задержки 57, регистр 58 тестовых наборов.

Первый коммутатор 3 (фиг. 10) содержит п узлов коммутации 59 и трехстабильные элементы НЕ 60,61.

На фиг.1-15 использованы следующие сокращенные обозначения сигналов:

АДР - адрес,

ЗАГР - загрузка,

ЗП () - запись,

ЗПКТ - запись коммутационного теста,

ЗПКЦ - запись кода циклов,

ЗПТН - запись тестового набора,

ИНД1-ИНДЗ - сигналы разрешения индикации.

КИД - конец идентификатора,

КНЦ - конец цикла,

КОС - код обратной связи,

КТ - коммутационный тест,

КТПД - конец теста поиска дефектов,

КЦ - код циклов,

НКЭД - номер класса эквивалентных дефектов,

НТН - номер тестового набора,

НЦ- номер цикла,

ОГТ - останов генератора,

РАБ - работа,

РВК - разрешение выхода коммутатора,

РЗС. РЗС1, РЗС2 - разрешение сравнения,

СВР - сброс.

СБРЦ - сброс счетчика циклов,

СБТН - сброс счетчика тестовых наборов,

СДЧ - сброс делителя частоты,

СИ - синхронизирующие импульсы,

СИЗ () - синхронизирующие импульсы загрузки.

СИР - синхронизирующие импульсы рабочие.

СРВ1, СРВ2 - сигналы сравнения,

СТР - стробирующий сигнал.

ТИН - тестовая информация,

УСТ - установка,

Ч Т - чтение.

Устройство для диагностирования дискретных узлов (см. фиг. 1,11,12) работает следующим образом. По команде от блока 10 синхронизации устанавливаются в исходное состояние блоки 1 управления и 8 задания режима коммутации. Затем от блока 1

0 управления на первый коммутатор 3 поступает коммутационный тест, согласно которому производится разделение внешних контактов объекта 9 диагностирования (ОД) на входные и выходные. Затем от блока 1

5 управления на второй блок 6 сравнения поступает код циклов, задающий количество циклов тестирования. После этого от блока 1 управления в блок 2 регистров сдвига начинают поступать тестовые наборы, состав0 ляющие идентификатор, который позволяет доказать наличие или отсутствие в ОД определенного класса дефектов. Тестовые наборы записываются в блок 2 регистров сдвига по синхронизирующим импульсам загруз5 ки, поступающие от блока 8 задания режима коммутации.

Одновременно в блоке 8 задания режима коммутации подсчитывается количество тестовых наборов, составляющих данный

0 идентификатор. Такой подсчет необходим для формирования кода обратных связей, который подается на второй коммутатор 4. В соответствии с кодом обратных связей

5 второй коммутатор 4 совместно с блоком 2 регистров сдвига образуют кольцевой регистр сдвига требуемой длины. Затем от блока 1 управления на блок 8 задания режима коммутации поступает команда начала

0 цикла тестирования, по которой блок 8 задания режима коммутации, во-первых, разрешает формирование сигналов на группе информационных входов второго коммутатора 4; во-вторых, начинает посылать рабо5 чие синхронизирующие импульсы на блок 2 регистров сдвига. Частота следования рабочих синхронизирующих импульсов значительно превышает частоту следования синхронизирующих импульсов загрузки и

0 определяется требуемой частотой формирования тестовых воздействий. По рабочим синхронизирующим импульсам блок 2 регистров сдвига осуществляет циклический сдвиг тестовой информации через второй

5 коммутатор 4. При этом тестовая информация, поступающая от второго коммутатора 4, параллельно разветвляется следующим образом: тестовые наборы потсупают через первый коммутатор 3 на входы ОД; ожидаемые реакции подаются на первый блок 5 сравнения для сравнения с фактическими

реакциями, поступающими через первый коммутатор 3 от ОД; сигналы, разрешающие сравнение на данном тестовом наборе, поступают на блок 1 управления. По разрешающим сигналам от блока 1 управления в первом блоке сравнения 5 производится сравнение фактических реакций ОД с ожидаемыми. Сигнал сравнения с выхода первого блока 5 сравнения передается в блок 1 управления.

Одному циклу тестирования соответствует полный сдвиг диагностической информации в блоке 2 регистров сдвига. Если за время цикла тестирования все ответные реакции ОД совпали с ожидаемыми, то дальнейшая работа устройства прекращается, а в блоке 7 индикации появляется сообщение найден дефект, а также индицируется номер класса эквивалентных дефектов, соответствующего данному индентификатору. В противном случае циклы тестирования повторяются до тех пор, пока номер очередного законченного цикла, поступающий на второй блок 6 сравнения от блока 8 задания режима коммутации, не становится равным коду циклов, поступающему на второй блок 6 сравнения от блока 1 управления., В этом случае по команде от блока 8 задания режима коммутации второй блок 6 сравнения выдает на блок 8 задания режима коммутации сигнал сравнения, по которому начинаетсязагрузкаследующегоиндентификатора.

Если при попытке считать первый тестовый набор очередного идентификатора в блоке 1 управления считана метка конца теста поиска дефектов, то в блоке 7 индикации возможно появление следующих сообщений. Сообщение исправно появляется в том случае, если за время прохождения теста не зафиксировано ни одного совпадения ответной реакции ОД с ожидаемой. В противном случае появляется сообщение неисправно.

Работа блока 1 управления (см. фиг.2, 11-15) начинается с установки в исходное состояние узла Т2 синхронизации и узла 11 задания режима по сигналу СВР - сброс от блока 10 синхронизации. В этом случае узел 12 синхронизации вырабатывает сигнал СБРЦ - сброс счетчика циклов, который поступает в блок 8 задания режима коммутации. Затем от блока 10 синхронизации на вход узла 11 задания режима начинают поступать сигналы ЧТ - чтение. Затем от узла 11 на третью группу выходов блока 1 управления и далее - к первому коммутатору 3 поступает КТ - коммутационный тест, а на вторую группу выходов кода операции и далее- к второму блоку 6 сравнения поступает КЦ - код циклов.

После этого от узла 11 задания режима на первую группу выходов кода операции блока 1 управления начинает поступать ТИН - тестовая информация, которая загружается в блок 2 регистров сдвига по сигналам, поступающим от узла 11 задания режима на выход ЗПТН - запись тестовых

0 наборов блока 1 управления. Тестовая информация от узла 11 задания режима подается также на входы узла 12 синхронизации, в котором распознаются метки КИД - конец идентификатора и КТПД - конец теста по5 иска дефектов. Распознав метку КИД, узел 12 синхронизации формирует на выходах блока 1 управления еджиничные сигналы КИД и СБРЦ. поступающие на блок 8 задания режима коммутации как команда начала

0 тестирования.

В режиме тестирования на блок 1 управления от второго коммутатора 4 поступают сигналы РЗС - разрешение сравнения, на основе которых узел 12 синхронизации вы5 рабатывает сигналы РЗС1 - разрешение сравнения, поступающие на первый блок 5 сравнения.

При совпадении фактической реакции с ожидаемой сигнал сравнения с выхода пер0 вого блока 5 сравнения подается на вход СРВ1 - сравнение узла 12 синхронизации. Каждый цикл тестирования завершается поступлением от блока 8 задания режима коммутации на входы узла 12 синхронизации

5 сигналов УСТ - установка и КНЦ - конец цикла.

В том случае, если на протяжении всего цикла тестирования по каждому формируемому блоком 1 управления сигналу РЗС1

0 первый блок 5 сравнения вырабатывал СРВ 1, т.е. все фактические реакции ОД совпали с ожидаемыми, в блоке 1 управления вырабатываются следующие сигналы: от узла 12 синхронизации сигнал ОГТ - останов

5 генератора поступает на блок 10 синхронизации, запрещая формирование синхроимпульсов fr на его выходе; с выходов узла 12 синхронизации на блок 7 индикации поступает НКЭД - номер класса эквивалентных

0 дефектов, сопровождающийся сигналом ИНДЗ, разрешающим индикацию сообщения найден дефект в блоке 7 индикации.

Если за время цикла тестирования не все реакции ОД совпали с ожидаемыми, то

5 цикл тестирования повторяется заданное число раз, после чего осуществляется загрузка очередного индентификатора в блок 2 регистров сдвига.

Если на входы узла 12 синхронизации от узла 11 задания режима поступила метка

КТПД - конец теста поиска дефектов, в блоке 1 управления возможно формирвоание следующих сигналов: сигнал ИНД2, разрешающий индикацию в блоке 7 индикации сообщения исправно, формируется в том случае, если на протяжении всего теста поиска дефектов на блок 1 управления не поступило ни одного сигнала СРВ1; в противном случае блок 1 управления формирует сигнал ИНД1, разрешающий индикацию в блоке 7 индикации сообщения неисправно.

Блок ТО синхронизации (см. фиг.4,13} работает следующим образом, При нажатии клавиши пуск 16 единичный сигнал поступает на вход элемента 17 задержки, а также на выход СБР - сброс для начальной установки блоков 1 управления и 8 задания режима коммутации.

Спустя время, необходимое для начальной установки устройства и определяемое элементом 17 задержки, единичный сигнал с выхода элемента 17 задержки поступает на вход пуск генератора 18 синхроимпульсов. С выхода генератора 18 синхроимпульсы подаются на вход делителя 19 частоты, а также на выход fr блока и далее - к блоку 8 задания режима коммутации. Делитель 19 частоты представляет собой счетчик с уста- -новочным входом. Пока на входе СДЧ - сброс делителя частоты блока 10 синхронизации поддерживается единичный сигнал, формирование выходных сигналов делителя 19 частоты запрещается, Как только на входе СДЧ устанавливается нулевой сигнал, в делителе 19 частоты начинается цикл пересчета, по окончании которого единичный сигнал ЧТ поступает на блок 1 управления. Работа генератора 18 прекращается при поступлении единичного сигнала на вход 01Т

-останов генератора блока 10 синхронизации.

Работа узла 11 задания режима (см, фиг.5,13) начинается с поступления на вход СБР - сброс сигнала начальной установки, по которому устанавливается в ноть счетчик 20 (адреса). Нулевой адрес с информационных выходов счетчика 20 подается параллельно на адресные входы памяти 21 и дешифратора 26. Затем единичный сигнал поступает с входа ЧТ - чтение узла на входы ЧТ памяти 21 и элемента 23 задержки. При этом на выходах памяти 21 формируется КТ

-коммутационный тест, хранящийся по нулевому адресу и предназначенный для записи в регистр (коммутационного теста) 24. Через время, необходимое для активизации выходов памяти 21 и определяемое элементом 23 задержки, единичный сигнал с выхода элемента 23 задержки поступает на вход

стробирования дешифратора 26, а также на вход элемента 22 задержки. При этом на выходе ЗПКТ - запись коммутационного теста дешифратора 26 формируется единичный сигнал, поступающий на вход разрешения записи регистра 24, с выхода которого КТ подается на первый коммутатор 3. Затем, через время, необходимое для записи КТ в регистр 24 и определяемое эле0 ментом 22 задержки, единичный сигнал с

выхода элемента 22 задержки поступает на

суммирующий вход счетчика 20 (адреса),

увеличивая его содержимое на единицу.

При поступлении на вход узла 11 зада5 ния режима следующего сигнала ЧТ, из памяти 21 считывается КЦ - код циклов, который записывается в регистр 25 по разрешающему сигналу ЗПКЦ - запись циклов от дешифратора 26. С выхода регистра 25

0 КЦ поступает на второй блок 6 сравнения. При поступлении на вход узла 11 задания режима последующих сигналов ЧТ, из памяти 21 осуществляется считывание ТИН - тестовой информации, которая подается на

5 узел 12 синхронизации и блок 2 регистров сдвига. Каждое считывание ТИН сопровождается формированием единичного сигнала на выходе ЗПТН - запись тестового набора дешифратора 26. Сигнал ЗПТН подается на

0 блок 8 задания режима коммутации.

Узел 12 синхронизации (см. фиг.6,13-15) работает следующим образом. По сигналу СБР - сброс устанавливаются в ноль триггеры 40-42, счетчик 28 (идентификаторов), а

5 также через элемент ИЛИ 37 триггер 39. Сигнал СБР, проходя через элемент ИЛИ 38, формирует на выходе СБРЦ - сброс счетчика циклов узла 12 синхронизации единичный сигнал, который поступает на блок 8

0 задания режима коммутации, Метка КИД - конец идентификатора, поступающая на входы узла 12 синхронизации, распознается дешифратором 27, на выходе КИД которого формируется единичный сигнал, С

5 выхода КИД дешифратора 27 единичный сигнал; во-первых, поступая на суммирующий вход счетчика 28 (идентификаторов), увеличивает на единицу его содержимое; во-вторых, проходя через элемент ИЛИ 38.

0 как сигнал СБРЦ, поступает на блок 8 задания режима коммутации; в-третьих, с выхода КИД, как команда начала тестирования, поступает на блок 8 задания режима коммутации. В режиме тестирования единичный

5 сигнал от входа РЗС - разрешение сравнения поступает на вход элемента 29 задержки. Через время, необходимое для установления на выходах ОД ответной реакции, с выхода элемента 29 задержки единич- ный сигнал поступает: во-первых, как

сигнал РЗС1 - разрешение сравнения на первый блок 5 сравнения; во-вторых, через элемент 30 задержки - на вход элемента И 33. Результат сравнения может иметь два исхода, поэтому рассмотрим оба случая.

При несовпадении ответной реакции ОД с ожидаемой сигнал СРВ1 с первого блока 5 сравнения отсутствует. В этом случае на выходе элемента НЕ 32 присутствует единичный сигнал, который в момент времени, определяемый элементом 30 задержки, устанавливает в единицу триггер 39. Элемент 30 задержки, рассчитанный на время сравнения реакций, предназначен для устранения ложных срабатываний триггера 39.

Если ответная реакция ОД совпала с ожидаемой, то с первого блока 5 сравнения выдается сигнал СРВ1. В результате, во- первых, на выходе элемента НЕ 32 устанавливается ноль, запрещающий переключение триггера 39; во-вторых, устанавливается в единицу триггер 40.

Каждый цикл тестирования завершается поступлением от блока 8 задания режима коммутации сигналов КНЦ - конец цикла и УСТ - установка, первый из которых имеет активный нулевой уровень. Если на момент поступления сигнала КНЦ триггер 39 находился в нуле, что возможно только при совпадении всех реакций, поступивших от ОД в течение цикла, с ожидаемыми, то на выходе элемента ИЛИ-НЕ 36 формируется единичный сигнал, который: во-первых, устанавливает в единицу триггер 42; во-вторых, как сигнал ОГТ - останов генератора поступает на блок 10 синхронизации. Единичный сигнал с выхода триггера 42 поступает: во-первых, на вход группы 43 элементов И, разрешая формирование на ее выходах НКЭД - номера класса эквивалентных дефектов, поступающего от счетчика 28 (идентификаторов); во-вторых, как сигнал ИНДЗ на блок 7 индикации, разрешая индикацию сообщения найден дефект и номера класса эквивалентных дефектов. Единичный сигнал УСТ, проходя через элемент 31 задержки, спустя время, необходимое для переключения триггера 42 и останова генератора в блоке синхронизации, сбрасывает в ноль триггер 39, подготавливая его к дальнейшей работе.

При поступлении на вход дешифратора 27 метки КТПД - конец теста поиска дефектов единичный сигнал КТПД с его выхода устанавливает в единицу триггер 41, При этом, если триггер 40 находится в единице, то на выходе элемента И 34 формируется единичный сигнал ИНД1, поступающий в блок 7 индикации и разрешающий индикацию сообщения неисправно.

В случае нулевого состояния триггера 40 единичный сигнал формируется на выходе элемента И 35 и, как сигнал ИНД2. разрешает в блоке 7 индикацию сообщения

исправно.

Блок 8 задания режима коммутации (см. фиг.3,13,14) работает следующим образом. По команде начальной установки, поступающей на вход СБР от блока 10 синхрониза0 ции, устанавливаются в исходное состояние регистр 13 режима коммутации и регистр 15 обратных связей. По сигналу СБР регистр 13 режима коммутации вырабатывает единичный сигнал СБТН - сброс счетчика тестовых

5 наборов, который поступает на группу 14 счетчиков номеров и устанавливает их в исходное состояние. Кроме того, на группу 14 счетчиков номеров поступает установочный сигнал СБРЦ - сброс счетчиков циклов, вы0 рабатываемый в блоке 1 управления по сигналу СБР. В исходном состоянии: на выходах СДЧ-сброс делителя частоты, СИР - синхроимпульсы рабочие и РВК - разрешение выхода коммутатора регистра 13 ре5 жима коммутации устанавливаются нулевые сигналы; на группе выходов регистра 15 обратных связей устанавливается нулевой КОС - код обратных связей; на группах выходов группы 14 счетчиков номе0 ров устанавливаются нулевые НТН - номер тестового набора и НЦ - номер цикла.

Затем на входы блока 8 задания режима коммутации от блока 10 синхронизации начинают поступать синхроимпульсы fr, а от

5 блока 1 управления - сигналы ЗПТН - запись тестового набора. При этом с выходов регистра 13 режима коммутации начинают поступать следующие сигналы: СИЗ - синхроимпульсы загрузки на регистр 15 обрат0 ных связей; СИ - синхроимпульсы на блок 2 регистров сдвига. По сигналам СИЗ регистр 15рбратных связей формирует сигналы СИЗ с активным нулевым уровнем, поступающие на группу 14 счетчиков номеров. Та5 ким образом, запись очередного тестового набора в блок 2 регистров сдвига сопровождается приходом очередного СИЗ на регистр 15 обратных связей, что вызывает увеличение на единицу НТН. Каждое новое

0 значение НТН поступает в регистр 15 обратных связей и фиксируется там, что подверж- дается соответствующим увеличением КОС, который подается как на группу 14 счетчиков номеров, так и на второй коммутатор 4.

5 В результате КОС, равный числу тестовых наборов, загруженных в блок 2 регистров сдвига, поступает от блока 8 задания режима коммутации на управляющие входы второго коммутатора 4. Режим загрузки за- канчивается при поступлении на вход КИД

- конец идентификатора команды начала тестирования от блока 1 управления. Сигнал КИД поступает на регистр 13 режима коммутации, вызывая на его выходах формирование единичных сигналов СДЧ и РВК, первый из которых поступает на блок 10 синхронизации, второй - на второй коммутатор 4, разрешая активизацию его выходов. На выходе СИЗ регистра 13 режима коммутации прекращается формирование синхроимпульсов загрузки, в то время как с выхода СИР начинают поступать рабочие синхроимпульсы. Увеличивается также частота синхроимпульсов СИ, поступающих на блок 2 регистров сдвига.

Если в режиме загрузки частота следования СИ соответствовала частоте сигналов СИЗ, то в режиме тестирования она соответствует частоте следования СИР. Таким образом, каждый сдвиг тестовой информации в блоке 2 регистров сдвига сопровождается поступлением импульсов СИР на группу 14 счетчиков номеров, в результате чего НТН на выходе группы уменьшается на единицу. К моменту окончания цикла тестирования в блоке 2 регистров сдвига на вход СИР группы 14 счетчиков номеров поступит столько импульсов, сколько тестовых наборов загружено в блок 2 регистров сдвига. При этом на выходах группы 14 счетчика номеров НТН достигает нуля, а НЦ увеличивается на единицу. Затем группа 14 счетчиков номеров восстанавливает первоначальное значение НТН путем перезаписи КОС из регистра 15 обратных связей и вырабатывает следующие сигналы: РЗС2 - разрешение сравнения на второй блок 6 сравнения и КНЦ - конец цикла на блок 1 управления.

В том случае, если отработано заданное количество циклов тестирования, с выхода второго блока 6 сравнения сигнал СРВ2 поступает на регистр 13 режима коммутации, переводя его в режим загрузки.

В противном случае циклы тестирования повторяются до получения сигнала СРВ2.

Регистр 13 режима коммутации (см. фиг.7,13,14) работает следующим образом. Поступающий на вход СВР - сброс единичный сигнал, проходя через элемент ИЛИ 49, во-первых, сбрасывает в ноль триггер 44; во-вторых, как сигнал СБТН - сброс счетчика тестовых наборов поступает на группу 14 счетчиков номеров. Нулевое состояние триггера 44 соответствует режиму загрузки. При этом единица с инверсного выхода триггера 44 разрешает прохождение сигналам ЗПТН - запись тестового набора через элемент И 47. С выхода элемента И 47 единичные сигналы поступают: во-первых, на

выход СИЗ - синхроимпульсы загрузки; во- вторых, через элемент ИЛИ 48 на выход СИ

-синхроимпульсы. Ноль с прямого выхода триггера 44 запрещает формирование сигналов на выходе элемента И 46. При поступлении единичного сигнала на вход КИД - конец идентификатора триггер 44 устанавливается в единицу, что соответствует режиму тестирования. При этом единица с

прямого выхода триггера 44 поступает: во- первых, на вход элемента И 46, разрешая прохождение сигналов fr; во-вторых, через элемент 45 завдержки на выход СДЧ и далее

-к блоку 10 синхронизации; в-третьих, на выход РВК и далее - к второму коммутатору

4, С выхода элемента И 46 единичные сигналы поступают: во-первых, на выход СИР - синхроимпульсы рабочие; во-вторых, через элемент ИЛ И 48 на выход СИ. Ноль с инверсного выхода триггера 44 запрещает формирование сигналов на выходе элемента И 47. Действие сигнала СРВ2, поступающего от второго блока 6 сравнения, аналогично действию сигнала СВР.

Работа группы 14 счетчиков номеров (см. фиг.8,14,) начинается с поступления сигналов начальной установки. Сигнал СБТН - сброс счетчика тестовых наборов устанавливает в ноль счетчик 51, а сигнал СБРЦ сброс счетчика циклов устанавливает в ноль счетчик 52. Счетчик 51 тестовых наборов - реверсивный, с возможностью параллельной записи информации (типа ИЕ7). В режиме загрузки сигналы СПЗ - синхроимпульсы

загрузки с низким активным уровнем поступают на суммирующий вход счетчика 51, вызывая увеличение НТН - номера тестового набора на его выходах Q, В режиме тестирования сигналы СИР - синхроимпульсы

рабочие, проходят через элемент НЕ 53, поступают на вычитающий вход счетчика 51, уменьшая его содержимое. При нулевом состоянии счетчика 51 и единичном сигнале СИР выход 0 счетчика принимает активное нулевое значение. Ноль с выхода 0 поступает: во-первых, через элемент НЕ 55 на суммирующий вход счетчика 52 циклов, увеличивая на единицу значение Н Ц - номера циклов на его выходах; во-вторых, на

вход элемента 50 задержки. С выхода элемента 50 задержки нулевой сигнал поступает: во-первых, на вход ЗП - параллельной записи данных счетчика 51, разрешая запись в него КОС - кода обратной связи,

поступающего на входы данных Д; во-вторых, как сигнал КН Ц - конец цикла - на блок 1 управления; в-трётьих, через элемент НЕ 54 как сигнал РЗС2 - разрешение сравнения - на блок 1 управления и второй блок 6

сравнения. Элемент 50 задержки необходим для увеличения длительности сигнала S

Регистр 15 обратных связей (см. фиг.9) работает следующим образом. Сигнал СВР - сброс производит начальную установку регистра 58 тестовых наборов. Синхроимпульсы загрузки, приходящие на вход СИЗ. через элемент НЕ 56 поступают; во-первых, как сигнал СИЗ на суммирующий вход счетчика 51 тестовых наборов группы 14 счетчи- ков номеров; во-вторых, на вход элемента 57 задержки. Через время, необходимое для переключения счетчика 51 (см. фиг.8) и определяемое элементом 57 задержки, на вход ЗП - запись регистра 58 поступает единичный сигнал, по которому НТН - номер тестового набора переписывается в регистр 58 и поступает на выходы КОС - код обратной связи,

Первый коммутатор 3 (см. фиг.10) рабо- тает следующим образом. Входные и выходные контакты обьекта 9 диагностирования и выходы второго коммутатора 4 подключены к первому коммутатору 3, а коммутация осуществляется согласно КТ, поступающему из блока 1 управления. Работу коммутатора 3 рассмотрим на примере узла 59 коммутации, к которому подключен один контакт ОД 9 и один выход второго коммутатора 4. Узел 59 коммутации в зависимости от значений разрядов КТ может работать в следующих режимах: подключить входной контакт ОД 9 к выходу второго коммутатора 4; подключить выходной контакт ОД 9 к выходу первого блока 5 сравнения; обеспечить отключение контакта ОД 9 от входа блока 5 сравнения и от выхода второго коммутатора 4. В первом режиме КТ содержит нулевой запрещающий сигнал, поступающий на вход трехстабильного элемента НЕ 60, и единичный разрешающий сигнал, поступающий на вход трехстабильного элемента НЕ 61. В результате выход трехстабильного элемента НЕ 60 принимает значение высокого сопротивления, а выход второго комму- татора 4 оказывается подключенным через трехстабильный элемент НЕ 61 к входному контакту ОД 9. Во втором режиме КТ содержит единичный разрешающий сигнал, поступающий на вход трехстабильного элемента НЕ 60, и нулевой запрещающий сигнал, поступающий на вход трехстабильного элемента НЕ 61. В результате выход трехстабильного элемента НЕ 61 принимает значение высокого сопротивления, а вход первого блока 5 сравнения оказывается подключенным через трехстабильный элемент НЕ 60 к выходному контакту ОД 9. В третьем режиме из КТ на входы трехста- бильных элементов НЕ 60 и 61 подаются

нулевые запрещающие сигналы, и выходы этих элементов принимают значение высокого сопротивления.

Формула изобретения 1. Устройство для диагностирования дискретных узлов, содержащее блок регистров сдвига, первый блок сравнения, блок индикации, блок синхронизации, блок управления и первый коммутатор, причем первая группа выходов блока управления соединена с группой входов разрешения индикации блока индикации, группа информационных входов которого соединена с второй группой выходов блока управления, третья группа выходов которого соединена с группой управляющих входов первого коммутатора, первые группы информационных входов и выходов которого являются соответственно группой входов и группой выходов устройства для подключения к выходу и входу диагностируемого дискретного узла, вторая группа информационных выходов первого коммутатора соединена с первой группой информационных входов первого блока сравнения, выход равно которого соединен с входом логического условия блока управления, выход разрешения сравнения которого соединен с входом разрешения первого блока сравнения, вход останова блока синхронизации соединен с выходом останова блока управления, вход стробирования которого соединен с первым выходом блока синхронизации, второй выход которого соединен с первым входом установки блока управления, отличающееся тем, что. с целью повышения полноты и достоверности диагностирования, в устройство введены второй блок сравнения, блок задания режима коммутации и второй коммутатор, причем группа информационных выходов блока регистров сдвига соединена с группой информационных входов второго коммутатора, группа управляющих входов которого соединена с группой управляющих выходов блока задания режима коммутации, выход задания режима которого соединен с входом задания режима второго коммутатора, группа информационных выходов которого и первая группа выходов кода операции блока управления соединены с группой информационных входов блока регистров сдвига и вторыми группами информационных входов первого коммутатора и первого блока сравнения, группа информационных выходов блока задания режима коммутации соединена с первой группой информационных входов второго блока сравнения, вторая группа информационных входов которого соединена с второй группой выходов кода операции блока

управления, второй вход установки которого соединен с выходом разрешения сравнения блока задания режима коммутации и входом разрешения второго блока сравнения, выход равно которого соединен с входом условия сравнения блока задания режима коммутации, выход синхронизации которого соединен с входом синхронизации блока регистров сдвига, первый выход группы информационных выходов второго коммутатора соединен с входом синхронизации блока управления, третий вход установки которого соединен с первым выходом установки блока задания режима коммутации, второй выход установки которого соединен с входом установки блока синхронизации, третий выход которого соединен с управляющим входом блока задания режима коммутации, вход установки которого соединен с первым входом установки блока управления, четвертая группа выходов которого соединена с группой управляющих входов блока задания режима коммутации, вход запуска которого соединен с выходом запуска блока управлениян причем блок задания режима коммутации содержит регистр режима коммутации, регистр обратных связей и группу счетчиков номеров, при этом вход условия сравнения блока задания режима - коммутации соединен с входом разряда условия сравнения регистра режима коммутации, вход разрешения записи которого соединен с первым входом группы управляющих входов блока задания режима коммутации, выход задания режима которого соединен с выходом разряда задания режима регистра режима коммутации, вход синхронизации которого соединен с управляющим входом блока задания режима коммутации, выход синхронизации которого соединен с первым выходом синхронизации регистра режима коммутации, вход установки которого соединен с входом установки регистра обратных связей и входом установки блока задания режима коммутации, группа информационных выходов которого соединена с первой группой информационных выходоз счетчиков номеров группы, первые входы установки которых соединены с вторым входом группы управляющих входов блока задания режима коммутации, выход разрешения сравнения которого соединен с выходами обнуления счетчиков номеров группы, выходы установки которых соединены с первым выходом установка блока задания режима коммутации, группа управляющих выходов которого соединена с группой управляющих входов счетчиков номеров группы и группой информационных выходов регистра обратных связей, выход синхронизации которого соединен с первыми входами синхронизации счетчиков номеров группы, вторая группа информационных выходов которых соединена с группой информационных входов регистра обратных связей, вход синхронизации которого соединен с вторым выходом синхронизации регистра режима коммутации, первый выход установки которого соединен с вторым выходом установки блока задания режима коммутации, второй выход установки регистра режима коммутации соединен с вторыми входами установки счетчиков номеров группы, вторые входы

синхронизации которых соединены с третьим выходом синхронизации регистра режима коммутации, вход запуска которого является входом запуска блока задания режима коммутации.

2. Устройство по п,1, о т л и ч а ю щ е е- с я тем, что блок управления содержит узел задания режима и узел синхронизации, причем второй вход установки блока соединен с первым входом установки узла синхронизации, второй вход установки которого соединен с третьим входом установки блока, вход синхронизации которого соединен с входом синхронизации узла синхронизации, выход останова которого является выходом останова блока, вход логического условия которого соединен с входом условия сравнения узла синхронизации, выход установки которого соединен с первым выходом четвертой группы выходов блока, выход разрешения сравнения которого соединен с выходом разрешения сравнения узла синхронизации, третий вход установки которого соединен с входом установки узла задания режима и первым входом установки блока, первая группа выходов которого соединена с первой группой выходов узла синхронизации, вторая группа выходов которого является второй группой выходов блока, вторая группа выходов кода операции которого соединена с первой группой информационных выходов узла задания режима, выход разрешения записи которого соединен с вторым выходом четвертой группы выходов блока, третья группа выходов

которого соединена с группой управляющих выходов узла задания режима, вход считывания которого соединен с входом считывания блока, первая группа выходов кода операции которого соединена с второй

группой информационных выходов узла задания режима и группой информационных входов узла синхронизации, выход запуска которого соединен с выходом запуска блока.

3.Устройство по п.2, отличающее- с я тем, что узел задания режима содержит счетчик, постоянную память, два элемента задержки, дешифратор и два регистра, причем вход считывания узла соединен с входом считывания постоянной памяти и входом первого элемента задержки, выход которого соединен с входом стробирования дешифратора и через второй элемент задержки - с суммирующим входом счетчика, вход установки которого соединен с входом установки узла, вторая группа информационных выходов которого соединена с группами информационных входов первого и второго регистров и группой информационных выходов постоянной памяти, группа адресных входов которой соединена с группой выходов счетчика и группой входов дешифратора, первый выход которого является выходом разрешения записи узла, группа управляющих выходов которого соединена с группой выходов первого регистра, вход разрешения записи которого соединен с вторым выходом дешифратора, третий выход которого соединен с входом разрешения записи второго регистра, группа выходов которого является первой группой информационных выходов узла.

4.Устройство по п.2, отличающее- с я тем, что узел синхронизации содержит дешифратор, счетчик, три элемента задержки, элемент НЕ, три элемента И, элемент ИЛИ-НЕ, два элемента ИЛИ, четыре триггера и группу элементов И, причем вход синхронизации узла через первый элемент задержки соединен с выходом разрешения сравнения узла и через второй элемент задержки - с первым входом первого элемента И, выход которого соединен с единичным входом первого триггера, прямой выход которого соединен с первым входом элемента ИЛИ-НЕ, второй вход которого является вторым входом установки узла, первый вход установки которого через третий элемент

задержки соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом сброса первого триггера, выход останова узла соединен с выходом элемента ИЛИ-НЕ и единичным входом второго триггера, прямой выход которого соединен с управляющими входами элементов И группы и первым выходом первой группы выходов узла, вторая группа выходов которого сое динена с группой выходов элементов И

группы, группа входов которых соединена с группой выходов счетчика, суммирующий вход которого соединен с первым выходом дешифратора, первым входом второго элемента ИЛИ с выходом запуска узла, вход

условия сравнения которого соединен с вторым входом первого элемента И через элемент НЕ - и с единичным входом третьего триггера, прямой и инверсный выходы которого соединены соответственно с первыми

входами второго и третьего элементов И, выходы которых соединены соответственно с вторым и третьим выходами первой группы выходов узла, группа информационных входов которого соединена с группой входов дешифратора, второй выход которого соединен с единичным входом четвертого триггера, прямой выход которого соединен с вторыми входами второго и третьего элементов И, выход установки узла соединен с

выходом второго элемента ИЛИ, второй вход которого соединен с входом установки счетчика, вторым входом первого элемента ИЛИ, третьим входом установки узла и входами сброса второго, третьего и четвертого

триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностирования группы логических узлов | 1987 |

|

SU1520520A1 |

| Устройство для диагностирования цифровых узлов | 1986 |

|

SU1520517A1 |

| Устройство для диагностирования группы из @ логических узлов | 1985 |

|

SU1390611A1 |

| Устройство для диагностирования цифровых блоков | 1987 |

|

SU1548789A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Устройство для поиска дефектов дискретных блоков | 1985 |

|

SU1379784A1 |

| Устройство для диагностирования цифровых блоков | 1988 |

|

SU1631546A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам проверки работоспособности и поиска дефектов дискретных узлов и блоков. Целью изобретения является повышение полноты и достоверности диагностирования. С этой целью в устройство, содержащее блок регистров сдвига, первый блок сравнения, блок индикации, блок синхронизации, блок управления и первый коммутатор, введены второй блок сравнения, блок задания режима коммутации и второй коммутатор. 3 з.п.ф-лы, 15 ил.

Фиг. 1

-5

//

12

Фиг. 2

ЗПТН

Qmfa.( От5л,1ЛкиД

Qmfa. Отб/г,/№сбР

От 5л,

Ш

Ct/3

СБРЦ

СИЗ

15

L.

Фиг.}

1 I

кц

ЗЛТН

4Kfa.$

С6РЦ

ТИН

KM.2t$t5

ffffA

Н$Л.8

НДМНДЪ ШГ7

ийьа

ННЭД Мелу

РЗС1

ОГТ

IS

KjrjtJlO

f

wgo

I .J

1

i

РВК I к fa. 4

С Kfat

СДЧ HfatO

i

СИР

7

.1 P3CZ Ч1&Д.1,$

НЦ

НОС

КблЛ

V

I

Uo

-/7

ПУСК

От 5л. 1Л ОП

От 5л.8 СДЧ

Л

I

Г7Г От6л.

47

От5л. 0

+1

20

АДР.

i -t

L2J

II

Фиг. 5

С6Р

Н 6л. 1,8

18

/л

К 5л. 8

.0

/9

47

Kff/l.j

.J

ФигЛ

П

21

О

m K/tts.W -i-

3/7/ГГ

#

/7/Г/

25

.$

ЗПТН

зптн к 6л. 8 1-

ff

I

Г/Г

Omfa.1 КИД

Qт 5л Ю fr

От5л.1

От 5л. Ю От 5 л 6

Фиг. 7

1

.J.

Фиг. 6

ю

СИ Kfa2

Н15

|

L.

Фиг. 8

I

Фиг. 3

С

ПУСИ

)

/

Начальная установка блоков 1 управления и 8 зада - ни я режима коммутации

0/77$./

Запись КТв РГКТ 5лока 1 управления. Подача К Т на первыйкоммутаторЗ. Разделение Входов-выходов ОД.

Запись НЦ в РГКЦ блока 1 управления. Подача НЦ на второй блок сравнения 6.

к 5л. 5

ОтЪлА

Фиг. 11

.8

V

Загрузка идентификатора из ПЗУ блока 1 управления В 5лон 2 регистров сдвига с одновременным подсчетом числа ТН д идентификаторе

Подача на второй комму - татар Ц кода обратной связи для ззциклидания идентификатора д 2 регистров сдвига

10

Ж

Активизация выходов второго коммутатора 4

г

Реализация цикла: ТН идентификатора последовательно по даются на ОД , ожидаемые реакции сравниваются с фактическими по сигналу P3CJ. Полный - рот тестовой информации, в 5локе2 регистров сдвига

Во время 19 реализации цик/tcr /Ј Зафиксирован сигнал

НСРВ1 Да

Увеличение на / содержи мого счетчика циклов

Реализовано заданное число циклов

Да

Увеличение на 1 содержимого счетчика идентификаторов

Нет

16-.

Индикация сообщения „найден дефект и номера класса эквивалентных дере mod (содержимого счетчика идентификаторов).

С

ОСТ. ГТ.

)

Фиг. /2

Фиг. 15

Составитель Г. Виталиев

Редактор Е. Зубиетова Техред М.Моргентал

Заказ 3312Тираж 389Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул.Гагарина, 101

Фиг. /4

Корректор М. Шароши

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1149779A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1991-09-30—Публикация

1988-03-22—Подача