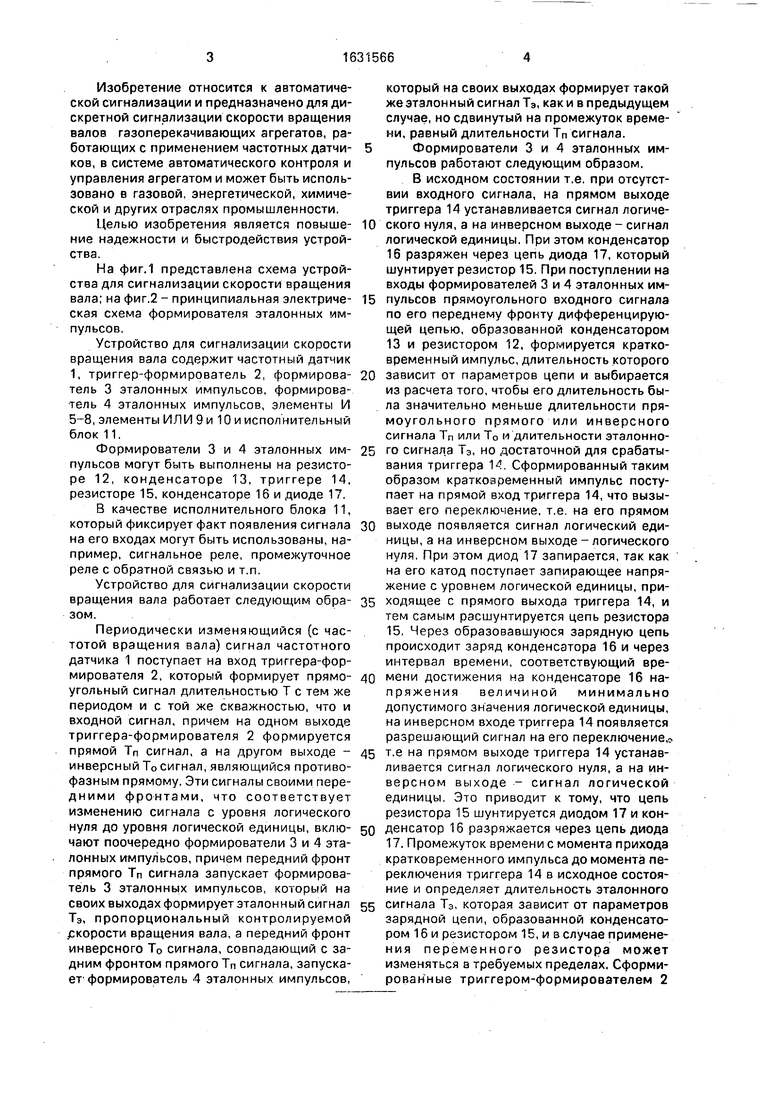

Фиг. 1

Изобретение относится к автоматической сигнализации и предназначено для дискретной сигнализации скорости вращения валов газоперекачивающих агрегатов, работающих с применением частотных датчиков, в системе автоматического контроля и управления агрегатом и может быть использовано в газовой, энергетической, химической и других отраслях промышленности.

Целью изобретения является повышение надежности и быстродействия устройства.

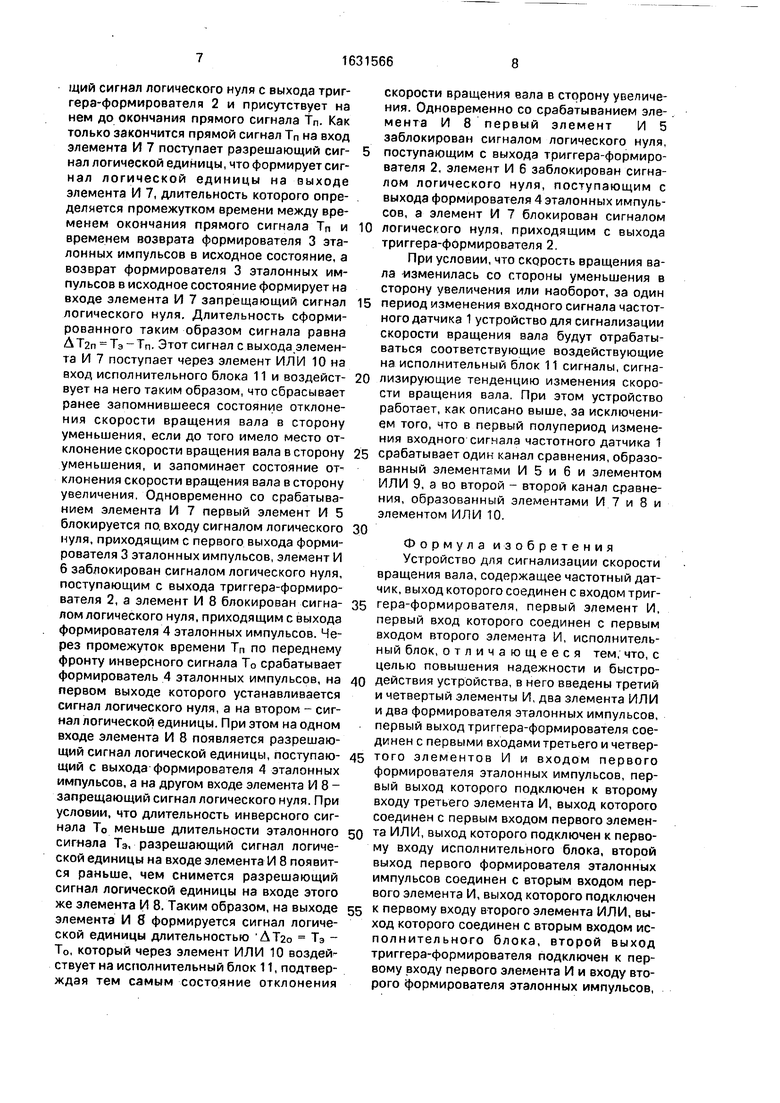

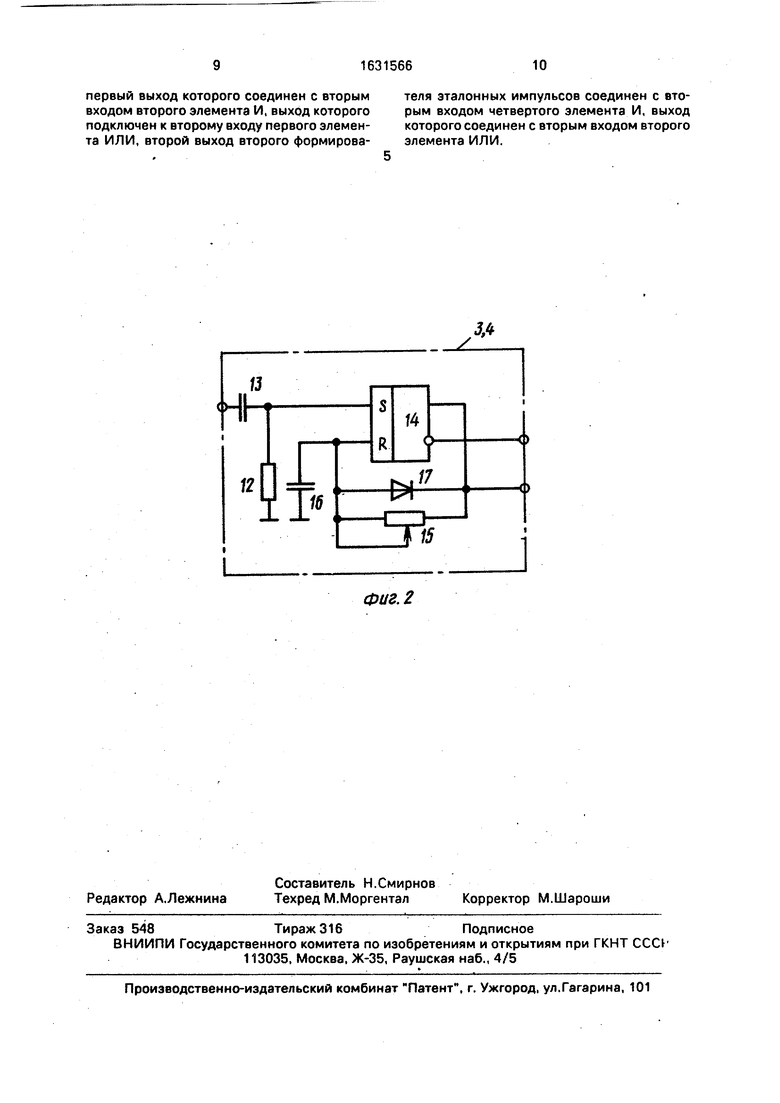

На фиг.1 представлена схема устройства для сигнализации скорости вращения вала; на фиг.2 - принципиальная электрическая схема формирователя эталонных импульсов.

Устройство для сигнализации скорости вращения вала содержит частотный датчик 1, триггер-формирователь 2, формирователь 3 эталонных импульсов, формирователь 4 эталонных импульсов, элементы И 5-8, элементы ИЛИ 9 и 10 и исполнительный блок 11.

Формирователи 3 и 4 эталонных импульсов могут быть выполнены на резисторе 12, конденсаторе 13, триггере 14, резисторе 15, конденсаторе 16 и диоде 17.

В качестве исполнительного блока 11, который фиксирует факт появления сигнала на его входах могут быть использованы, например, сигнальное реле, промежуточное реле с обратной связью и т.п.

Устройство для сигнализации скорости вращения вала работает следующим образом.

Периодически изменяющийся (с частотой вращения вала) сигнал частотного датчика 1 поступает на вход триггера-формирователя 2, который формирует прямоугольный сигнал длительностью Т с тем же периодом и с той же скважностью, что и входной сигнал, причем на одном выходе триггера-формирователя 2 формируется прямой Тп сигнал, а на другом выходе - инверсный То сигнал, являющийся противофазным прямому. Эти сигналы своими пере- дними фронтами, что соответствует изменению сигнала с уровня логического нуля до уровня логической единицы, включают поочередно формирователи 3 и 4 эталонных импульсов, причем передний фронт прямого Тп сигнала запускает формирователь 3 эталонных импульсов, который на своих выходах формирует эталонный сигнал Тэ, пропорциональный контролируемой скорости вращения вала, а передний фронт инверсного Т0 сигнала, совпадающий с задним фронтом прямого Тп сигнала, запускает формирователь 4 эталонных импульсов,

который на своих выходах формирует такой же эталонный сигнал Тэ, как и в предыдущем случае, но сдвинутый на промежуток времени, равный длительности Тп сигнала.

Формирователи 3 и 4 эталонных импульсов работают следующим образом.

В исходном состоянии т.е. при отсутствии входного сигнала, на прямом выходе триггера 14 устанавливается сигнал логиче0 ского нуля, а на инверсном выходе - сигнал логической единицы. При этом конденсатор 16 разряжен через цепь диода 17, который шунтирует резистор 15. При поступлении на входы формирователей 3 и 4 эталонных им5 пульсов прямоугольного входного сигнала по его переднему фронту дифференцирующей цепью, образованной конденсатором 13 и резистором 12, формируется кратковременный импульс,длительность которого

0 зависит от параметров цепи и выбирается из расчета того, чтобы его длительность была значительно меньше длительности прямоугольного прямого или инверсного сигнала Тп или Т0 и длительности эталонно5 го сигнала Тэ, но достаточной для срабатывания триггера 1. Сформированный таким образом кратковременный импульс поступает на прямой вход триггера 14, что вызывает его переключение, т.е. на его прямом

0 выходе появляется сигнал логический единицы, а на инверсном выходе - логического нуля. При этом диод 17 запирается, так как на его катод поступает запирающее напряжение с уровнем логической единицы, при5 ходящее с прямого выхода триггера 14, и тем самым расшунтируется цепь резистора 15. Через образовавшуюся зарядную цепь происходит заряд конденсатора 16 и через интервал времени, соответствующий вре0 мени достижения на конденсаторе 16 напряжения величиной минимально допустимого значения логической единицы, на инверсном входе триггера 14 появляется разрешающий сигнал на его переключение,

5 т-е на прямом выходе триггера 14 устанавливается сигнал логического нуля, а на инверсном выходе - сигнал логической единицы. Это приводит к тому, что цепь резистора 15 шунтируется диодом 17 и кон0 денсатор 16 разряжается через цепь диода 17. Промежуток времени с момента прихода кратковременного импульса до момента переключения триггера 14 в исходное состояние и определяет длительность эталонного

5 сигнала Тэ, которая зависит от параметров зарядной цепи, образованной конденсатором 16 и резистором 15, и в случае применения переменного резистора может изменяться в требуемых пределах. Сформированные триггером-формирователем 2

прямой Тп и инверсный Т0 сигналы, а также эталонные сигналы Тэ, сформированные в соответствующие моменты времени формирователями 3 и 4 эталонных импульсов, поступают «а соответствующие входы элементов И 5-8. Элементы И формируют разностные сигналы, по длительности пропорциональные разности в длительности сигналов, приходящих с частотного датчика 1 и формируемых формирователями 3 и 4 эталонных импульсов. Формирование воздействующих на исполнительный блок 11 сигналов происходит по двум каналам сравнения. Первый канал сравнения включает элементы И 5 и б и элемент ИЛИ 9, а второй канал сравнения - элементы И 7 и 8 и элемент ИЛИ 10, причем первый канал сравнения срабатывает при отклонении скорости вращения вала в сторону уменьшения, а второй - при отклонении скорости вращения вала в сторону увеличения от требуемого для целей контроля значения.

Допустим, что скорость вращения вала отклонилась в сторону уменьшения от требуемого значения, т.е. ТП(Т0) ТЭ. Примем за исходное состояние формирование прямого Тп сигнала триггером-формирователем 2. В этом случае после срабатывания формирователя 3 эталонных импульсов на один вход элемента И 5 поступает сформированный эталонный сигнал Т3 с уровнем логического нуля, являющийся запрещающим, и хотя на другой вход этого же элемента И 5 поступает разрешающий прямой сигнал Тп с уровнем логической единицы, элемент И 5 заблокирован. Элементы И 6 и 7 заблокированы запрещающим сигналом логического нуля, приходящим с выхода триггера-формирователя 2, на промежуток времени, равный длительности прямого сигнала Тп, а элемент И 8 заблокирован поступающим с выхода формирователя 4 эталонных импульсов запрещающим сигналом логического нуля, по длительности равным длительности прямого сигнала Тп. Поскольку имеется отклонение скорости вращения вала в сторону уменьшения, т.е. ТП(Т0) ТЭ, формирователь 3 эталонных импульсов возвращается в исходное состояние раньше, чем заканчивается прямой сигнал Тп, т.е. запрещающий сигнал логического нуля на входе элемента И 5 исчезает по окончании длительности эталонного сигнала Тэ. Таким образом, на входе элемента И 5 появляется разрешающий сигнал логической единицы, который вызывает появление сигнала логической единицы на выходе элемента И 5, и присутствует до окончания прямого сигнала Тп, так как в момент окончания этого сигнала на вход элемента И 5 поступает запрещающий сигнал логического нуля. Элементы И 6, 7 и 8 остаются в исходном (заблокированном) состоянии, т.е. на их выходах присутствуют сигналы логического нуля. Сигнал

логической единицы с выхода элемента И 5 через элемент ИЛИ 9 поступает на вход исполнительного блока 11, который срабаты- вает и фиксирует состояние отклонения скорости вращения вала в сторону уменьше0 ния от величины контролируемого значения, причем длительность сигнала, воздействующего на исполнительный блок 11, определяется как ATtn Тп - Тэ. По окончании прямого сигнала Тп, т.е. одновре5 менно с его задним фронтом, формируется передний фронт инверсного сигнала Т0, который своим передним фронтом запускает формирователь 4 эталонных импульсов. При этом на одном выходе формирователя 4 эга0 лонных импульсов появляется сигнал логического нуля, а на другом выходе - сигнал логической единицы. Таким образом, элемент И 5 по входу заблокирован сигналом логического нуля, приходящим с выхода

5 триггера-формирователя 2, который одновременно блокирует по входу элемент И 8. Элемент И 7 по входу заблокирован запрещающим сигналом логического нуля, посту- пающим с выхода формирователя 3

0 эталонных импульсов. На один вход элемента И 6 поступает запрещающий сигнал логи- ческого нуля, поступающий с выхода формирователя 4 эталонных импульсов, а на другом входе элемента И 6 присутствует

5 разрешающий сигнал логической единицы, по длительности соответствующий длительности инверсного сигнала Т0. При условии (То) ТЭ запрещение с одного входа элемента И 6 снимается раньше, чем закончится

0 инверсный сигнал Т0, т.е. на выходе второго элемента И 6 формируется сигнал AT-io То - Тэ. Этот сигнал так же, как и в предыдущем случае, через элемент ИЛИ 9 поступает на вход исполнительного блока

5 14. чем подтверждает отклонение скорости вращения вала в сторону уменьшения.

При отклонении скорости вращения вала в сторону увеличения, т.е при ТП(Т0) Тэ, срабатывает второй канал сравнения. За

0 исходное состояние примем как и в предыдущем случае формирование триггером- формирователем 2 прямого сигнала Тп. В этом случае после срабатывания формирователя 3 эталонных импульсов, т.е. на его

5 одном выходе его сигнал логического нуля, а на другом - сигнал логической единицы, на один вход элемента И 7 с выхода формирователя 3 эталонных импульсов поступает разрешающий сигнал логической единицы. а на другой вход элемента И 7 - запрещающий сигнал логического нуля с выхода триггера-формирователя 2 и присутствует на нем до окончания прямого сигнала Тп. Как только закончится прямой сигнал Тп на вход элемента И 7 поступает разрешающий сигнал логической единицы, что формирует сиг- нал логической единицы на выходе элемента И 7, длительность которого определяется промежутком времени между временем окончания прямого сигнала Тп и временем возврата формирователя 3 эталонных импульсов в исходное состояние, а возврат формирователя 3 эталонных импульсов в исходное состояние формирует на входе элемента И 7 запрещающий сигнал логического нуля. Длительность сформированного таким образом сигнала равна А Т2п Тэ - Тп. Этот сигнал с выхода .элемента И 7 поступает через элемент ИЛИ 10 на аход исполнительного блока 11 и воздействует на него таким образом, что сбрасывает ранее запомнившееся состояние отклонения скорости вращения вала в сторону уменьшения, если до того имело место отклонение скорости вращения вала в сторону уменьшения, и запоминает состояние отклонения скорости вращения вала в сторону увеличения, Одновременно со срабатыванием элемента И 7 первый элемент И 5 блокируется по. входу сигналом логического нуля, приходящим с первого выхода формирователя 3 эталонных импульсов, элемент И 6 заблокирован сигналом логического нуля, поступающим с выхода триггера-формирователя 2, а элемент И 8 блокирован сигналом логического нуля, приходящим с выхода формирователя 4 эталонных импульсов. Через промежуток времени Тп по переднему фронту инверсного сигнала Т0 срабатывает формирователь 4 эталонных импульсов, на первом выходе которого устанавливается сигнал логического нуля, а на втором - сигнал логической единицы. При этом на одном входе элемента И 8 появляется разрешающий сигнал логической единицы, поступающий с выхода формирователя 4 эталонных импульсов, а на другом входе элемента И 8 - запрещающий сигнал логического нуля. При условии, что длительность инверсного сигнала Т0 меньше длительности эталонного сигнала Тэ, разрешающий сигнал логической единицы на входе элемента И 8 появится раньше, чем снимется разрешающий сигнал логической единицы на входе этого же элемента И 8. Таким образом, на выходе элемента И 8 формируется сигнал логической единицы длительностью ДТао Тэ - То, который через элемент ИЛИ 10 воздействует на исполнительный блок 11, подтверждая тем самым состояние отклонения

скорости вращения вала в сторону увеличения. Одновременно со срабатыванием элемента И 8 первый элемент И 5 заблокирован сигналом логического нуля,

поступающим с выхода триггера-формирователя 2, элемент И 6 заблокирован сигналом логического нуля, поступающим с выхода формирователя 4 эталонных импульсов, а элемент И 7 блокирован сигналом

0 логического нуля, приходящим с выхода триггера-формирователя 2.

При условии, что скорость вращения вала изменилась со стороны уменьшения в сторону увеличения или наоборот, за один

5 период изменения входного сигнала частотного датчика 1 устройство для сигнализации скорости вращения вала будут отрабатываться соответствующие воздействующие на исполнительный блок 11 сигналы, сигна0 лизирующие тенденцию изменения скорости вращения вала. При этом устройство работает, как описано выше, за исключением того, что в первый полупериод изменения входного сигнала частотного датчика 1

5 срабатывает один канал сравнения, образованный элементами И 5 и 6 и элементом ИЛИ 9, а во второй - второй канал сравнения, образованный элементами И 7 и 8 и элементом ИЛИ 10.

0

Формула изобретения Устройство для сигнализации скорости вращения вала, содержащее частотный датчик, выход которого соединен с входом триг5 гера-формирователя, первый элемент И, первый вход которого соединен с первым входом второго элемента И, исполнительный блок, отличающееся тем, что, с целью повышения надежности и быстро0 действия устройства, в него введены третий и четвертый элементы И, два элемента ИЛИ и два формирователя эталонных импульсов, первый выход триггера-формирователя соединен с первыми входами третьего и четвер5 того элементов И и входом первого формирователя эталонных импульсов, первый выход которого подключен к второму входу третьего элемента И, выход которого соединен с первым входом первого элемен0 та ИЛИ, выход которого подключен к первому входу исполнительного блока, второй выход первого формирователя эталонных импульсов соединен с вторым входом первого элемента И, выход которого подключен

5 к первому входу второго элемента ИЛИ, выход которого соединен с вторым входом ис- полнительного блока, второй выход триггера-формирователя подключен к первому входу первого элемента И и входу второго формирователя эталонных импульсов,

первый выход которого соединен с вторым входом второго элемента И, выход которого подключен к второму входу первого элемента ИЛИ, второй выход второго формирователя эталонных импульсов соединен с вторым входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод | 1985 |

|

SU1309235A1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| Способ преобразования скоростей вращения двух валов для измерения соотношения скоростей и устройство для его осуществления | 1989 |

|

SU1636774A1 |

| Корректор частоты электроагрегата | 1985 |

|

SU1288890A1 |

| Устройство для допускового контроля длительности последовательности временных интервалов | 1988 |

|

SU1647508A1 |

| Селектор импульсной последовательности | 1990 |

|

SU1748238A1 |

| Устройство бесконтактного измерения излучательной способности объектов | 1991 |

|

SU1824527A1 |

| Цифровой следящий привод | 1983 |

|

SU1151925A1 |

| Система для проведения испытаний турбины | 1989 |

|

SU1636706A1 |

| Устройство для ограничения скорости вращения колесных пар транспортного средства | 1983 |

|

SU1136974A1 |

Изобретение относится к автомг иче- ской сигнализации и предназначено для дискретной сигнализации скорости вращения газоперекачивающих агрегатов, работающих с применением частотных датчиков, в системе автоматического контроля и управления агрегатом и может быть использовано в газовой, энергетической, химической и других отраслях промышленности. Целью изобретения является повышение надежности и быстродействия устройства. Для этого в устройство, содержащее частотный датчик 1, триггер-формирователь 2, элементы И 5 и 6 и исполнительный блок 11, введены формирователи 3 и 4 эталонных импульсов, элементы И 7 и 8 и элементы ИЛ И 9 и 10. Работа устройства сигнализации скорости вращения вала основана на преобразовании входного сигнала переменного тока в прямоугольные сигналы определенной длительности, пропорциональной текущей скорости вращения вала, и последующем сравнении его длительности с длительностью эталонного сигнала, пропорционального требуемой скорости вращения вала.2 ил. сл с

13

п

ai

/

U

Г4

-И

17

Фиг. 2

| УСТРОЙСТВО ДЛЯ ИНДИКАЦИИ | 1972 |

|

SU427356A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| СИГНАЛИЗАТОР СКОРОСТИ ВРАЩЕНИЯ ВАЛА | 0 |

|

SU404109A1 |

| кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-02-28—Публикация

1988-11-28—Подача