Изобретение относится к вычислительной технике и может быть использовано для цифровой фильтрации случайных процессов, представленных в формате линейной дельта-модуляции (ЛДМ).

Цель изобретения - упрощение фильтра и расширение области его применения за счет использования импульсной характеристики произвольного вида.

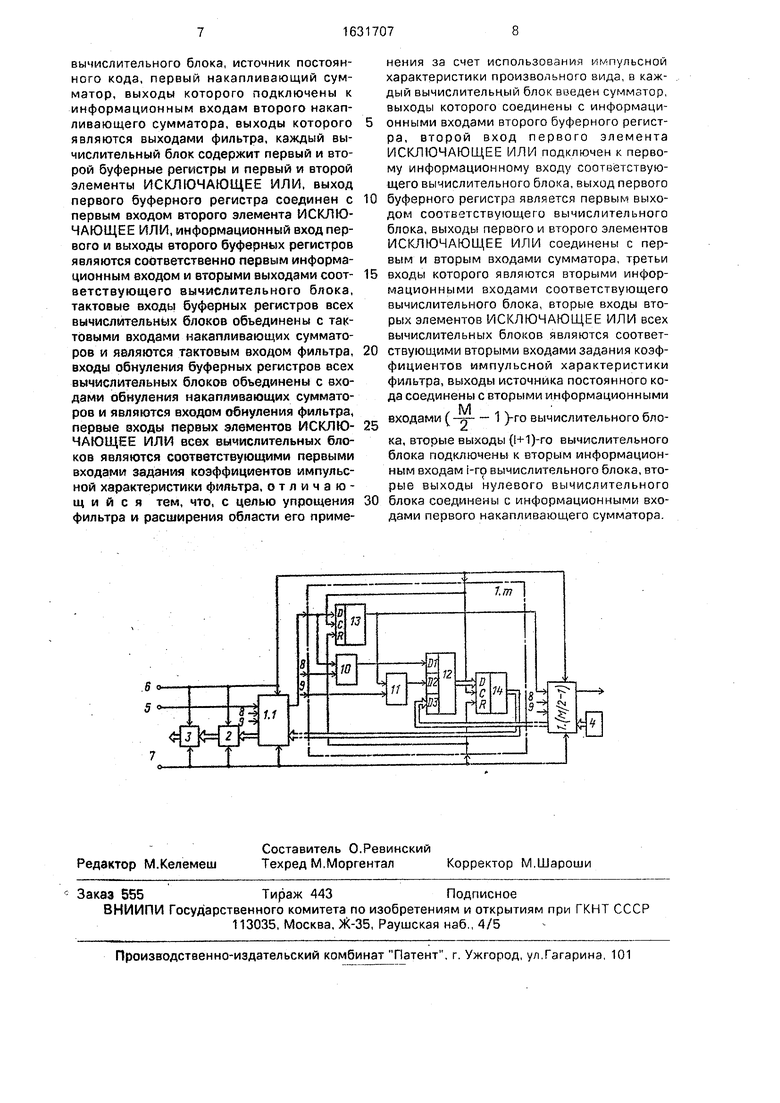

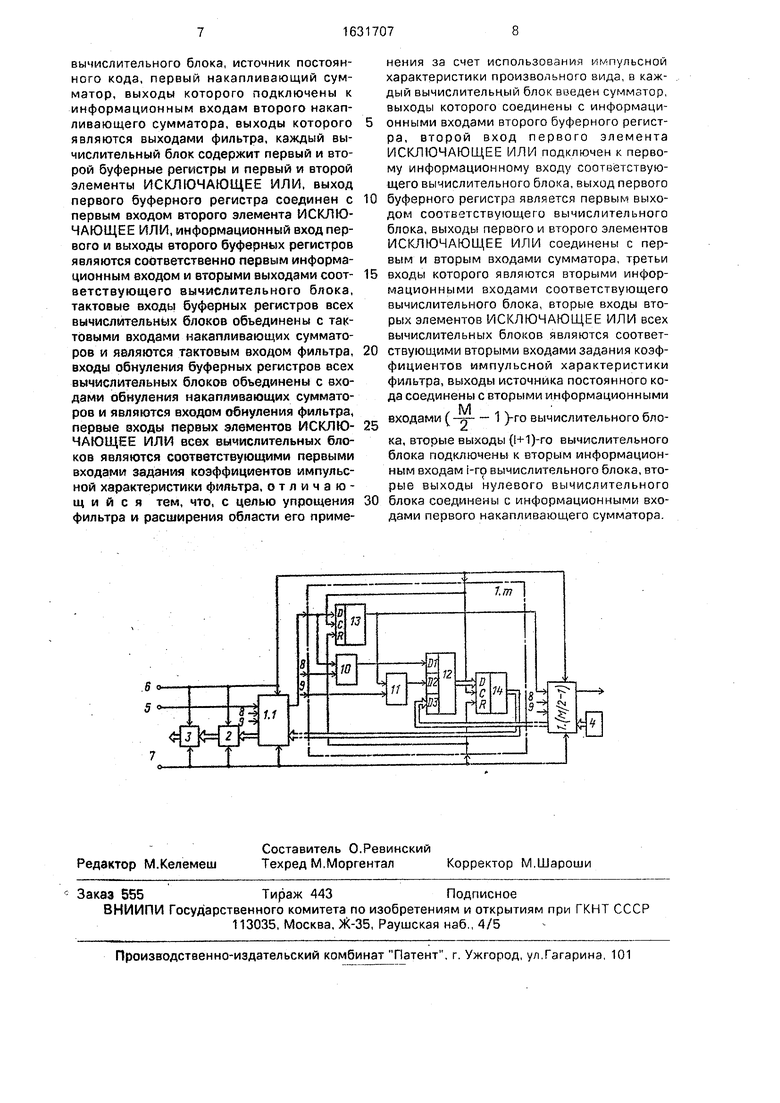

На чертеже приведена функциональная схема предложенного фильтра.

Цифровой фильтр содержит вычислительные блоки 1, первый и второй накапливающие сумматоры 2, 3 и источник 4 постоянного кода. На чертеже обозначены информационный вход 5, тактовый вход 6, вход 7 обнуления, первые и вторые входы 8, 9 задания коэффициентов импульсной характеристики. Каждый вычислительный блок 1 содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 10, 11, сумматор 12 и первый и второй буферные регистры 13, 14.

Цифровой фильтр работает следующим образом.

В фильтре осуществляется фильтрация входного сигнала, представленного в формате ЛДМ. Выходной сигнал такого фильтра в формате импульсно-кодовой модуляции (ИКМ) описывается выражением:

n I M-1 (х)(h)

Уп 2, 2, 2, е k - г ег , (1)

i 1 k 1 г 0

где {e/h)} при г б, М -1 - весовая, {ek( при k .0 - входная ЛДМ последовательности.

Для четной длины импульсной характеристики фильтра М Omod2, выделяя из выражения (1) сумму двух последовательных произведений шагов квантования входного сигнала на соответствующие весовые коэффициенты и разделяя свертку этого выражения на три последовательных этапа, каждый из которых выполняется при помощи суммирования с накоплением, получаем алгоритм функционирования фильтра:

(Л

С

О СО

4 О V

Уп

Ј Vyi;

i 1

k 1

2

V yk;

м

V x(2)

m 0 vr ()(К (x)(h)

xLek-2m e2rn + e k-2m-i e 2m + i

Значения eA € {-1,1}, поэтому значение под знаком суммы в алгоритме (2), равное

(х)(h) (x)

6k-2nn 6 2m + ek-2rn-l х (h)

Xezm + i €{-2,0, 2 J,(3)

а значение второй разности

V ykЈ / -МУМ I.

Осуществим замену переменных

1+ег(-)

, а умножение в выражеu()

нии (3) заменим сложением по модулю два с отрицанием, тогда G j 0, 1 I, а значение

.Т

,х)(h)

L k -2m + L 2m +

+ Lk-2m -1 ©Lzm+1 € {0.1.2}.

где Ф - операция суммирования по модулю два.

Используя последнее выражение, знаw2. 4°

чение второй разности V yk может быть

вычислено следующим образом:

V72о TV72 Ml1л

V yk 2 V yk ;(4)

м , ,

U2 L),4.ЛЬ)-,

V Vk 2, L k-2m + L 2m + -0 J-

+ L k-2m -1 L 2m +1 :

2 (L)

v yk e I о, м 1

Число два в выражении (4) может быть опущено, так как его наличие приводит только к изменению амплитудного диапазона выходного сигнала цифрового фильтра в формате ИКМ {уп}, а значение второй разности в этом случае равно:

22 ( L )

V yk

M 2

(2)

) 0

+ i

ие е

15

3)

20

ых

25

евана30

ду35

на4°

ть

л

4)

-,

+

45

50

5)

2 О

где значение V yk вычисляется согласно выражения (5).

Описанный алгоритм реализуется следующим образом.

Работа цифрового фильтра начинается с приходом установочного импульса на вход 7 обнуления. В результате воздействия этого импульса на всех выходах блоков 1 и сумматоров 2, 3 устанавливается нулевое значение сигнала. На входы 8, 9 (входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ) подаются значения коэффициентов весовой последо- вательности, причем в m-м блоке 1.т т О.т/2-1, значение коэффициентов равно и . На входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10, 11 с входа и выхода первого буферного регистра 13 поступает последовательность шагов квантования входного сигнала {Li } при k 0, которые сопровождаются тактовыми импульсами по входу 6. По переднему фронту импульса с входа 6 значение выходного сигнала сумматора 12 записывается во второй буферный регистр 14, а значение сигнала из регистра 14 блока 1.0 записывается в первый накапливающий сумматор 2, где суммируется с его нулевым значением. Одновременно значение выходного сигнала сумматора 2 запи- сывается во второй накапливающий сумматор 3, в результате на выходах фильтра подтверждается нулевое состояние.

Входная последовательность {L } при

k 0 поступает на -у- -разрядный регистр

сдвига, образованный одноразрядными регистрами 13 блока 1. Поэтому после поступления k импульсов с входа 5 на входе и выходе регистра 13 устанавливается значение шагов квантования входного сигнала

(х)

«W

ть 55 ит зоа в ноLk-m и Lk-m-i . С учетом значений весовой последовательности на входах 8 и 9 блока 1.т на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и 11 сформируется значения сигнала U-m(x) Ф L2mW и U-m-iw © ). Указанные значения в виде одноразрядного позиционного кода поступают на первый и второй входы сумматора 12, где суммируются со значением на его третьих входах, т.е. значением сигнала на вторых информационных входах блока 1.пл.

На вторые информационные входы блока 1. (-1) с источника 4 подано значение -М/2. Это значение суммируется с одноразрядными сигналами с выходов элементов 10 и 11 и при поступлении очередного импульса с входа 6 фиксируется в

регистре 4 блока 1. (д1 ). С выходов

этого регистра 14 указанное значение сигнала в следующем (к+1)-м такте поступает на третьи входы сумматора 12 в вычислительном блоке 1. (-и1 ), где суммируется со значением сигналов на выходах его элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и 11 т.е.

. (х)... ОХ

,,, 1

k + 1() ®L 2(.М-2) ()...(h)

(О

+ -(M-4) M+1-()1 ф|

|

(х)

k +

(h) 2(-Ј-2) + i

М

м

, (О

1 -(м -з) У L м -з

Таким образом, значения сигналов, вычисленные в к-м такте на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и 11 блока 1.т, поступают на вторые выходы блока 1.0 через m тактов, т.е. соответствуют (к+т)-му периоду дискретизации входного сигнала.

Аналогично производится накопление сигнала в последующих тактах, в результате на втором выходе блока 1,т в (к+ М/2-1)-м периоде дискретизации входного сигнала формируется значение сигнала:

м

-1

ц г (х)- О)

„ L (,+Ж-1-5)-3 L2S +

()

(h)

+ L ( .j.s).,.. tfc)L2S + 1j м

где индексы (k + -1 - S ) соответствуют номеру такта входного сигнала фильтра, а индекс S - номеру вычислительного блока 1.

На выходе блока 1.0 в ( k + -1 ) -м

периоде дискретизации выходного сигнала число слагаемых этой суммы равно М, а значение соответствует величине

2

V у

k +

М

- 1

Таким образом, на вторых выходах блока 1.0 формируется последовательность

2

значений {V yk} при k 0, которые поступают на последовательно включенные накапливающие сумматоры 2 и 3,

Рассмотрим формирование из последовательности значений {V выходного сигнала {уп} цифрового фильтра с момента 5 времени, когда на выходе блока 1 0 форми2

руется значение V у-|. По переднему фронту сигнала на входе 6 значение

2

V yi записывается в сумматор 2, где сум- мируется с его предыдущим значением, формируя сигнал Vyi. По переднему фронту следующего импульса с входа б производится суммирование выходного сигнала Vyi сумматора 2 с предыдущим, нулевым 5 значением выходного сигнала устройства в сумматоре 3. т.е. yi уо + Vyi Vyi, а в сумматоре 2 формируется значение

2

Vy2 Vyi+V у2. Дальше работа фильтра

0 происходит аналогично.

В случае случайных сбоев (например, по питанию) нормальная работа фильтра восстанавливается подачей установочного импульса на вход 7.

5 Таким образом, по сравнению с прототипом в предложенном фильтре уменьшено число одноразрядных регистров, а также расширена область его применения за счет использования импульсной характеристики

0 произвольного вида, в то время как, например, в прототипе импульсная характеристика должна быть симметричной относительно середины. Кроме того, реализация сумматора является более простой,

5 чем реализация реверсивного счетчика, а это также способствует уменьшению аппаратурных затрат фильтра по сравнению с прототипом.

Увеличение длины импульсной характе0 ристики приводит только к увеличению числа последовательно включенных блоков 1 и не требует изменения структуры цифрового фильтра в целом, что обеспечивает высокое качество фильтрации при высокой унифика5 ции устройства, которое легко реализуется в интегральном исполнении.

Формула изобретения Цифровой фильтр с линейной дельта- 0 модуляцией, содержащий вычислительные

блоки с нулевого по (-л- - 1 )-й (М - длина

импульсной характеристики), первый информационный вход нулевого вычислитель- 5 ного блока является информационным входом фильтра, первый выход -го вычислительного блока ( 0, ) соединен с

первым информационным входом ( + 1)-го

вычислительного блока, источник постоянного кода, первый накапливающий сумматор, выходы которого подключены к информационным входам второго накапливающего сумматора, выходы которого являются выходами фильтра, каждый вычислительный блок содержит первый и второй буферные регистры и первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого буферного регистра соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, информационный вход первого и выходы второго буферных регистров являются соответственно первым информационным входом и вторыми выходами соот- ветствующего вычислительного блока, тактовые входы буферных регистров всех вычислительных блоков объединены с тактовыми входами накапливающих сумматоров и являются тактовым входом фильтра, входы обнуления буферных регистров всех вычислительных блоков объединены с входами обнуления накапливающих сумматоров и являются входом обнуления фильтра, первые входы первых элементов ИСКЛЮ- ЧАЮЩЕЕ ИЛИ всех вычислительных блоков являются соответствующими первыми входами задания коэффициентов импульсной характеристики фмяьтра, отличающийся тем, что, с целью упрощения фильтра и расширения области его применения за счет использования импульсной характеристики произвольного вида, в каждый вычислительный блок введен сумматор, выходы которого соединены с информационными входами второго буферного регистра, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к первому информационному входу соответствующего вычислительного блока, выход первого буферного регистра является первым выходом соответствующего вычислительного блока, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первым и вторым входами сумматора, третьи входы которого являются вторыми информационными входами соответствующего вычислительного блока, вторые входы вторых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ всех вычислительных блоков являются соответствующими вторыми входами задания коэффициентов импульсной характеристики фильтра, выходы источника постоянного кода соединены с вторыми информационными

входами ( 1 )-го вычислительного блока, вторые выходы (1+1)-го вычислительного блока подключены к вторым информационным входам 1-го вычислительного блока, вторые выходы нулевого вычислительного блока соединены с информационными входами первого накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с симметричной импульсной характеристикой | 1987 |

|

SU1495979A1 |

| Цифровой фильтр с симметричной импульсной характеристикой | 1988 |

|

SU1589384A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1990 |

|

SU1730723A2 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1990 |

|

SU1716607A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661969A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1990 |

|

SU1716606A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661968A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

Изобретение относится к вычислительной технике. Его использование для цифровой фильтрации случайных процессов, представленных в формате линейной дельта-модуляции, позволяет упростить фильтр и расширить область его применения за счет использования импульсной характеристики произвольного вида. Цифровой фильтр содержит вычислительные блоки 1, накапливающие сумматоры 2, 3 и источник 4 постоянного кода, причем в вычислительный блок 1 входят элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 10. 11 и буферные регистры 13, 14. Положительный эффект достигается благодаря введению сумматора 12 и соответствующим соединением блоков. 1 ил

| Известия ВУЗов | |||

| Сер.: Радиоэлектроника, 27, 1984, №9, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-28—Публикация

1989-02-22—Подача