г- г

ел

00 UD 00 00 09

Изобретение относится,к цифровой обработке сигналов с применением дельта-модуляции и может быть исполь- - зовано для цифровой фильтрации слу- чайных процессов, представленных в формате линейной дельта-модуляции (ЛДМ) с преобразованием в формат им- пульсно-кодовой модуляции.

Цель изобретения - упрощение циф- рового фильтра за счет исключения умножителей.

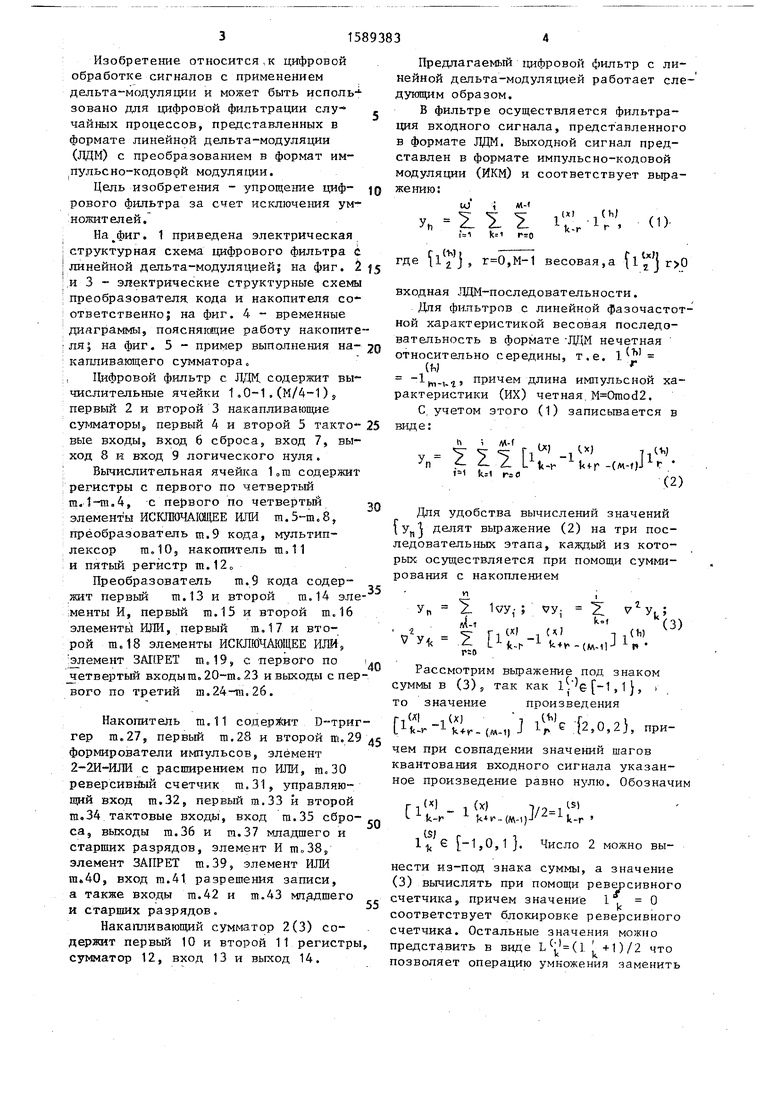

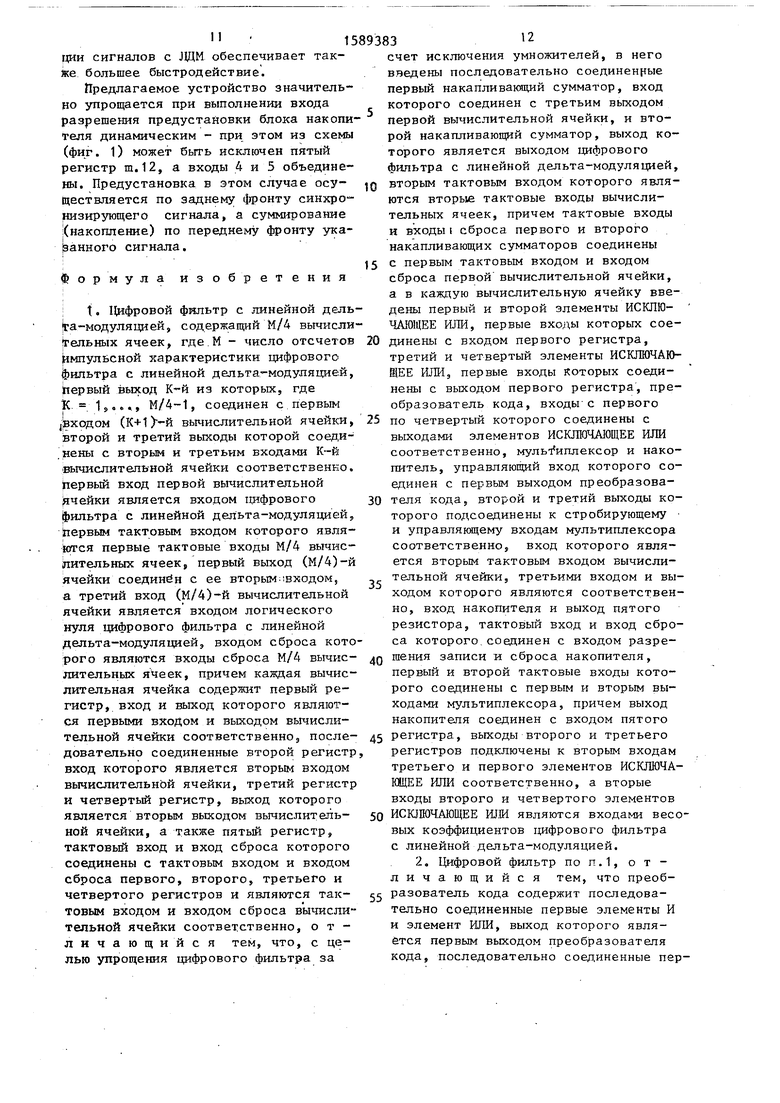

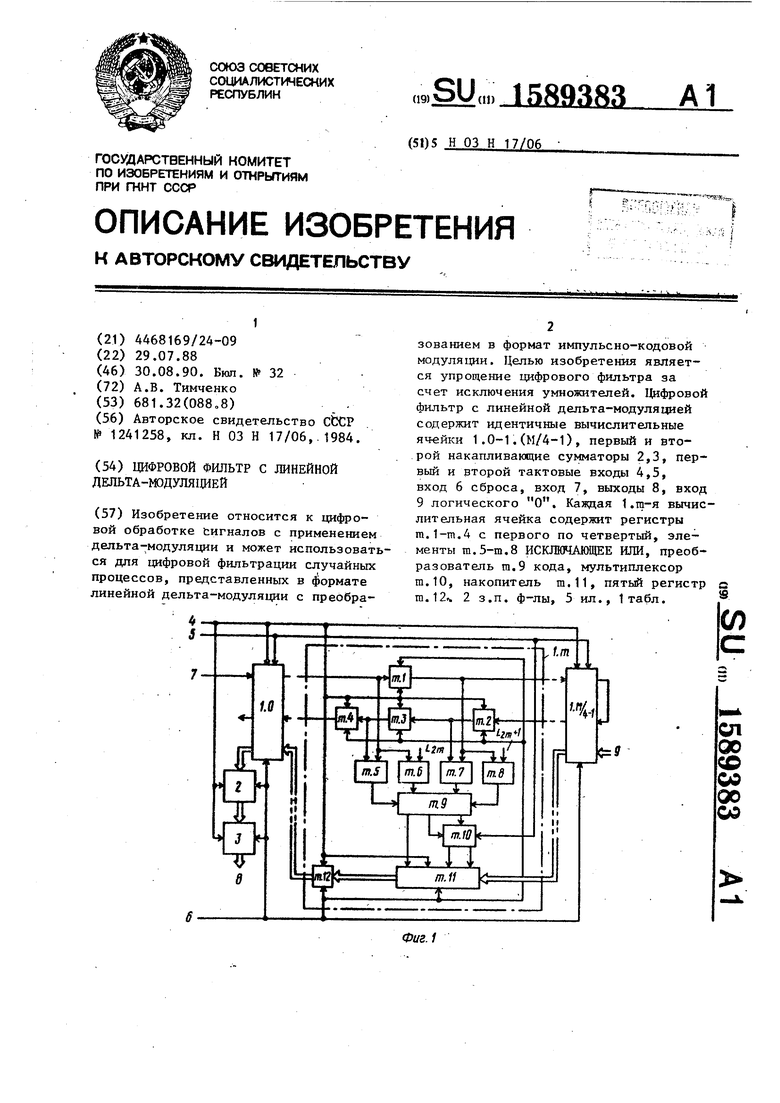

. 1 приведена электрическая ; структурная схема: цифрового фильтра с линейной дельта-модуляцией; на фиг. И .и 3 - электрические структурные схемы преобразователя кода и накопителя со- ответственно на фиг. 4 - временные диаграммы, пояснягацие работу накопите гля; на фиг. 5 - пример выполнения на- ; капливающего сумматора. ;, Цифровой фильтр с ЛДМ, содержит вычислительные ячейки 1,0-1.(М/4-1)5 первый 2 и второй 3 накапливающие сумматоры, первый 4 и второй 5 такто - вые входы, вход 6 сброса, вход 7, выход 8 и вход 9 логического нуля. Вьиислительная ячейка Km содержит ; регистры с первого по четвертый m.1-m.4, с первого по четвертьш элементы ЙСКЛЮЧА.КШ(ЕЕ ИЛИ in.5-m.8, : Преобразователь т,9 кода, мультиплексор т,10, накопитель и пятый регистр П1.12„

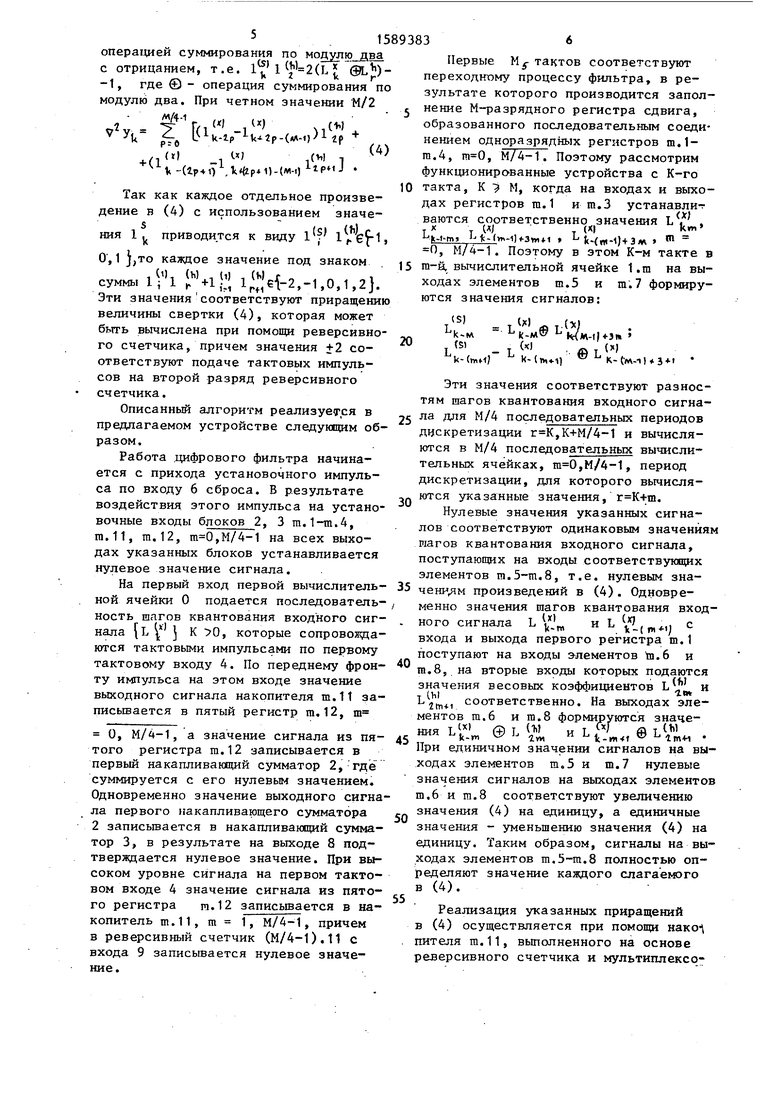

Преобразователь т.9 кода содержит первый т.13 и второй т.14 элементы И, первый га.15 и второй т.16 элементь ШШ, первый т. 17 и второй т, 18 элементы ИСКЛЮЧАЮЩЕЕ ИДИ-, :элемент ЗАПРЕТ т 19, с -первого по четвертый входыт.20-т. 23 и выходы с первого по третий т,24-1п.2б.

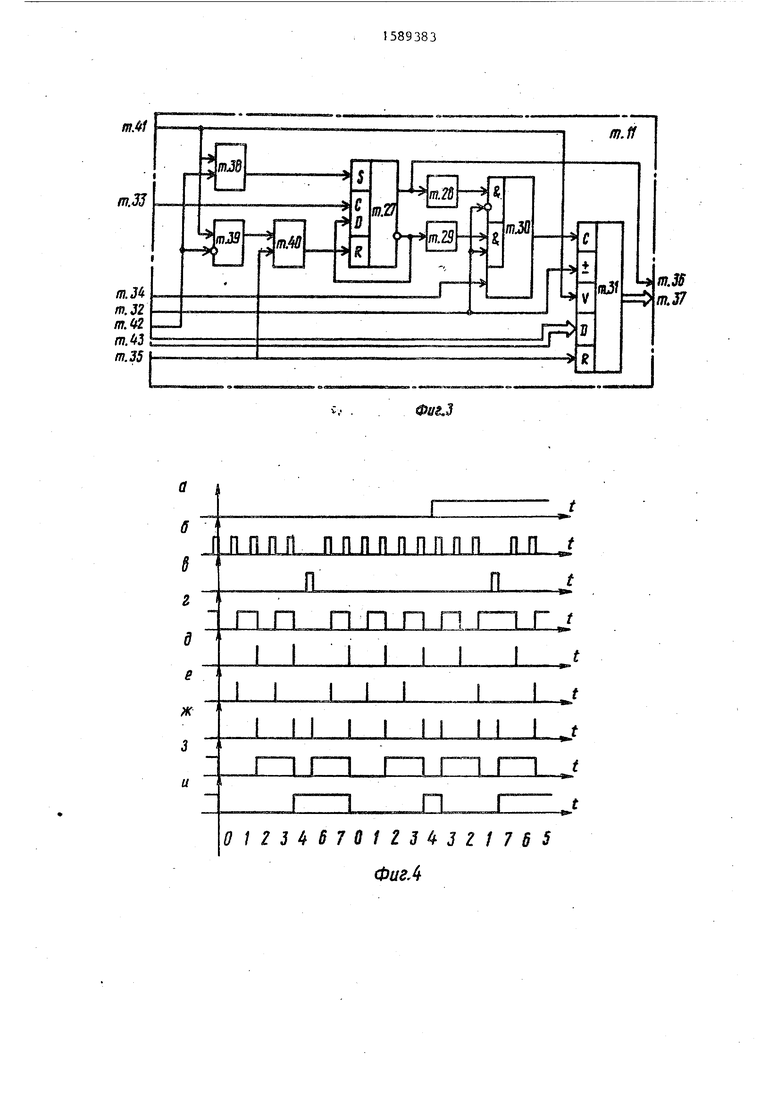

Накопитель т„11 содерЛит гер га.27, первый т.28 и второй iri.29 формирователи импульсов, элемент 2-2И-ИЛИ с расширением по ИЛИ, т.30 реверсивйый счетчик т.31, управляющий вход т.32, первый т.33 и второй т,34 тактовые входы, вход т.35 сброса, выходы т.36 и т.37 младшего и старших разрядов, элемент И т„38, элемент ЗАПРЕТ т.39, элемент ИЛИ , вход т.41 разрешения записи, а также входы т.42 и т.43 младшего и старших разрядов.

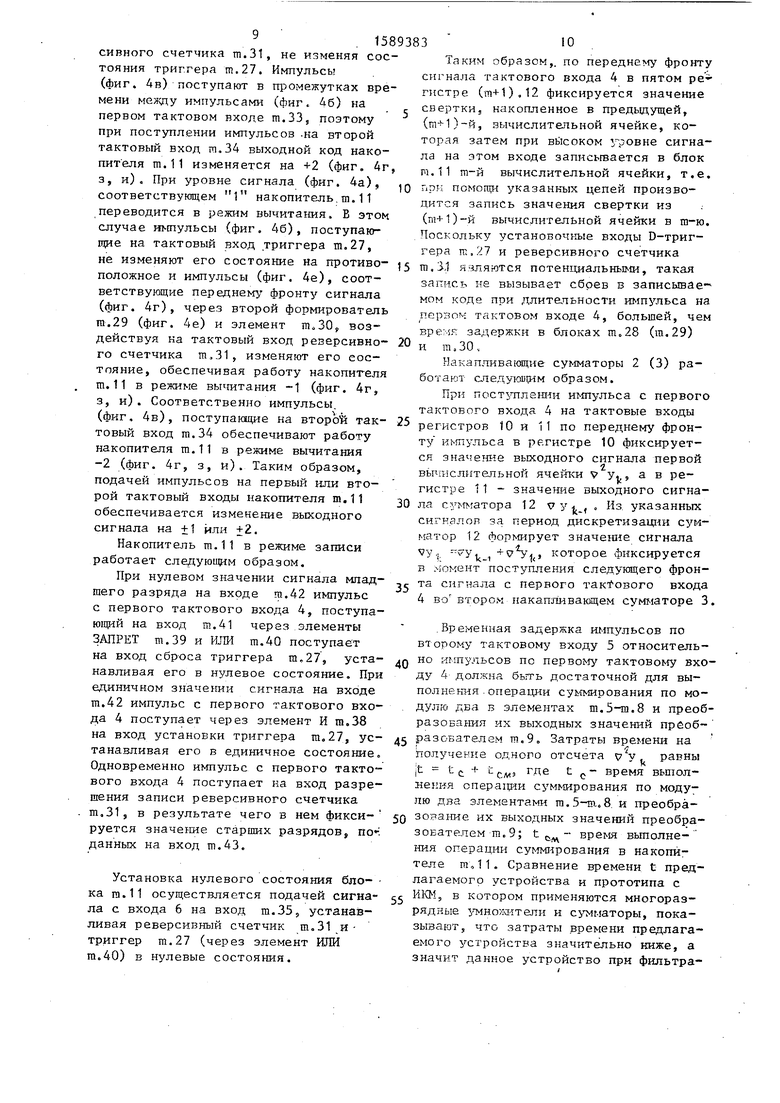

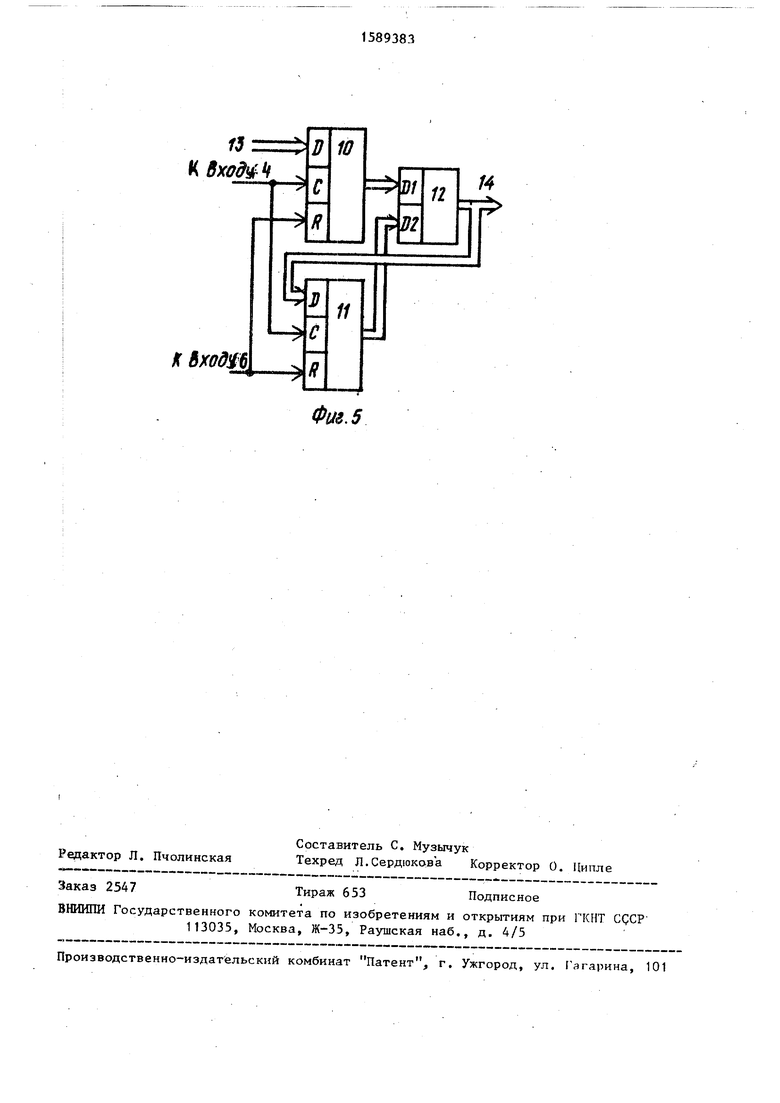

Накапливающий сумматор 2(3) содержит первый 10 и второй 11 регистры сзгмматор 12, вход 13 и выход 14.

Предлагаемый 11ифровой фильтр с линейной дельта-модуляцией работает следующим образом.

В фильтре осуществляется фильтрация входного сигнала, представленного в формате ЛДМ. Выходной сигнал представлен в формате импульсно-кодовой модуляции (ИКМ) и соответствует выражению:

ю i мУ. z 11 I :L-I , ( ГгО

k-r

где flD ,M-1 весовая,а fl j j

входная .ПДМ-последовательности.

Для фильтров с линейной фазочастот- ной характеристикой весовая последовательность в формате -ЛДМ нечетная относительно середины, т.е.

(

tn-. причем длина импульсной характеристики (ИХ) четная. M 0raod2.

С, учетом этого (1) записьгоается в виде:,

V S- .

УП III L4..-4.r-(M-t,J4 Ы r±e..

Для удобства вычислений значений 1У„ делят выражение (2) на три последовательных этапа, каждьй из которых осуществляется при помощи суммирования с накоплением

У г. 1vy,- ; vyj . ;

оЧ - Ф . I, L4-r-l и.-(ми1 1„Рассмотрим вьфажение под знаком суммы в (3)s так как -1 ,1), то значение произведения

lS.-lS.. (,..„ ,0,2}, при- чем при совпадении значений шагов квантования входного сигнала указанное произведение равно нулю. Обозначим

сС-1

(51

(Х)

k v -CM-i)

..nJ

IjOjl } Число 2 можно вынести из-под знака суммы, а значение (3) вычислять при помощи реверсивного счетчика, причем значение if, 0 соответствует блокировке реверсивного счетчика. Остальные значения можно представить в виде (l +1)/2 что позволяет операцию умножения заменить

оператщей суммирования по мощшю „ с отрицанием, т.е. (1. -1, где © - операция суммирования по модулю два. При четном значении М/2

(-} .ЛЯ

158 1ва

S/4 Т Га -1

и р4( (АЛ-«,)11р+ + П 1 1

V -(ip+l) Л«р41)-(М-1) .

(4)

Так как каждое отдельное произведение в (4) с использованием значе- (S)

КИЯ 1 . приводится к виду 1

iV e{-i.

0,1 J,To каждое значение под знаком

1 , суммы 1J 1

,-i,o,i,2j.

Эти значения соответствуют приращению величины свертки (4), которая может быть вычислена при помощи реверсивного счетчика, причем значения +2 соответствуют подаче тактовых импульсов на второй разряд реверсивного счетчика.

Описанный алгоритм реализуется в предлагаемом устройстве следующим образом.

Работа .цифрового фильтра начинается с прихода установочного импульса по входу 6 сброса. В результате воздействия этого импульса на установочные входы блоков 2, 3 т.1-т.4, га.11, га.12, ,М/4-1 на всех выходах указанных блоков устанавливается нулевое значение сигнала.

Нулевые значения указанных сигна лов соответствуют одинаковым значен piaroB квантования входного сигнала, поступающих на входы соответствующи элементов m.5-m.8, т.е. нулевым зна

На первый вход первой вычислитель- 35 произведений в (4). Одновре- НОИ ячейки О подается последователь-у ность шагов квантования входного

нала L К 0, которые сопровождаются тактовыми импульсами по первому тактовому входу 4. По переднему фронту импульса на этом входе значение выходного сигнала накопителя т.11 за- письшается в пятый регистр га.12, т

О, М/4-1, а значение сигнала из пятого регистра га.12 записывается в первый накапливающий сумматор 2, где суммируется с его нулевым значением. Одновременно значение выходного сигнала первого накапливающего сумматора 2 записьшается в накапливающий сумматор 3, в результате на выходе 8 под- тверзкдается нулевое значение. При высоком уровне сигнала на первом тактовом входе 4 значение сигнала из пятого регистра т.12 записьшается в накопитель т.11, га 1, М/4-1, причем в реверсивный счетчик (М/4-1).11 с входа 9 записывается нулевое значение.

менно значения шагов квантования вх U) „ т (щ

ного сигнала L

и L

1-(

входа и выхода первого регистра т.1

40

поступают на входы элементов ta.S и та.8, на вторые входы которых подаютс

значения весовых коэффициентов

(Ы

гп

2(71+1 соответственно. На выходах эле ментов га.6 и т.8 формируются знаце45

ния L

IX)

k-pi

т (W Iwi

И

т f«;

V-m41

@ L

(W Im-H

50

55

При единичном значении сигналов на в ходах элементов га.З и га.7 нулевые значения сигналов на выходах элемент га.6 и га.8 соответствуют увеличению значения (4) на единицу, а единичные значения - уменьшению значения (4) н единицу. Таким образом, сигналы на в ходах элементов га,5-га.8 полностью оп ределяют значение каждого слагаемого в (4).

Реализация указанных приращений в (4) осуществляется при помощи нако пителя га.11, вьтолненного на основе реверсивного счетчика и мультиплексо

9383

Первые тактов соответствуют переходнпму процессу фильтра, в результате которого производится запол нение М-разрядного регистра сдвига, образованного последовательным соединением одноразрядных регистров т.1- га.4, , М/4-1. Поэтому рассмотрим функционированные устройства с К-го

10 такта, К } М, когда на входах и выходах регистров га. 1 и га.З устанавли-г

ваются соответственно значения L , . , (

t-H,,, bjM№-i)-3wfi i-k-(ni-i)+3M - 0, М/4-1. Поэтому в этом К-м такте в 15 га-й, вычислительной ячейке l.ra на выходах элементов т.5 и га.7 формируются значения сигналов:

k-w - LK-M© LMM-I|OI« 5 - Т Лт

k-(n,H) k-(«,)

() K-( M--i)

Эти значения соответствуют разностям шагов квантования входного сигна25 ла для М/4 последовательных периодов дискретизации ,К+М/4-1 и вычисляются в М/4 последовательных вычислительных ячейках, ,М/4-1, период дискретизации, для которого вычисля2Q ются указанные значения, .

Нулевые значения указанных сигналов соответствуют одинаковым значения piaroB квантования входного сигнала, поступающих на входы соответствующих элементов m.5-m.8, т.е. нулевым зна35 произведений в (4). Одновре-

5 произведений в (4). Одновре-

менно значения шагов квантования вход- U) „ т (щ

ного сигнала L

и L

1-(

входа и выхода первого регистра т.1

0

поступают на входы элементов ta.S и та.8, на вторые входы которых подаются

и

значения весовых коэффициентов

(Ы

гп

2(71+1 соответственно. На выходах элементов га.6 и т.8 формируются знаце5

ния L

IX)

k-pi

т (W Iwi

И

т f«;

V-m41

@ L

(W Im-H

0

5

При единичном значении сигналов на выходах элементов га.З и га.7 нулевые значения сигналов на выходах элементов га.6 и га.8 соответствуют увеличению значения (4) на единицу, а единичные значения - уменьшению значения (4) на единицу. Таким образом, сигналы на выходах элементов га,5-га.8 полностью определяют значение каждого слагаемого в (4).

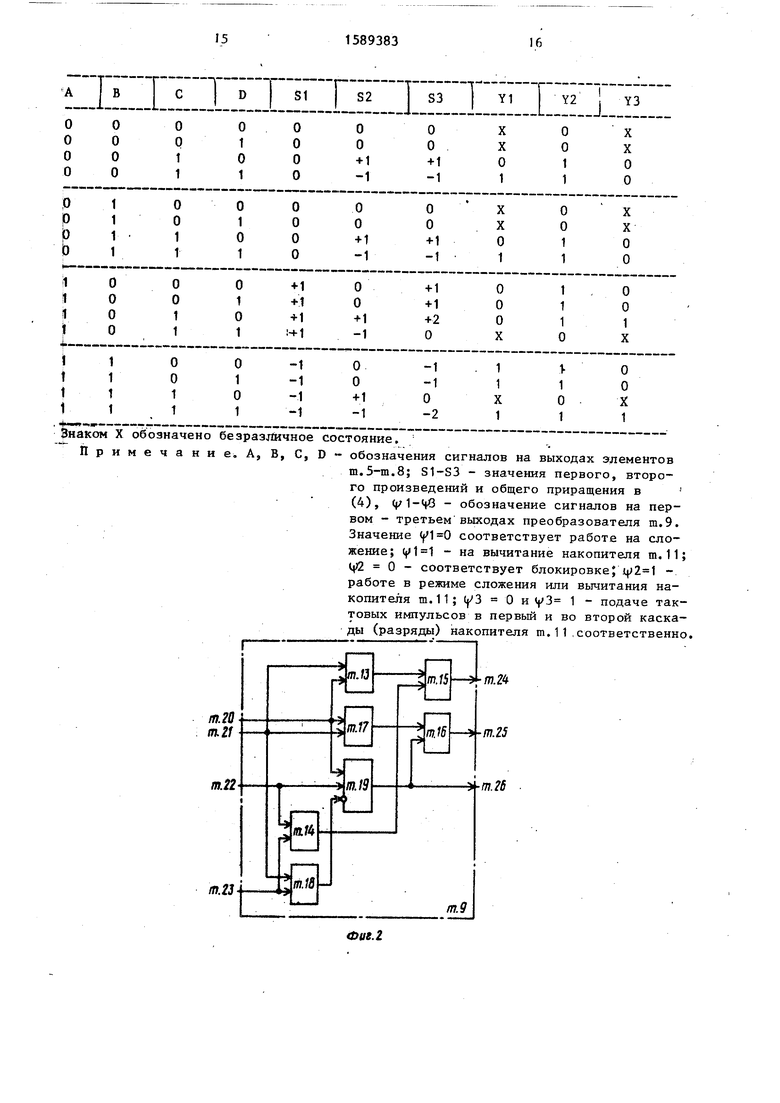

Реализация указанных приращений в (4) осуществляется при помощи нако- пителя га.11, вьтолненного на основе реверсивного счетчика и мультиплексоpa m. 10, в одном такте, нуле-вое значение приращения соответствует блокировке счетчика, а ± 2 подаче тактовых импульсов во второй каскад счетчика. Для реализации этих функций при помощи преобразователя т,9 сводят указанные соотношения в таблицу

(

Логические функции у , реали- зуются как функции переменных.А, В,

,..

из табл. 1 можно определить что у А© С + АС (B®D).

Если два последних безразличных состояния 3 Ц) заменить значением 1, а все безразличные состояния вц}3 - О, то20

у АВ + CD; (4)5 АС (B©D)s

откуда ц1 А © С

Поэтому при поступлении импульсов с второго тактового входа 5 на инфор- 1мационньй вход мультиплексора т,10 Последний передает этот импульс- на , первый или второй тактовый вдод .накопителя то11 согласно таблице, Тов согласно значению сигналов на выходах элементов m.5-m,8. В результате этого состояние накопи-теля т. 11 изменяется в соответствии с выражением под знаком суммы в (4).

В следуицем такте значение выходного сигнала накопителя т. 1.1 переписывается через пятый регистр т.12 в накопитель (m-1).11 с,пегг,ующей (т-1)-й вычислительной ячейкиj где при поступлении очере,цного импульса с, второго тактового входа 5 суммируется со значением:

f UItxj. (bj

t:f(.l(ni-i) - 1.-и-(ли-Ц -Кц-) J Кяп-П

VXj/

С a(w,-i)Mj- -4-n - (м-1)4-рЫч)-1}Г1 (w-D-H

величина которого определяется значением сигналов на выходах элементов mc5-m,8 в -.(K+D-M такте.

. Таким образом5 последовательно от вычислительной ячейки 1. к вычислительной ячейке 1,0 производится .накопление значений под знаком суммы в (4), начиная с Р М/4-1, еоответст-. вующего номеру вычислительной ячейки.

j

5

0

25

Q

40

50

и заканчивая , в результате чего на выходе первой вычислительной ячей- ,ки 1.0 в (К+М/4-1)-м такте входного сигнала формируется значение v У. Гаким образом, на третьем выходе первой вычислительной ячейки 1.0 формируется последовательность значений fv у , К О, которые поступают на последоват.ельно включенные накапливающие сумматоры 2 и 3.

Рассмотрим формирование выходного сигнала jy У ирнфрового фильтра с момента времени, когда на выходе первой вычислительной ячейки 1.0 формируется значение . По сигналу на первом

rt

тактовом входе 4 значение у записывается в сумматор 2, где суммир-у- ется с его предьщущим значением, формируя сигнал V у , После прихода следующего синхроимпульса производится суммирование выходного сигнала первого накапливающего сумматора 2 с предыдущим значением выг одного сигнала устройства во втором накапливающем сумматоре 3 у Уд+ , а в первом накапливающем сумматоре 2 формируется значение у vy vy Дальше устройство работает аналогично описанному,

В случае случайных сбоев, например, по питанию нормальная работа предла- - гаемого устройства восстанавливается подачей сигнала на вход 6 сброса.

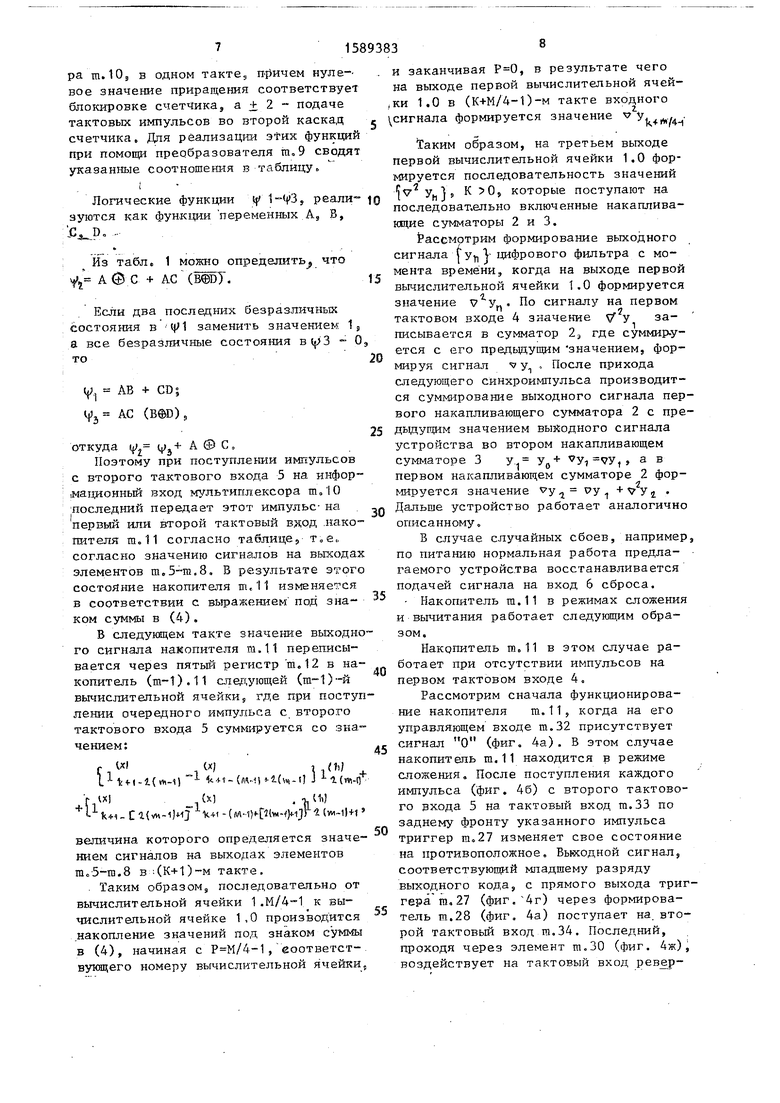

- Накопитель т.11 в режимах сложения и вычитания работает следующим образом.

Накопитель т.11 в этом случае работает при отсутствии импульсов на первом тактовом входе 4.

Рассмотрим сначала функционирование накопителя т.11, когда на его управляющем входе т.32 присутствует сигнал О (фиг. 4а). В этом случае накопитель т.11 находится в режиме сложения. После поступления каждого импульса (фиг. 46) с второго тактового входа 5 на тактовый вход т.33 по заднему фронту указанного импульса триггер га.27 изменяет свое состояние на противоположное. Вьнходной сигнал, соответствующий младшему разряду выходного кода, с прямого выхода триггера га. 27 (фиг.Чг) через формирователь т.28 (фиг. 4а) поступает на. второй тактовый вход т.34. Последний, проходя через элемент т.30 (фиг. 4ж), воздействует на тактовый вход ревер 158

сивного счетчика та.31, не изменяя состояния триггера т.27. Импульсы (фиг. 4в) поступают в промежутках времени между импульсами (фиг. 4б) на первом тактовом входе т.33, поэтому при поступлении импульсов -на второй тактовый вход га.34 выходной код накопителя га.11 изменяется на +2 (фиг, Аг, 3, и). При уровне сигнала (фиг. 4а), соответствующем 1 накопитель.т.11 переводится в режим вычитания. В этом случае импульсы (фиг, 46), поступающие на тактовый вход триггера т.27,

Таким образом,, по переднему фронту сигнала тактового входа 4 в пятом ре гистре (га+1),12 фиксируется значение свертки, накопленное в предьщущей, (т+1)-Й5 вычислительной ячейке, которая затем при высоком 1,фовне сигнала на этом входе записьгеается в блок т. 11 тп-й вычислительной ячейки, т.е. при помощи указанных цепей производится запись значения свертки из ; (т+1)-й вычислительной ячейки в ш-ю. Поскольку установочные входы D-триг- гера ГС.27 и реверсивного счетчика

не изменяют его состояние на противо- iс -л

а д длиьи )5 ni,i,1 я-шяются потенциальными, такая положное и импульсы (Фиг. 4е) с-оот-

у ш чФИ1 . че/, с,иотзапись не вызывает сбоев в записывавветствующие переднему фронту сигнала (фиг. 4г), через второй формирователь та.29 (фиг. 4е) и элемент m.BOf воздействуя на тактовый вход реверсивного счетчика т,31, изменяют его состояние, обеспечивая работу накопителя т.11 в режиме вычитания -1 (фиг. 4г, 3, и). Соответственно импульсы.

35

(фиг, 4в), поступающие на второй так- 25 товый вход га.34 обеспечивают работу накопителя т.11 в режиме вычитания -2 (фиг. 4г, 3, и). Таким образом, подачей импульсов на первый или вто- рой тактовый входы накопителя т.11 обеспечивается изменение выходного сигнала на +1 или +2.

Накопитель т.11 в режиме записи работает следующим образом.

При нулевом значении сигнала мпад- шего разряда на входе т.42 импульс с первого тактового входа 4, поступа- Ю1ЦИЙ на вход т.41 через .элементы ЗАПРЕТ т.39 и ИЛИ т.40 поступает на вход сброса триггера т,27, устанавливая его в нулевое состояние. При единичном значении сигнала на входе т.42 импульс с первого тактового входа 4 поступает через элемент И га.38 на вход установки триггера га,27, устанавливая его в единичное состояние. Одновременно импульс с первого тактового входа 4 поступает на вход разрешения записи реверсивного счетчика т.31, в результате чего в нем фикси- руется значение старших разрядов, по. данных на вход т.43.

мои коде при длитаттьности импульса на . .первом тактовом входе 4, большей, чем

время задержки в блоках т,28 (га.29) 20 и пьЗО,

Накапливающие сумматоры 2 (3) работают следуюБщм образом.

При пост тглешад и шульса с первого тактового входа 4 на тактовые входы

регистров to и 11 по переднему фронту иьшульса в регистре 10 фиксируется значение выходного сигнала первой

1

вы шслительной ячейки v у

V

а в регистре 11 - значение выходного сигна- 30 ла суьгматора 12 v у i,, , Из. указанных сигкалоп за период дискретизации сумматор 12 формирует значение сигнала vy.j. vy +7V|(S которое фиксируется в момент поступления следующего фронта сигнала с первого тактового входа

4 .во втором накапливающем сумматоре 3.

.Временная задержка импульсов по второму тактовому входу 5 относитель Q но импульсов по первом тактовому входу 4 должна быть достаточной для вы- полне:ния .операции суммирования по мо- . дулю два в элементах га.5-т.8 и преоб- разова шя их выходных значений преоб-

д5 разоБателем т.9, Затраты времени на получение одного отсчета vV. равны jt t (. Lj,3 где t ,- время вьтол- нения опера1щи суммирования по модулю два элементами га. 5-ю..8. и преобразование их выходных значений преобразователем га, 9; t с, - вьтолне- ния операции суммирования в накопителе га, 11 . Сравнение времени t предлагаемого устройства и прототипа с ШШ, в котором применяются многоразрядные умноло-гтел-ги и сумматоры, показывают, что затраты времени предлагаемого устройства значительно ниже, а значит данное устройство при фильтра50

Установка нулевого состояния бло- ка га.11 осуществляется подачей сигнала с входа 6 на вход га.35, устанавливая реверсивный счетчир; т.31 и- триггер га.27 (через элемент ИЛИ га.40) в нулевые состояния.

10

0

Таким образом,, по переднему фронту сигнала тактового входа 4 в пятом ре гистре (га+1),12 фиксируется значение свертки, накопленное в предьщущей, (т+1)-Й5 вычислительной ячейке, которая затем при высоком 1,фовне сигнала на этом входе записьгеается в блок т. 11 тп-й вычислительной ячейки, т.е. при помощи указанных цепей производится запись значения свертки из ; (т+1)-й вычислительной ячейки в ш-ю. Поскольку установочные входы D-триг- гера ГС.27 и реверсивного счетчика

с -л

5

5

мои коде при длитаттьности импульса на . .первом тактовом входе 4, большей, чем

время задержки в блоках т,28 (га.29) 0 и пьЗО,

Накапливающие сумматоры 2 (3) работают следуюБщм образом.

При пост тглешад и шульса с первого тактового входа 4 на тактовые входы

регистров to и 11 по переднему фронту иьшульса в регистре 10 фиксируется значение выходного сигнала первой

1

вы шслительной ячейки v у

V

а в регистре 11 - значение выходного сигна- 0 ла суьгматора 12 v у i,, , Из. указанных сигкалоп за период дискретизации сумматор 12 формирует значение сигнала vy.j. vy +7V|(S которое фиксируется в момент поступления следующего фронта сигнала с первого тактового входа

4 .во втором накапливающем сумматоре 3.

.Временная задержка импульсов по второму тактовому входу 5 относительно импульсов по первом тактовому входу 4 должна быть достаточной для вы- полне:ния .операции суммирования по мо- дулю два в элементах га.5-т.8 и преоб- разова шя их выходных значений преоб-

разоБателем т.9, Затраты времени на получение одного отсчета vV. равны jt t (. Lj,3 где t ,- время вьтол- нения опера1щи суммирования по модулю два элементами га. 5-ю..8. и преобразование их выходных значений преобразователем га, 9; t с, - вьтолне- ния операции суммирования в накопителе га, 11 . Сравнение времени t предлагаемого устройства и прототипа с ШШ, в котором применяются многоразядные умноло-гтел-ги и сумматоры, показывают, что затраты времени предлагаемого устройства значительно ниже, а начит данное устройство при фильтра

дай сигналов с JЩM обеспечивает также большее быстродействие.

Предлагаемое устройство значительно упрощается при выполнении входа разрешения предустановки блока накопителя динамическим - при этом из схемы (фиг. 1) может быть исклЕочен пятый регистр т.12, а входы 4 и 5 объединены. Предустановка в этом случае осуществляется по заднему фронту синхро- низирз Щвго сигнала, а суммирование :(накопление) по переднему фронту ука- |занного сигнала.

формула изобретения

t. Цифровой фильтр с линейной дельта-модуляцией, содерткащий М/4 вычисли

1гельных ячеек, где. М - число отсчетов импульсной характеристики цифрового фильтра с линейной дельта-модуляцией, первый выход К-й из которых, где К. 1s..., М/4-1, соединен с первым (входом ( вычислительной ячейки, второй и третий выходы которой соел;и- .нены с вторым и третьим входами К-й |вьгчислитель-ной ячейки соответственно. первый вход первой вычислительной |ячейки является входом тшфрового фильтра с линейной дельта-модуляцией, Первым тактовым входом которого явля- Ьгся первые тактовые входы М/4 вычислительных ячеек, первый выход (М/4)-и ячейки соединён с ее вторым:1входом, а третий вход (М/4)-и вычислительной ячейки является входом логического нуля цифрового фильтра с линейной дельта-модуляцией, входом сброса которого являются входы сброса М/4 вычислительных ячеек, причем каждая вычислительная ячейка содержит первый регистр, вход и выход которого являются первыми входом и выходом вьгчисли

тельной ячейки соответственно, после- довательно соединенные второй регистр вход которого является вторым входом вычислительнЬй ячейки, третий регистр и четвертый регистр, выход которого является вторым выходом вычислительной ячейки, а также пятый регистр, тактовый вход и вход сброса которого соединены с тактовым входом и входом сброса первого, второго, третьего и четвертого регистров и являются тактовым входом и входом сброса вычислительной ячейки соответственно, отличающийся тем, что, с целью упрощения цифрового фильтра за

счет исключения умножителей, в него введены последовательно соединенные первый накапливающий сумматор, вход которого соединен с третьим выходом первой вычислительной ячейки, и второй накапливающий сумматор, выход которого является выходом цифрового фильтра с линейной дельта-модуляцией,

вторым тактовым входом которого являются вторые тактовые входы вычислительных ячеек, причем тактовые входы и входы I сброса первого и второго накапливающих сумматоров соединены

с первым тактовым входом и входом сброса первой вычислительной ячейки, а в каждую вычислительную ячейку введены первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых соединены с входом первого регистра,

третий и четвертый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых соединены с выходом первого регистра, преобразователь кода, входы с первого по четвертый которого соединены с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, мульт иплексор и накопитель, управляющий вход которого со

единен с первым выходом преобразователя кода, второй и третий выходы которого подсоединены к стробирующему и управляющему входам мультиплексора соответственно, вход которого является вторым тактовым входом вычислительной ячейки, третьими входом и выходом которого являются соответственно, вход накопителя и выход пятого резистора, тактовый вход и вход сброса которого,соединен с входом разрешения записи и сброса накопителя, первый и второй тактовые входы которого соединены с первым и вторым выходами мультиплексора, причем выход накопителя соединен с входом пятого регистра, выходы второго и третьего регистров подключены к вторым входам третьего и первого элементов ИСКЛЮЧА- ЩЕЕ ИЛИ соответственно, а вторые входы второго и четвертого элементов ИСЮПОЧАЮЩЕЕ ИЛИ являются входами весовых коэффициентов цифрового фильтра с линейной дельта-модуляцией.

2, Цифровой фильтр по П.1, отличающийся тем, что преобразователь кода содержит последовательно соединенные первые элементы И и элемент ИЛИ, выход которого является первым выходом преобразователя кода, последовательно соединенные пер

10

вый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и второй элемент ИЛИ, выход которого является вторым выходом преобразователя кода,: элемент ЗАПРЕТ, выход которого соеди-: иен с вторым входом второго элемента ИЛИ и является третьим выходом преобразователя кода, второй элемент И, выход которого подключен к второму входу первого элемента ИЛИ, и второй элемент ИСКЛЮЧАЩЕЕ ИЛИ, выход которого соединен с инверсным выходом элемента ЗАПРЕТ, первый вход которого соединен с первыми Ёходами первых элементов И и ИСКЛЮЧАЩЕЕ ИЛИ и являет- j ся первым входом преобразователя кода, вторым входом которого являются вторые входы первых элементов И и ИСКЛЮЧАЩЕЕ ЮТИ и первьй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход ко-20 торого соединен с первым входом второго элемента И и является четвертым входом преобразователя кода; третьим входом которого являются вторые входы второго элемента И и элемента АПРЕТ. 25

первый и второй входы которого пoдкJ: ю- чены к выходам первого и второго фор - мирователя импульсов соответственно, реверсивный счетчик, управлякщий вход которого соединен с третьим и четвертым входами элемента 2-2И-ИЛИ С РАСШИРЕНИЕМ ПО ИЛИ и является управляющим входом накопителя, элементы И и ЗАПРЕТ, первые входы которых соедине3. Цифровой фильтр по п. 1, от- личающийся тем, что накопи- .тель содержит D-триггер, тактовый вход которого является первым вым входом накопителя, первый и второй формирователи импульсов, входы которых соединены с прямым и инверсным выходами D-триггера соответственно, элемент 2-2И-ИПИ С РАСШИРЕНИЕМ ПО ИЛИ,

ны с входом разрешения записи реверсивного счетчика и являются входом разрешения записи накопителя, и элемент ИЛИ, первый вход которого является входом сброса накопителя и соединен с входом сброса реверсивного счетчика, тактовый вход которого соединен с выходом элемента 2 -2И-ИЛИ С РАСШИРЕНИЕМ,ПО ИЛИ, вход расширения которого является вторым тактовым входом накопителя, выходом старших и мпадших разрядов которого являются выходы реверсивного счетчика и D-триг гера соответственно, инверсный выход которого соединен с информационным входом D-триггера, входы установки и сброса которого соединены с выходом элемента И и элемента ИЛИ, второй вход которого соединен с выходом эле- такто- 30 мента ЗАПРЕТ, инверсный вход которого соединен с вторьм входом элемента И и является входом младшего разряда накопителя, входом старших разрядов которого является вход реверсивного счетчика„

первый и второй входы которого пoдкJ: ю- чены к выходам первого и второго фор - мирователя импульсов соответственно, реверсивный счетчик, управлякщий вход которого соединен с третьим и четвертым входами элемента 2-2И-ИЛИ С РАСШИРЕНИЕМ ПО ИЛИ и является управляющим входом накопителя, элементы И и ЗАПРЕТ, первые входы которых соедине Знаком X обозначено безразшчное сослояниё .

П р и м е ч а н и е. А, В, С, D - обозначения сигналов на выходах элементов

m.5-m.8; S1-S3 - значения первого, второго произведений и общего приращения в (4), (j/1-ЦО - обозначение сигналов на первом - третьем выходах преобразователя т.9. Значение ( соответствует работе на сложение; у - на вычитание накопителя т. 11; Ц2 О - соответствует блокировке; - работе в режиме сложения или вычитания накопителя т.11; уз О и уЗ 1 - подаче тактовых импульсов в первый и во второй каскады (разряды) накопителя т.11.соответственно.

Фи.$

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр с симметричной импульсной характеристикой | 1987 |

|

SU1495979A1 |

| Цифровой трансверсальный фильтр | 1987 |

|

SU1517118A1 |

| Цифровой фильтр с дельта-модуляцией | 1987 |

|

SU1418908A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Анализатор активности непрерывных сигналов | 1989 |

|

SU1658386A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1989 |

|

SU1631707A1 |

Изобретение относится к цифровой обработке сигналов с применением дельта-модуляции и может использоваться для цифровой фильтрации случайных процессов, представленных в формате линейной дельта-модуляции с преобразованием в формат импульсно-кодовой модуляции. Целью изобретения является упрощение цифрового фильтра за счет исключения умножителей. Цифровой фильтр с линейной дельта-модуляцией содержит идентичные вычислительные ячейки 1.0-1.(M/4-1), первый и второй накапливающие сумматоры 2, 3, первый и второй тактовые входы 4, 5, вход 6 сброса, вход 7, выходы 8, вход 9 логического "0". Каждая 1.M-я вычислительная ячейка содержит регистры M.1-M.4 с первого по четвертый, элементы M.5 - M.8 ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразователь M.9 кода, мультиплексор M.10, накопитель M.11, пятый регистр M.12. 2 з.п. ф-лы, 5 ил., 1 табл.

| Устройство для цифровой фильтрации | 1984 |

|

SU1241258A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-30—Публикация

1988-07-29—Подача