сд

ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1631752A1 |

| Устройство для сжатия цифровых телевизионных сигналов цветного изображения | 1988 |

|

SU1529471A1 |

| Устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1607080A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для считывания изображений | 1984 |

|

SU1179394A1 |

| СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 1992 |

|

RU2022356C1 |

| Устройство для контроля | 1985 |

|

SU1295421A1 |

| Многофункциональный преобразователь | 1986 |

|

SU1401479A1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

Изобретение относится к технике передачи и хранения цветных изображений в системах с применением телевизионных дисплеев и видеотерминалов. Цель изобретения - увеличение коэффициента сжатия. Устройство содержит АЦП 1, блок 2 установки опорного уровня, блок 6 управления, два блока 7, 11 сравнения, блок 12 памяти, преобразователь 13 кода. Для достижения указанной цели в устройство введены блок 3 элементов И, три регистра 4, 5, 10 и два счетчика 8,9. Когда будет прекращена выдача тактовых и управляющих импульсов на блоки устройства, оно из режима считывания информации в канал переходит в режим ожидания поступления кадрового синхроимпульса следующего кадра. 1 з.п. ф-лы, 2 ил.

(fuel ,

315

Изобретение относится к технике передачи и хранения цветных изображений в системах с применением телевизионных дисплеев и видеотерминалов и может быть использовано в автоматизированных системах отображения, обработки данных и управления.

Цель изобретения - увеличение коэффициента сжатия.

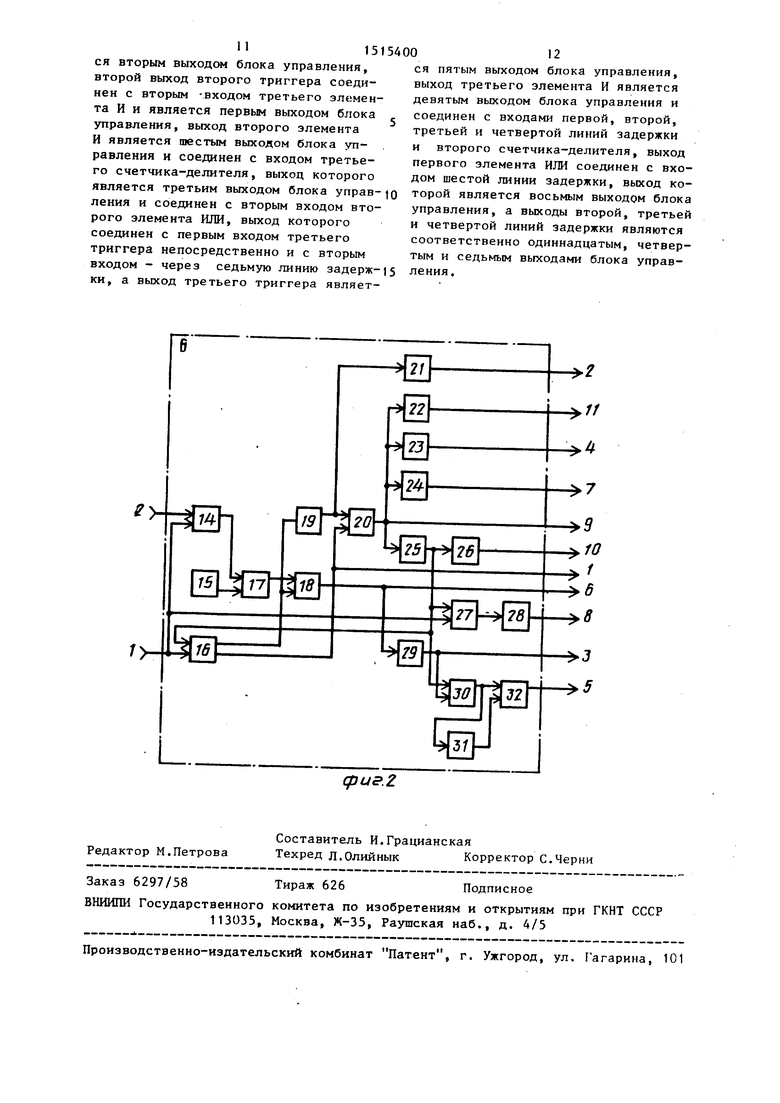

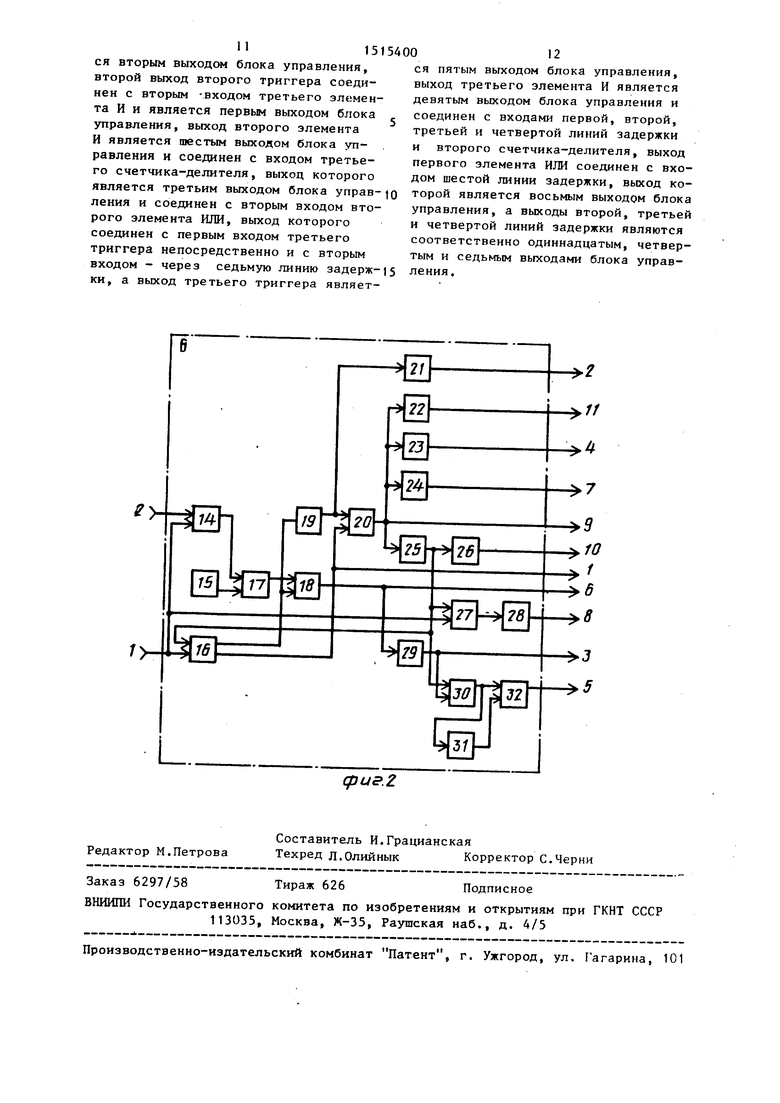

На фиг. 1 представлена структурная электрическая схема устройства; на фиг. 2 - функциональная электрическая схема блока управления.

Устройство для сжатия цветовых сигналов телевизионных изображений содерямт аналого-цифровой преобразо- .чь (лип) 1 , блок 2 установки опорного фовня, блок 3 элементов И, псрпый 4 и второй 5 регистры, блок 6 уиргшленпя, первый блок 7 сравнения, псррый 8 и второй 9 счетчики, третий рег истр 10, второй блок 11 сравнения блок 12 памяти и преобразователь 13 кода.

Блок 6 (фиг. 2) содержит первый триггер 14, генератор 15 тактовых импульсов, второй триггер 16, первый |17 и нторой 18 элементы И, первый счетчик-делитель 19, третий элемент И 20, первую - четвертую линии 21 - 24 задрржки соответственно, второй счетчик-делитель 25, пятую линию-26 задержки, первый элемент ИЛИ 27, шестую линию 28 задержки, третий , счетчик-делитель 29, второй элемент ИЛИ 30, седьмую линию 31 задержки и третий триггер 32.

Устройство работает следующим образом.

Входной аналоговый сигнал поступает одновременно на входы аналого- цифрового преобразователя 1 и блока 2 установки опорного уровня. В пос леднем производится формирование стартового импульса, которьп поступает на блок 6 управления, разрешая его работу. Параллельный код с выхода АЦП 1 поступает на первый вход блока 3 элементов И, на второй вход которого поступает управляющий сигнал с выхода блока 6 управления, который разрешает прохождение кода цвета на информационный вход первого регистра 4 при обработке кадра и записи инструкций в блок 12 памяти и запрещает - при считывании инструкци из блока 12 памяти. Паралелышй код, поступив1иий на информационный вход

04

первого регистра 4, записывается в него по приходу на вход регистра тактового импульса с выхода блока 6 управления. Код с выхода первого регистра 4 записывается в регистр 5 по приходу на вход BTOpoi o регистра 5 тактового импульса с выхода блока 6 управления. Так как тактовые импульсы на второй регистр 5 поступают с некоторым опережением тактовых импульсов, поступающих на первый регистр 4, то Во второй регистр 5 записывается код, соответствующий предыдy цe ry элементу отображения, а в пер- Bbiii регистр 4 - код, соответствующий последнему элементу отображения. Параллельный код с выхода первого регистра 4 поступает на вход первого

блока 7 срав 1ения, на другой вход которого поступает параллельный код с выхода второго регистра 5. В случае несовпадения кодов па выходе первого блока 7 сравне1гия в момент подачи

тактового импульса с выхода блока 6 управления формируется единичный импульс .

В исходном состоянии первый ре, гистр 4 обнулен. К моменту записи кода первого элемента отображения кадра в первый регистр 4 во второй регистр 5 с выхода первого регистра 4 переписывается комбинация из п нулей. При сравнении (в случае гесовпадения содержимого регистров 4 и 5) на выходе первого блока 7 сравнения появляется единичный импульс. Этот сигнал одновременно поступает на счетный вход второго счетчика 9 и

обнуляющий вход первого счетчика 8. Под воздействием этого сигнала второй счетчик 9 изменяет свое состояние (увеличивает на единицу), а пер- вый счетчик 8 обнуляется. Параллельные коды с выходов первого регистра 4 (I.) и первого счетчика 8 (D) записываются по адресу, формируемому вторым счетчиком 9, в блок 12 памяти в момент поступления импульса записи с выхода блока 6 управления. Па этом обработка первого элемента отображения завершается.

Последующей код с выхода АЦП 1 через блок 3 элементов И записывается в первый регистр 4 и сравнивается в блоке 7 с предыду1цим кодом, переписанным во второй регистр 5. Если код послед тощего элемента отображения отличен от кода пре;№1дущего эле

51

мента отображения, цикл обработки аналогичен рассмотренному. Если же коды совпадают, то на выходе первого блока 7 сравнения устанавливается потенциал нуля, в результате чего второй счетчик 9 своего состояния не изменяет, а первый счетчик 8 увеличивает свое состояние на единицу под действием импульса с выхода блок 6 управления. Новая инструкция (с измененным) запишется в блок 12 памяти по старому адресу.

По данному алгоритму обрабатывают все элементы отображения кадра. После обработки последнего элемента кадра с выхода блока 6 управления на вход третьего регистра 10 поступает импульс записи, под воздействием которого код максимального адреса с выхода второго счетчика 9 записывается в третий регистр 10. С задержко (по отношению к сигналу с выхода блока 6 управления) с выхода блока 6 поступает обнуляющий сигнал на второ вход второго счетчика 9 и третий вхо первого регистра А. На второй вход блока 3 элементов И поступает сигнал запрета с выхода блока 6 управления на время считывания информации (инструкций (I; + D;) из блока 12 памяти. Сигналом разрешения считывания информации из блока 12 памяти является импульс, поступающий на вход блока 12 памяти и второй вход преобразователя 13 кода с выхода блока 6 управления. Этот сигнал разрешения считывания поступает только после обнуления второго счетчика 9. Так как второй счетчик 9 находится в нулевом состоянии,.то первый (п + р)-разряд- ный код считывается из ячейки памяти с нулевым адресом блока 12 и парал- |Лельно поступает на первый вход преобразователя 13 кода. Данная ячейка памяти используется для хранения синхрокода. С выхода блока 6 управления на вход преобразователя 13 кода поступают тактовые импульсы,обеспечивающие последовательный сдвиг информации на третьем входе преобразователя 13 в (п + р) раз больше частоты сигнала считывания, поступающего на тактовый вход блока 12 памяти и тактовый вход преобразователя 13 кода.

Первый блок 7 сравнения, сравнивая нулевую комбинацию, поступившую с выхода первого регистра 4 и отлич0

5

0

4006

ную от нулевой комбинации с выхода второго регистра 5, формирует на своем выходе единичные импульсы. Эти сигналы синхронны тактовым импульсам, поступающим с выхода блока 6 управления на тактовый вход первого блока 7 сравнения. Поступление единичных импульсов с выхода первого блока 7 сравнения на счетный вход второго счетчика 9 обеспечивает последовательный перебор ячеек памяти блока 12 памяти, информация из которых считывается в параллельном коде и поступает на преобразователь 13 кода. Процесс считывания информации с блока 12 памяти и запись ее в преобразователь 13 кода обеспечивается периодической выдачей сигнала разрешения считывания с выхода блока 6 управления .

Подачей тактовых импульсов с выхода блока 6 управления на вход преобразователя 13 кода обеспечивается последовательная передача информации в канал. Единичные импульсы с выхода первого блока 7 сравнения также подаются и на обнуляющий вход перво- го счетчика 8, не оказывая воздействия на процесс считывания. Коды адреса, формируемые на выходе второго счетчика 9, параллельно с поступлением на вход блока 12 памяти поступают на информационный вход третьего регистра 10 и вход второго блока 11 сравнения.

Из-за отсутствия сигнала разрешения записи на входе третьего регистра 10 поступающие коды адреса не изменяют хранящийся в нем код максимального адреса. Этот код поступает с выхода третьего регистра 10 на вход второго блока 11 сравнения. При поступлении тактовых импульсов с выхода блока 6 управления на вход второго блока 11 сравнения обеспечивается появление на выходе блока 11 сигнала результата сравнения. Сравнение кода максимального адреса происходит с кодом адреса ячейки памяти блока 12

5

0

5

0

5

0

5

памяти, информация из которой через преобразователь 13 кода уже поступила в канал. Это достигается тем, что тактовые импульсы с выхода блока 6 управления на вход второго блока 11 сравнения поступают тактовых импульсов с выхода блока 6 управления на тактовый вход первого блока 7 сравнения. Таким образом.

совпадение кода текущего адреса с кодом максимального адреса произойдет после считывания из блока 12 памяти последней инструкции данного кода. Результат совпадения кодов текущего и максимального адресов в виде единичного импульса с выхода второго блока 11 сравнения поступит на вход третьего регистра 10, обнулив его, и одновременно - на вход блока 6 управления. Этим будет прекращена выдача тактовых и управляющих импульсов на блоки устройства. Таким образом, устройство из режима считывания информации в канал переходит в режим ожидания поступления кадрового синхроимпульса следующего кадра.

Блок 6 управления работает следую щим образом.

В исходном состоянии первый 14 и второй 16 триггеры, первый 19, второй 25, третий 29 счетчики-делители, третий триггер 32 находятся в нулевом состоянии. В момент поступления на вход блока 6 управления импульса с выхода блока 2 установки опорного уровня первый триггер 14 переключается в единичное состояние. Сигнал высокого уровня с выхода первого триггера 14 поступает на первый вход первого элемента И 17. разрешая прохождение тактовых импульсов с генератора 15 тактовых импульсов на выход первого элемента И 17, откуда они поступают на вход первого счетчика-делителя 19. Последний при поступлении (п + р) импульсов формирует на своем выходе импульс, поступающий на вход третьего элемента И 20 и через первую линию 21 задержки - на выход блока 6 управления. Первая линия 21 задержки обеспечивает задержку, необходимую для завершения процесса записи кодов предьщу- щего и последующего элементов отображения во второй 5 и первый 4 регистры. Запись информации в первый регистр 4 происходит по получении сигнала с выхода третьего элемента И 20 через четвертую линию 24 задержки. Второй регистр 5 сигналы, управляющие записью, получает непосредственно с выхода третьего элемента И 20. В период обработки информации, поступающей на вход предлагаемого устройства, наличие сигналов на выходе третьего элемента И 20 обеспе10

15

20

25

30

35

40

45

50

55

чивается подачей на его вход единичного потенциала с выхода второго триггера 16. Этот же единичный потенциал поступает на выход блока 6 управления. Время задержки второй 22 и третьей 23 линий задержки больше времени задержки первой линии 21 задержки. Кроме того, время задержки линии 23 задержки больше времени второй линии 22 задержки. Второй счетчик-делитель 25, подключенный к выходу третьего элемента И 20, осуществляет деление входной последовательности импульсов на 2 , после чего формирует на своем выходе импульс. Этот импульс одновременно поступает на вход пятой линии 26 задержки, первый вход первого элемента ИЛИ 27, первый вход второго элемента ИЛИ 30 и на первый вход второго триггера 16 и является сигналом окончания цикла обработки кадра изображения. Под воздействием этого импульса второй триггер 16 переключается в единичное состояние. Нулевой потенциал с второго выхода второго триггера 16 поступает на выход блока 6 управления и на вход третьего элемента И 20, запрещая выдачу тактовых импульсов с выходов блока 6 управления. Первый элемент ИЛИ 27, пропуская импульс с выхода второго счетчика-делителя 25 на выход блока 6 управления с задержкой, определяемой линией 28 задержки, обеспечивает обнуление соответствующих блоков по завершении цикла обработки кадра. Единичный потенциал с первого выхода второго триггера 16 разрешают выдачу тактовых импульсов с вькода второго элемента И 18. Эти импульсы поступают на выход блока 6 управления и на вход третьего счетчика-делителя 29. При поступлении (п+р) тактовых импульсов третий счетчик- делитель 29 на своем выходе формирует импульс, поступающий на второй вход второго элемента ИЛИ 30 и на выход блока 6 управления. Единичный импульс, поступивший на первый вход второго элемента ИЛИ 30, с его выхода поступит на первый вход третьего триггера 32 и через седьмую линию 31 задержки - на второй вход того же триггера. Третий триггер 32 формирует на выходе блока 6 управления управляющий импульс. Этот импульс обеспечивает считывание в канал синх15

рокода. В дальнейшем единичные импульсы поступают на второй вход второго элемента ИЛИ 30, обеспечивая работу третьего триггера 32 по формированию управляющих импульсов на выходе блока 6 управления. По завершении цикла считывания информации единичный импульс, поступивший на вход блока 6 управления, установит первый 14 и второй 16 триггеры в нулевое состояние. Кроме того, этот единичный импульс поступит на второй вход первого элемента ИЛИ 27, обеспечивая формирование на выходе блока 6 управле1п- Я импульса обнуления. В дальнейшем работа элементов блока 6 управления повторяется по описанному алгоритму.

Формула изобретения

АОО °

девятый вьгход блока управ:тения и первый сигнальный вход первого блока сравнения, первый сигнальный вход блока памяти и выход первого регистра, первый и второй счетчики и третий регистр, к входу запуска, входу обнуления и информационному входу которого подключены соответстненно

Q десятьи1 выход блока управления, выход второго блока сравнения и первый вход второго блока сравнения, адресный вход блока памяти и выход второго счетчика, к счетному и обнуляюще5 му входам которого подключены соответственно обнуляющий вход первого счетчика и выход первого блока сравнения н второй выход блока управления, одиннадцатый выход 1-:оторого сос

0 динен со счетным входом первого счетчика, выход которого соединен с вторым он. нальным входом блока памяти, при этом выход третьего регистра соединен с вторым входом второг о

5 блока сравнения, к второму входу блока управления подключен выход блока установки опорного уровня, выход второго регистра соединен с вторым сигнальным входом первого блока сравие0 ия.

5

5

11151

ся вторым выходом блока управления, второй выход второго триггера соединен с вторым -входом третьего элемента И и является первым выходом блока управления, выход второго элемента И является шестым выходом блока управления и соединен с входом третьего счетчика-делителя, выход которого является третьим выходом блока управления и соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом третьего триггера непосредственно и с вторым входом - через седьмую линию задержки, а выход третьего триггера являет012

ся пятым выходом блока управления, выход третьего элемента И является девятым выходом блока управления и соединен с входами первой, второй, третьей и четвертой линий задержки и второго счетчика-делителя, выход первого элемента ИЛИ соединен с входом шестой линии задержки, выход которой является восьмым выходом блока управления, а выходы второй, третьей и четвертой линий задержки являются соответственно одиннадцатым, четвертым и седьмым выходами блока управления.

г

| Устройство для сжатия цифровых телевизионных сигналов | 1982 |

|

SU1136325A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-10-15—Публикация

1987-08-04—Подача