1

(21)4658190/24

(22)02.03.89

(46) 07.03.91. Икш. М 9

(71)Белорусский государственный университет им. В.И.Ленина

(72)Л.В.Соболев, И.П.Оецко, Г.Н.Черников и В.А.Чудовгкий

(53)681.325(088.8)

(56) Авторское свидетельство (ССР № 1132284, кл. С, 06 F 7/()(), 1983.

Авторское свидетельство СССР № 1280606, кл. С, 06 F 7/00, 1986.

(54)УСТРОЙСТВО АНАЛИЗА И ЧАЛОЙ ЧИСЛОВЫХ ПОЛЕЙ

(57) Устройство анализа и замены числовых попей относится к цифровой вычислительной технике и может быть использовано при обработке структурно-сложной информации (графов, таб- лин), анапизе алгоритмов, программ. Цель изобретения - ускорение выполнения операции анализа и замены числовых полей. Устройство содержит входные регистры 1, 2, блок J формирования масок, регистры 4, 5 маски, группы элементов И 6, 7, блок 8 коррекции, группу -элементов ИЛИ 9, группу элементов И 10. Два элемента данных, которые необходимо проанализировать,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство анализа и перестановки числовых полей | 1985 |

|

SU1317429A1 |

| Устройство анализа и замены числовых полей | 1985 |

|

SU1280606A1 |

| Устройство анализа и замены числовых полей | 1985 |

|

SU1312562A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

аъ со со со

00

со

поступают на входные регистры н с них - на входы блока формирования масок и входы групп элементов И. С помощью блока формирования масок знали- зируется возможность замены числовых полей н формируются маски, поступающие на регистры масок и с выходов последних - на входы первой и второй групп элементов И. С выходов групп элементов И выделенные поля первого

Изобретение относится к цифровой вычислительной технике и может быть использовано при обработке структурно-сложной информации (графов, таблиц), анализе алгоритмов, программ.

Цель изобретения - ускорение выполнения операций анализа и замены числовых полей.

На фиг.1 изображена функциональная схема устройства анализа и замены

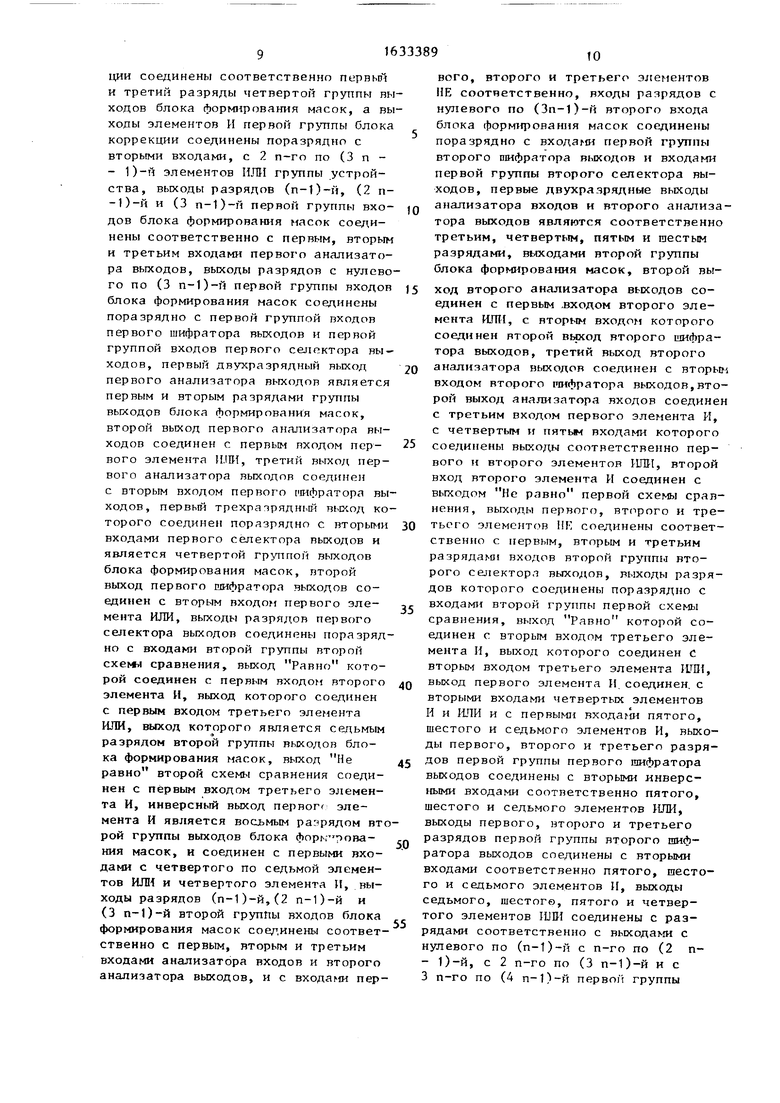

числовых попей; на фиг. 7. - функциональная схема, блока коррекции; на фиг.3 - функциональная схема блока формирования масок; на фиг.4 - функциональная схема схемы предваритель- ного анализа блока формирования масок на фиг.5 - функциональная схема анализатора выходов; на фиг.6 - функциональная схема анализатора входов; на фиг.7 - функциональная схема шифрато- ра выходов; на фиг.8 - функциональная схема сепектора выходов.

Устройство анализа и замены числовых полей содержит входные регистры 1 и 2, бпок 3 формирования масок, ре- гистр 4 маски, регистр 5 маски, группу 6 элементов И, группу 7 элементов И, блок 8 коррекции, группу 9 элементов ИЛИ, группу 10 элементов И.

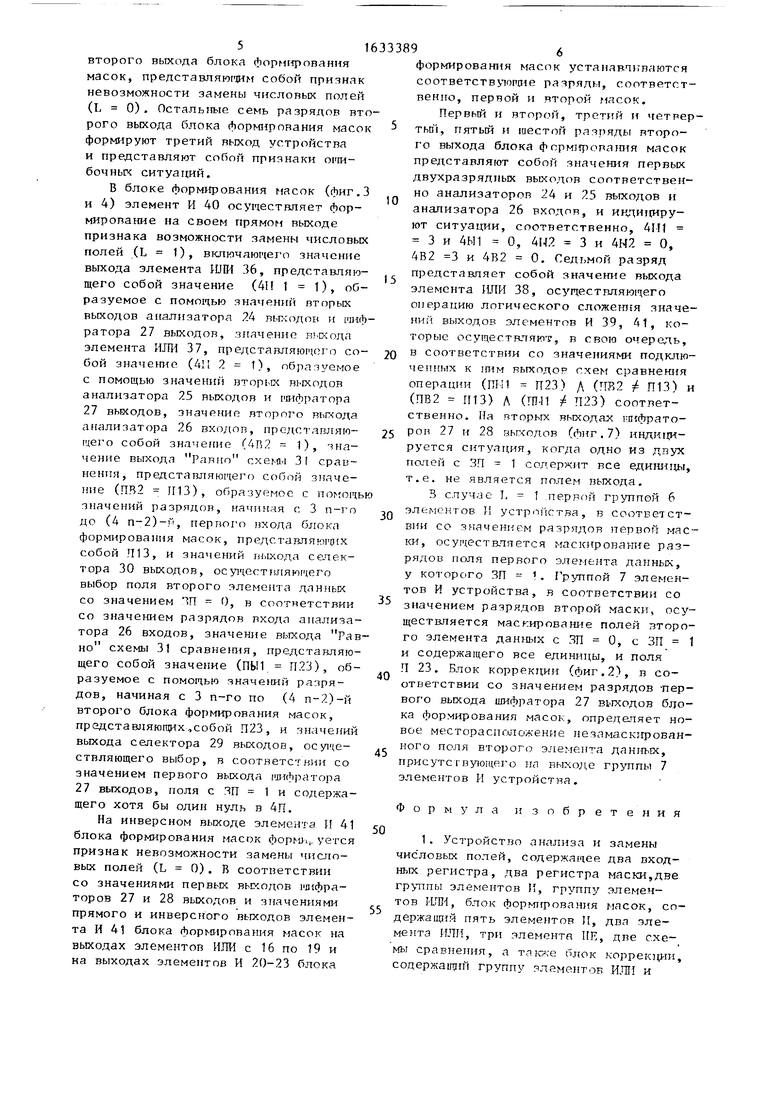

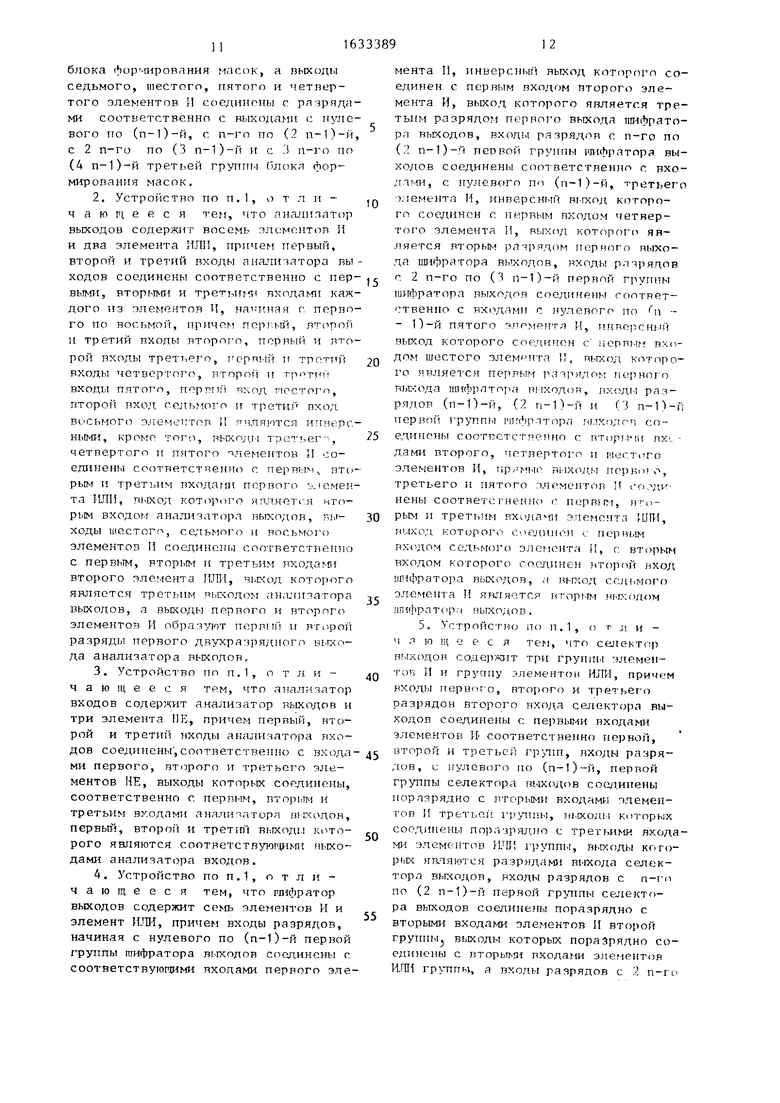

Функциональная схема блока коррек- нии (фиг.2) состоит из группы 11 элементов ИЛИ, групп 12-14 элементов И.

I

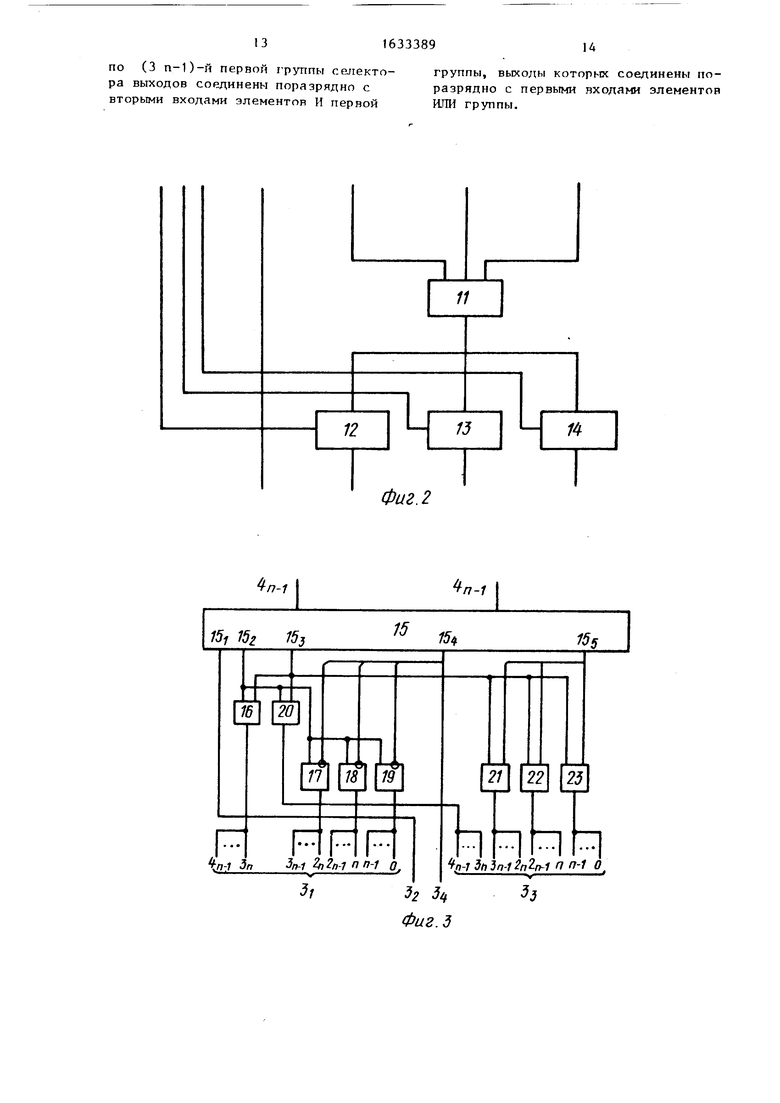

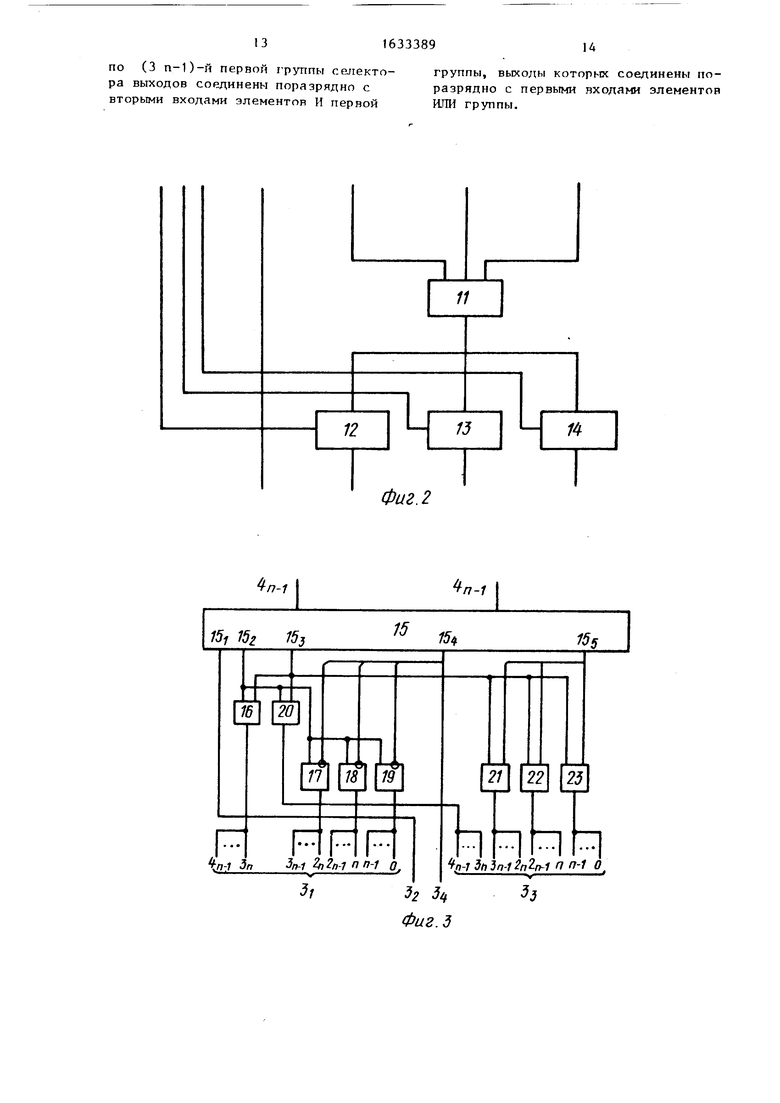

Функциональная схема блока формирования масок (фиг.З) включает схему 15 предварительного анализа, элементы ИЛИ 16-19, элементы И 20-23.

Функциональная схема схемы предварительного анализа блока формирования масок (фиг.4) включает анализаторы 24 и 25 выходов, анализатор 26 входов, шифраторы 27 и 28 выходов,селекторы 29 и 30 выходов, схемы 31 и 32

элемента данных непосредственно, л второго элемента данных - через блок коррекции подаются на пходы группы элементов ШШ, где объединимте я и поступают на первый выход устройства, на второй выход которого поступает с выхода третьей группы элементов И, в случае невозможности замены числовых полей, второй элемент данных. 4 э.п. ф-лы, 8 ил.

сравнения, элементы НЕ 33-35, элементы ИЛИ 36-38, элементы И 39-41.

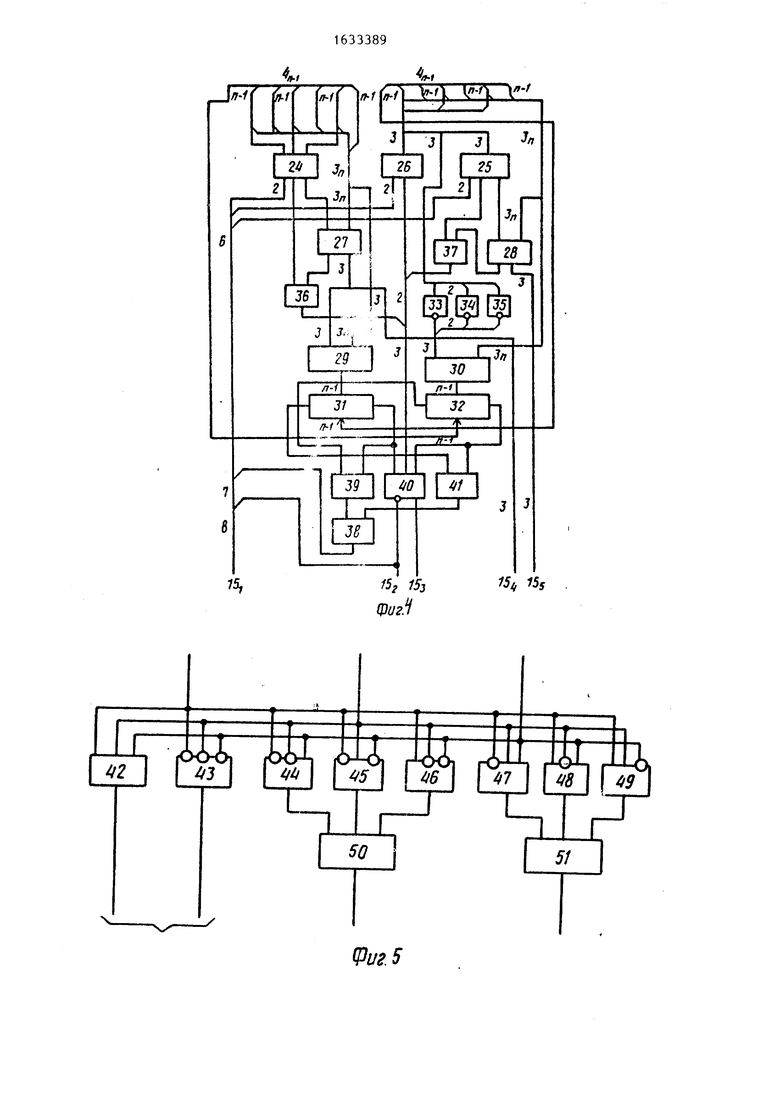

Функциональная схема анализатора выходов (фиг.5) состоит из элементов И 42-49, элементов ИЛИ 50 и 51.

Функциональная схема анализатора входов (фиг.6) состоит из элементов НЕ 52-54 и анализатора 55 выходов.

Функциональная схема шфратора выходов (фиг.7) состоит из элементов И 56-62 и элемента ШШ 63.

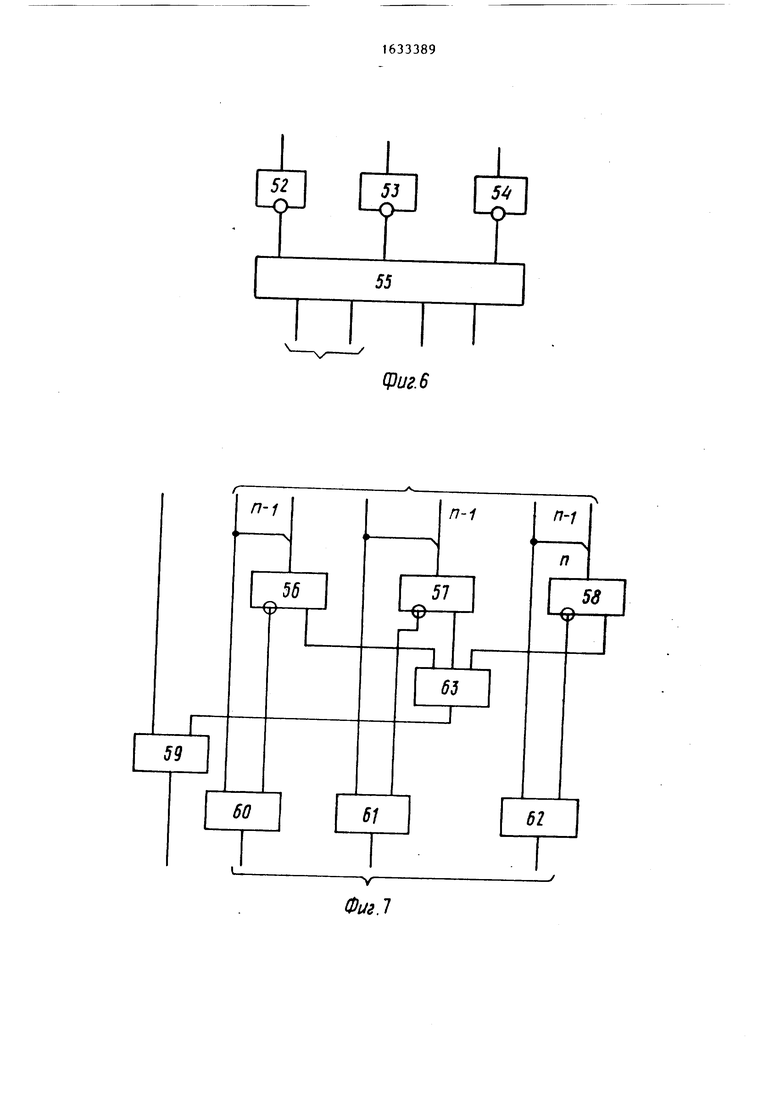

Функциональная схема селектора выходов (фиг.8) состоит HI 66 групп элементов И 64-66 и группы 67 элементов ИЛИ.

Устройство функционирует следукнчи образом.

В первый входной регистр 1 заносится первый элемент данных, во второй входной регистр 2 заносится второй элемент данных. С выходов первого 1 и второго 2 входных регистров первый и второй элементы данных поступают на группы 6 н 7 элементов И, осуществлявших операцию поразрядного И элементов данных и соответствующих масок, поступаюр(их с выходов регистров 4 и 5 масок, на входы которых маски поступают соответственно с первого и третьего выходов блока 3 формирования масок. На первый и второй входы блока 3 формирования масок поступают разряды соответствующих элементов данных. Г, помощью группы 9 элементов ИЛИ производится логическое сложение кодов с. выходов группы 6 элементов И и выхода блока 8 коррекции. Результат поступает нл первый выход устройства, второй выхп которого представляет собой выход группы 10 элементов И, пропускаюгчих второй элемент данных в соответствии со значением восьмого разряд,ч

второго выхода блока формирования масок, представляющим собой признак невозможности замены числовых полей (L 0). Остальные семь разрядов второго выхода блока Формирования масок формируют третий выход устройства и представляют собой признаки ощи- бочных ситуаций.

В блоке формирования масок (фиг.3 и 4) элемент И 40 осуществляет формирование на своем прямом выходе признака возможности замены числовых полей (L 1), включающего значение выхода элемента ШШ 36, представляющего собой значение (4П 1 1), образуемое с помощью значений вторых выходов анализатора 24 выводов и шифратора 27 выходов, значение выхода элемента ИЛИ 37, представляющего собой значение (411 2 1), образуемое с помощью значений вторых выходов анализатора 25 выходов и шифратора 27 выходов, значение второго выхода анализатора 26 входов, представляющего собой значение (4П2 1), значение выхода Равно схемы 31 сравнения, представляющего собой значение (ПВ2 П13), образуемое с помощь значений разрядов, начиная с 3 п-го до (4 n-2), первого входа блока формирования масок, предетавлячг(их собой 413, и значений выхода селектора 30 выходов, осущегтвляюгцего выбор поля второго элемента данных со значением Ш 0, в соответствии со значением разрядов входа анализатора 26 входов, значение выхода Равно схемы 31 сравнения, представляющего собой значение (ПЫ1 П23), образуемое с помощью значений разрядов, начиная с 3 n-го по (4 п-2)-й второго блока формирования масок, представляющих,собой П23, и значений выхода селектора 29 выходов, осуществляющего выбор, в соответствии со значением первого выхода шифратора 27 выходов, поля с Ш 1 и содержащего хотя бы один нуль в 4П.

На инверсном выходе элемента И 41 блока формирования масок уется признак невозможности замены числовых полей (L 0). В соответствии со значениями первых выходов шифраторов 27 и 28 выходов и значениями прямого и инверсного выходов элемента И 41 блока формирования масок на выходах элементов ИЛИ с 16 по 19 и на выходах элементов И 20-23 блока

10

15

20

333896

формирования масок устанавливаются соответствующие разряды, соответственно, первой и чторой масок.

Первый и второй, третий и четвертый, пятый и шестой разряды второго выхода блока форм форания масок представляют собой значения первых двухразрядных выходов соответственно анализаторов 24 и 25 выходов и анализатора 26 входов, и индицируют ситуации, соответственно, 4П1 3 и 4Ы1 О, 4Ы2 3 и 4Н2 О, 4В2 3 и 4В2 0. Седьмой разряд представляет собой значение выхода элемента ИЛИ 38, осуществляющего операцию логического сложения значении выходов элементов И 39, 41, которые осуществляют, в свою очередь, в соответствии со значениями подключенных к ним выходов схем сравнения операции (ГТН1 IT23) Д (ТВ2 П13) и (ПВ2 П13) Л (ТП-11 t П23) соответственно. На вторых выходах ггнфрато- ров 27 и 28 выходов (Лиг.7) индицируется ситуация, когда одно из дпух полей с ЗП 1 содержит все единицы, т.е. не является полем выхода.

В спучас L - 1 перяон группой 6 элементов И устройства, в соответствии со значением разрядов первой маски, осуществляется маскирование разрядов поля первого элемента данных, у которого ЗП . Группой 7 элементов И устройства, в соответствии со значением разрядов второй маски, осуществляется маскирование полей второго элемента данных с ЗП 0, с ЗП 1 и содержащего все единицы, и поля Л 23. Блок коррекции (фиг.2), в соответствии со значением разрядов -первого выхода шифратора 27 выходов блока формирования масок, определяет новое месторасположение незамасктгрован- ного поля второго элемента данных, присутствующего па выходе группы 7 элементов И устройстпа.

25

30

35

40

45

Формула изобретения

две группы элементов И, причем входы первого и второго входных регистров являются соответственно входами первого и второго элементов данных уст- ройства, выходы первого и второго входных регистров подключены поразрядно к первым входам элементов И соответственно первой и второй групп, к вторым входам которых подключены поразрядно выходы соответственно первого и второго регистров маски, выходы разрядов с нулевого по (2 п-1)и с (3 п-1)-го по (4 п-2)-й выходов, где п - количество разрядов элемен- тов данных, деленное на 4, первого входного регистра соединены с входами соответствующих разрядов первой группы входов блока формирования масок, а входы разрядов с нулевого по (п-1)-й, с (2 п-1)-го по (3 п-2)-й и с 3 n-го по (4 п-2)-й выходов второго входного регистра соединены поразрядно с входами соответствуюгхих

разрядов второй группы входов блока

формирования масок, входы первого и второго pernqTpoB масок поразрядно соединены соответственно с выходами первой и третьей групп блока формирования масок, выходы элементов И группы подключены поразрядно к первым входам элементов ИЛИ группы, к вторым входам которых поразрядно подключены выходы блока коррекции, к входам второй группы которого поразрядно под- ключены выходы элементов И второй группы, а первые входы элементов И второй группы блока коррекции соединены с вторым разрядом четвертого выхода блока формирования масок, вы- ходы элементов ИЛИ группы устройства являются выходами результатов устройства, причем в блоке формирования масок входы первой группы второй схемы сравнения соединены поразрядно с вы- ходами разрядов с 3 n-го по (4 п-2)-й второго входного регистра, а выходы разрядов с 3 n-го по (4 п-2)-й первого входного регистра соединены поразрядно с входами первой группы первой схемы сравнения, выходы Равно первой и второй схем сравнения соединены соотвтственно с первым и вторым входами первого элемента И блока формирования масок, выходы разрядов с ну- левого по (п-1)-й элементов И второй группы устройства соединены поразрядно с первыми входами элементов ИЛИ группы блока коррекции, выходы

5 0

5

0 j 0 5 Q .,

разрядов с n-го по (2 п-1)-н элементов И второй группы устройства соединены поразрядно с вторыми входами элементов ИЛИ группы блока коррекции, разряды с Зп-го по (4 п-1)-й выходов элементов И второй группы устройства соединены с вторыми входами соответствуюгц х элементов ИЛИ группы устройства, выходы элементов ИЛИ группы блока коррекции соединены поразрядно с вторыми входами элементов И третьей и второй групп блока коррекции, выходы разрядов соответственно с нулевого по (п-1)-н и г. n-го по (2 п-1)-й которых соединены с вторыми входами соответствующих элементов ИЛИ группы устройства, отличающееся тем, что, с целью увеличения быстродействия выполнения операций анализа и замены числовых полей, в него введена третья группа элементов И, блок формирования масок дополнительно содержит два анализатора выходов, анализатор входов, два шифратора выходов, два селектора выходов, пять элементов ИЛИ, два элемента И, причем чы- ходы разрядов г. 2 n-го по (1 п-2)-й первого входного регистра соединены поразрядно с соответствующими разрядами первой группы входов блока формирования масок, а выходы разрядов с n-го по (2 )-н и разряд (3 п-1)-и второго входного регистра соединены поразрядно с соответствующими разрядами второй группы входов блока формирования масок, выходы второго входного регистра соединены поразрядно с первыми входами элементов И третьей группы устройства, с вторыми входами которых соединен восьмой разряд второго выхода блока формирования масок, выходы элементов II третьей группы являются выходами второго элемента данных устройства, выходами признака оииГючные ситуации устройства являются чыходы разрядов с первого по седьмой второй группы блока Формирования масок, выходы с 2 n-го по (3 п-1)-ч элементов И второй группы устройства соединены поразрядно с третьими входами элементов ИЛИ группы блока коррекции, выходы которых соединены поразрядно дополнительно с вторыми входами элементов И первой группы блока коррекции, с первыми входами элементов 1 первой и третьей групп блока коррекцин соединены соответственно первый и третий разряды четвертой группы выходов блока формирования масок, а выходы элементов И первой группы блока коррекции соединены поразрядно с вторыми входами, с 2 n-го по (3 п - - 1)-й элементов ИЛИ группы устройства, выходы разрядов (п-1)-й, (2 п- -1)-й и (3 п-1)-н первой группы входов блока формирования масок соединены соответственно с первым, вторым и третьим входами первого анализатора выходов, выходы разрядов с нулевого по (3 п-1)-н первой группы входов блока формирования масок соединены поразрядно с первой группой входов первого шифратора выходов и первой группой входов первого селектора выходов, первый двухразрядный выход первого анализатора выходов является первым и вторым разрядами группы выходов блока формирования масок, второй выход первого анализатора выходов соединен с первым входом первого элемента ИЛИ, третий выход первого анализатора выходов соединен с вторым входом первого шифратора выходов, первый трехратрядный выход которого соединен поразрядно с вторыми входами первого селектора выходов и является четвертой группой выходов блока формирования масок, второй выход первого шифратора выходов соединен с вторым входом первого элемента ИЛИ, выходы разрядов первого селектора выходов соединены поразрядно с входами второй группы второй схемя сравнения, выход Равно которой соединен с первым входом второго элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого является седьмым разрядом второй группы выходов блока формирования масок, выход Не равно второй схемы сравнения соединен с первым входом третьего элемента И, инверсный выход первое элемента И является восьмым разрядом второй группы выходов блока ния масок, и соединен с первыми входами с четвертого по седьмой элементов ИЛИ и четвертого элемента И, выходы разрядов (п-1)-й,(2 п-1)-й и (3 п-1)-й второй группы входов блока формирования масок соединены соответственно с первым, вторым и третьим входами анализатора входов и второго анализатора выходов, и с входами пер10

15

20

5

0

5

0

5

.0

5

вого, второго и третьего элементов НЕ соответственно, входы разрядов с нулевого по (Зп-1)-н второго входа блока формирования масок соединены поразрядно с входами первой группы второго шифратора выходов и входами первой группы второго селектора выходов, первые двухразрядные выходы анализатора входов и второго анализатора выходов являются соответственно третьим, четвертым, пятым и шестым разрядами, выходами второй группы блока формирования масок, второй выход второго анализатора выходов соединен с первым .входом второго элемента ИЛИ, с вторым входом которого соединен второй выход второго шифратора выходов, третий выход второго анализатора выходов соединен с вторым входом второго шифратора выходов,второй выход анализатора входов соединен с третьим входом первого элемента И, с четвертым и пятым входами которого соединены выходы соответственно первого и второго элементов ИЛИ, второй вход второго элемента И соединен с выходом Не равно первой схемы сравнения, выходы первого, второго и третьего элементов НЕ соединены соответственно с первым, вторым и третьим разрядам входов второй группы второго селекторл выходов, выходы разрядов которого соединены поразрядно с входами второй группы первой схемы сравнения, выход Равно которой соединен г вторым входом третьего элемента И, выход которого соединен С вторым входом третьего элемента ИЛИ, выход первого элемента И соединен, с вторыми входами четвертых элементов И и ИЛИ и с первыми входагш пятого, шестого и седьмого элементов И, выходы первого, второго и третьего разрядов первой группы первого шифратора выходов соединены с вторыми инверсными входами соответственно пятого, шестого и седьмого элементов ИЛИ, выходы первого, второго и третьего разрядов первой группы второго шифратора выходов соединены с вторыми входами соответственно пятого, шестого и седьмого элементов И, выходы седьмого, шестого, пятого и четвертого элементов ИЛИ соединены с разрядами соответственно с выходами с нулевого по (п-1)-й с n-го по (2 п- - 1)-й, с 2 n-го по (3 п-1)-й и с 3 n-го по (4 п-1)-й первой группы

блока фор -шрования масок, а выходы седьмого, шестого, пятого и четвертого элементов И соединимы г раэряда- ми соответственно с выходами с нулевого по (п-1)-й, с n-го по (2 п-1)-й, с 2 n-го по (3 п-1)-й и с n-го по (4 п-1)-й третьей группы блока формирования масок.

0

0 5

45

0

5

0

50

5

мента II, инверсный выход которого соединен с первым входом второго элемента И, выход которого является третьим разрядом первого выходя шифратора выходов, входы разрядов с n-го по (2 п-1)-ч пеовой группы шифратора выходов соединены соответственно с вхо- ;п.ми, с нулевого по (п-1)-й, третьего элемента И, инверсный выход которого соединен с первым входом четвертого элемента И, выход которого является вторым разрядом первого выхода шифратора выходов, входы разрядов г 2 n-го по (3 п-1)-й первой группы шифратора выходов соединены соответственно с входами с нулевого по I ll - - 1)-й пятого ЧПРМРТГГЯ И, инверсный выход которого соединен с первым входом шестого элемента И, выход которого является первым разрядом первого выходя 1шфрлтора выходов, входы разрядов (п-1)-й, (2 п-1)-й и (3 п-О-Г; первой группы ниЛртторл внхчдг-п соединены СООТГ, С ПТОрЫМН ПХ

дами второго, четвертого п ме.гтого элементов И, прямые выходы пгпвп о, третьего н пятого элементов И соw йены соотвеч ствепно г- первым, рым и третьим входами эчемента ИЛИ, выход которого соединен первым входом седьмого элемента Н, с вторым входом которого соединен второй вход шифратора вькодов, .( выход седьмого элемента И является вторым выходом пшфратор 1 выходов.

по (3 п-1)-н первой группы селектора выходов соединены поразрядно с вторыми входами элементов И первой

п

группы, выходы которых соединены поразрядно с первыми входами элементов ИЛИ группы.

L

13

п

Фиг. 2

V/

«м

Я, 153 Фиг.Ч

1St 155

Фиг. 5

52

Фиг.1

54

Фиг. 6

Фиг 8

Авторы

Даты

1991-03-07—Публикация

1989-03-02—Подача