. чены соответственно к третьим входа К-1-го и К-го элементов ИЛИ группы. Где К - количество элейентов ИЛИ в группе, входы с первого по четвертьй второго и третьего элемен тов ИЛИ селектора операций подключены соответственно к выходам операций умножения, деления, сдвига на один разряд, сдвига на два разряда, сложения, вычитания, отрицания, передачи дешифратора, входы четвертого элемента ИЛИ селектора операций подключены соответственно к вы содам операций конъюнкции,дизъюнкци Ti сложения по модулю два дешифратор отличающийся тем, что, с целью повьшения быстродействия, о содержит дешифратор первого операнд дешифратор второго операнда, третий дешифратор, сдвигатель, блок коммутации, шифратор, вторую группу элементов ИЛИ, группу элементов НЕ и четьфе группы эйементов И, а селектор операций дополнительно содержит пятый и шестой элементы ИЛИ, причем первьй и втсгрой входы пятого и шестого элементов ИЛИ селектора операций подключены соответственно к выходам операций конъюнкции, пере дачи, отрицания и сложения по модулю два дешифратора, выход регистра первого операнда подключен к входу дешифратора первого операнда, выход мультиплексора подключен к вход дешифратора второго операнда, первый и второй выходы шифратора по ключены соответственно к первому и второму информационным входам ком мутатора результата, кроме того, первые и вторые входы i -го элемента И первой группы подключены (Соответственно к -м выходам регистра первого операнда и мультиплексора ( 1 ТТМ ), где М разрядность микропроцессора, и соединены соответственно с первым и вторым входами и -го элемента ИЛИ второй группы, выход которого п ключен к первому входу i -го элемента И второй группы и соединен с первым входом i -го элемента И тре тьей группы, выход -го элемента И первой группы .подключен к входу i -го элемента НЕ группы и соеди нен с первым входом i -го элемента И четвертой группы, второй вход i-го элемента И третьей группы сое динен с выходом 4 -го элемента НЕ, 19 выходы элементов И групп с второй по четвертую подключены соответственно к информационным входам коммута.тора результата с третьего по пятый, выходы пятого и шестого элементов ИЛИ селектора операций и выход операции дизъюнкции дешифратора подключены соответственно к вторым входам элементов И четвертой группы,третьим входам элементов И третьей группы и вторым входам элементов И второй группы, выход дешифратора первого операнда подключен к информационному входу сдвигателя, управлякиций вход которого подключен к входу переноса микропроцессора, первый и второй выходы сдвигателя подключены соответственно к первому и второму информационным входам блока коммутации, третий информационный вход которого подключен к выходу дешифратора второго операнда, первьй и второй выходы блока коммутации подключены соответственно к первому входу шифратора и входу третьего дешифратора, выход которого подключен к второму входу шифратора, информационные входы коммутатора с первого по четвертьй подключены соответственно к входу переноса микропроцессора, выходу регистра первого операнда, вькоду дешифратора первого операнда, выходу мультиплексора, информационный выход и выход окончания операции коммутатора подключены соответственно к второму входу формирователя сигнала конца операции и к шестому информационному входу коммутатора реэультата, выходы операций умножения и . сложения дешифратора подключены к управляющему входу коммутатора. 2. Микропроцессор по п.1, о тличающийся тем, что блок коммутации содержит две группы эле- ментов ИЛИ и группу элементов И, причем выходы элементов И группы под- ключёны к первому выходу блока, выходы элементов ИЛИ первой группы блока подключены к второму выходу блока, выход i .-го элемента ИЛИ второй группы блока подключен к первому входу i -го элемента И группы (, 2 -1), второй вход которого соединен с первым входом -го элемента ИЛИ первой группы блока, второй и третий входы i -го элемента ИЛИ первой группы блока соединены соответственно с первым и вторым

входами i -го элемента ИЛИ второй|Входов блока, второй вход i -го

группы блока и подключены соответ-элемента И группы соединен с. входом

ственно к входам i -го разряда пер-4-го разряда третьего информационнового и второго информационныхго входа блока.

1141419

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1977 |

|

SU717772A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Вычислительное устройство | 1980 |

|

SU1008731A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Процессор | 1977 |

|

SU691858A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ | 1999 |

|

RU2157560C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

1. МИКРОПРОЦЕССОР, содержащий регистр первого операнда, регист р второго операнда, мультиплексор, группу элементов ИЛИ, коммутатор результата, первьй блок памяти, второй блок памяти, селектор операций, демультиплексор, регистр результата, формирователь сигнала конца операции, причем первый и второй информационные входы микропроцессора соединены соответственно с информационными входами регистров первого и второго операндов, входы записи которых соединены с первым управляющим входом микропроцессора, выход регистра второго операнда, выходы элементов ИЛИ группы, выход первого блока памяти подключены соответственно к информационным входам мультиплексора с первого по третий, адресный вход микропроцессора подключен к адресному входу второго блока памяти, выход коммутатора результата подключен к информационному входу демультиплексора, первьй и второй выходы которого подключены соответственно к информационному входу регистра результата и к информационному входу первого блока памяти, первьй и второй выходы регистра результата подключены соответственно к выходу конца операции и информационному выходу микропроцессора, выход формирователя сигнала конца операции подключен к управляющему входу регистра результата, причем селектор операций содержит регистр команд, дешифратор, четыре элемента ИЛИ, причем вход регистра команд соединен с выходом второго блока памяти, первьй выход:регистра команд соединен с входом дешифратора, первьй выход которого и выход -{ :первого элемента ИЛИ селектора опера(Л ций подключены соответственно к первому и второму управляющим входам коммутатора результата, входы первого элемента ИЛИ селектора onejpaций подключены соответственно к выходам операций умножения, сдвига на один и на два разряда дешифратора, второй выход регистра команд, . выходы элементов ИЛИ селектора операций с второго по четвертый со подключены к первым входам формирователя сигнала конца операции, третий и четвертый выходы регистра команд подключены соответственно к управляющим входам мультиплексора и демультиплексора, пятый выход регистра команд подключен к адресному входу первого блока памяти, выход операции отрицания дешифратора подключен к первым входам элементов ИЛИ группы, вторые входы которых подключены к выходу операции передачи дешифратора, выходы операций сдвига на один разряд и сдвига на два разряда дешифратора подклю

Изобретение относится к вычислительной технике и цифровой автомати и может быть использовано в электро .ных и вычислительных машинах и вычислительных устройствах цифровой автоматики для обработки данных.

Известен микропроцессор, содержащий регистры первого и второго операнда, мультиплексор, демультиплексор, блок памяти микропроцессора, управлякнцую память, регистр результата, которьй обеспечивает выполнение алгебраического сложения и логических операций при помощи аппаратурных средств, а умножение и деление операндов программным и микропрограммным способами ij.

Недостатками такого процессора являются низкое быстродействие, большой объем управляющей памяти, сложная схема управления операциями особенно длинными, типа умножения.

Наиболее близким к предлагаемому устройству по технической сущности является микропроцессор, содержащий регистр первого операнда, регистр второго операнда, мультиплексор, демультиплексор, блок памяти микропроцессора, управляющую память, регистр результата, блок формирования псевдооперандов, матрицу узлов поразрядной обработки операндов, матрицу одноразрядных двоичных сумматоров, коммутатор результата, селектор арифметико-логических one-. раций, формирователь длительности операций, которьй обеспечивает алгебраическое сложение, логическую .обработку операндов, умножение и деление при помощи аппаратурных средств 2.

Недостатком микропроцессора является невысокое быстродействие, обусловленное матричным алгоритмом умножения и его зависимость от разрядности операндов.

Цель изобретения - повышение быстродействия микропроцессора.

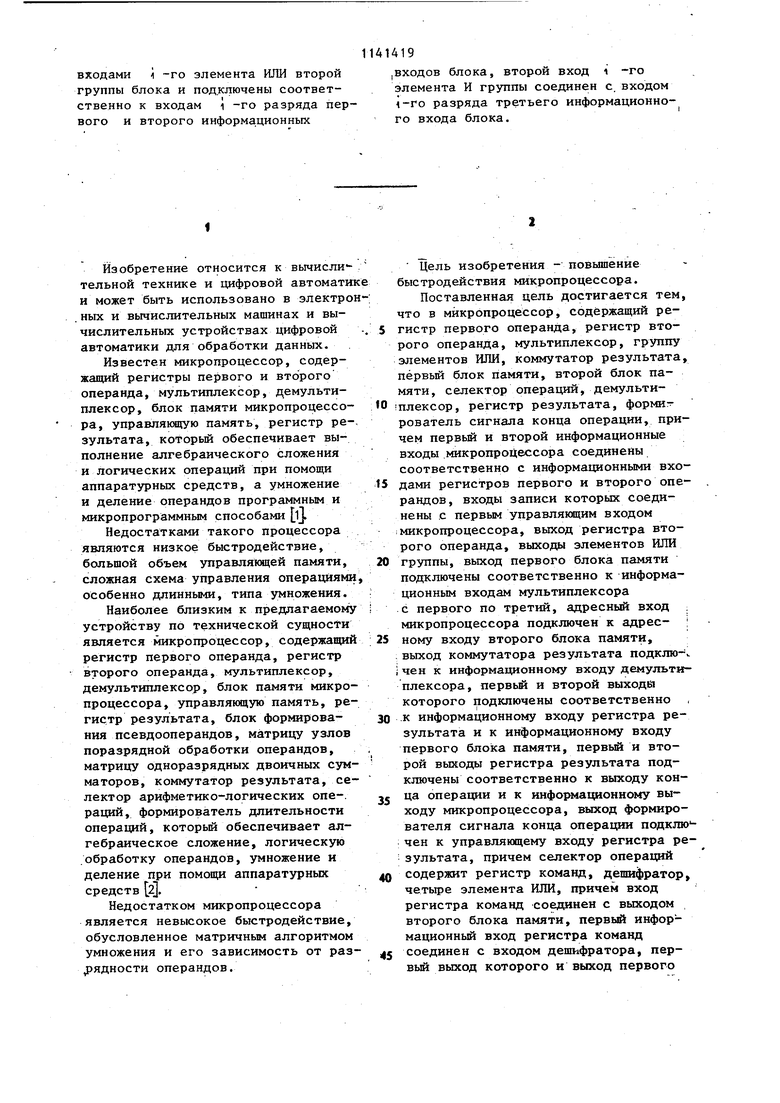

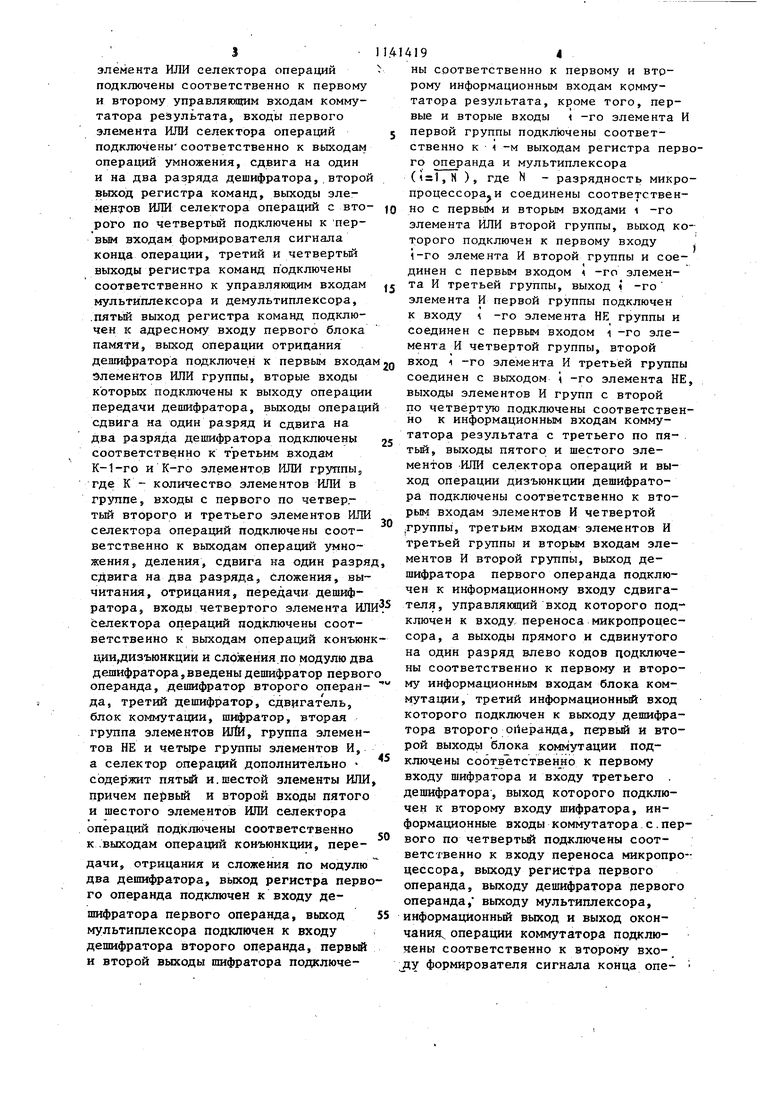

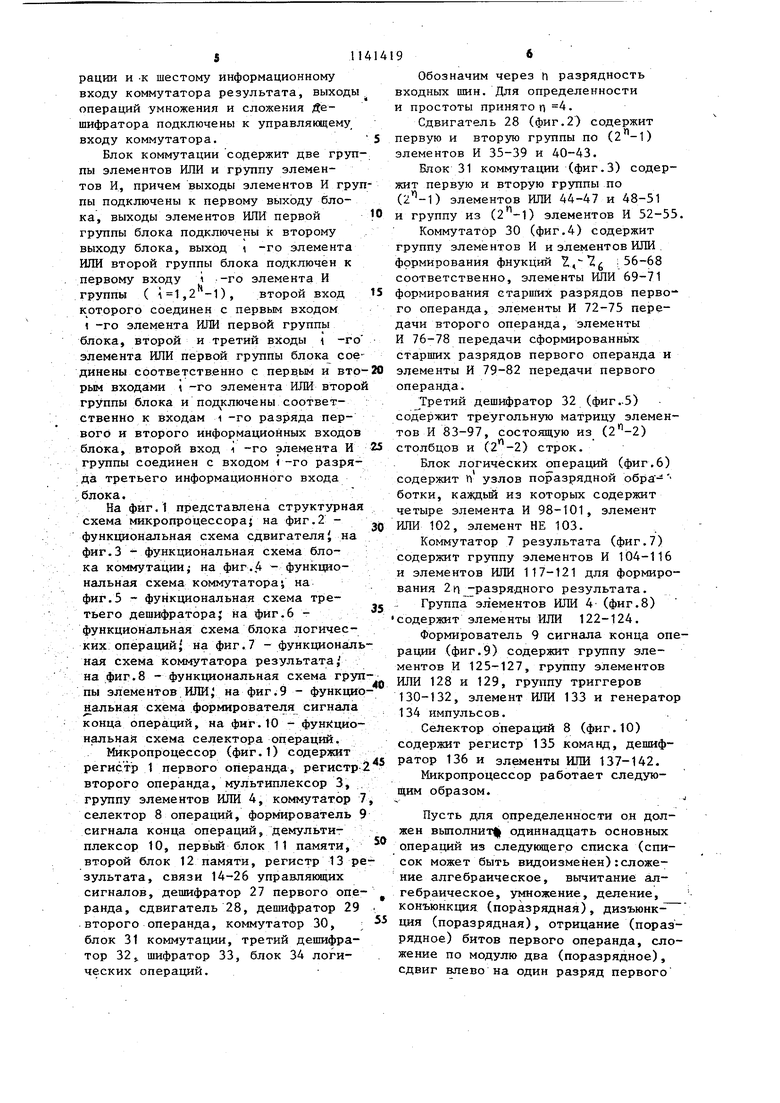

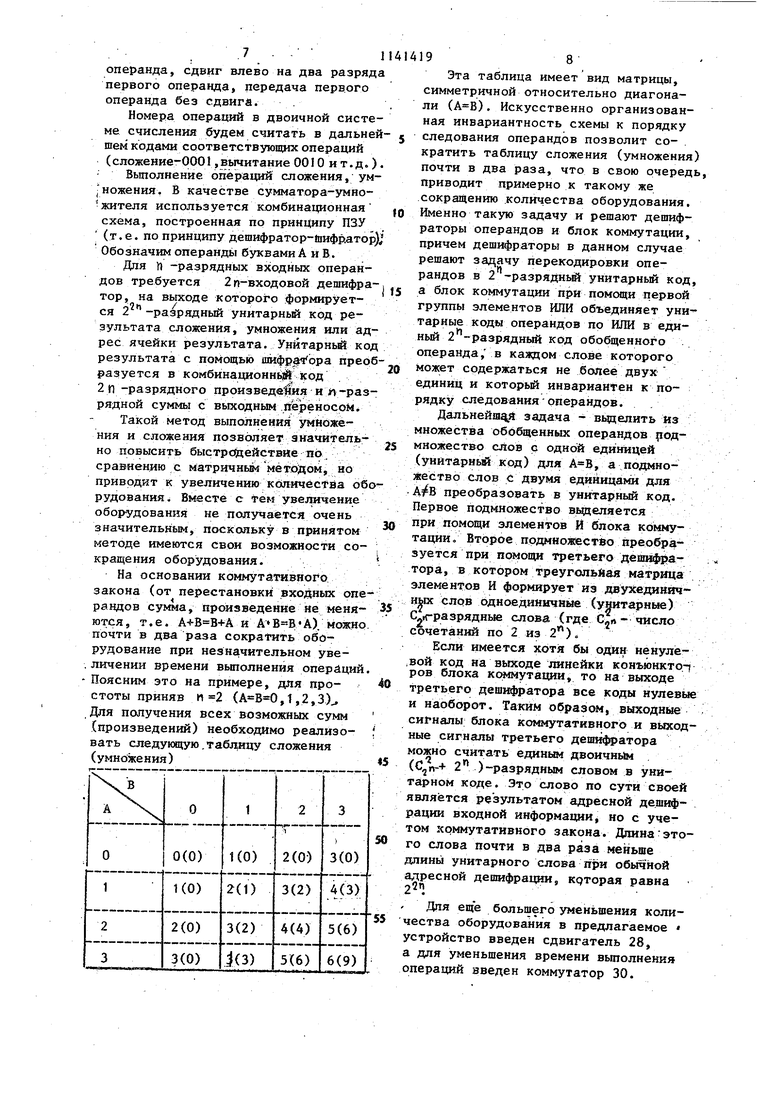

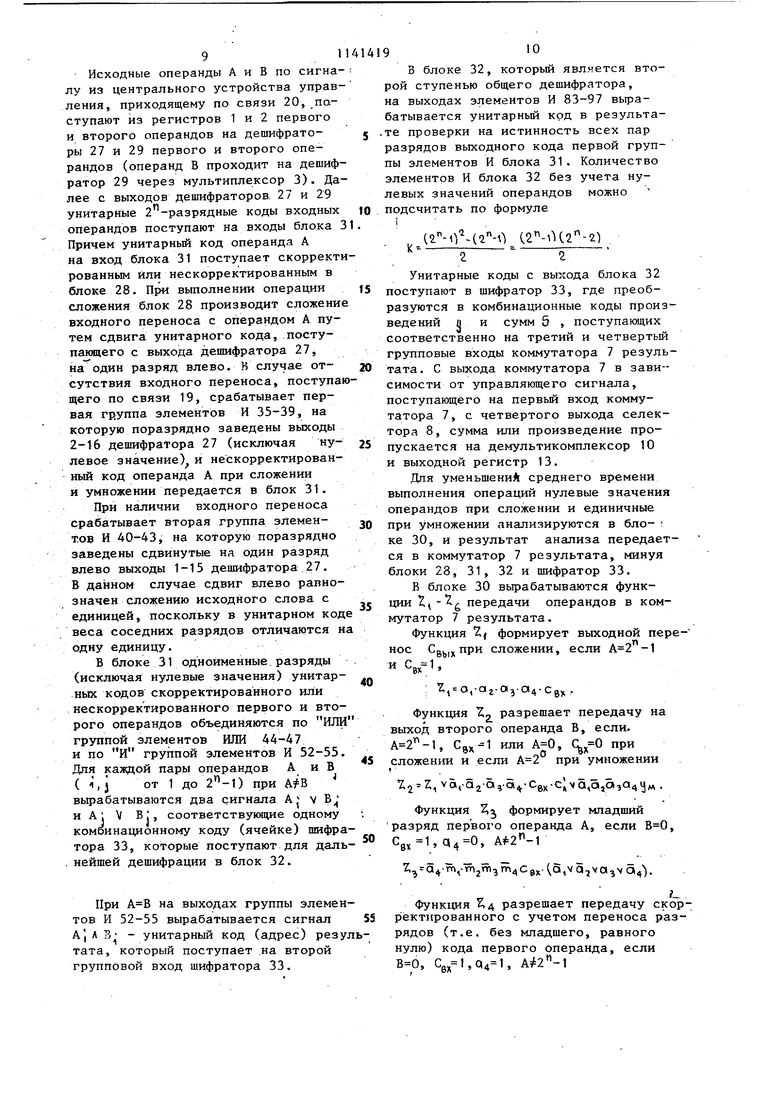

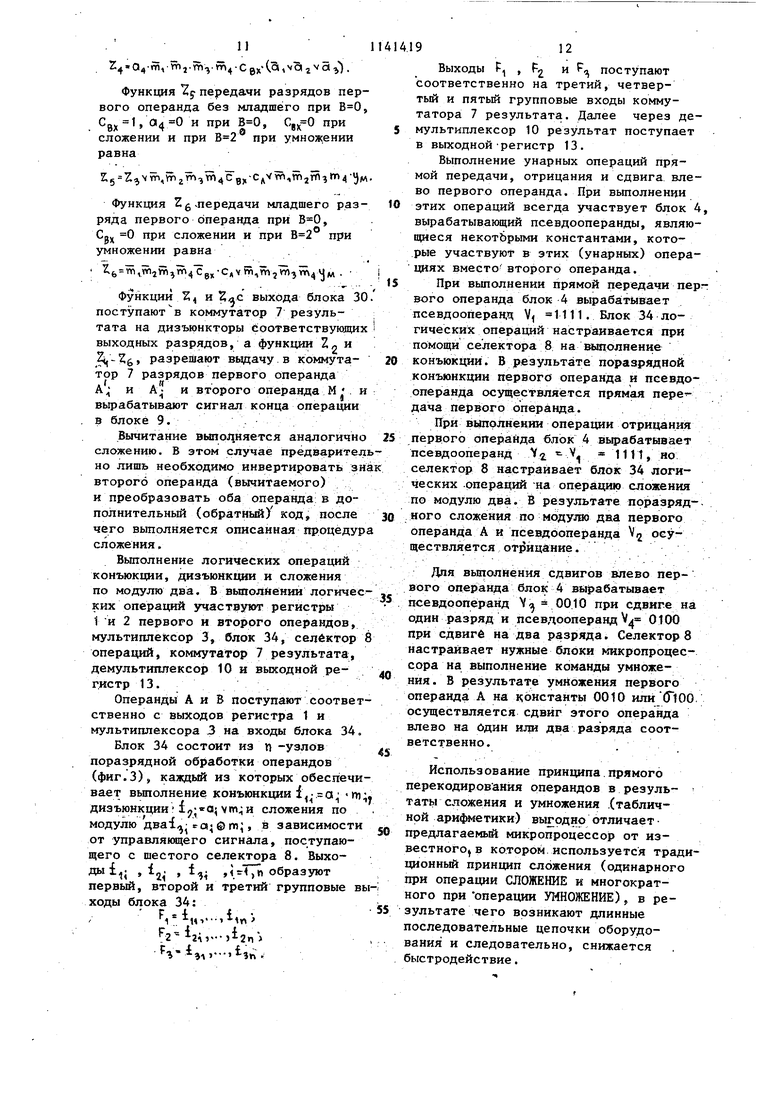

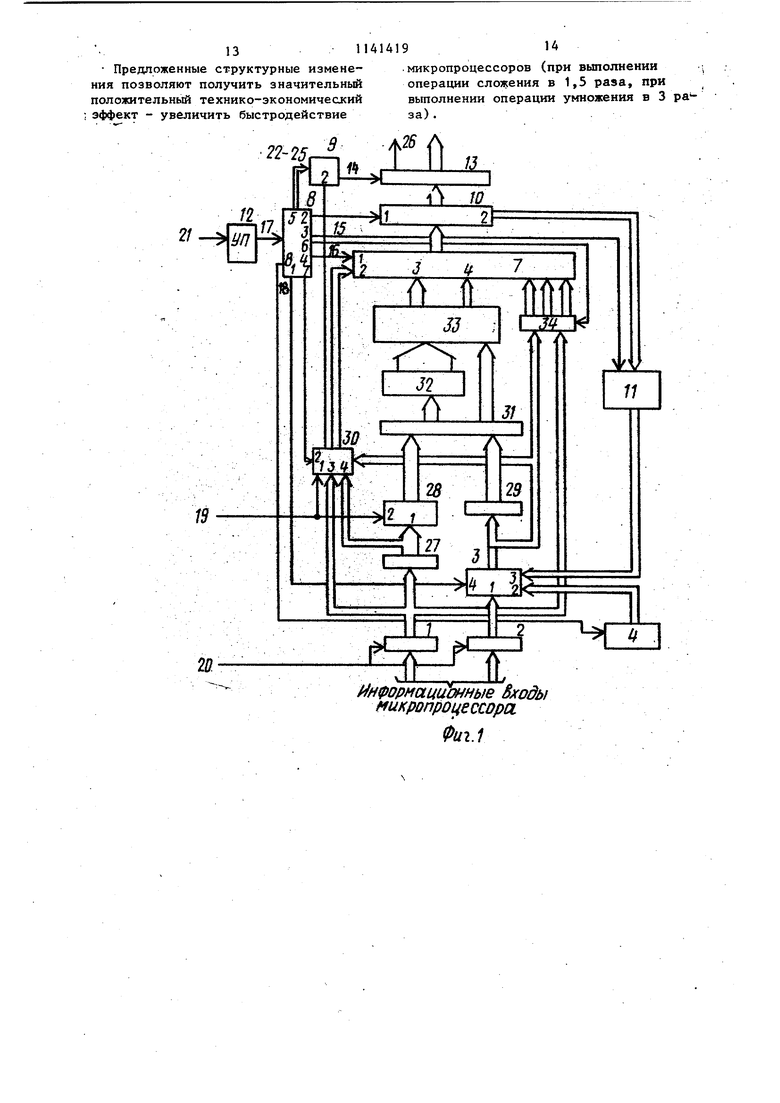

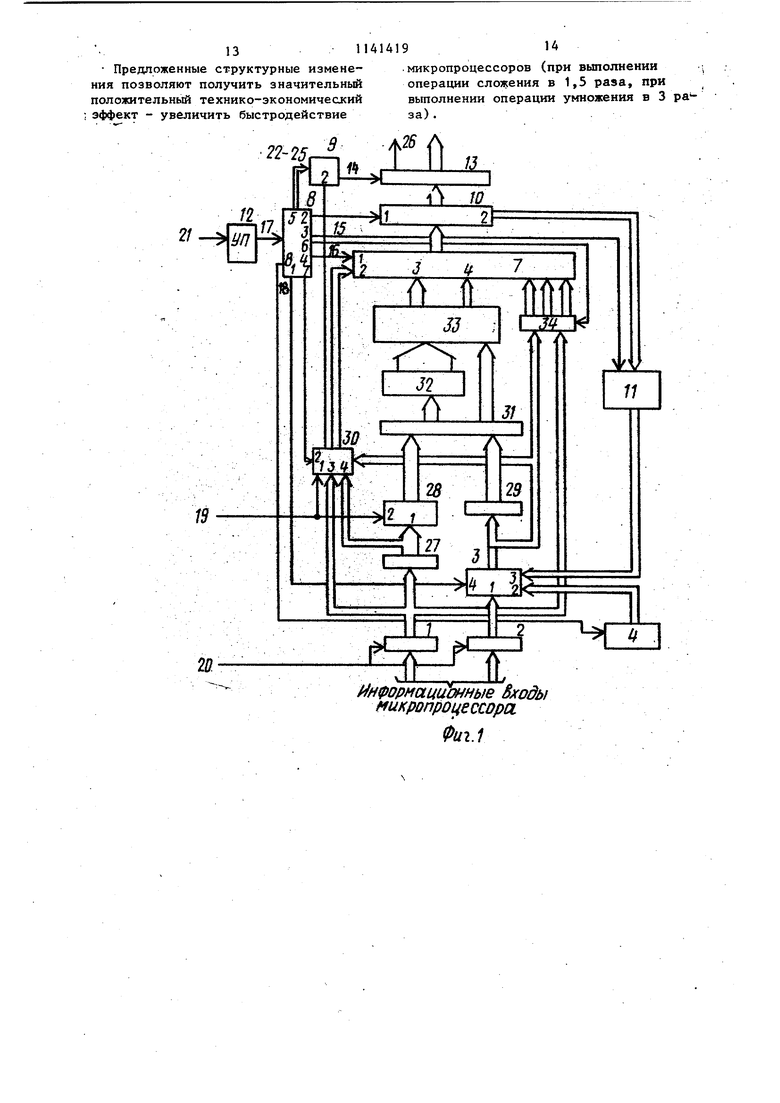

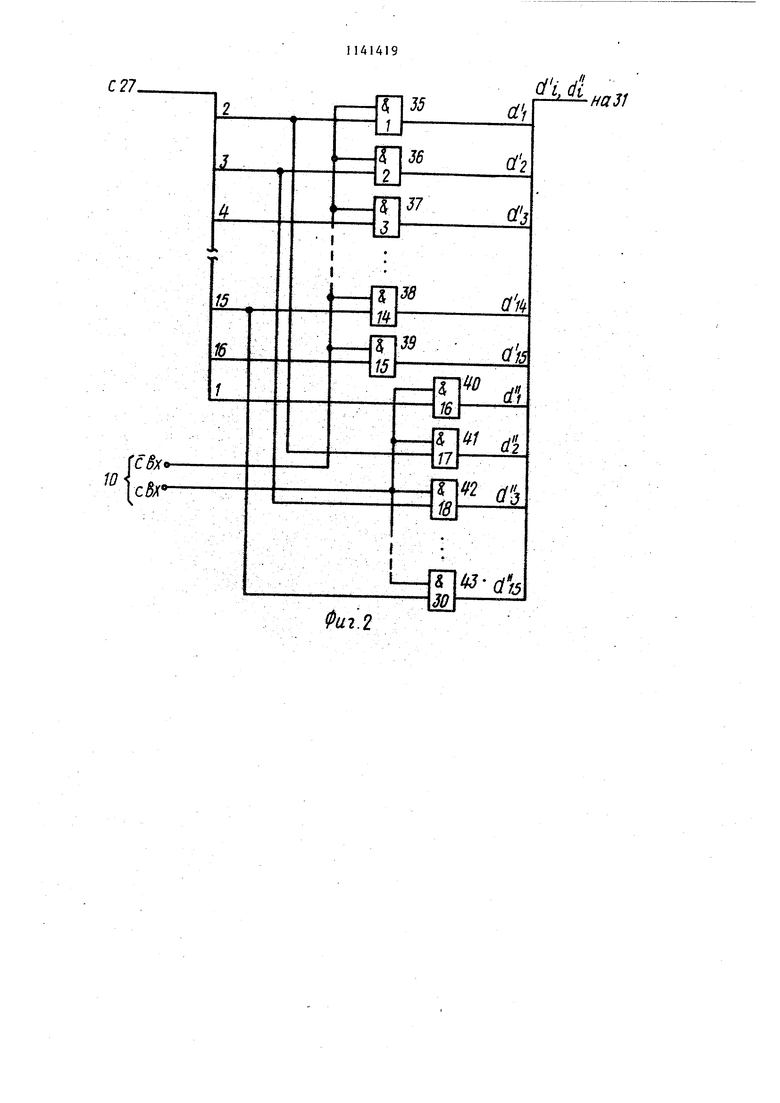

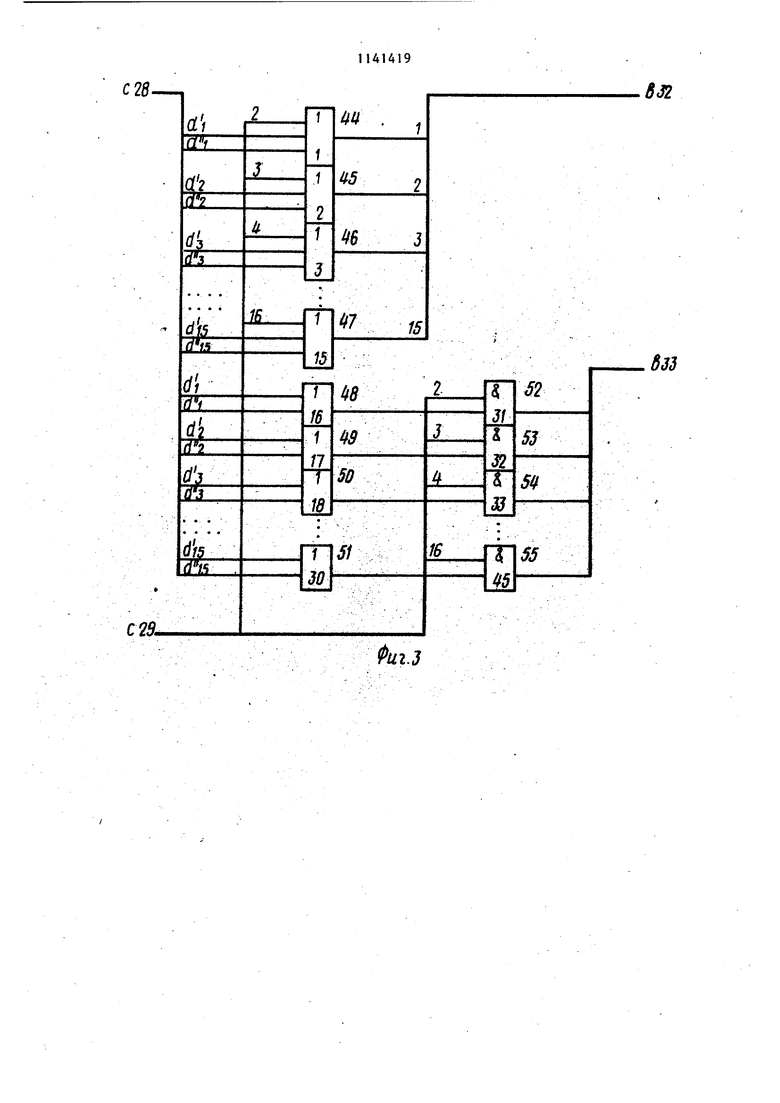

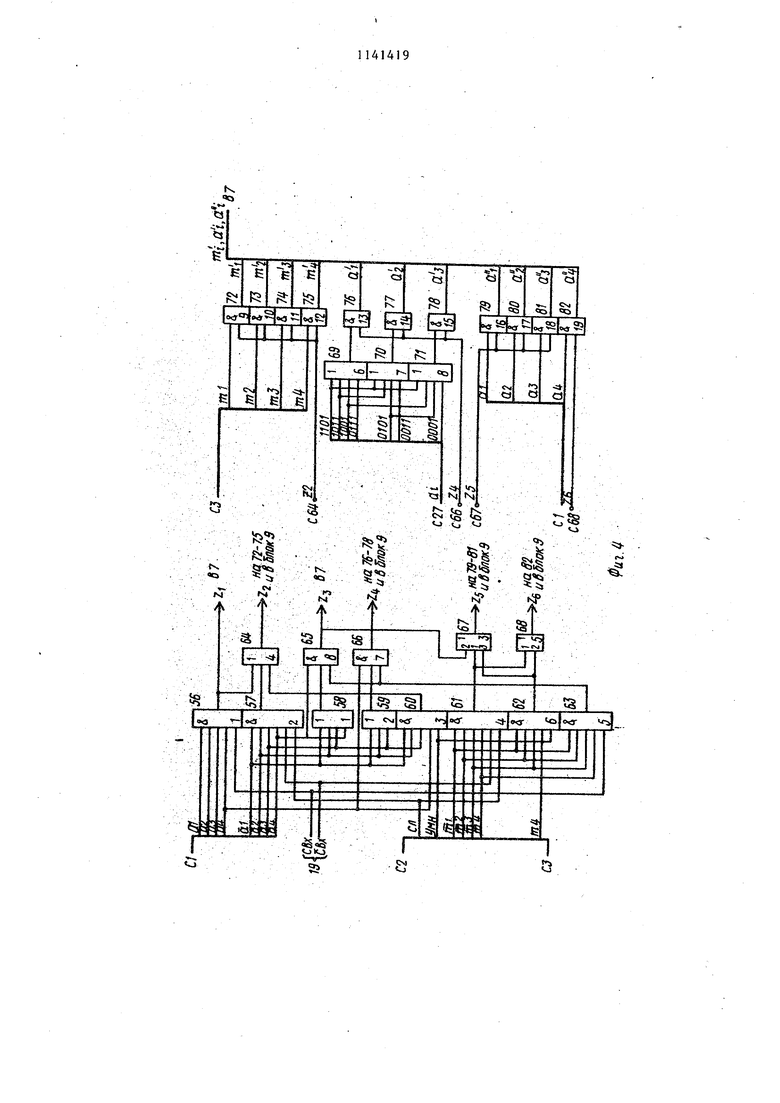

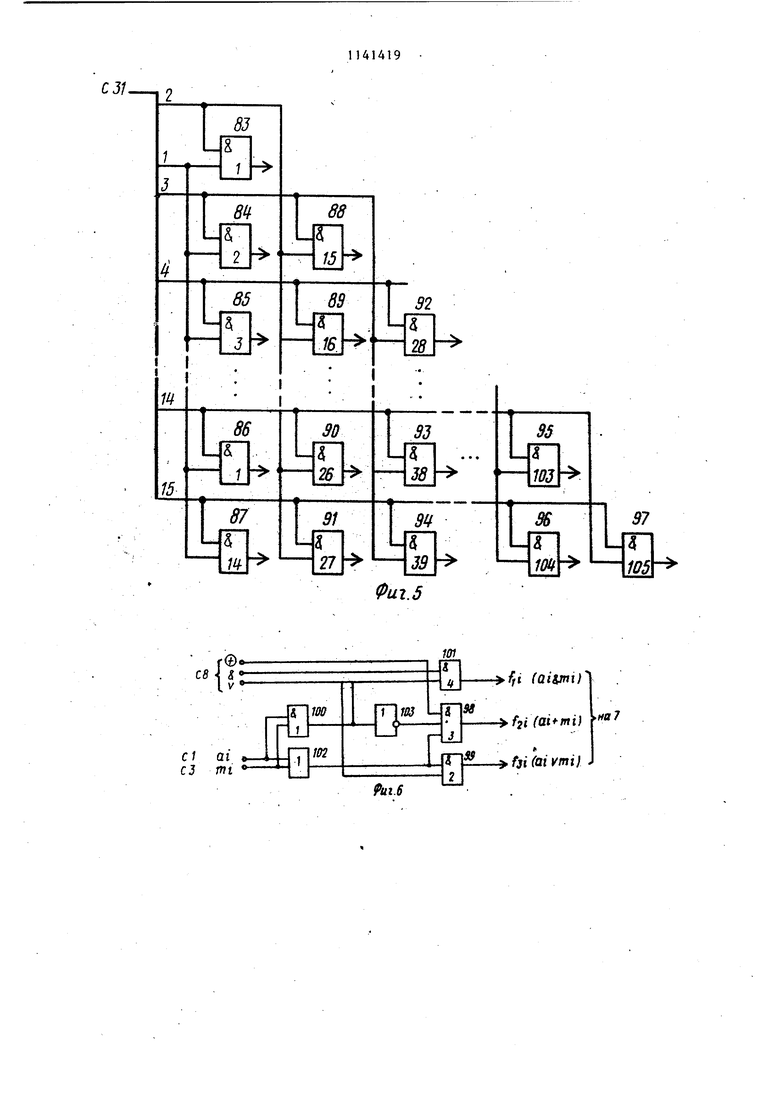

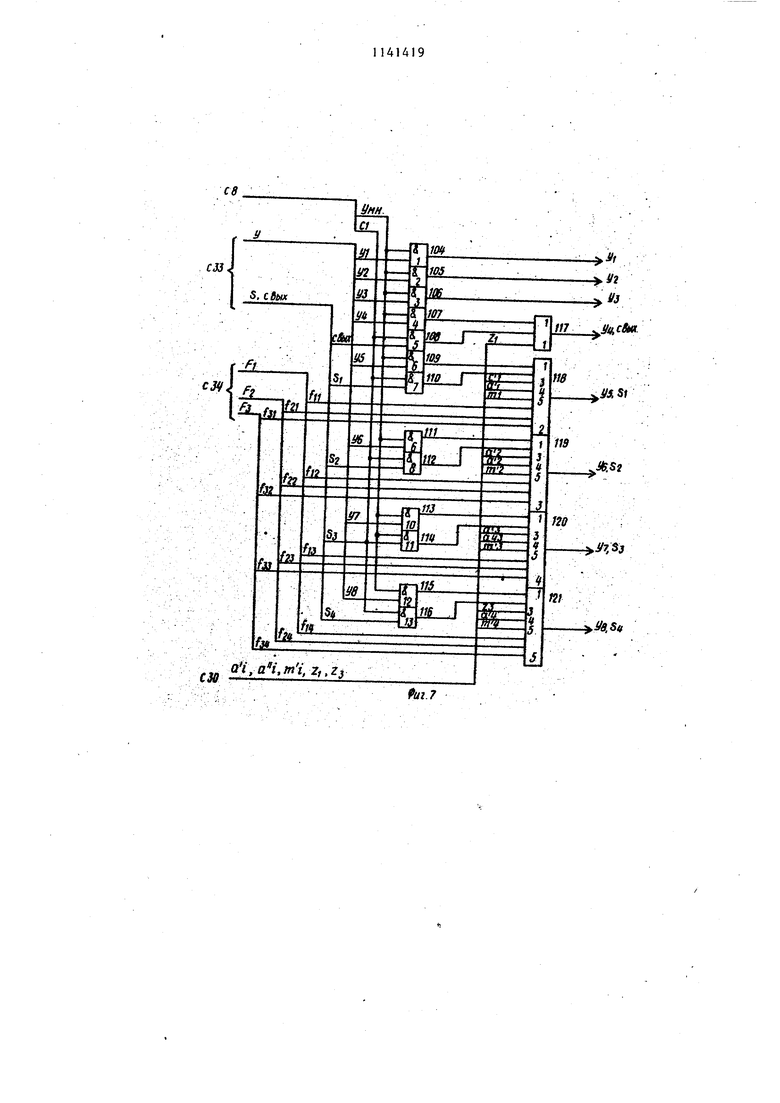

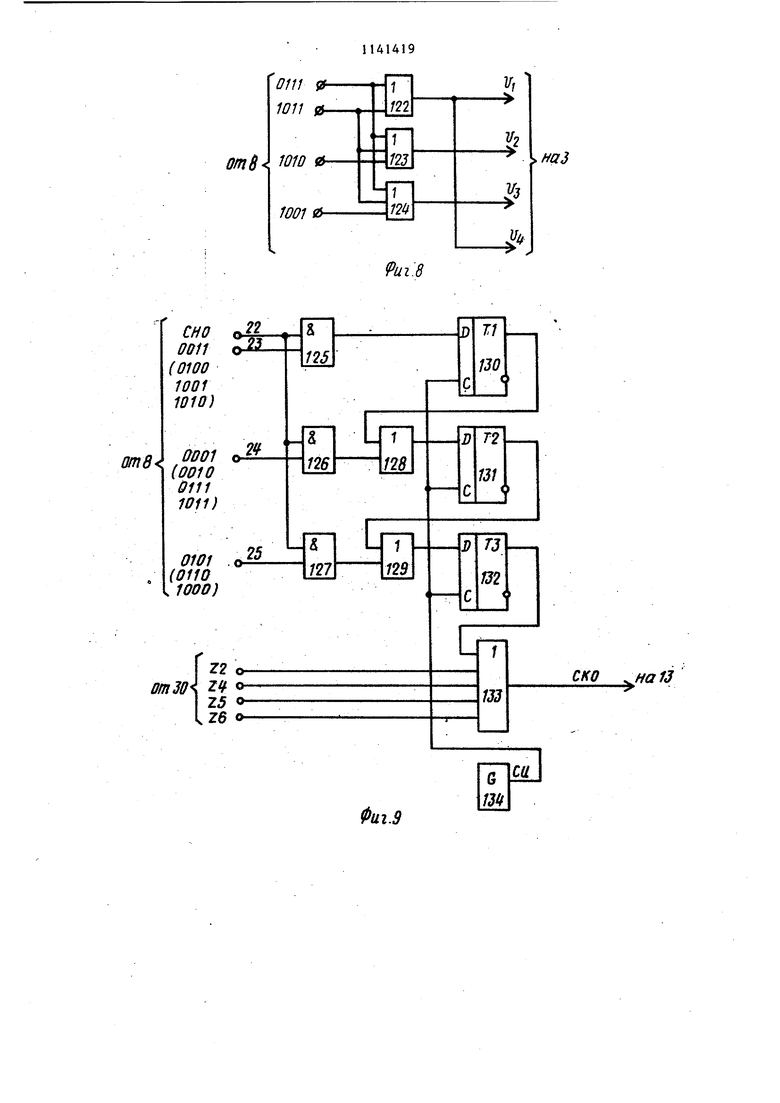

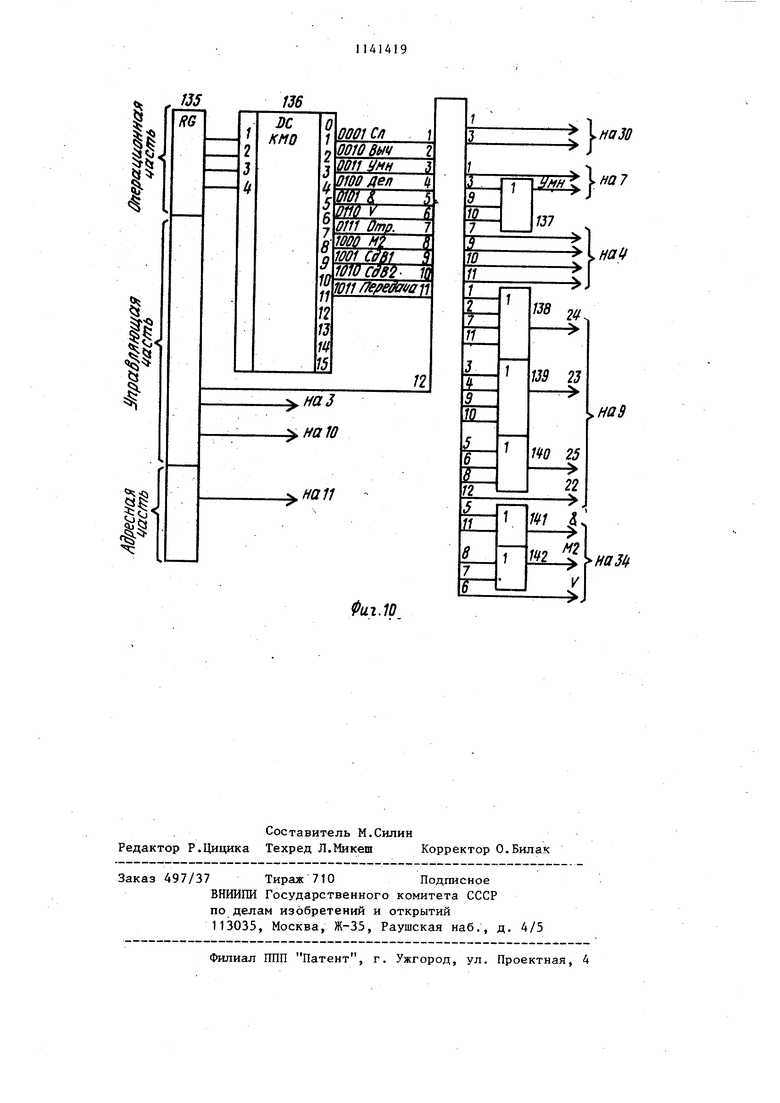

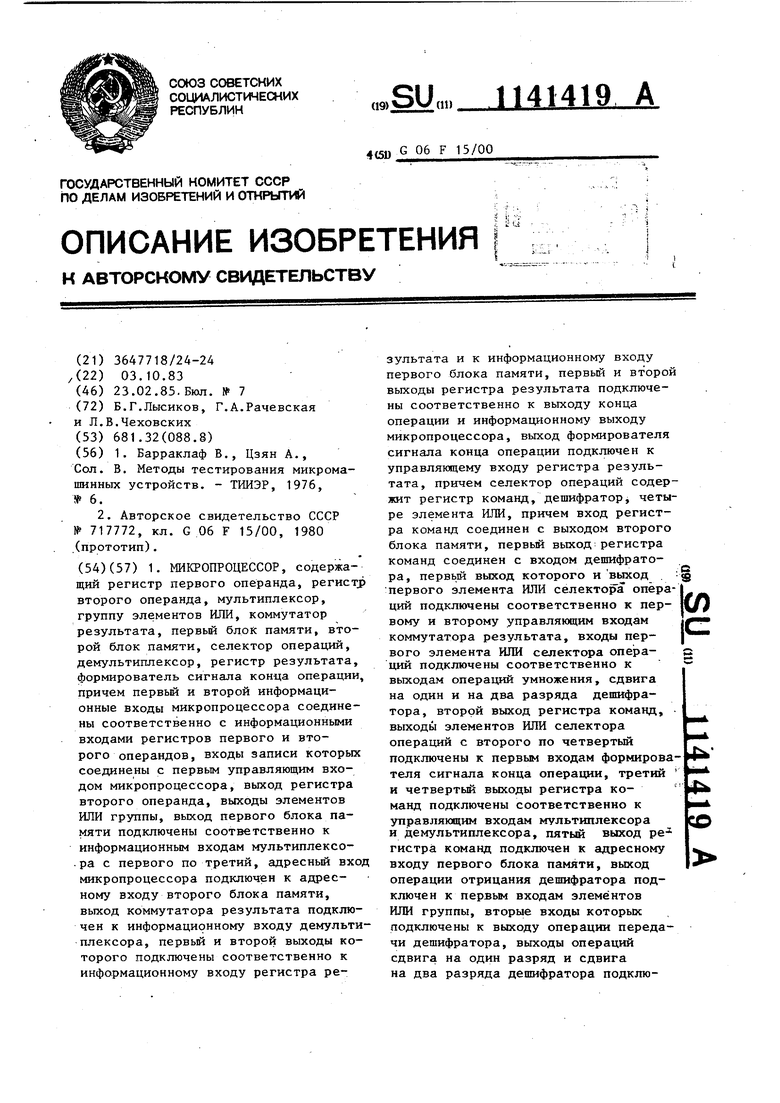

Поставленная цель достигается тем что в микропроцессор, содержащий регистр первого операнда, регистр второго операнда, мультиплексор, группу элементов ИЛИ, коммутатор результата пёрвьй блок памяти, второй блок памяти, селектор операций, демульти плексор, регистр результата, формирователь сигнала конца операции, причем пёрвьй и второй информационные входы микропроцессора соединены соответственно с информационными входами регистров первого и второго операндов, входы записи которых соединены с первым управлякяцим входом микропроцессора, выход регистра второго операнда, выходы элементов ИЛИ группы, выход первого блока памяти подключены соответственно к информационным входам мультиплексора с первого по третий, адресный вход микропроцессора подключен к адресному входу второго блока памяти, ;выход коммутатора результата подклюi чек к информационному входу демультиплексора, пёрвьй и второй выходы которого подключены соответственно к информационному входу регистра результата и к информационному входу первого блока памяти, первый и второй выходы регистра результата подключены соответственно к выходу конца операции и к информационному выходу микропроцессора, выход формирователя сигнала конца операции подклю чен к управляющему входу регистра ре зультата, причем селектор операций содержит регистр команд, дешифратор четыре элемента ИЛИ, причем вход регистра команд соединен с выходом второго блока памяти, первый информациоиньй вход регистра команд соединен с входом дешифратора, первый выход которого и выход первого 3 элемента ИЛИ селектора операций подключены соответственно к первому и второму управляющим входам коммутатора результата, входы первого элемента ИЛИ селектора операций подключенысоответственно к выходам операций умножения, сдвига на один и на два разряда дешифратора,.второй выход регистра команд, выходы элемертов ИЛИ селектора операций с второго по четвертый подключены к первым входам формирователя сигнала конца операции, третий и четвертьй выходы регистра команд подключены соответственно к управляющим входам мультиплексора и демультиплексора, пятьй выход регистра команд подключен к адресному входу первого блока памяти, вькод операции отрицания дешифратора подключен к первым входа элементов ИЛИ группы, вторые входы которых подключены к выходу операции передачи дешифратора, выходы операци сдвига на один разряд и сдвига на два разряда дешифратора подключены соответственно к третьим входам К-1-ГО и К-го элементов ИЛИ группЫэ где К - количество элементов ИЛИ в группе, входы с первого по четвер.тый второго и третьего элементов ИЛИ селектора операций подключены соответственно к выходам операций умножения, деления, сдвига на один разря сдвига на два разряда, сложения, вычитания, отрицания, передачи дешифратора, входы четвертого элемента ИЛ селектора операций подключены соответственно к выходам операций конъюн ции,дизъюнкции и сложения по модулю два дешифратора, введены дешифратор первог операнда, дешифратор второго операнда, третий дешифратор, сдв|1гатель, блок коммутации, шифратор, вторая группа элементов Ш1И, группа элементов НЕ и четыре группы элементов И, а селектор операций дополнительно соде1 жит пятый и.шестой элементы ИЛИ причем первьй и второй входы пятого и шестого элементов ИЛИ селектора операций подключены соответственно к .выходам операций конъюнкции, передачи, отрицания и сложения по модулю два дешифратора, выход регистра перв го операнда подключен к входу дешифратора первого операнда, выход мультиплексора подключен к входу дешифратора второго операнда, первый и второй выходы шифратора подключе4194ны соответственно к первому и второму информационным входам коммутатора результата, кроме того, первые и вторые входы -го элемента И первой группы подключены соответственно к -м выходам регистра перво гр операнда и мультиплексора (,N ), где N - разрядность микропроцессора и соединены соответственно с первым и вторым входами i -го элемента ИЛИ второй группы, выход которого подключен к первому входу . i-ro элемента И второй группы и соединен с первым входом -го элемента И третьей группы, выход i -го элемента И первой группы подключен к входу -го элемента НЕ группы и соединен с первым входом i -го элемента И четвертой группы, второй вход 1 -го элемента И третьей группы соединен с выходом 1 -го элемента НЕ, выходы элементов И групп с второй по четверт то подключены соответственно к информационным входам коммутатора результата с третьего по пятьй, выходы пятого и шестого элементов -ИЛИ селектора операций и выход операции дизъюнкции дешифратора подключены соответственно к вторым входам элементов И четвертой :группы, третьим входам элементов И третьей группы и вторым входам элементов И второй группы, выход дешифратора первого операнда подключен к информационному входу сдвигателя, управлякщий вход которого подключен к входу переноса микропроцессора, а выходы прямого и сдвинутого на один разряд влево кодов подключены соответственно к первому и второму информационным входам блока коммутации, третий информационный вход которого подключен к выходу дешифратора второго ойеранда, первый и второй выходы блока коммутации подключены соответственно к первому входу шифратора и входу третьего . дешифратора, выход которого подключен к второму входу шифратора, информационные входы коммутатора с.первого по четвертьй подключены соответственно к входу переноса микропроцессора, выходу регистра первого операнда, выходу дешифратора первого операнда, выходу мультиплексора, информационный выход и выход окончания операции коммутатора подключены соответственно к второму входу формирователя сигнала конца one- рации и -к шестому информационному входу коммутатора результата, выходы операций умножения и сложения Дешифратора подключены к управлякяцему/ входу коммутатора. Блок коммутации содержит две груп пы элементов ИЛИ и группу элементов И, причем выходы элементов И гру пы подключены к первому выходу блока, выходы элементов ИЛИ первой группы блока подключены к второму выходу блока, выход -го элемента ИЛИ второй группы блока подключен к первому входу i --го элемента И группы ( ,2 -1), второй вход которого соединен с первым входом 1 -го элемента ИЛИ первой группы блока, второй и третий входы -го элемента ИЛИ первой группы блока сое динены соответственно с первым и ВТО рым входами 1 -го элемента ИЛИ второ группы блока и подключены соответСтвенно к входам 1 -го разряда первого и второго информационных входов блока, второй вход i -го элемента И группы соединен с входом г-го разряда третьего информационного входа блока. На фиг.1 представлена структурна схема микропроцессора; на фиг.2 функциональная схема сдвигателя на фиг.З - функциональная схема блока коммутации,- на фиг.,4 - функциональная схема коммутатораi на фиг.5 - функциональная схема третьего дешифратора; на фиг.6 функциональная схема блока логических операций на фиг.7 - функционал ная схема коммутатора результата, на фиг.8 - функциональная схема гру пы элементовИЛИ на фиг.9 - функци нальная схема формирователя сигнала конца опера ций, на фиг. 10 функцио нальнай схема селектора операций. Микропроцессор {фиг.1) содержит регистр 1 первого операнда, регистр второго операнда, мультиплексор 3, группу элементов ИЛИ 4, коммутатор селектор 8 операций, формирователь сигнала конца операций, демультиплексор 10, первый блок 11 памяти, второй блок 12 памяти, регистр 13 р зультата, связи 14-26 управлякнцих сигналов, дешифратор 27 первого one ранда, сдвигатель 28, дешифратор 29 второго операнда, коммутатор 30, блок 31 коммутации, третий дешифратор 32 шифратор 33, блок 34 логических операций. Обозначим через h разрядность входных шин. Для определенности и простоты принятой 4. Сдвигатель 28 (фиг.2) содержит первую и вторую группы по () элементов И 35-39 и 40-43. Блок 31 коммутации (фиг.3) содержит первую и вторую группы по () элементов ИЛИ 44-47 и 48-51 и группу из () элементов И 52-55. Коммутатор 30 (фиг.4) содержит группу элементов И и элементов ИЛИ . формирования фнукций ,7 ; 56-68 соответственно, элементы ИЛИ 69-71 формирования старпмх разрядов первого операнда, элементы И 72-75 передачи второго операнда, элементы И 76-78 передачи сформированных старших разрядов первого операнда и элементы И 79-82 передачи первого операнда. Третий дешифратор 32 (фиг ..5) содержит треугольную матрицу элементов И 83-97, состоящую из () столбцов и () строк. Блок логических операций (фиг.6) содержит И узлов поразрядной обра- ботки, каждый из которых содержит четыре элемента И 98-101, элемент ИЛИ 102, элемент НЕ 103. Коммутатор 7 результата (фиг.7) содержит группу элементов И 104-116 и элементов ИЛИ 117-121 для формирования 2г( -разрядного результата. : Группа элементов ИЛИ 4 (фиг.8) содержит элементы ИЛИ 122-124. Формирователь 9 сигнала конца операции (фиг.9) содержит группу элементов И 125-127, группу элементов ИЛИ 128 и 129, группу триггеров 130-132, элемент ИЛИ 133 и генератор 134 импульсов. Селектор операций 8 (фиг.10) содержит регистр 135 команд, дешифратор 136 и элементы ИЛИ 137-142. Микропроцессор работает следующим образом. Пусть для определенности он должен выполнит одиннадцать основных операций из следуккцего списка (список может быть видоизменен):сложение алгебраическое, вычитание алгебраическое, умножение, деление, конъюнкция (поразрядная), дизъюнкция (поразрядная), отрицание (поразрядное) битов первого операнда, сложение по модулю два (поразрядное), сдвиг влево на один разряд первого операнда, сдвиг влево на два разряд первого операнда, передача первого операнда без сдвига. . Номера операций в двоичной систе ме счисления будем считать в дальне шем кодами соответствующих операций С сложение-0001, вьтчитаниа 0010 и т. д. Выполнение операций сложения, ум |ножения, В качестве сумматора-умно жителя используется комбинахщонная схема, построенная по принципу ПЗУ (т.е. по принципу дешифратор-шифратор Обо значим операнды буквами А и В. Для И -разрядных входных операндов требуется 2п-входовой дешифра тор, на выходе которого формируется 2 -разрядный унитарный код результата сложения, умножения или ад рес ячейки результата. Унитарньй ко результата с пq foщыo прео разуется в комбинационней код 2п -разрядного произведа и и п-раз рядной суммы с выходным rtiepeHocoM. Такой метод выполнения умножения и сложения позволяет значительно повысить быстродействие по. сравнению с матричным методом, но приводит к увеличению кбличёс аа об рудования. Вместе с тем увеличение оборудования не полз ается очень значительным, поскольку в принятом методе имеются свои возможности сокращения оборудования. На основании коммутативного закона (от перестановки входных опе рандов сумма, произведение не меняются, т.е. и ). можно почти в два раза сократить оборудование при незначительном уве. личении времени выполнения операций Поясним это на примере, для простоты приняв (,1,2,3) Для получения всех возможных сумм (произведений) необходимо реализовать следующую.таблицу сложения (умножения) 198 Эта таблица имеет вид матрицы, симметричной относительно диагонали (). Искусственно организованная инвариантность схемы к порядку следования операндов позволит со- . кратить таблицу сложения (умножения) почти в два раза, что в свою очередь, приводит примерно к такому же сокращению количества оборудования. Именно такую задачу и решают дешифраторы операндов и блок коммутации, причем дешифраторы в данном случае решают задачу перекодировки операндов в 2 -разрядный унитарный код, а блок коммутации при помощи первой группы элементов ИЛИ объединяет унитарные коды операндов по ИЛИ в единый 2 -разрядный код обобщенного операнда, в каждом слове которого Может содержаться не более двух единиц и которьй инвариантен к порядку следования - операндов . Дальнейшей задача - вьщелить из множества обобщенных операндов годмножество слов с однбй единицей (унитарный код) для , а подмножество слов С двумя едййица1 М для преобразовать в унитарный код. Первое подмножество вьщеляется при помощи элементов И блока коммутации. Второе подмножест ао преобразуется при третьего дешифратора, в котором треугольйая матрица элементов И формирует из даухвдиняч нь1х слов Одноединичные (унитарные) Cjrf-разрядные слова (где С п-число сочетаний по 2 из 2)« Если имеется хотя бы один ненулёвой код на выходе линейки конъюнкто.-; ров блока коммутации, то на выходе третьего дешифратора все коды нулевые и наоборот. Таким образом, выходные сигналы блока коммутативного и выходные сигналы третьего дешифратора можно считать единьм двоичньЫ ( 2 )-разрядным словом в унитарном коде. Это слово по сути своей является результатом адресной дешифрации входной информацииj но с учетом коммутативного закона. Длина:этого слова почти в два раза меньше длины унитарного слова при обычНой адресной дешифрации, крторая равна 22П Для еще большего уменьшения количества оборудования в предлагаемое « устройство введен сдвигатель 28, а для уменьшения времени вьтолнения операций введен коммутатор 30. 9 Исходные операнды А и В по сигна лу из центрального устройства управ ления, приходящему по связи 20, поступают из регистров 1 и 2 первого и второго операндов на дешифраторы 27 и 29 первого и второго операндов (операнд В проходит на дешиф ратор 29 через мультиплексор 3). Да лее с выходов дешифраторов. 27 и 29 унитарные 2 -разрядные коды входных операндов поступают на входы блока Причем унитарный код операнда А на вход блока 31 поступает скоррект рованным или нескорректированным в блоке 28. При выполнении операции сложения блок 28 производит сложени входного переноса с операндом А путем сдвига унитарного кода, поступающего с выхода дешифратора 27, на один разряд влево. В случае отсутствия входного переноса, поступа щего по связи 19, срабатывает первая гр.уппа элементов И 35-39, на которую поразрядно заведены выходы 2-t6 дешифратора 27 (исключая нулевое значение) и нескорректированный код операнда А при сложении и умножении передается в блок 31. При наличии входного переноса срабатывает вторая группа элементов И 40-43, на которую поразрядно заведены сдвинутые на один разряд влево выходы 1-15 дешифратора 27. В данном случае сдвиг влево равнозначен сложению исходного слова с единицей, поскольку в унитарном код веса соседних разрядов отличаются и одну единицу. В блоке 31 одноименные разряды (исключая нулевые значения) унитарных кодов скорректированного или нескорректированного первого и второго операндов объединяются по ИЛИ группой элементов ИЛИ 44-47 и по и группой элементов и 52-55. Для каждой пары операндов А и В ( , J от 1 до ) при вырабатываются два сигнала А V и А; V В, соответствующие одному комбинационному коду (ячейке) шифра тора 33, которые поступают для даль нейшей дешифрации в блок 32. При на выходах группы элемен тов И 52-55 вырабатывается сигнал А А - унитарный код (адрес) резу тата, который поступает .на второй групповой вход шифратора 33. 9 В блоке 32, который является второй ступенью общего дешифратора, на выходах элементов И 83-97 вырабатывается унитарный код в результате проверки на истинность всех пар разрядов выходного кода первой группы элементов И блока 31. Количество элементов И блока 32 без учета нулевых значений операндов можно подсчитать по формуле ( ) 22 Унитарные коды с выхода блока 32 поступают в шифратор 33, где преобразуются в комбинационные коды произведений и и сумм 5 , поступающих соответственно на третий и четвертый групповые входы коммутатора 7 результата. С выхода коммутатора 7 в зависимости от управляющего сигнала, поступающего на первьй вход коммутатора 7, с четвертого выхода селектора 8, сумма или произведение пропускается на демультикомплексор 10 и выходной регистр 13. Для уменьшений среднего времени выполнения операций нулевые значения операндов при сложении и единичные при умножении анализируются в блоке 30, и результат анализа передается в коммутатор 7 результата, минуя блоки 28, 31, 32 и шифратор 33. В блоке 30 вырабатываются функции передачи операндов в коммутатор 7 результата. Функция Z| формирует выходной перенос при сложении, если и VI, ; ,-аг-а,.а4-Св, Функция Zp разрешает передачу на выход второго операнда В, если. , или , при сложении и если при умножении Z2 Z, va,.a2-a,.a -Cgx-civa,aja,a4(jw. Функция j формирует младший разряд первого операнда А, если , , 0(0, 4 - 2 3 4C9x4a ajva,v54V Функ1щя 4 разрешает передачу скорректированного с учетом переноса разрядов (т.е. без младшего, равного нулю) кода первого операнда, если , С 1,,

n1

Z a4-rn,-Wj.YYi -m -Cgx 2 °3V

Функция 7f передачи разрядов первого операнда без младшего при , Cg 1, и при , при сложении и при при умножении равна

,ч,),.2Т Э С Функция Zg.передачи младшего разряда первого операнда при , при сложении и при при умножении равна .

fe TO,rn.jVf),m4Cg -C;(,m,vYi3W4JM

Функции Z и лС выхода блока 30 поступают в коммутатор 7 результата на дизъюнкторы Соответствующих выходных разрядов, а функции 2 и 2ц , разрешают задачу в коммутатор 7 разрядов первого операнда и А и второго операнда М и вырабатывают сигнал конца операции в блоке 9.

Вычитание вьшо няется аналогично сложению. В этом случае предварительно лишь необходимо инвертировать зн$ второго операнда (вычитаемого) и преобразовать оба операнда в дополнительный (обратный) код, после чего выполняется описанная процедура сложения.

Выполнение логических операций конъюкции, дизъюнкции и сложения по модулю два. Б вьтолнении логических операций участвуют регистры t И 2 первого и второго операндов, мультиплексор 3, блок 34, селбктор 8 операций, коммутатор 7 результата, демультшшексор 10 и выходной регистр 13.

Операнды А и В поступают соответственно с выходов регистра 1 и мультиплексора 3 на входы блока 34.

Блок 34 состоит из n -узлов поразрядной обработки операндов (фиг.З), каждый из которых обеспечивает выполнение конъюнкции i,--a 111; дизъюнкции-ij; a сложения по модулю ). ©rw, в зависимости от управляющего сигнала, поступающего с шестого селектора 8. Выходы ; 2i Э4 ,1.-Т7п образуют первый, второй и третий групповые вы

ходы блока 34:

с X (

1

2 iab-J Zn

г° «

1912

Выходы PI , 2 поступают соответственно на третий, четвертый и пятьй групповые входы коммутатора 7 результата. Далее через демультиплексор 10 результат поступает в выходнойрегистр 13.

Выполнение унарных операций прямой передачи, отрицания и сдвига влево первого операнда. При выполнении этих операций всегда участвует блок 4 вырабатывающий псевдооперанды, являющиеся некоторыми константами, которые участвуют в этих (унарных) операциях вместовторого операнда.

При выполнении прямой передачи первого операнда блок 4 выраба;тывает псевдооперан,ч V 1111. Блок 34 логических операций настраивается при помощи селектора 8 на выполнение конъюкции. В результате поразрядной конъюнкции первого операнда и псевдооперанда осуществляется прямая пере дача первого операнда.

При выполнении операции отрицания первого операнда блок 4 вырабатывает псевдооперанд V 1 1П1, но селектор 8 настраивает блок 34 логических операций -на операцию сложения по модулю два. В результате прразрядного сложения по модулю дна первого операнда А и псевдооперанда V осуществляется отрицание.

Для выполнения сдвигов Влево первого операнда блок 4 вырабатывает псевдооперанд V; 0010 при сдвиге на один разряд и псевдооперанд V 0100 при сдвиге на два разряда. Селектор 8 настраивает нужные блоки микропроцессора на выполнение команды умножения . В р езультате умножения первого операнда А на щонстанты 0010 или (ГШО осуществляется сдвиг этого операнда влево на Один или два разряда соответственно.

Использование принципа.прямого перекодирования операндов в результатьг сложения и умножения .(табличной арифметики) выгодно отличаетпредлагаемьй микропроцессор от известного в котором используется традиционный принцип сложения (одинарного при операции СЛОЖЕНИЕ и многократного при операции УМНОЖЕНИЕ), в результате чего возникают длинные последовательные цепочки оборудования и следовательно, снижается быстродействие.

13 114141914

Предложенные структурные измене-.микропроцессоров (при вьшолнении

ния позволяют получить значительныйоперации сложения в 1,5 раза, при

положительный технико-экономическийвыполнении операции умножения в 3 ра; эффект - увеличить быстродействиеза).

л4 Л 22(Информационные Входы ffUKponpOLfe ссора

Фиг.Г

С 27,

Фиг.7.

dul

на 31

C2g-

eJ2

Фиг.З

С 31,

С8 4 S

ci ai c3 mi

tfZ.J

101

сзо

9иг.7

от 6

сио

0011 (0100 1001 1010)

0001 о (0010 0111 1011)

0101 (0110

L1000}

отЗО

kZ6 о

маЗ

иг.Ю

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Барраклаф В., Цзян А., Сол | |||

| В | |||

| Методы тестирования микромашинных устройств | |||

| - ТИИЭР, 1976 6 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропроцессор | 1977 |

|

SU717772A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-23—Публикация

1983-10-03—Подача