можностей за счет перестройки основания системы счисления. Перемножаемые числа могут быть записаны в системе счисления с произвольным основанием Р, где для записи любого основания используется одно и то же количество двоичных разрядов. При работе с меньшими основаниями в неиспользуемые двоичные разряды сомножителей записываются нули. Сомножители имеют г Р-ичных разрядов и могут быть простыми дробями, смешанными дробями или целыми числами в любой комбинации. Сомножители подаются синхронно младшими разрядами вперед по одному Р-ич- ному разряду в такте. Младшая часть произведения выдается с 1-го по г-й такт, старшая часть произведения выдается начиная с (г+1)-го такта. Младшая и старшая части произведения выдаются по раздельным выходам. Изме1

Изобретение относится к вычислительной технике и предназначено для умножения чисел, представленных в различных Р-ичных системах счисления и, поступающих синхронно, младшими разрядами вперед.

Цель изобретения - расширение фунциональных возможностей путем перестройки основания системы счисления.

На фиг.1 изображена функциональная

.-

схема устройства; на фиг.2 - функциональная схема блока управления; на фиг.З - функциональная схема выходного сумматора; на фиг.4 - функциональная схема узла образования пере носа,

В состав устройства входят первый 1 и второй 2 регистры сомножителей, группа умножителей 3, образующих блок формирования частичных произведений, группа узлов 4 суммирования, образу- юпдах блок суммирования, регистр 5 хранения поразрядньпс сумм, регистр 6 хранения переносов, первый 7 и вто- рой 8 буферные регистры, три коммутатора 9 - П, выходной сумматор 12, элемент 13 памяти, дешифратор 14 ос- йования системы счисления, сумматор 15 по модулю два, второй 16 и первый

17 триггеры знака, блок 18 унравленение основания системы счисления производится сменой кода основания на шинах кода основания, Устройство может работать с числами различной разрядности, что достигается изменением кода разрядности на шинах кода разрядности. В состав устройства входят регистры 1 и 2 первого и второго сомножителей, блок формирования частичных произведений, состоящий из группы умножителей 3, блок суммирования, состоящий из группы узлбй суммирования 4, регистров 5, 6 хранения поразрядных сумм и поразрядных переносов, буферные регистры 7, 8, коммутаторы 9 - 11, выходной сумматор I2, элемент памяти 13, дешифратор 14 основания системы счисления, сумматор 15 по модулю два, два триггера знака 16, 17 и блок управления 18. 1 з.п, ф-лы. 4 ил.

5

fO

t5

.

30

НИН, вход 19 первого сомножителя, вход 20 второго сомножителя, входы 21 и 22 знаков первого и второго сомножителей, выход 23 старшей части ; произведения, выход 24 младшей части произведения, вход 25 кода основания, выход 26 знака произведения, вход 27 кода разрядности, вход 28 начальной установки, вход 29 запуска, вход 30 внешней синхронизации, первый вход 31 синхронизации, второй вход 32 синхронизации, вход 33 отключения коррекции. Узел 4 суммирования имеет входы 34 выбора основания, выход 35 блокировки, входы 36 слагаемых, выходы 37 поразрядной суммы и выходы 38 поразрядного переноса.

Блок 18 управления имеет выход 39, выходы 40 разрядности и выходы 41 управления. Блок 18 управления содержит генератор 42 тактовых импульсов, регистр 43 сдвига, элемент ИЛИ-НЕ 44, коммутатор 45 разрядности, дешифратор 46 разрядности, 1К-триггер 47 и элемент ИЛИ 48.

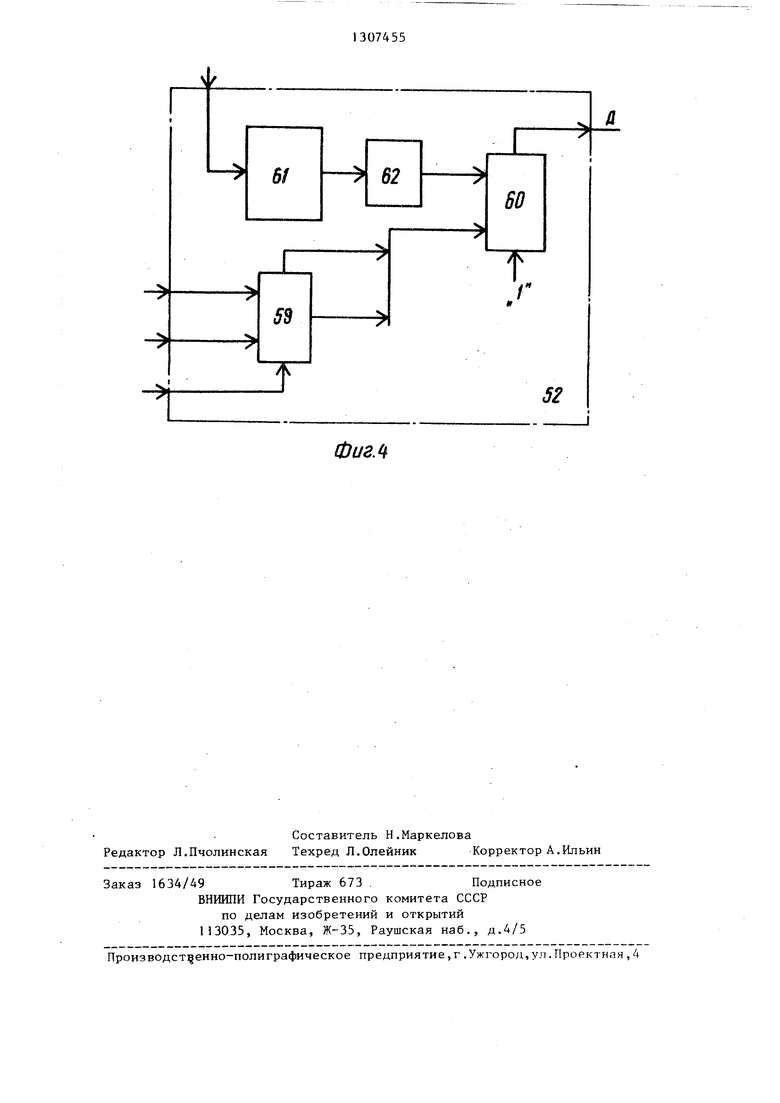

Выходной сумматор 12 образуют второй 49 и первый 50 сумматоры, коммутатор 51, узел 52 образования tiepe- носа, узел 53 коррекции, узел 54 инверсии, D-триггер 55, элемент И 56,

3

элемент ИЛИ 57 и узел 58 ограничения разрядности.

Узел 52 образования переносов сдержит сумматоры 59 и 60, шифратор 61 и узел 62 инверсии.

Устройство работает следующим оразом.

Как положительные, так и отрицательные сомножители записаны прямы кодами в используемой Р-ичной систме счисления где Р 5 и подаются синхронно младшими разрядами впере на входы 19 и 20. Знаки сомножи- ел подаются на входы 21 и 22. Старшая часть произведения вьщается на выход 23, младшая часть произведения на выход 24, а знак произведения - на выход 26. Основание системы счи

ления, в которой работает устройство, определяется кодом основания, пода- 20 ваемым на вход 25. Величина основания соответствует двоичному отображению кода основания. Например, при основании код основания в двоичной форме 10111. Рассмотрим в качестве примера перемножение двух правильных дробей .(Г1) (5) (22) и .(8) (10) (13), выраженных в систе ме счисления с основанием .

5

25

30

С каждым тактом сомножители А и В подаются на входы регис тров 1 и 2, в старших неиспользуемых при данном основании Р разрядах подаются нули. На выходах умножителей 3 образуются проряда вправо в следующем такте. Ввод сомножителей, образование углов и суммирование в тактах производится согласно с приведенной диаграммой ум- 5 ножения. В последнем г-м такте запи- сьтаются старшие разряды сомножителей, на выходах узлов 4 образуются два Р-ичных числа, которые подаются на входы буферных регистров 7 и 8, этих двух чисел есть искомое произведение. По (г+1)-му такту два числа г-го такта записываются в буферные регистры 7 и 8, а их младшие разряды через коммутаторы 9 и 10 подаются на числовые входы выходного сумматора 12, на выходах 23 которого образуется младший Р-ичный разряд произведения. С каждым следующим тактом на выходах 23 образуются очередные разряды произведения. Знак произведения определяется на сумматоре 15, первым тактом записывается в триггер 17, а (r-i-l)-M тактом -.в триггер 16 и въедается на выход 26. На выходной сумматор 12 последовательно из буферных регистров 7 и 8 через коммутаторы 9 и 10 подаются значения двух чисел г-го такта. При умножейии чисел, выраженных смешанными дробями или це- лъо4И числами в любой комбинации, включая и правильные дроби, младшую часть произведения получают на выходах. Младшая часть произведения выдается .с первого по г-й такт .

30

изведения одноразрядных Р-ичных чи- Р вводе сомножителей разряды млад- сел, записанных в регистрах 1 и 2. шей части произведения последова- На входы управления каждого умножи- тельно с первого по г-й такт образу- теля 3 подаются сигналы выбора осно- тся на выходах 37 поразрядных сумм вания с выходов дешифратора 14 осно- п узлов 4(1) - 4(4) суммирования, которые подключены к входам коммутатора И . Сигналами управления выходов 41 блока 18 управления в первом такте на выход коммутатора 11 передает-.

вания. В исходном состоянии в (2,..., 4) разрядах регистроб 1 и 2 сомножителей и в регистрах 5 и 6 должны быть записаны нули. С каждым тактом

сомножители записываются в регистры ся значение поразрядной суммы с вы1 и 2, на входах узлов 4 суммирова- -хода 37 узла 4(1), во втором такте ния в совокупности образуются в 1,с выхода 37 узла 4(2)..., в г-ом так2,3,... тактах соответственно 1-йте с выхода 37 узла 4(4) . Старшая часть

угол, 2-й угол, 3-й угол,.... На вы-произведения выдается по шинам 23 начи.

50

ходах узлов 4 суммирования образуются в совокупности два Р-ичных числа суммы угла данного такта и двух чисел суммы предыдущего такта, сдвинутых на два Р-ичных разряда вправо в

ная с (г+1)-го такта. Таким образом, при перемножении двух произвольных трехразрядных чисел три мпадших разряда выдаются по шинам 24, а три старших - по шинам 23. Порядок просторону младших разрядов. Сумма в ви-сс изведения определяется по значениям де двух чисел с выходов узлов 4 за- порядков сомножителей, а величина письшается каждым тактом в регистры 5.и 6 и подается на соответствующие входы узлов 4 со сдвигом на два разцикла определяется по числу с большей разрядностью. При получении млад .шей и старшей частей произведения знач

ряда вправо в следующем такте. Ввод сомножителей, образование углов и суммирование в тактах производится согласно с приведенной диаграммой ум- ножения. В последнем г-м такте запи- сьтаются старшие разряды сомножителей, на выходах узлов 4 образуются два Р-ичных числа, которые подаются на входы буферных регистров 7 и 8, этих двух чисел есть искомое произведение. По (г+1)-му такту два числа г-го такта записываются в буферные регистры 7 и 8, а их младшие разряды через коммутаторы 9 и 10 подаются на числовые входы выходного сумматора 12, на выходах 23 которого образуется младший Р-ичный разряд произведения. С каждым следующим тактом на выходах 23 образуются очередные разряды произведения. Знак произведения определяется на сумматоре 15, первым тактом записывается в триггер 17, а (r-i-l)-M тактом -.в триггер 16 и въедается на выход 26. На выходной сумматор 12 последовательно из буферных регистров 7 и 8 через коммутаторы 9 и 10 подаются значения двух чисел г-го такта. При умножейии чисел, выраженных смешанными дробями или це- лъо4И числами в любой комбинации, включая и правильные дроби, младшую часть произведения получают на выходах. Младшая часть произведения выдается .с первого по г-й такт .

произведения выдается по шинам 23 начиная с (г+1)-го такта. Таким образом, при перемножении двух произвольных трехразрядных чисел три мпадших разряда выдаются по шинам 24, а три старших - по шинам 23. Порядок произведения определяется по значениям порядков сомножителей, а величина

цикла определяется по числу с большей разрядностью. При получении млад- .шей и старшей частей произведения значёние пшныЗЗ должно быть раэ но нулю, ч ем производится отключение кр ррекции.

Неиспользуемые основания 2,3, 4,5 можно реализовать через другие основания, кратные данным по степеням. Так основания 2, 4 через основания 8, 16... Основания 3 и 5 через основания 9 и 25 , только в этом случае требуется прямое перекодирование разрядов произведения, так как в устройстве все основания кодируются в двоичном коде. Формула изобретения

1. Последовательное множительное устройство, содержащее два регистра сомножителей, регистры хранения поразрядных сумм и поразрядных переносов, два буферных регистра, три коммутатора, выходной сумматор, два триггера знака, блок формирования частичных произведений, блок суммирования, элемент памяти и блок управления, содержащий генератор тактовых импульсов, регистр сдвига, дешифратор разрядности, коммутатор разрядности, JK-триггер и элемент ИЛИ, причем выход генератора тактовых импульсов соединен с тактовыми входами регистра сдвига и JK-триггера, входы первого и второго сомножителей устройства являются информационными входами первых разрядов первого и второго регистров сомножителей соответственно, вход кода разрядности устройства является входом дешифратора разрядности, выход которого соединен с управляющим входом коммутатора разрядности и управляющими входами первого и второго коммутаторов, вход начальной установки устройства соединен с R-входом JK-триггера, инверсный выход которого соединен с входами установки в О регистра сдвига и с 2-го по г-й разрядов (где г - раз

рядность сомножителей) первого и вто-45 является выходом знака произведения рого регистров сомножителей, регист- устройства, вход кода основания устров хранения подразрядных сумм и переносов, первого триггера знака и является первым входом синхронизации устройства, вход запуска устройства соединен с J-входом JK-триггера, вход внешней синхронизации устройства соединен с первым входом элемента ИЛИ, второй вход которого соединен с

ройства соединен с входом дешифратора основания системы счисления и с входом кода основания выходного, суммато- 50 ра, выход третьего коммутатора является выходом младшей части произведения устройства, при этом в блок управления введен элемент ИЛИ-НЕ, а блок формирования частичных произвевыходом коммутатора разрядности и яв- 55 дений содержит группу умножителей, а ляется вторым выходом синхронизации блок суммирования содержит группу устройства, выход элемента ИЛИ соеди- узлов суммирования, выход первого иен с К-входом JK-триггера, с входа- разряда регистра первого сомножителя ми разрешения записи первого и второ- соединен с входами первого сомножи3074556

го буферных регистров и второго триггера знака и входом установки в О элемента памяти, группа выходов регистра сдвига соединена с группой ин- формационных входов, выходы поразрядных переносов блока суммирования соединены с информационными входами регистра хранения поразрядных сумм и первого буферного регистра, выход ко10 торого соединен с информационным входом первого коммутатора, выход которого соединен с входом первого слагаемого выходного сумматора, вход второго слагаемого которого соединен с

f5 выходом второго коммутатора, информационный вход которого соединен с выходом второго буферного регистра, информационный вход которого соединен с информационными входами третьего ком20 мутатора и регистра хранения поразрядных сумм, Z-й разряд информационного входа которого (где ,...,г) соединены с выходами (Р-1)-го разряда поразрядной суммы блока суммиро2;5 вания, выход переноса выходного сумматора соединен с информационным входом элемента памяти, выход которого соединен с входом переноса выходного сумматора, выход суммы которого яв30 ляется выходом старшей части произведения устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем перестройки основания системы

ас счисления, в него введены сумматор по модулю два и дешифратор основания системы счисления, причем входы знаков первого и второго сомножителей являются первым и вторым входами сум40 матора по модулю два, выход которого соединен с информационным входом первого триггера знака, выход которого соединен с информационным входом второго триггера знака, выход которого

ройства соединен с входом дешифратора основания системы счисления и с входом кода основания выходного, суммато- 50 ра, выход третьего коммутатора является выходом младшей части произведения устройства, при этом в блок управления введен элемент ИЛИ-НЕ, а блок формирования частичных произве7. 1307455 8

i-го умножителей труп- суммирования группы соединены сооттеля первого и пы (где ,4,,.,,2 г), выход первого разряда регистра второго сомножителя соединен с входами первого сомножителя (21+1)-го умножителя группы и входом второго сомножителя первого умножителя группы, выход К/2-го раз-ряда (где ,,..2г) регистра первого сомножителя соединен с входом второго сомножителя второго и К-го умножителей группы, выход К/2-го разряда регистра второго сомножителя соединен с входами второго сомножителя третьего и (К+1)-го умножителя группы, выход дешифратора основания системы счисления соединен с входами выбора основания системы счисления всех умножителей группы, всех узлов суммирования группы и выходного сумматора, выход старшего разряда первого умножителя группы соединен с информационным входом первого разряда регистра хранения попазрядных : сумм, входы первого и второго слагаемых р-го узла суммирования группы ( где ,4,...,г) соединены с выходами младших разрядов соответственно (2р-2)-го и (2р-1)-го умножителей группы, входы третьего и четвертого слагаемых р-го узла суммирования группы соединены с выходами старших разрядов соответственно 2р-го и (2р+1)-го умножителей группы, входы пятого и шестого слагаемых К/2-го узла суммирования группы соединены с выходами (К/2-1)-х разрядов соответственно регистров хранения поразрядных переносов и поразрядных сумм, вход первого слагаемого первого узла суммирования группы соединен с входом О устройства и входами третьего и четвертого слагаемых г-го узла суммирования группы, выходы младших разрядов первого умножителя группы Соединены с входами второго слагаемого первого узла суммирования группы, выходы младших разрядов второго умножителя группы соединены с входами первого слагаемого второго узла суммирования группы, выходы старших разрядов второго и третьего умножителей группы соединены с входами третьего и четвертого слагаемых первого узла суммирования группы, входы пятого и шестого слагаемых которого соединены с входами логического нуля устройства, входы второго, третьего и четвертого слагаемых второго узла

to

f5

20

25

ветственно с выходом младшего разряда третьего и выходами старших разрядов четвертого и пятого умножителей группы, выход (г-)-го разряда второго буферного регистра соединен с вторым информационным входом второго коммутатора, выход которого сое динен с входом коррекции выходного сумматора, группа выходов регистра сдвига соединена с группой входов элемента ИЛИ-НЕ, выход которого соединен с информационным входом регист ра сдвига и с управляющим входом третьего коммутатора, выход элемента ИЛИ соединен с входом разрешения выходного сумматора, вход отключения коррекции устройства является входом отключения коррекции выходного сумма тора, выход кода управления разрядностью которого соединен с входами блокировки узлов суммирования группы 2. Устройство по п.1, о тли ч а ю щ е е с я тем, что выходной сумма тор содержит два сумматора, коммутатор, узел образования переноса, узел коррекции, узел инверсии, D-триггер, элемент И, элемент ИЛИ и узел ограничения разрядности, причем вход раз решения выходного сумматора является информационным входом D-триггера, вы ход которого соединен с первым входо элемента И, выход которого соединен первым входом элемента ИЛИ, узел об35 разования переноса содержит шифратор узел инверсии и два сумматора, вход переноса первого сумматора узла обра зования переноса соединен с выходом элемента ИЛИ, с входом младшего разр да первого слагаемого первого сумматора выходного сумматора и входом переноса второго сумматора выходного сумматора, входы второго и третьего слагаемых которого соединены с входа ми первого и второго слагаемых соответственно второго сумматора выходного сумматора, входами первого и второго слагаемых соответственно пер вого сумматора узла образования пере носа и являются входами первого и второго слагаемых соответственно выходного сумматора, вход выбора основания системы счисления выходного сумматора является входом шифратора узла образования переноса, выход которого соединен с входсэм узла инверсии узла образования переноса, выход которого соединен с входом первого

30

40

45

50

55

o

5

0

5

ветственно с выходом младшего разряда третьего и выходами старших разрядов четвертого и пятого умножителей группы, выход (г-)-го разряда второго буферного регистра соединен с вторым информационным входом второго коммутатора, выход которого соединен с входом коррекции выходного сумматора, группа выходов регистра сдвига соединена с группой входов элемента ИЛИ-НЕ, выход которого соединен с информационным входом регистра сдвига и с управляющим входом третьего коммутатора, выход элемента ИЛИ соединен с входом разрешения выходного сумматора, вход отключения коррекции устройства является входом отключения коррекции выходного сумматора, выход кода управления разрядностью которого соединен с входами блокировки узлов суммирования группы. 2. Устройство по п.1, о тли ч а- ю щ е е с я тем, что выходной сумматор содержит два сумматора, коммутатор, узел образования переноса, узел коррекции, узел инверсии, D-триггер, элемент И, элемент ИЛИ и узел ограничения разрядности, причем вход разрешения выходного сумматора является информационным входом D-триггера, выход которого соединен с первым входом элемента И, выход которого соединен с первым входом элемента ИЛИ, узел об .

5 разования переноса содержит шифратор, узел инверсии и два сумматора, вход переноса первого сумматора узла образования переноса соединен с выходом элемента ИЛИ, с входом младшего разряда первого слагаемого первого сумматора выходного сумматора и входом переноса второго сумматора выходного сумматора, входы второго и третьего слагаемых которого соединены с входами первого и второго слагаемых соответственно второго сумматора выходного сумматора, входами первого и второго слагаемых соответственно первого сумматора узла образования переноса и являются входами первого и второго слагаемых соответственно выходного сумматора, вход выбора основания системы счисления выходного сумматора является входом шифратора узла образования переноса, выход которого соединен с входсэм узла инверсии узла образования переноса, выход которого соединен с входом первого

0

0

5

0

5

слагаемого второго узла 067 разования переноса, входы второго слагаемого и переноса которого сое- динены с выходами суммы и переноса соответственно первого сумматора уз- ла образования переноса, вход 1 устройства является входом младшего разряда второго слагаш ого второго сумматора узла образования переноса, выход переноса которого является вы- ходом переноса выходного сумматора к соединен с первым управляющим входом коьшутатора, второй управляющий вход которого соединен с выходом узла ограничения разрядности и являет- ся выходом кода управления разрядностью выходного сумматора, вход отДиаграмма умноже

Примечание. Сдвиг на два Р-ичных разряда

вправо на диаграмме показан смещением углов с каждым тактом влево на два разряда.

ключения коррекции которого является вторым входом элемента И, третий вход которого соединен с выходом узла коррекции, вход коррекции которот го является входом коррекции выходного сумматора, вход выбора основа- ння системы счисления которого соединен с входом кода основания узла, коррекции, вход переноса выходного сумматора является вторым входом элемента ИЛИ, выходы суммы первого и второго сумматоров выходного сумматора соединены с первым и вторым ин- формацонньми входами коммутатора , выход суммы которого является выходом суммы выходного суммаТо- ра.

Фиг. 5

Фигл

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

Изобретение относится к вычислительной технике и предназначено для умножения синхронно поступающих младшими разрядами вперед чисел, выраженных в различных Р-нчных системах счисления, Целью изобретения является расширение функциональных воз 40 / J9 |1 т: г (Л Ч ел :л

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Параллельно-последовательное множительное устройство | 1982 |

|

SU1156065A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| . | |||

Авторы

Даты

1987-04-30—Публикация

1985-09-03—Подача