Изобретение относится к вычислительной технике и может использоваться для обмена информацией между ЭВМ и периферийными устройствами,,

Целью изобретения является повышение быстродействия обмена информацией

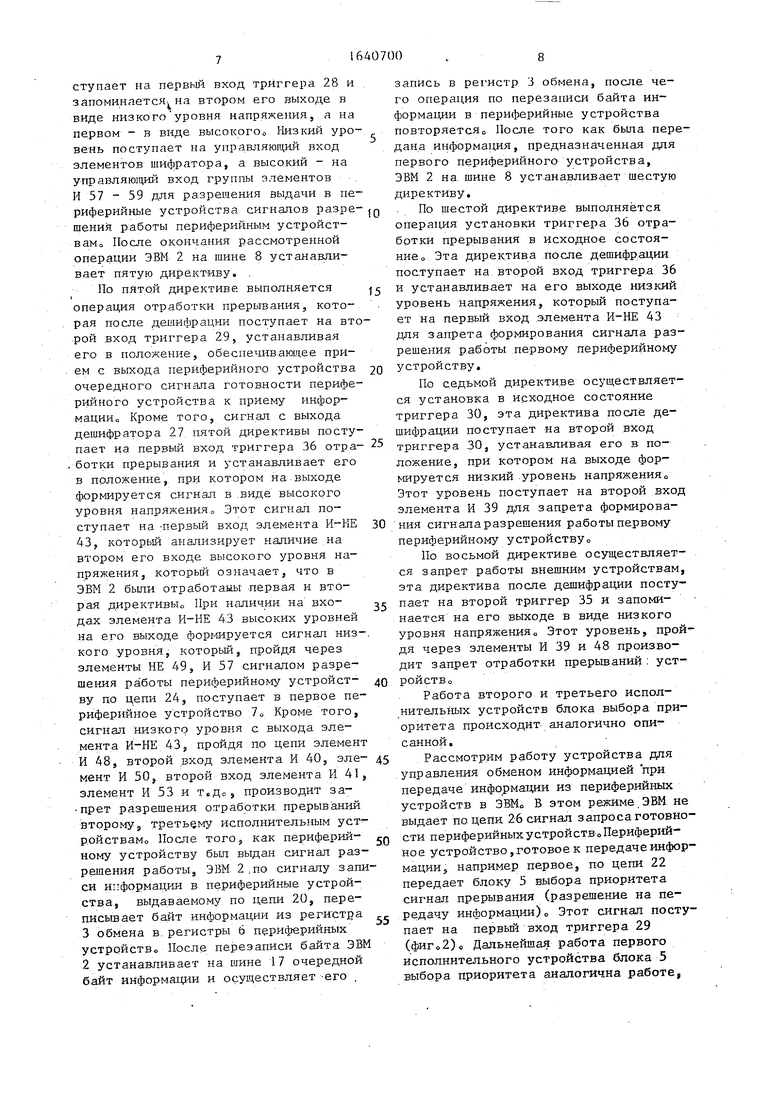

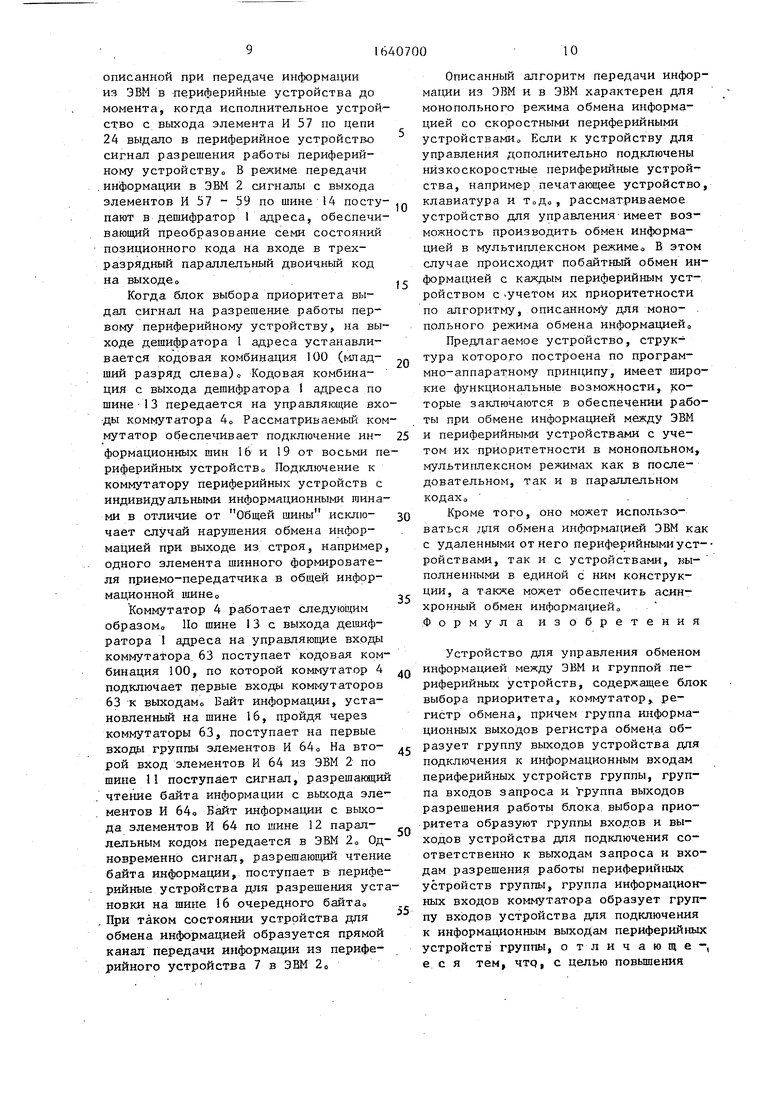

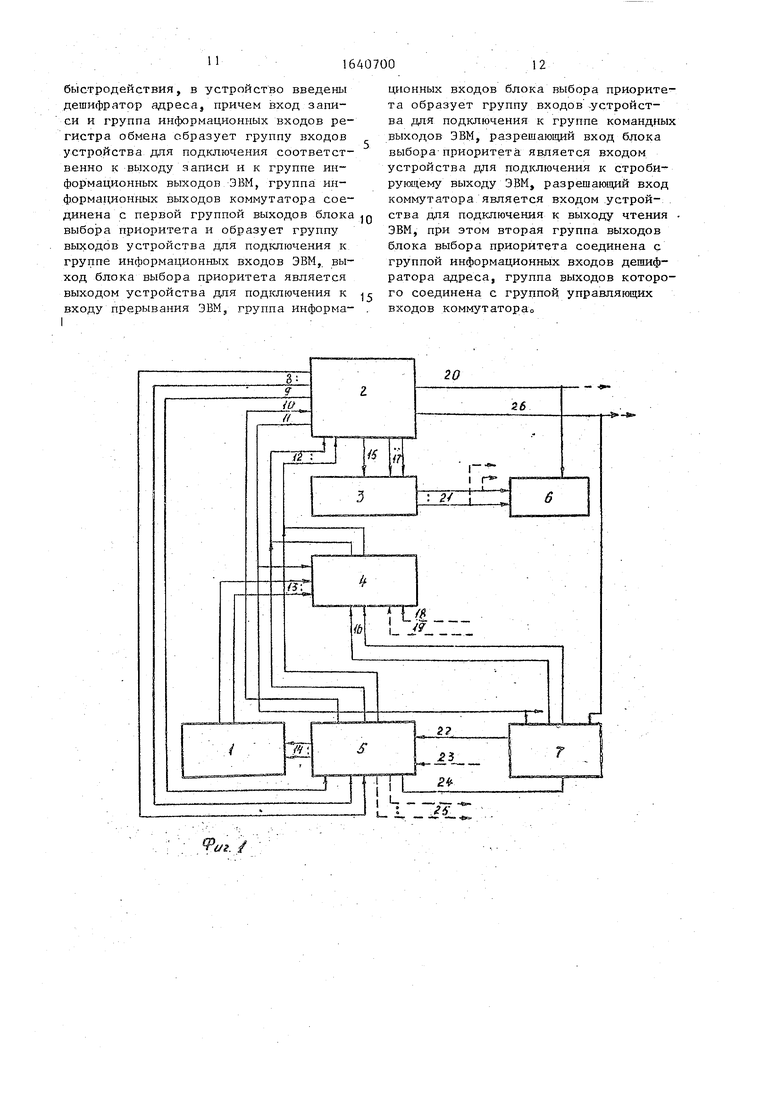

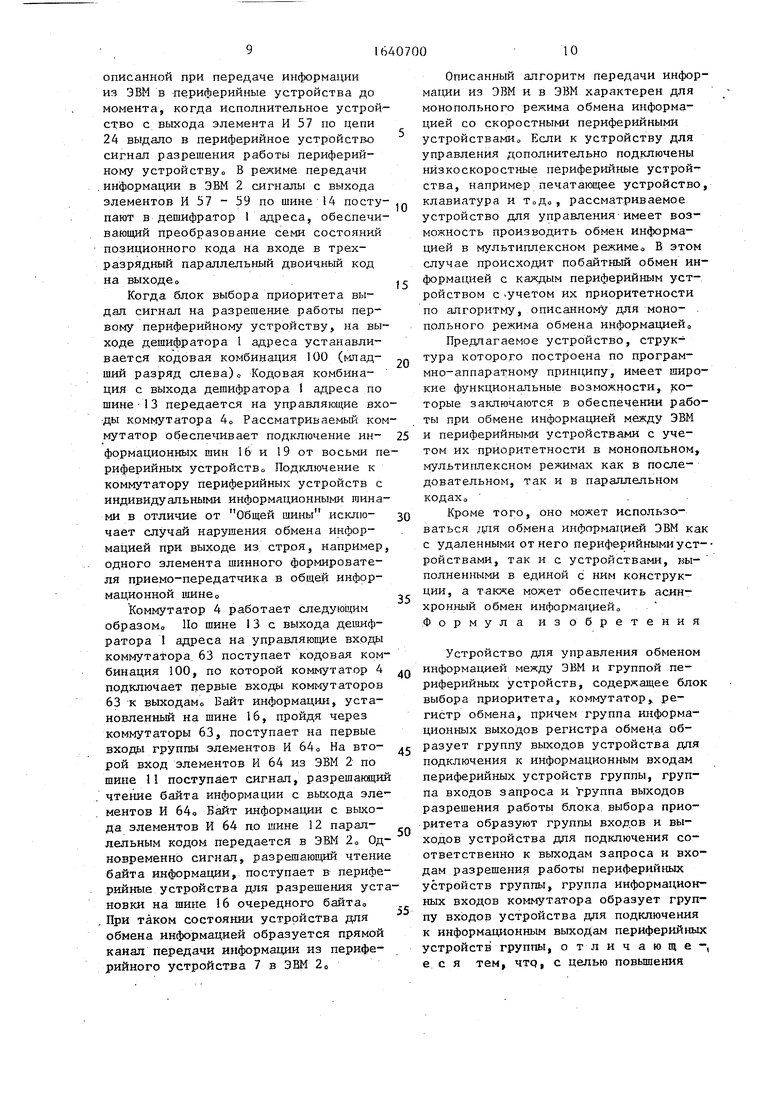

На фиг представлена блок-схема устройства (связи показаны только для одного периферийного устройства)j на- фиг„2 - функциональная схема блока выбора приоритета; на фиг03 - функциональная схема коммутатора

Устройство (фиг,) содержит дешифратор 1 адреса, ЭВМ 2, регистр 3 обмена, коммутатор 4, блок 5 выбора приоритета, периферийный регистр 6, периферийное устройство 7, параллельную шину 8 кода числа, цепь 9 сигнала стробирования, цепь 10 прерываний, цепь 11 чтения информации, информационную шину 12 параллельного обмена, внутренние шины 13 и 14, цепь 15 записи информации, шины 16 - 19 обмена

информацией, цепь 20 записи информации, информационную шину 21 параллельного обмена информацией, цепь 22 запроса, группу цепей 23 запросов, цепь

24разрешения работы, группу цепей

25разрешения работы, информационную шину 26 параллельного обмена информацией о

Блок 5 (фиг.2) содержит дешифратор 27, группу триггеров 28 - 38, элементы И 39 - 4, элементы И-НЕ 42 - 47, элемент И 48, элемент НЕ 49, элементы И 50 и 51, элемент НЕ 52, элементы И 53 и 54, элемент НЕ 55, элемент И-НЕ 56, элементы И 57 и 59 и элементы И 60 - 62.

Коммутатор (фиГоЗ) содержит группы коммутаторов 63 и элементов И 640

Устройство по своему построению представляет собой иерархическую структуру К первому уровню иерархии относится ЭВМ 2, которая является ведущим по отношению к периферийным уст,- ройствам, к второму уровню иерархии

SS

(/

j

относятся дешифратор 1 адреса, коммутатор 4 и блок 5 выбора приоритета, который является исполнительным устройством по организации обмена информацией между ЭВМ 2 и периферийными - устройствами 7 К третьему уровню иерархии относятся: регистр 3 обмена, периферийные регистры 6 и их внеш10

20

ние устройства 7, каждый из которых имеет свой приоритете Обмен информацией между ЭВМ и внешними устройствами осуществляется по программе, состоящей из подпрограмм, каждая из которых управляет обменом информацией . только с внешним устройством соответствующего приоритета,. Данное устройство может обеспечивать обмен информацией между ЭВМ и периферийными устройствами .битами, байтами или массивами как в последовательном, так и в параллельном коде В качестве примера рассматривается подключение к ЭВМ для обмена информацией трех периферийных устройств 7 (на фиг01 показано 25 только одно), первое из которых имеет высший приоритет, а третье - низший. Каждое периферийное устройство имеет свои индивидуальные цепи за- проса0 Для первого устройства это цепь 22, с помощью которой периферийное устройство подключено к одному из входов триггера 29, для второго и третьего периферийных устройств - цепи, входящие в группу цепей 23, которыми периферийные устройства подключены к триггерам 31 и 33 соответственно блока 5 выбора приоритета0 По своей организации структуру блока 5

30

35

выбора приоритета условно можно пред4

ставить в виде ряда исполнительных устройств, каждое из которых управляет обменом информацией между ЭВМ и периферийным устройством только одного приоритета,,

Первое исполнительное устройство так же, как и первое периферийное устройство, имеет высший приоритете В состав данного устройства входят следующие олементб : триггер 29 запроса запоминания от периферийного устройства, триггер 30 разрешения обработки прерываний, триггер ЗЬ обработки прерываний, элементы И 39, 48 и 57, элементы И-НЕ 42 и 43, элемент НЕ 49„ В состав второго исполнительного устройства входят элементы: триггеры 31, 32 и 37, имеющие то же назначение, что и в первом устройстве, элементы

5

0

0

0

5

0

5

0

И 40, 50, 51 и 58, элементы И-НЕ 44 и 45, элемент НЕ 52 0 В состав третьего исполнительного устройства входят элементы: триггеры 33, 34 и 38, элементы И 41, 53, 54 и 59, элементы И-НЕ 46 и 47, элемент НЕ 55 „ Следует отметить, что структурная схема блока выбора приоритета построена аппаратно таким образом, что при работе исполнительного устройства высшего приоритета происходит запрет работы исполнительным устройствам низшего приоритета,, Кроме того, в состав блока выбора приоритета входят элементы, которые являются общими для всех исполнительных устройств К таким элементам относится дешифратор 27 директив кода числа, триггер 28 разрешения (запрета) формирования вектора прерывания, триггер 35 разрешения (запрета) работы периферийных устройств, элемент И-НЕ 56, формирующий сигнал прерывания, элементы И 60 - 62, с помощью которых происходит формирование векторов прерываний,,

Устройство работает следующим образ ОМ0

Инициатором передачи информации в периферийные устройства является ЭВМ, которая по цепи 26 передает всем периферийным устройствам сигнал запроса готовности Периферийные устройства, получив данный сигнал, при готовности к приему информации передают по индивидуальным цепям 22 и 23 запроса в блок выбора приоритета сигнал запроса готовности периферийных устройств, где он запоминается на триггерах 29, 31 и 33 ()0 ЭВМ в это время устанавливает на шине 17 байт информации в параллельном коде и по сигналу,передаваемому по цепи 15, производит его запись в регистр 3 обмена0 Байт информации с выхода регистра по шине 21 одновременно ларал- лельным кодом передается на входы всех периферийных регистров0 Информацию с выхода периферийного регистра воспринимает только то устройство,которому из блока 5 выбора приоритета по индивидуальным цепям 24 и 25 поступил сигнал, разрешающий работу соответствующему периферийному устройству о

Пример, Работа блока 5 выбо-{ ра приоритета по формированию сигнала разрешения работы первому устройству 7, имеющему высший приоритет,,

для которого ЭВМ подготовила инфор- - мацию для передачио

Формирование сигнала разрешения работы периферийному устройству бло- ком выбора приоритета осуществляется по программе, записанной в ЗУ ЭВМ 20 Программа состоит из подпрограммо Каждая подпрограмма содержит последовательность директив, с помощью которых происходит управление работой соответствующего исполнительного устройства блока 5 выбора приоритета,, Количество подпрограмм, как и количество исполнительных устройств в блоке 5 выбора приоритета, однозначно определяется количеством подключенных периферийных устройств.

ЭВМ 2, выполняя первую подпрограмму управления исполнительным устройством, по шине 8 передает на вход дешифратора 27 (фигс-2) последовательность директивt на разрешающий вход по цепи 9 - управляющий сигнал, разрешающий дешифрацию кодов этих директив о При наличии разрешающего сигнала дешифратор 27 производит дешифрацию кодов директив, формируя на соответствующем выходе сигнал микрооперации 0 Сигналы с выходов дешифратора 27 с помощью линий связи подключены к входам исполнительных элементов функциональной схемы блока 5 выбора приоритетов (фиг02)0

По первой директиве выполняется операция разрешения работы всем периферийным устройствам, которая после дешифрации поступает на первый вход триггера 35 и запоминается на его выходе в виде высокого уровня напряжения (двоичная 1)0 Этот уровень поступает на первые входы элементов И 39 и 48.

По второй директиве выполняется операция разрешения обработки прерывания первому исполнительному устройству, которая после дешифрации поступает на первый вход триггера 30 и запоминается на его выходе в виде высокого уровня напряженияо Этот уровень поступает на второй вход элемента И 39 з который производит анализ поступления высоких уровней напряжения на входах,, Если условие выполняется, на выходе формируется высокий уровень напряжения, который поступает на один из выходов элемента И-НЕ 42 и второй вход элемента И-НЕ 43„

0

Элемент И-НЕ 42 производит анализ наличия на втором его входе поступления с. выхода триггера 29 высокого уровня напряжения сигнала готовности ( периферийного устройства 7 для приема информации,, Этот сигнал поступает от периферийного устройства 7 (при его готовности к приему информации)

по цепи 22 на первый вход триггера 29 и запоминается на его выходе в виде высокого уровня напряжения При наличии на входах элемента И-НЕ 42 высоких уровней напряжения на его выходе формируется сигнал в виде низкого уровня напряжения (двоичный О), который, пройдя по цепи первый вход элемента И-НЕ 44, элемент И 51, первый вход элемента И-НЕ 46, элемент И 54 и т„До, осуществляет запрет формирования сигнала разрешения работы второму, третьему и т„д0 периферийным устройствам Одновременно низкий уровень напряжения с выхода элемен- 5 та И-НЕ 42, пройдя элемент И-НЕ 56 по цепи 10 сигналом прерывания от внешнего устройства, поступает в ЭВМ 2, а-также на группу элементов И-НЕ 60 - 62, выполняющих функции шифратора, для формирования вектора прерывания (номера) первого периферийного устройства 7 о ЭВМ 2, получив сигнал прерывания, устанавливает на шине 8 третью директиву

0

По третьей директиве выполняется операция разрешения формирования вектора прерывания, которая после дешифрации поступает на второй вход триггера 28 и запоминается на его втором выходе в виде высокого уровня напряжения,, Этот уровень поступает на управляющие входы группы элементов И 60 - 62 для разрешения формирования вектора прерыванияа Вектор прерывания с выхода шифратора по информационной шине 12 поступает в ЭВМ 20 Последняя по результатам анализа данного вектора определяет, какое периферийное устройство готово для приема информации (в данном случае - первое) о После окончания операции анализа векторам прерывания ЭВМ 2 на шине 8. устанавливает четвертую директиву,,

По четвертой директиве выполняется операция запрета формирования вектора прерывания и разрешения выдачи сигналов разрешения работы внешних устройств, которая после дешифрации по-

ступает на первый вход триггера 28 и запоминается на втором его выходе в виде низкого уровня напряжения, а на первом - в виде высокого Низкий уровень поступает на управляющий вход элементов шифратора, а высокий - на управляющий вход группы элементов И 57 - 59 для разрешения выдачи в периферийные устройства сигналов разрешения работы периферийным устройствам После окончания рассмотренной операции ЭВМ 2 на шине 8 устанавливает пятую директиву.

По пятой директиве выполняется операция отработки прерывания, которая после дешифрации поступает на второй вход триггера 29, устанавливая его в положение, обеспечивающее прием с выхода периферийного устройства очередного сигнала готовности периферийного устройства к приему информации Кроме того, сигнал с выхода дешифратора 27 пятой директивы поступает на первый вход триггера 36 отра- ботки прерывания и устанавливает его в положение, при котором на выходе формируется сигнал в виде высокого уровня напряжения о Этот сигнал поступает на -первый вход элемента И-НЕ 43, который анализирует наличие на втором его входе высокого уровня напряжения, который означает, что в ЭВМ 2 были отработаны первая и вторая директивы,. При наличии на вхо- дах элемента И-НЕ 43 высоких уровней на его выходе формируется сигнал низкого уровня, который, пройдя через элементы НЕ 49, И 57 сигналом разрешения работы периферийному устройст- ву по цепи 24, поступает в первое периферийное устройство 7о Кроме того, сигнал низкого уровня с выхода элемента И-НЕ 43 s пройдя по цепи элемент И 48, второй вход элемента И 40, эле- мент И 50, второй вход элемента И 41, элемент И 53 и твдс, производит за- прет разрешения отработки прерываний второмуs третьему исполнительным устройствам После того, как периферий- ному устройству был выдан сигнал разрешения работы3 ЭВМ 2 по сигналу записи информации в периферийные устройства j выдаваемому по цепи 20, переписывает байт информации из регистра 3 обмена в регистры 6 периферийных устройств. После перезаписи байта ЭВМ 2 устанавливает на шине 17 очередной байт информации и осуществляет его .

Q

c 05 30 35 0 45 д

5

запись в регистр 3 обмена, после чего операция по перезаписи байта информации в периферийные устройства повторяетсяо После того как была передана информация, предназначенная для первого периферийного устройства, ЭВМ 2 на шине 8 устанавливает шестую директиву.

По шестой директиве выполняется операция установки триггера 36 отработки прерывания в исходное состояние Эта директива после дешифрации поступает на второй вход триггера 36 и устанавливает на его выходе низкий уровень напряжения, который поступает на первый вход элемента И-НЕ 43 для запрета формирования сигнала разрешения работы первому периферийному устройству.

По седьмой директиве осуществляется установка в исходное состояние триггера 30, эта директива после дешифрации поступает на второй вход триггера 30, устанавливая его в положение, при котором на выходе формируется низкий уровень напряжения0 Этот уровень поступает на второй вход элемента И 39 для запрета формирования сигнала разрешения работы первому периферийному устройству0

По восьмой директиве осуществляется запрет работы внешним устройствам, эта директива после дешифрации поступает на второй триггер 35 и запоминается на его выходе в виде низкого уровня напряжения Этот уровень, пройдя через элементы И 39 и 48 производит запрет отработки прерываний устройств

Работа второго и третьего исполнительных устройств блока выбора приоритета происходит аналогично описанной.

Рассмотрим работу устройства для управления обменом информацией при передаче информации из периферийных устройств в ЭВМ0 В этом режиме ЭВМ не выдает по цепи 26 сигнал запроса готовности периферийных устройств о Периферийное устройство,готовое к передаче информации , например первое, по цепи 22 передает блоку 5 выбора приоритета сигнал прерывания (разрешение на передачу информации)„ Этот сигнал поступает на первый вход триггера 29 (), Дальнейшая работа первого исполнительного устройства блока 5 выбора приоритета аналогична работе,

описанной при передаче информации из ЭВМ в периферийные устройства до момента, когда исполнительное устройство с выхода элемента И 57 по цепи 24 выдало в периферийное устройство сигнал разрешения работы периферийному устройствуо В режиме передачи информации в ЭВМ 2 сигналы с выхода элементов И 57 - 59 по шине 14 поступают в дешифратор 1 адреса, обеспечивающий преобразование семи состояний позиционного кода на входе в трехразрядный параллельный двоичный код на выходео

Когда блок выбора приоритета выдал сигнал на разрешение работы первому периферийному устройству, на выходе дешифратора 1 адреса устанавливается кодовая комбинация 100 (младший разряд слева)о Кодовая комбинация с выхода дешифратора 1 адреса по шине 13 передается на управляющие входы коммутатора 40 Рассматриваемый коммутатор обеспечивает подключение информационных шин 1Ь и 19 от восьми периферийных устройство Подключение к коммутатору периферийных устройств с индивидуальными информационными тинами в отличие от Общей шины исключает случай нарушения обмена информацией при выходе из строя, например, одного элемента шинного формирователя приемо-передатчика в общей информационной шине о

Коммутатор 4 работает следующим образомо Но шине 13 с выхода дешифратора 1 адреса на управляющие входы коммутатора 63 поступает кодовая комбинация 100, по которой коммутатор 4 подключает первые входы коммутаторов 63 к выходам0 Байт информации, установленный на шине 16, пройдя через коммутаторы 63, поступает на первые входы группы элементов И 640 На второй вход элементов И 64 из ЭВМ 2 по шине 11 поступает сигнал, разрешающий чтение байта информации с выхода элементов И 64о Байт информации с выхода элементов И 64 по шине 12 параллельным кодом передается в ЭВМ 20 Одновременно сигнал, разрешающий чтение байта информации, поступает в периферийные устройства для разрешения установки на шине 16 очередного байта, При таком состоянии устройства для обмена информацией образуется прямой канал передачи информации из периферийного устройства 7 в ЭВМ 2о

0

5

0

5

0

5

0

5

0

Описанный алгоритм передачи информации из ЭВМ и в ЭВМ характерен для монопольного режима обмена информацией со скоростными периферийными устройствами. Если к устройству для управления дополнительно подключены низкоскоростные периферийные устройства, например печатающее устройство, клавиатура и ТоД0, рассматриваемое устройство для управления имеет возможность производить обмен информацией в мультиплексном режиме0 В этом случае происходит побайтный обмен информацией с каждым периферийным устройством с .учетом их приоритетности по алгоритму, описанному для монопольного режима обмена информацией„

Предлагаемое устройство, структура которого построена по программно-аппаратному принципу, имеет широкие функциональные возможности, которые заключаются в обеспечении работы при обмене информацией между ЭВМ и периферийными устройствами с учетом их приоритетности в монопольном, мультиплексном режимах как в последовательном, так и в параллельном кодахо

Кроме того, оно может использоваться для обмена информацией ЭВМ как с удаленными от него периферийными уст- ройствами, так и с устройствами, выполненными в единой с ним конструкции, а также может обеспечить асинхронный обмен информациейо Формула изобретения

Устройство для управления обменом информацией между ЭВМ и группой периферийных устройств, содержащее блок выбора приоритета, коммутатор,. регистр обмена, причем группа информационных выходов регистра обмена образует группу выходов устройства для подключения к информационным входам периферийных устройств группы, группа входов запроса и группа выходов разрешения работы блока выбора приоритета образуют группы входов и выходов устройства для подключения соответственно к выходам запроса и вхо- дам разрешения работы периферийных устройств группы, группа информационных входов коммутатора образует группу входов устройства для подключения к информационным выходам периферийных устройств группы, отличающе-, е с я тем, чтр, с целью повышения

быстродействия, в устройство введены дешифратор адреса, причем вход записи и группа информационных входов регистра обмена образует группу входов устройства для подключения соответственно к выходу записи и к группе информационных выходов ЭВМ, группа информационных выходов коммутатора соединена с первой группой выходов блока выбора приоритета и образует группу выходов устройства для подключения к группе информационных входов ЭВМ, выход блока выбора приоритета является выходом устройства для подключения к входу прерывания ЭВМ, группа информа- I

ционных входов блока выбора приоритета образует группу входов устройства для подключения к группе командных выходов ЭВМ, разрешающий вход блока выбора приоритета является входом устройства для подключения к строби- рующему выходу ЭВМ, разрешающий вход коммутатора является входом устройства для подключения к выходу чтения . ЭВМ, при этом вторая группа выходов блока выбора приоритета соединена с группой информационных входов дешифратора адреса, группа выходов которого соединена с группой управляющих входов коммутаторао

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обменом информацией между ЭВМ и группой периферийных устройств | 1989 |

|

SU1711170A2 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство приоритетных прерываний | 1990 |

|

SU1741134A1 |

| Устройство для сопряжения электронных вычислительных машин | 1981 |

|

SU1013938A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения электронной вычислительной машины с абонентами | 1976 |

|

SU642701A1 |

| Устройство для обмена информацией между процессором и абонентами | 1987 |

|

SU1444792A1 |

Изобретение относится к вычислительной технике и может использоваться для обмена информацией между ЭВМ и периферийными устройствами., Целью изобретения является повышение быстродействия Устройство содержит дешифратор адреса, блок выбора приоритета, коммутатор, регистр обмена, 3 ил„

№.

W

#:

Фиг /

26

#

)7

16

ТОЛ

L J

г

J&,

2

1

L« jz

| Система для обмена данными управляющей вычислительной машины с периферийными устройствами | 1972 |

|

SU490115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-07—Публикация

1988-02-15—Подача