Фиг.1

10

15

20

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах для преобразования последовательных ко- дов, изменяющих порядок следования разрядов

Цель изобретения - расширение области применения устройства за счет замены одних разрядов последовательного кода другими.

На фиг0 1 представлена структурная схема устройства; на фигс 2 - временная диаграмма его работы,,

Устройство содержит (n-Н) -разрядный счетчик 1 импульсов, схему 2 сравнения, мультиплексор 3, блок 4 оперативной памяти,триггер 5,элемент б запрета, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, формирователь 8 импульсов, информационный вход 9, первые установочные входы 10, тактовый вход 11, сбросовый вход 12$ вторые установочные входы t3 и выход 14 устройства

Формирователь 8 импульсов содержит 25 три элемента НЕ 15, элемент И 16 и три элемента НЕ 17 „ Элементы НЕ 15 инвертируют и задерживают тактовый импульс на время Ј3 (фиг„2 г) , при этом на выходе элемента И 16 появляется импульс с длительностью Q (фиго 2д)„ Элементы НЕ 17 инвертируют и задерживают импульс с выхода элемента И 16 на время Јп (фиг.2е). При использовании микросхем серии К-|55 формирователь вырабатывает ин версный. импульс длительностью 60-90 нс5 задержанный относительно переднего фронта тактового сигнала на 80- 120 не,40

На тактовый вход 11 поступают импульсы с периодом Т На вход 9 устройства поступает входной М-раэрядный код с частотой смены разрядов 1/Т0 Изменение разрядов кода должно проис- 45 ходить при паузе тактового сигнала на входе 11. На вход 12 подается стробирующий импульс произвольной длительности, размещенный на временной оси перед первым разрядом входного кода При непрерывной подаче на вход 9 последовательных N-разряд- ных кодов, где N 2п, стробирующий импульс на вход 12 достаточно подать один раз перед подачей первого кода На входы 10 поступает n-разрядный па раллельный код номера заменяющего разряда. Например, если в коде на место 5-го разряда нужно поставить 7-й

,35

50

10

15

20

25 с5 40

45 35

50

55

разряд, то на входы 10 нужно подать код 7, а на входы 13 - код 5,

Устройство работает следующим образом.

После включения на вход 12 подается импульсный сигнал, а на вход 9 - входной последовательный код„ Состояние счетчика 1 начинает изменяться по заднему фронту тактовых сигналов„ При единичном тактовом сигнале осуществляется запись информации в блок 4 оперативной памяти под действием импульсных инверсных сигналов с формирователя 80 В паузе тактового сигнала производится считывание информации из блока 4 в триггер 5 передним фронтом тактового сигнала (триггер 5 имеет динамический стробирующий вход). Цикл работы устройства, равный 2П-И тактам, делится на два подцикла. В первом подцикле старший разряд счетчика 1 нулевой, а во втором единичный Блок 4 оперативной памяти состоит из двух частей по 2 ячеек памяти в каждойс В первом подцикле запись осуществляется во вторую половину блока 4, а во втором - в первую половину, так как в первом подцикле при действии сигнала записи на старший адресный вход блока 4 подается с элемента 7 единичный сигнал, а во втором подцикле - нулевой,, Младшие n-адресные входы блока 4 формируются следующим образом.

Если сигнал на выходе элемента 6 нулевой, то через мультиплексор 3 пропускается двоичный изменяющийся код с выхода счетчика 1, если единичный - то двоичный код номера заменяющего разряда. Единичный сигнал на выходе элемента 6 появляется при нулевом тактовом сигнале и единичном сигнале на выходе схемы 2 сравнения, Таким образом, при записи последовательного кода в блок 4 сигнал на выходе элемента 6 всегда нулевой и поэтому запись осуществляется в 2 ячеек блока 4 последовательно, начиная с младших адресов, T«et в первую ячейку записывается первый разряд, во вторую - второй и т.д. При считывании из блока 4 адрес или номер считываемого разряда определяется сигналом на выходе схемы 2 сравнения о Еспи этот сигнал нулевой, то разряды считываются в том же порядке, в каком они поступили на вход

устройства. Если сигнал на выходе схемы. 2 единичный, то считывается разряд с номером, равным коду на входах 10.

В зависимости от того, какой выход схемы 2 сравнения используется, могут наблюдаться следующие три режима работы устройства. Пусть код D равен номеру заменяющего разряда, код А - коду на выходе счетчика 1, а код В - номеру заменяемого разряда.

1.Единичный сигнал на выходе схемы 2 появляется при равенстве

А В. В этом случае все разряды с. блока 4 считываются в естественном порядке (т.е. в таком же порядке, в каком поступили на вход блока 4), кроме разряда с номером В, вместо которого считывается разряд с номером D.

2.Единичный сигнал на выходе схемы 2 появляется при неравенстве: . В этом случае разряды с 1-го по В-й считываются в естественном порядке, а разряды с (В-М)-го по 2п-й заменяются разрядом с номером Г

30 Единичный сигнал на выходе схемы 2 появляется при неравенстве В этом случае разряды с 1-го по (.-1)-й заменяются разрядом с номером D, а разряды с В-го по 2 -и считываются в естественном порядке,

Схемы сравнения выполняются обычно с наличием всех описанных выше выходов (например, микросхема К 134 СА), однако на схеме фиг 1 указан только один выход, который определяется выбранным режимом работы

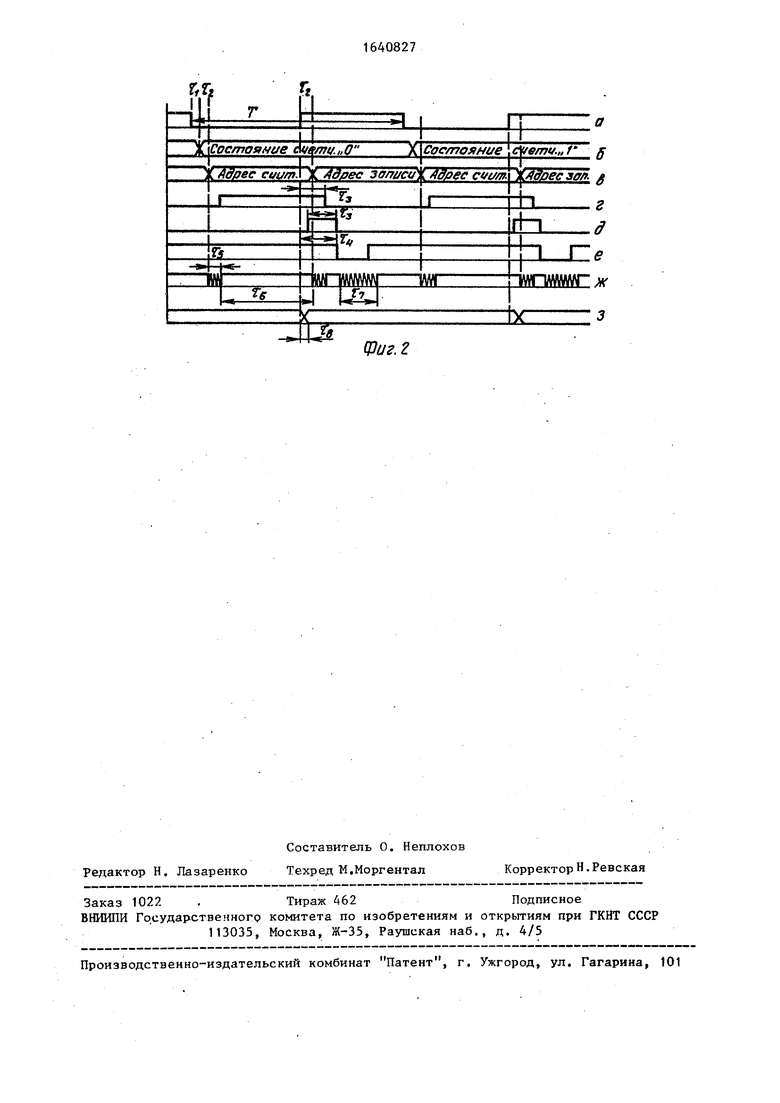

Временные диаграммы (фиг„ 2) поясняют работу устройства. На диаграмме фиг. 2а изображен тактовый сигнал на входе 11 устройства Счетчик 1 переключается от заднего фронта тактового сигнала (фиг, 26) с задержкой Ј, о Изменение адреса осуществляется с задержкой относительно фронтов тактового сигнала (фиг., 2в) „ Время определяется временем срабатывания мультиплексора 3 и элемента 7. На диаграммах фиг 2г, д, е представлены сигналы, поясняюцие работу формирователя 8„ На диаграмме фиг 2ж изображен сигнал на выходе блока 4 памяти,, В течение времени Ј$ протекают переходные процессы, связанные

с изменением адреса блока памяти. В течение времени &б осуществляется считывание информации из блока памяти о В течение времени С7 протекают переходные процессы, связанные с записью в блок памяти новой информации. На диаграмме фиг„ 2з представлен сигнал на выходе триггера 50 Время Ј равно времени переключения триггера.

5

0

5

0

5

0

5

Формула изобретения

Устройство для преобразования последовательного кода, содержащее счетчик, вход обнуления и счетный вход которого являются соответственно входом обнуления и тактовым входом устройства, блок оперативной

0 памяти, информационный вход которого является информационным входом устройства, выход блока оперативной памяти соединен с входом D-триггера, выход которого является информацион5 ным выходом устройства, и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения замены одних разрядов последовательного кода другими, в него введены формирователь, схема сравнения, элемент запрета и мультиплексор, первая группа входов которого является первыми установочными входами устройства, а выходы соединены с адресными входами младших разрядов блока оперативной памяти, первые входы схемы сравнения являются вторыми установочными входами устройства, выходы разрядов счетчика, кроме выхода старшего разряда, соединены с соответствующими вторыми входами мультиплексора и схемы сравнения, вход формирователя, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, инверсный вход элемента запрета и синхровход D-триггера объединены и подключены к тактовому входу устройства, выход схемы сравнения соединен с прямым входом элемента запрета, выход которого соединен с управляющим входом мультиплексора, выход старшего разряда счетчика соединен с вторым входом элемента ИСКЛЮ- ЧАЮЦЕЕ ИЛИ, выход которого соединен с адресным входом старшего разряда блока оперативной памяти, выход формирователя соединен с управляющим входом блока оперативной памяти.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367036A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ИНДИКАТОРА | 1991 |

|

RU2018977C1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Пульт учащегося для устройства обучения языкам | 1985 |

|

SU1354235A1 |

| Устройство для ввода информации в калькулятор | 1990 |

|

SU1791807A1 |

Изобретение относится к автоматике и может быть использовано в устройствах для преобразования последовательных кодов, изменяющих порядок следования разрядов Изобретение позволяет путем замены одних разрядов последовательного кода другими расширить область применения устройства. Устройство содержит счетчик 1 импульсов, схему 2 сравнения, мультиплексор 3, блок 4 оперативной памяти, триггер 5, элемент 6 запрета, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, формирователь 8 импульсов, содержащий элементы НЕ 15, элемент И 16 и элементы НЕ 17„ 2 ил„

| Устройство для преобразования последовательного кода в код | 1985 |

|

SU1270900A1 |

Авторы

Даты

1991-04-07—Публикация

1988-07-07—Подача