Изобретение относится к автоматике и вычислительной технике и может быть использовано для программного- управления работой исполнительных устройств и механизмов, а также специализированных ЦВМ и устройств с микропрограммным управлением.

Целью изобретения является повышение эффективности диагностики неисправностей за счет записи следов выполнения микропрограмм.

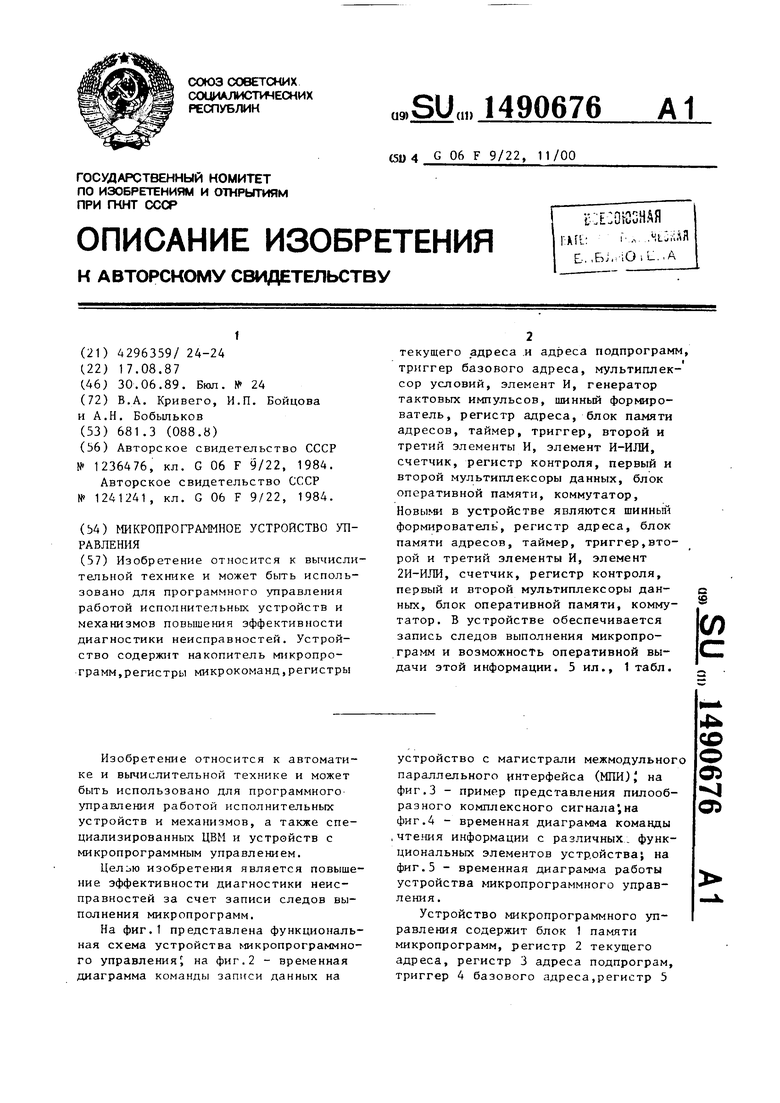

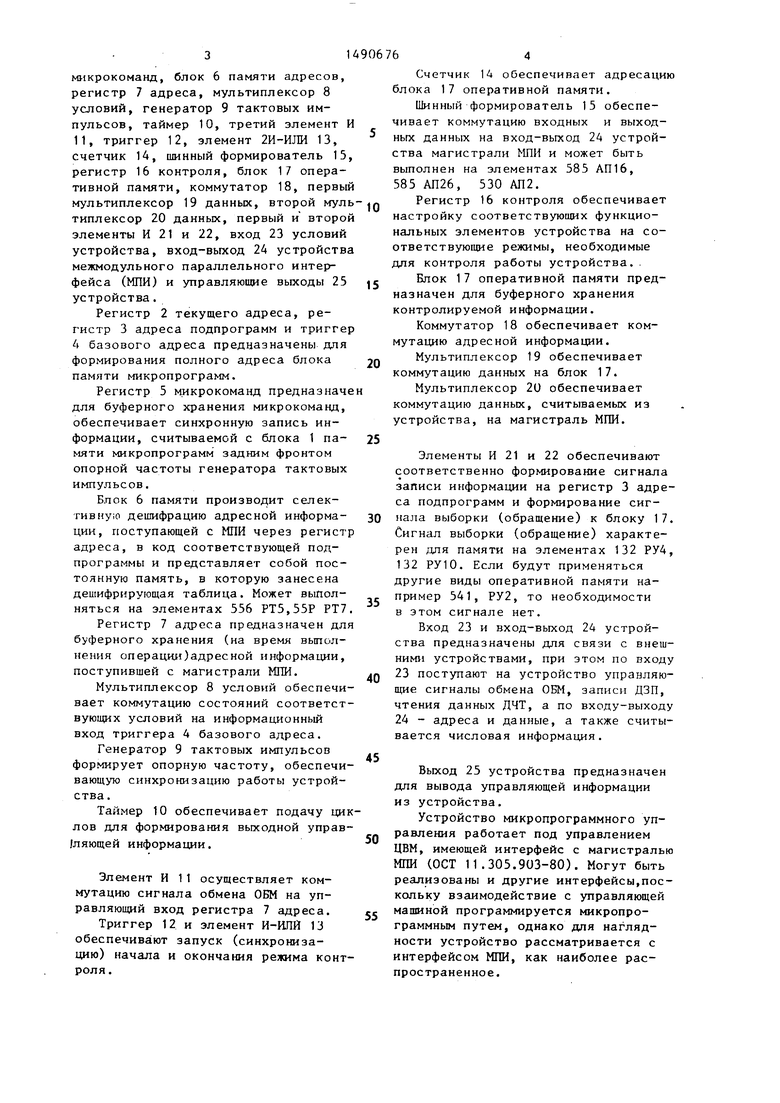

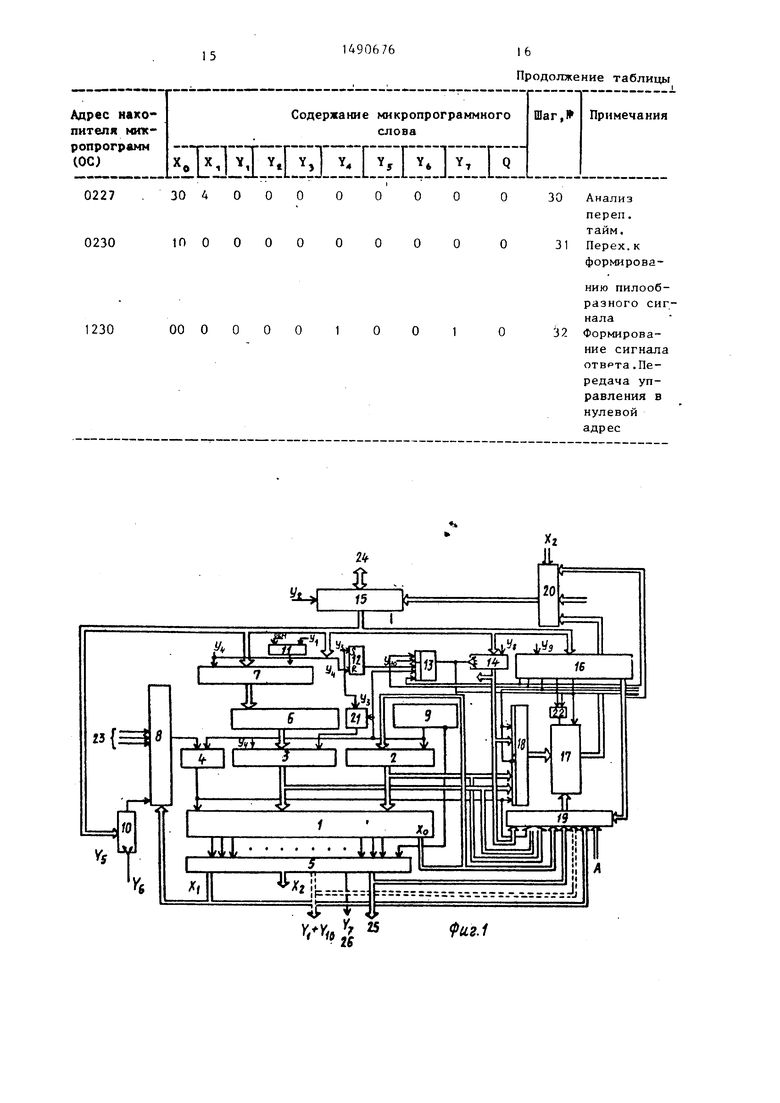

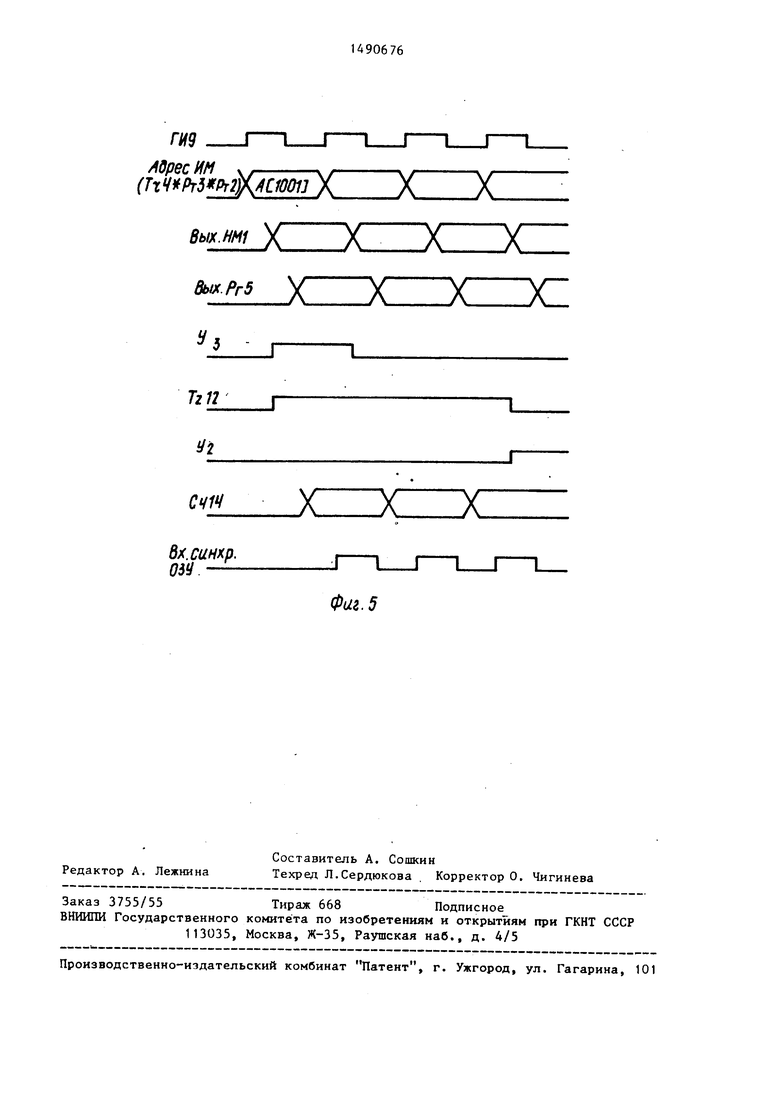

На фиг.1 представлена функциональная схема устройства микропрограммного управления5 на фиг.2 - временная диаграмма команды записи данных на

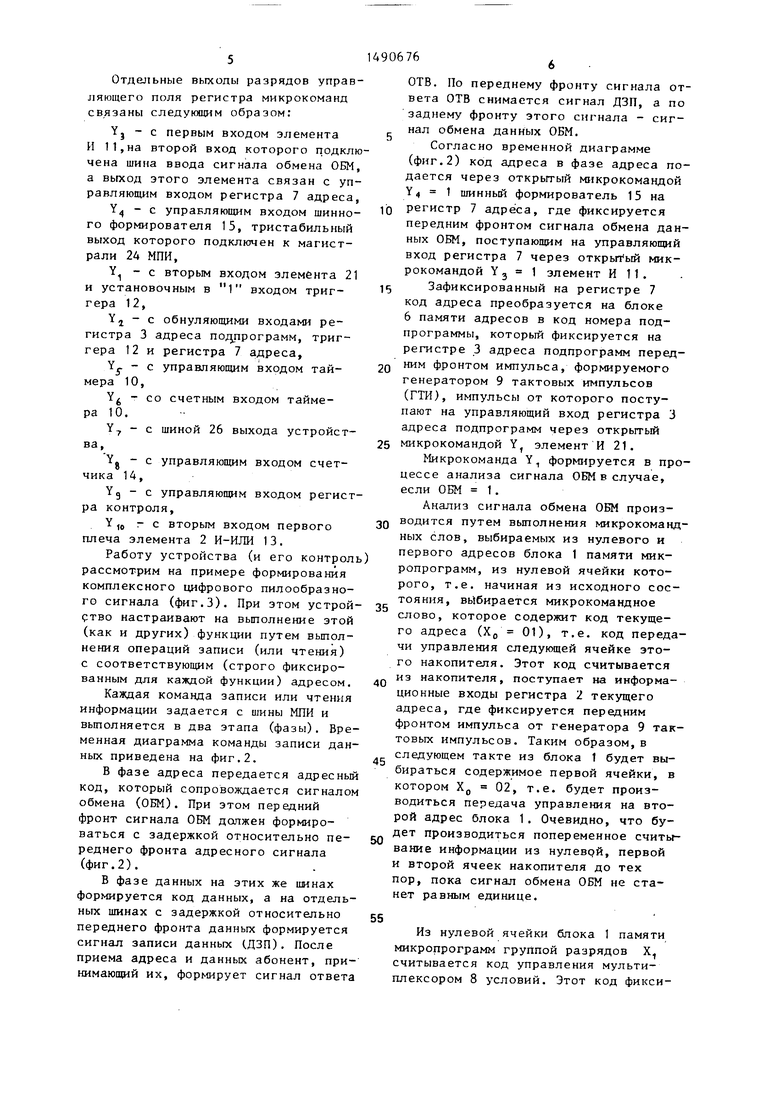

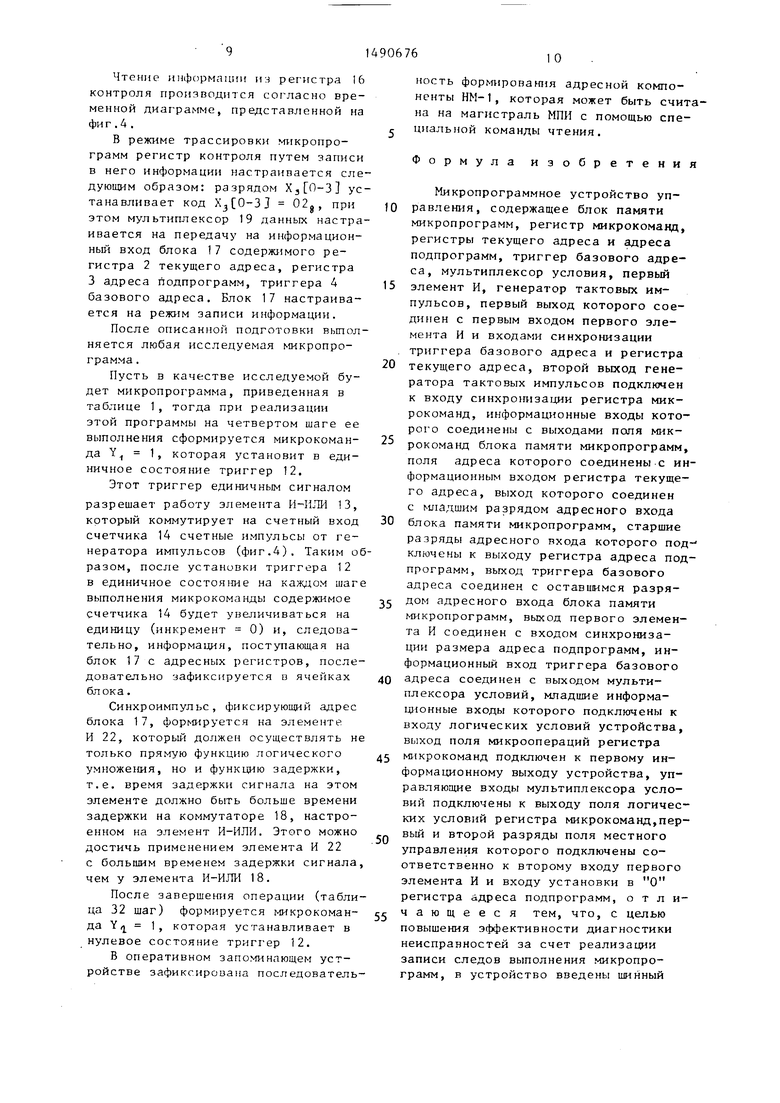

устройство с магистрали межмодульного параллельного интерфейса (МПИ)J на фиг.З - пример представления пилообразного комплексного сигнала ,на фиг.4 - временная диаграмма команды .чтения информации с различных, функциональных элементов устройства; на фиг.5 - временная диаграмма работы устройства микропрограммного управления .

Устройство микропрограммного управления содержит блок 1 памяти микропрограмм, регистр 2 текущего адреса, регистр 3 адреса подпрограм, триггер 4 базового адреса,регистр 5

4

со

о

СП)

о:

микрокоманд, блок 6 памяти адресов, регистр 7 адреса, мультиплексор 8 условий, генератор 9 тактовых импульсов, таймер 10, третий элемент И 11, триггер 12, элемент 2И-ИЛИ 13, счетчик 14, шинный формирователь 15, регистр 16 контроля, блок 17 оперативной памяти, коммутатор 18, первый мультиплексор 19 данных, второй мультиплексор 20 данных, первый и второй элементы И 21 и 22, вход 23 условий устройства, вход-выход 24 устройства межмодульного параллельного ннтер- фейса (МПИ) и управляющие выходы 25 устройства.

Регистр 2 текущего адреса, регистр 3 адреса подпрограмм и триггер 4 базового адреса предназначены для формирования полного адреса блока памяти микропрограмм.

Регистр 5 микрокоманд предназначе для буферного хранения микрокоманд, обеспечивает синхронную запись информации, считываемой с блока 1 памяти микропрограмм задним фронтом опорной частоты генератора тактовых импульсов.

Блок 6 памяти производит селективную дешифрацию адресной информации, поступающей с МПИ через регистр адреса, в код соответствующей подпрограммы и представляет собой постоянную память, в которую занесена дешифрирующая таблица. Может выполняться на элементах 556 РТ5,55Р РТ7.

Регистр 7 адреса предназначен для буферного хранения (на время выполнения операцни)адресной информации, поступившей с магистрали МПИ.

Мультиплексор 8 условий обеспечивает коммутацию состояний соответствующих условий на информационный вход триггера 4 базового адреса.

Генератор 9 тактовых импульсов формирует опорную частоту, обеспечивающую синхронизацию работы устройства.

Таймер 10 обеспечивает подачу циклов для формирования выходной управ- /ляющей информации.

Элемент И 11 осуществляет коммутацию сигнала обмена ОБМ на управляющий вход регистра 7 адреса.

Триггер 12 и элемент И-Ш1Й 13 обеспечивают запуск (синхронизацию) начала и окончания режима контроля.

н

10

15

20

25

30

35

40

45

50

55

764

Счетчик 14 обеспечивает адресацию блока 17 оперативной памяти.

Шинный формирователь 15 обеспечивает коммутацию входных и выходных данных на вход-выход 24 устройства магистрали МПИ и может быть выполнен на элементах 585 АП16, 585 АП26, 530 АП2.

Регистр 16 контроля обеспечивает настройку соответствующих функциональных элементов устройства на соответствующие режимы, необходимые для контроля работы устройства. .

Блок 17 оперативной памяти предназначен для буферного хранения контролируемой информации.

Коммутатор 18 обеспечивает коммутацию адресной информации.

Мультиплексор 19 обеспечивает коммутацию данных на блок 17.

Мультиплексор 20 обеспечивает коммутацию данных, считываемьк из устройства, на магистраль МПИ.

Элементы И 21 и 22 обеспечивают соответственно формирование сигнала записи информации на регистр 3 адреса подпрограмм и формирование сигнала выборки (обращение) к блоку 17. Сигнал выборки (обращение) характерен для памяти на элементах 132 РУ4, 132 РУ10. Если будут применяться другие виды оперативной памяти например 541, РУ2, то необходимости в этом сигнале нет.

Вход 23 и вход-выход 24 устройства предназначены для связи с внешними устройствами, при этом по входу

23поступают на устройство управляющие сигналы обмена ОБМ, записи ДЗП, чтения данных ДЧТ, а по входу-выходу

24- адреса и данные, а также считывается числовая информация.

Выход 25 устройства предназначен для вывода управляющей информации из устройства.

Устройство микропрограммного управления работает под управлением ЦВМ, имеющей интерфейс с магистралью МПИ (ОСТ 11.305.903-80). Могут быть реализованы и другие интерфейсы,поскольку взаимодействие с управляющей машиной программируется микропрограммным путем, однако для наглядности устройство рассматривается с интерфейсом МПИ, как наиболее распространенное.

Отдельные выходы разрядов управляющего поля регистра микрокоманд св яэаны следующим образом:

YJ - с первым входом элемента И 11,на второй вход которого подключена шина ввода сигнала обмена ОБМ, а вьгход этого элемента связан с управляющим входом регистра 7 адреса,

Y - с управляющим входом шинно- го формирователя 15, тристабильный выход которого подключен к магистрали 24 МПИ,

Y - с вторым входом элемента 21 и установочным в 1 входом триг- гера 12,

YJ - с обнуляющими входами регистра 3 адреса по;у1рограмм, триггера 12 и регистра 7 адреса,

У- - с управляющим входом тай- мера 10,

У - со счетным входом таймера 10.

Уу - с шиной 26 выхода устройст- ва,

Y- - с управляющим входом счетчика 14,

Уд - с управляющим входом регистра контроля.

10

г с вторым входом первого

плеча элемента 2 И-ИЛИ 13.

Работу устройства (и его контроль рассмотрим на примере формирования комплексного цифрового пилообразного сигнала (фиг.З). При этом устрой- (тво настраивают на выполнение этой (как и других) функции путем выполнения операций записи (или чтения) с соответствующим (строго фиксированным для каждой функции) адресом.

Каждая команда записи или чтения информации задается с шины МПИ и выполняется в два этапа (фазы). Временная диаграмма команды записи данных приведена на фиг.2.

В фазе адреса передается адресньм код, который сопровождается сигналом обмена (ОБМ). При этом передний фронт сигнала ОБМ должен формироваться с задержкой относительно пе- реднего фронта адресного сигнала (фиг.2).

В фазе данных на этих же шинах формируется код данных, а на отдельных шинах с задержкой относительно переднего фронта данных формируется сигнал записи данных (.ДЗП). После приема адреса и данных абонент, принимающий их, формирует сигнал ответа

5

0

0

5

0

5 0

5

0

5

ОТВ. По переднему фронту сигнала ответа ОТВ снимается сигнал ДЗП, а по заднему фронту этого сигнала - сигнал обмена данных ОБМ.

Согласно временной диаграмме (фиг.2) код адреса в фазе адреса подается через открытый микрокомандой У 1 шинный формирователь 15 на регистр 7 адреса, где фиксируется передним фронтом сигнала обмена данных ОБМ, поступающим на управляющий вход регистра 7 через открытый микрокомандой YJ 1 элемент И 11.

Зафиксированный на регистре 7 код адреса преобразуется на блоке 6 памяти адресов в код номера подпрограммы, который фиксируется на регистре 3 адреса подпрограмм передним фронтом импульса, формируемого генератором 9 тактовых импульсов (ГТИ), импульсы от которого поступают на управляющий вход регистра 3 адреса подпрограмм через открытый микрокомандой У, элемент И 21.

Микрокоманда У, формируется в процессе анализа сигнала ОБМв случае, если ОБМ 1.

Анализ сигнала обмена ОБМ производится путем выполнения микрокомандных слов, выбираемых из нулевого и первого адресов блока 1 памяти микропрограмм, из нулевой ячейки которого, т.е. начиная из исходного состояния, выбирается микрокомандное слово, которое содержит код текущего адреса (Х 01), т.е. код передачи управления следующей ячейке этого накопителя. Этот код считывается из накопителя, поступает на информационные входы регистра 2 текущего адреса, где фиксируется передним фронтом импульса от генератора 9 тактовых импульсов. Таким образом,в следующем такте из блока 1 будет выбираться содержимое первой ячейки, в котором Хр 02, т.е. будет производиться передача управления на второй адрес блока 1. Очевидно, что будет производиться попеременное считывание информации из нулеврй, первой и второй ячеек накопителя до тех пор, пока сигнал обмена ОБМ не станет равным единице.

Из нулевой ячейки блока 1 памяти микропрограмм группой разрядов X, считывается код управления мультиплексором 8 условий. Этот код фиксируется на соответствующих разрядах регистра 5 микрокоманд по переднему фронту инверсного значения импульсов ГТИ 9 и поступает на управляющий вход мультиплексора 8 условий. Под действием этого кода (X OU мультиплексор условий коммутирует сигнал обмена ОБМ на информационный вход триггера 4 базового адреса. При этом если сигнал обмена равен нулю, то триггер 4 своего исходного состояния не изменяет и управление передается в первую ячейку блока памяти 1 микропрограмм.

Если же сигнал обмена равен единице, то триггер 4 по переднему фронту импульсов от генератора 9 тактовых импульсов 9 изменяет свое состояние на единичное и управление передается на адрес блока 1 памяти микропрограмм.

Таким образом в следующем такте микропрограммное слово будет считываться из ячейки 100,

{икропрограммное слово, считываемое из ячейки с этим адресом, содержит код текущего адреса А ,- , Хд 02g и микрокоманду Y 1 . Микрокоманда Y 1 разрешает работу элемента И 21 и по переднему фронту импульса от генератора 9 тактовых импульсов код номера подпрограмм, соответствуюощй адресу, зафиксированному на регистре 7 адреса фиксируется на регистре 3 адреса подпрограмм. Одновременно на регистре 2 текущего адреса фиксируется код А 02. Триггер 4 базового адреса принимает нулевое значение, так как закрытый мультиплексор 8 условий формирует на своем выходе нулевой потенциал.

Следующие шесть шагов микропрограммы осуществляют анализ сигналов записи данных ДЗП или чтения данных дчт..

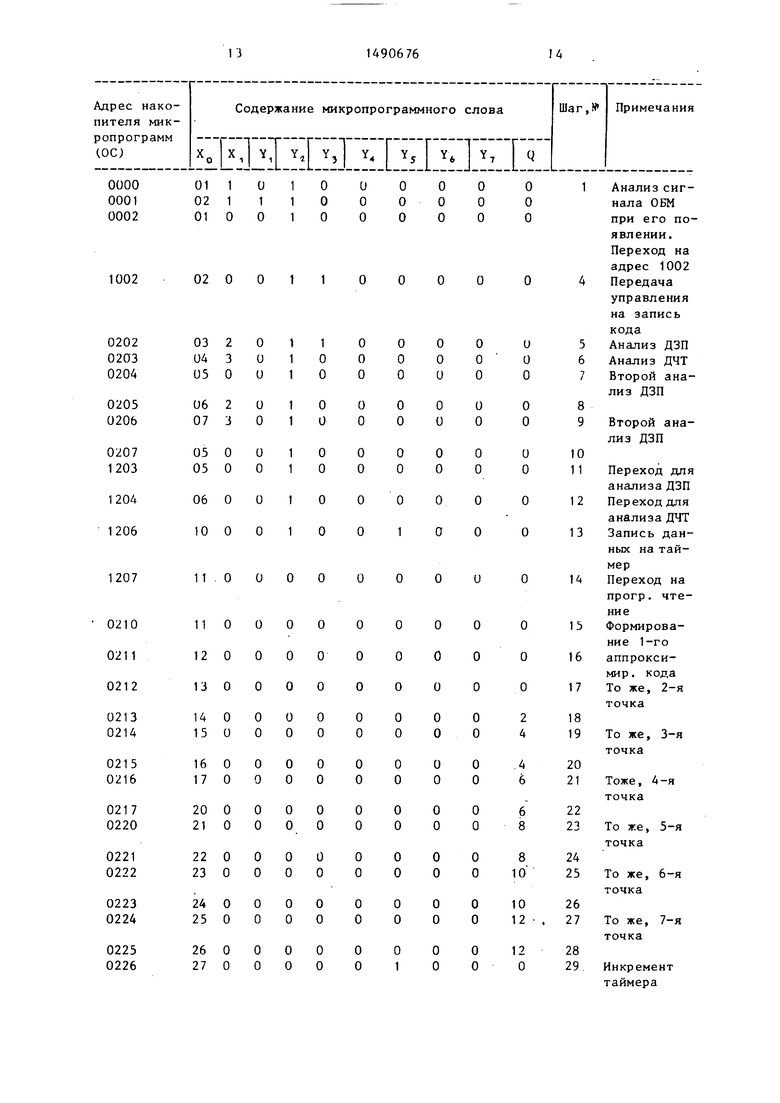

в таблице приведен пример реализации программ формирования пилообразного напряжения. При этом количество шагов К 2, количество циклов формирования комплексного сигнала К 2 (см.таблицу, 15-28 шаги). Контроль работы микропрограммного устройства управления осуществляется в двух режимах:

В режиме трассировки микропрограмм;

в режиме контроля формирования микрокоманд.

Каждый из режимов контроля реализуется в реальном масштабе времени и заключается в регистрации содержимого адресной компоненты микропрограммного устройства управления

.J (МПУУ) и собственно формировании микрокоманд. И первая и вторая компоненты МПУУ фиксируются в блоке 17 оперативной памяти, из которого затем считываются на МПИ с целью их

5 анализа на соответствие действительному их значению.

Анализ может производиться путем пословного сравнения или путем подсчета контрольных сумм с помощью

Q управляющей ЦВМ, подключенной к

МПИ магистрали межмодульного параллельного интерфейса МПИ.

Режим контроля задается регистром 16 контроля. При этом каждый

5 его разряд осуществляет соответствующую функцию задания режимов контроля или управления коммутацией соответствующей информации, подлежащей регистрации.

0 Назначение управляющих полей и

разрядов регистра 16 контроля (фиг.1) следующее:

группа разрядов X 0-3 обеспечивает управление мультиплексором 19«

- бит управления режимом работы блока 17: при О - запись информации, при 1 - чтение информации - бит управления режимом

Q выборки блока 17: при О - выборка запрещена, при 1 - выборка информации разрешена

зГб - бит управления адресацией блока 17: при 1 - разрешение работы по значению счетчика 14, при О - разрешение работы по адресной компоненте устройства;

Z 4,5 Г 7,8 - режим инкремента адресного кода блока 17: 1 - инкремент от внешнего сигнала , О - инкре мент от генерат ора 9 тактовых импульсов.

Загрузка регистра 16 контроля дан- J от магистрали МПИ производится аналогично загрузке таймера с той лишь разницей, что для записи информации на регистр 16 вырабатьшается микрокоманда Yg.

5

5

Чтение ин(})ормации ии регистра 16 контроля производится согласно временной диаграмме, представленной на фи г.4 ,

В режиме трассировки микропрограмм регистр контроля путем записи в него информации настраивается следующим образом: разрядом ХдГО-З устанавливает код 02g, при этом мультиплексор 19 данных настраивается на передачу на информационный вход блока 17 содержимого регистра 2 текущего адреса, регистра 3 адреса подпрограмм, триггера 4 базового адреса. Блок 17 настраивается на режим записи информации.

После описанной подготовки выполняется любая исследуемая микропрограмма .

Пусть в качестве исследуемой будет микропрограмма, приведенная в таблице 1, тогда при реализации этой программы на четвертом шаге ее выполнения сформируется микрокоманда Y 1, которая установит в единичное состояние триггер 12.

Этот триггер единичным сигналом разрешает работу элемента И-ИЛИ 13, который коммутирует на счетный вход счетчика 14 счетные импульсы от генератора импульсов (фиг.4). Таким оразом, после установки триггера 12 в единичное состояние на каждом шаг выполнения микрокоманды содержимое счетчика 14 будет увеличиваться на единицу (инкремент 0) и, следовательно, информация, поступающая на блок 17 с адресных регистров, последовательно зафиксируется в ячейках блока.

Синхроимпульс, фиксирующий адрес блока 17, формируется на элементе И 22, который должен осуществлять н только прямую функцию логического умножения, но и функцию задержки, т.е. время задержки сигнала на этом элементе должно быть больше времени задержки на коммутаторе 18, настроенном на элемент И-НЛИ. Этого можно достичь применением элемента И 22 с большим временем задержки сигнала чем у элемента И-ИЛИ 18.

После завершения операции (таблица 32 шаг) формируется микрокоманда Y 1, которая устанавливает в нулевое состояние триггер 12.

В оперативном запоминающем устройстве зафиксирована последовательность фop шpoвaнIlя адресной компоненты НМ-1, которая может быть считана на магистраль МПИ с помощью спе- циальной команды чтения.

Формула изобретения

Микропрограммное устройство уп0 равления, содержащее блок памяти микропрограмм, регистр микрокоманд, регистры текущего адреса и адреса подпрограмм, триггер базового адреса, мультиплексор условия, первый

5 элемент И, генератор тактовых импульсов, первый выход которого соединен с первым входом первого элемента И и входами синхронизации . триггера базового адреса и регистра

0 текущего адреса, второй выход генератора тактовых импульсов подключен к входу синхронизации регистра микрокоманд, информационные входы кото- poi o соединены с выходами поля мик рокоманд блока памяти микропрограмм, поля адреса которого соединены с информационным входом регистра текущего адреса, выход которого соединен с младшим разрядом адресного входа

0 блока памяти микропрограмм, старшие разряды адресного входа которого под- ключены к выходу регистра адреса подпрограмм, выход триггера базового адреса соединен с оставшимся разря5 дом адресного входа блока памяти

микропрограмм, выход первого элемента И соединен с входом синхронизации размера адреса подпрограмм, информационный вход триггера базового

0 адреса соединен с выходом мультиплексора условий, младшие информационные входы которого подключены к входу логических условий устройства, выход поля микроопераций регистра

5 микрокоманд подключен к первому информационному выходу устройства, управляющие входы мультиплексора условий подключены к выходу поля логических условий регистра микрокоманд,пер вый и второй разряды поля местного управления которого подключены соответственно к второму входу первого элемента И и входу установки в О регистра адреса подпрограмм, о т л и5 чающееся тем, что, с целью повышения эффективности диагностики неисправностей за счет реализации записи следов выполнения микропрограмм, в устройство введены шинный

формирователь, регистр адреса, блок памяти адресов, таймер, триггер,второй и третий элементы И, элемент 2И-ИЛИ, счетчик, регистр контроля, первый и второй мультиплексоры данных, блок оперативной памяти, коммутатор, причем выход шинного формирователя подключен к информационным входам таймера, счетчика, регистра контроля, а регистр адреса - к первому информационному входу первого мультиплексора данных, выход регистра адреса соединен с входом блока памяти адресов, выход которого сое- динен с информационным входом регистра адреса подпрограмм, выход счетчика подключен к первому информационному входу коммутатора, второму информационному входу первого мульти- плексора данных, первому информационному входу второго мультиплексора данных, выходы регистров текущего адреса, адреса подпрограмм и триггера базового адреса-объединены и под- ключены к второму информационному входу коммутатора и третьему информационному входу первого мультиплексор данных, выход которого соединен с информационным входом блока оператив ной памяти, выход которого соединен с вторым информационным входом второго мультиплексора данных, выход которого соединен с информационным входом шинного формирователя, информа- ционный вход-выход которого соединен с информационным входом-выходом устройства, вькод поля адреса блока памяти микрокоманд соединен с четверты информационным входом первого мульти плексора данных, выход поля микрокоманд регистра микрокоманд соединен с пятым информационным входом первого мультиплексора данных, выходы полей местного управления и логических ус- ловий регистра микрокоманд соединены соответственно с шестым и седьмым информационными входами первого мультиплексора данных, выход регистра контроля соединен с третьим информа

ционным входом второго мультиплексора

5 0 5 0 , Q

0

данных, с первого по четвертый разряды выхода -регистра контроля соединен с управляющим входом первого мультиплексора данных, с пятого по восьмой разряды выхода регистра контроля соединены соответственно с входом записи-чтения блока оперативной памяти, первым входом второго элемента И,управляющим входом коммутатора, первым и вторым входаьш элемента 2И-ИЛИ, выход коммутатора соединен с адресным входом блока оперативной памяти,.первый выход генератора тактовых пульсов соединен с третьим входом элемента И-ИЛИ, выход которого соединен со счетным входом счетчика и вторым входом второго элемента И,выход которого соединен с входом синхронизации блока оперативной памяти, выход таймера соединен со старшим разрядом информационного входа мультиплексора условий, первый и второй разряды выхода поля местного управления регистра микрокоманд соединены соответственно с входом установки в 1 и входом установки в О триггера, с второго по десятый разряды выхода поля местного управления регистра микрокоманд соединены соответственно с входом установки в О регистра адреса, первым-входом третьего элемента И, управляющим входом шинного формирователя, входом регулирования работы таймера, счетным входом таймера, вторым информационным выходом устройства, входом режима работы счетчика, входом синхронизации регистра контроля, четвертым входом элемента И-ИЛИ, выход триггера соединен с пятым входом элемента И-ИЛИ, выход третьего элемента И соединен с входом синхронизации регистра адреса, первый младших разряд входа логических условий устройства соединен с вторым входом третьего элемента И, выход поля связи регистра микрокоманд соединен с управляющим входом второго мультиплексора данных.

15

U90676

16

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1476477A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Многоканальный микропрограммный счетчик | 1985 |

|

SU1280598A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

Изобретение относится к вычислительной технике и может быть использовано для программного управления работой исполнительных устройств и механизмов повышения эффективности диагностики неисправностей. Устройство содержит накопитель микропрограмм, регистр микрокоманд, регистры текущего адреса и адреса подпрограмм, триггер базового адреса, мультиплексор условий, элемент И, генератор тактовых импульсов, шинный формирователь, регистр адреса, блок памяти адресов, таймер, триггер, второй и третий элементы И, элемент И-ИЛИ, счетчик, регистр контроля, первый и второй мультиплексоры данных, блок оперативной памяти, коммутатор. Новыми в устройстве являются шинный формирователь, регистр адреса, блок памяти адресов, таймер, триггер, второй и третий элементы И, элемент 2И-ИЛИ, счетчик, регистр контроля, первый и второй мультиплексоры данных, блок оперативной памяти, коммутатор. В устройстве обеспечивается запись следов выполнения микропрограмм и возможность оперативной выдачи этой информации. 5 ил., 1 табл.

Содержание микропрограммного

слова

..ItjjLiZrj -LQfliLlJZD.

30 4000 О О О О

0230

10 0000000Оо

1230

00 о о о о 1 о о 1

Шаг,

примечания

слова

0 Анализ переп. тайм.

31Перех.к формированию пилообразного сигнала

2Формирование сигнала отврта.Передача управления в нулевой адрес

м

у дрес Лонные

ОбМ

ДЗ/7

Фиг.1

V

мпи

.

06Н

uvr

073

j Лаинью v

V

Фиг. 5

| Устройство микропрограммного управления | 1984 |

|

SU1236476A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1241241A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-06-30—Публикация

1987-08-17—Подача